实验六Verilog设计分频器计数器电路

实验六 Verilog设计分频器计数器电路答案

实验六Verilog设计分频器/计数器电路一、实验目的1、进一步掌握最基本时序电路的实现方法;2、学习分频器/计数器时序电路程序的编写方法;3、进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10。

v.2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为coute r10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5。

v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3.。

0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端.三、实验步骤实验一:分频器1、建立工程2、创建Verilog HDL文件3、输入10分频器程序代码并保存4、进行综合编译5、新建波形文件6、导入引脚7、设置信号源并保存8、生成网表9、功能仿真10、仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。

用Verilog语言实现奇数倍分频电路3分频5分频7分频

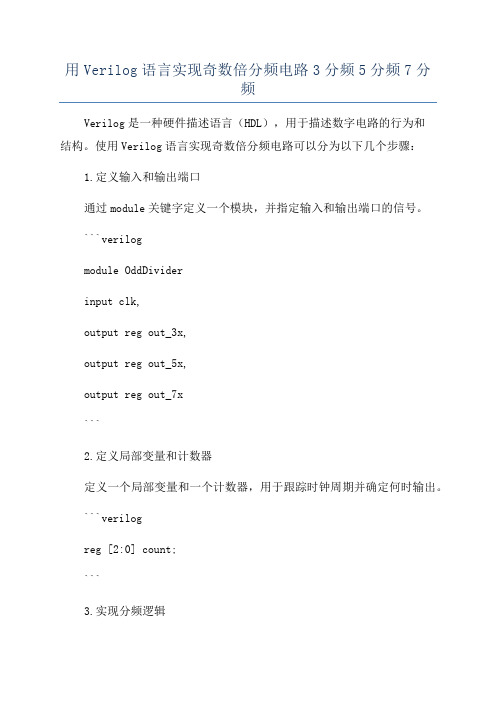

用Verilog语言实现奇数倍分频电路3分频5分频7分频Verilog是一种硬件描述语言(HDL),用于描述数字电路的行为和结构。

使用Verilog语言实现奇数倍分频电路可以分为以下几个步骤:1.定义输入和输出端口通过module关键字定义一个模块,并指定输入和输出端口的信号。

```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7x```2.定义局部变量和计数器定义一个局部变量和一个计数器,用于跟踪时钟周期并确定何时输出。

```verilogreg [2:0] count;```3.实现分频逻辑使用always块,根据计数器的值判断何时输出,并在输出端口上更新信号。

```verilogif (count == 3'b000) beginout_3x <= !out_3x;endif (count == 3'b001) beginout_5x <= !out_5x;endif (count == 3'b010) beginout_7x <= !out_7x;endcount <= count + 1;end```4.结束模块使用endmodule关键字结束模块定义。

```verilogendmodule完整的Verilog代码如下:```verilogmodule OddDividerinput clk,output reg out_3x,output reg out_5x,output reg out_7xreg [2:0] count;if (count == 3'b000) begin out_3x <= !out_3x;endif (count == 3'b001) begin out_5x <= !out_5x;endif (count == 3'b010) begin out_7x <= !out_7x;endcount <= count + 1;endmodule```以上代码实现了一个奇数倍分频电路,其中输入时钟信号为`clk`,输出分别是3倍分频的信号`out_3x`,5倍分频的信号`out_5x`和7倍分频的信号`out_7x`。

verilog奇偶分频

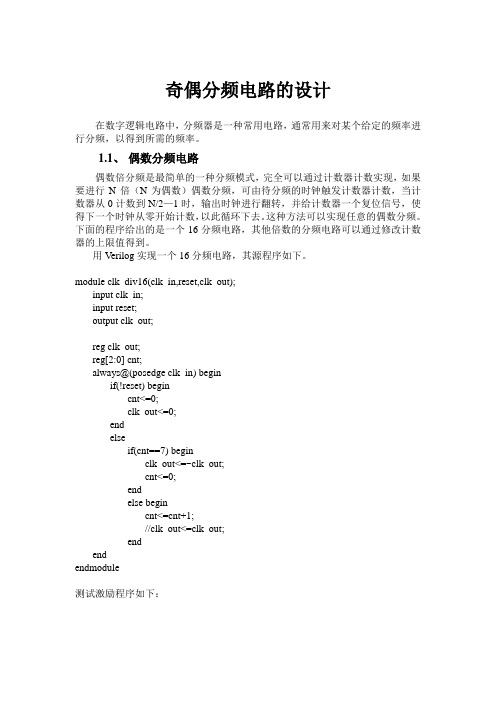

奇偶分频电路的设计在数字逻辑电路中,分频器是一种常用电路,通常用来对某个给定的频率进行分频,以得到所需的频率。

1.1、偶数分频电路偶数倍分频是最简单的一种分频模式,完全可以通过计数器计数实现,如果要进行N倍(N为偶数)偶数分频,可由待分频的时钟触发计数器计数,当计数器从0计数到N/2—1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数,以此循环下去。

这种方法可以实现任意的偶数分频。

下面的程序给出的是一个16分频电路,其他倍数的分频电路可以通过修改计数器的上限值得到。

用Verilog实现一个16分频电路,其源程序如下。

module clk_div16(clk_in,reset,clk_out);input clk_in;input reset;output clk_out;reg clk_out;reg[2:0] cnt;always@(posedge clk_in) beginif(!reset) begincnt<=0;clk_out<=0;endelseif(cnt==7) beginclk_out<=~clk_out;cnt<=0;endelse begincnt<=cnt+1;//clk_out<=clk_out;endendendmodule测试激励程序如下:module clk_div16_tb;reg clk_in;reg reset;wire clk_out;clk_div16 uut (.clk_in(clk_in),.reset(reset),.clk_out(clk_out));initial begin// Initialize Inputsclk_in = 0;reset = 0;#10 reset=1;endalways #2 clk_in=~clk_in;endmodule上述程序经过Synplify Pro 综合后,其RTL级结构如下图所示在ModelSim6.5中完成仿真,结果如图所示。

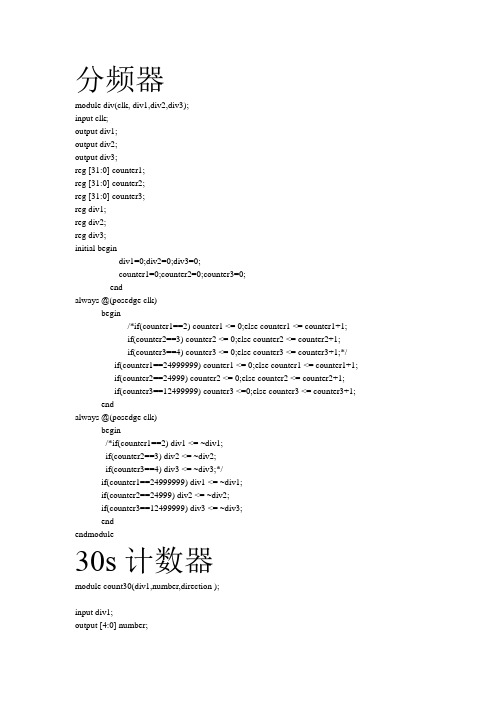

verilog 分频器,30s计数器及交通灯控制器设计

分频器module div(clk, div1,div2,div3);input clk;output div1;output div2;output div3;reg [31:0] counter1;reg [31:0] counter2;reg [31:0] counter3;reg div1;reg div2;reg div3;initial begindiv1=0;div2=0;div3=0;counter1=0;counter2=0;counter3=0;endalways @(posedge clk)begin/*if(counter1==2) counter1 <= 0;else counter1 <= counter1+1;if(counter2==3) counter2 <= 0;else counter2 <= counter2+1;if(counter3==4) counter3 <= 0;else counter3 <= counter3+1;*/ if(counter1==24999999) counter1 <= 0;else counter1 <= counter1+1;if(counter2==24999) counter2 <= 0;else counter2 <= counter2+1;if(counter3==12499999) counter3 <=0;else counter3 <= counter3+1;endalways @(posedge clk)begin/*if(counter1==2) div1 <= ~div1;if(counter2==3) div2 <= ~div2;if(counter3==4) div3 <= ~div3;*/if(counter1==24999999) div1 <= ~div1;if(counter2==24999) div2 <= ~div2;if(counter3==12499999) div3 <= ~div3;endendmodule30s计数器module count30(div1,number,direction );input div1;output [4:0] number;reg [4:0] number;reg direction;initialbegindirection=0;number=30;endalways@(posedge div1)beginif(number==0)begindirection<=~direction;number<=30;endelse number<=number-1;endendmodule控制器module moniter( div3,number,direction,eastred,eastyellow,eastgreen,northred,northyellow,northgreen );input div3;input direction;input [4:0]number;output eastred;output eastyellow;output eastgreen;output northred;output northyellow;output northgreen ;//wire [4:0] number;reg eastred;reg eastyellow;reg eastgreen;reg northred;reg northyellow;reg northgreen ;initial begineastred<=1;eastgreen<=0;northred<=1;northgreen<=0;northyellow<=eastyellow<=0;endalways @(posedge div3)beginif(number<=3)beginif (direction==0) eastyellow<=~eastyellow;else northyellow<=~northyellow;endelse begin eastyellow<=0;northyellow<=0;end endalways @(number )/*beginif(number==30&&direction==0)begin eastred<=1;eastgreen<=0;northred<=1;northgreen<=0;end*/if (number>2'b00010&&direction==0)begineastred<=0;eastgreen<=1;northred<=1;northgreen<=0;endelse if(number<3&&direction==0)begineastred<=0;eastgreen<=0;northred<=1;northgreen<=0;endelse if(number>2&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=1;endelse if(number<3&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=0;endendmodule译码器module yimaqi( clk,number,led1,led2);input clk;input [4:0] number;output [6:0] led1;output [6:0] led2;reg [6:0] led1;reg [6:0] led2;always @( number )begincase (number)5'b00000: begin led1 <= 7'b0000001; led2 <= 7'b0000001;end5'b00001: begin led1 <= 7'b0000001; led2 <= 7'b1001111;end5'b00010: begin led1 <= 7'b0000001; led2 <= 7'b0010010;end7'b0000110;end5'b00100: begin led1 <= 7'b0000001; led2 <= 7'b1001100;end5'b00101: begin led1 <= 7'b0000001; led2 <= 7'b0100100;end5'b00110: begin led1 <= 7'b0000001; led2 <= 7'b1100000;end5'b00111: begin led1 <= 7'b0000001; led2 <= 7'b0001111;end5'b01000: begin led1 <= 7'b0000001; led2 <= 7'b0000000;end5'b01001: begin led1 <= 7'b0000001; led2 <= 7'b0001100; end5'b01010: begin led1 <= 7'b1001111; led2 <= 7'b0000001;end5'b01011: begin led1 <= 7'b1001111; led2 <= 7'b1001111; end5'b01100: begin led1 <= 7'b1001111; led2 <= 7'b0010010;end5'b01101: begin led1 <= 7'b1001111; led2 <= 7'b0000110; end5'b01110: begin led1 <= 7'b1001111; led2 <= 7'b1001100;end5'b01111: begin led1 <= 7'b1001111; led2 <= 7'b0100100;end5'b10000: begin led1 <= 7'b1001111; led2 <= 7'b1100000;end5'b10001: begin led1 <= 7'b1001111; led2 <= 7'b0001111;end5'b10010: begin led1 <= 7'b1001111; led2 <= 7'b0000000;end5'b10011: begin led1 <= 7'b1001111; led2 <= 7'b0001100;end5'b10100: begin led1 <= 7'b0010010; led2 <= 7'b0000001;end5'b10101: begin led1 <= 7'b0010010; led2 <= 7'b1001111;end5'b10110: begin led1 <= 7'b0010010; led2 <= 7'b0010010;end5'b10111: begin led1 <= 7'b0010010; led2 <= 7'b0000110;end5'b11000: begin led1 <= 7'b0010010; led2 <= 7'b1001100;end7'b0100100;end5'b11010: begin led1 <= 7'b0010010; led2 <= 7'b1100000;end5'b11011: begin led1 <= 7'b0010010; led2 <= 7'b0001111;end5'b11100: begin led1 <= 7'b0010010; led2 <= 7'b0000000;end5'b11101: begin led1 <= 7'b0010010; led2 <= 7'b0001100;end5'b11110: begin led1 <= 7'b0000110; led2 <= 7'b0000001;enddefault: begin led1 <= 7'b0000000; led2 <= 7'b0000000;endendcaseendendmodulemodule dianzhen(direction,clk,div2,row,con);input div2;input clk;input direction;output[15:0] row;output[15:0] con;reg[15:0] row;reg[15:0] con;integer cnt,b;reg[15:0] r[48:0];initialbeginif (direction==0)begin// 丁r[0] <=16'b1111111111111111;r[1] <=16'b1011111111111111;r[2] <=16'b1011111111111111;r[3] <=16'b1011111111111111;r[4] <=16'b1011111111111111;r[5] <=16'b1011111111111011;r[6] <=16'b1011111111111101;r[7] <=16'b1000000000000011;r[8] <=16'b1011111111111111;r[9] <=16'b1011111111111111;r[10]<=16'b1011111111111111;r[11] <=16'b1011111111111111;r[12]<=16'b1011111111111111;r[13]<=16'b1011111111111111;r[14]<=16'b1011111111111111;r[15]<=16'b1111111111111111;// 乾r[16]<=16'b1101111111101111 ;r[17]<=16'b1101000000101111 ;r[18]<=16'b1101010101101111 ;r[19]<=16'b0000010101101111 ;r[20]<=16'b1101010100000000 ;r[21]<=16'b1101010101101111 ;r[22]<=16'b1101000000101111 ;r[23]<=16'b1101110111101111 ;r[24]<=16'b1111001111110011 ;r[25]<=16'b0000110111001101 ;r[26]<=16'b1010110110111101 ;r[27]<=16'b1110110101111101 ;r[28]<=16'b1110110011111101 ;r[29]<=16'b1110110111100001 ;r[30]<=16'b1110111111111011 ;r[31]<=16'b1111111111111111 ;// 全灭r[32]<=16'b1111111111111111;r[33]<=16'b1111111111111111;r[34]<=16'b1111111111111111;r[35]<=16'b1111111111111111;r[36]<=16'b1111111111111111;r[37]<=16'b1111111111111111;r[38]<=16'b1111111111111111;r[39]<=16'b1111111111111111;r[40]<=16'b1111111111111111;r[41]<=16'b1111111111111111;r[42]<=16'b1111111111111111;r[43]<=16'b1111111111111111;r[44]<=16'b1111111111111111;r[45]<=16'b1111111111111111;r[46]<=16'b1111111111111111;r[47]<=16'b1111111111111111;endelse if(direction==1)begin//1r[0] <=16'b 1111111111111111;r[1] <=16'b 1111111111111111;r[2] <=16'b 1111111111111111;r[3] <=16'b 1111111111111111;r[4] <=16'b 1111111111111111;r[5] <=16'b 1111011111111011;r[6] <=16'b 1111011111111011;r[7] <=16'b 1110000000000011;r[8] <=16'b 1111111111111011;r[9] <=16'b 1111111111111011;r[10]<=16'b 1111111111111111;r[11] <=16'b 1111111111111111;r[12]<=16'b 1111111111111111;r[13]<=16'b 1111111111111111;r[14]<=16'b 1111111111111111;r[15]<=16'b 1111111111111111;// 0r[16]<=16'b 1111111111111111;r[17]<=16'b 1111111111111111;r[18]<=16'b 1111111111111111;r[19]<=16'b 1111111111111111;r[20]<=16'b 1111111111111111;r[21]<=16'b 1111100000001111;r[22]<=16'b 1111011111110111;r[23]<=16'b 1110111111111011;r[24]<=16'b 1110111111111011;r[25]<=16'b 1111011111110111;r[26]<=16'b 1111100000001111;r[27]<=16'b 1111111111111111;r[28]<=16'b 1111111111111111;r[29]<=16'b 1111111111111111;r[30]<=16'b 1111111111111111;r[31]<=16'b 1111111111111111;// 9r[32]<=16'b 1111111111111111;r[33]<=16'b 1111111111111111;r[34]<=16'b 1111111111111111;r[35]<=16'b 1111111111111111;r[36]<=16'b 1111111111111111;r[37]<=16'b 1111100011111111;r[38]<=16'b 1111011101110011;r[39]<=16'b 1110111110111011;r[40]<=16'b 1110111110111011;r[41]<=16'b 1111011101110111;r[42]<=16'b 1111100000001111;r[43]<=16'b 1111111111111111;r[44]<=16'b 1111111111111111;r[45]<=16'b 1111111111111111;r[46]<=16'b 1111111111111111;r[47]<=16'b 1111111111111111;endendalways@(posedge clk )beginif (b==47)b<=0;else b<=b+1;endalways@(posedge div2)beginif(cnt==15)begincnt<=0;endelsecnt<=cnt+1;case(cnt)15: con<=16'b0000_0000_0000_0001; 14: con<=16'b0000_0000_0000_0010; 13: con<=16'b0000_0000_0000_0100; 12: con<=16'b0000_0000_0000_1000; 11: con<=16'b0000_0000_0001_0000; 10: con<=16'b0000_0000_0010_0000; 9: con<=16'b0000_0000_0100_0000; 8: con<=16'b0000_0000_1000_0000; 7: con<=16'b0000_0001_0000_0000; 6: con<=16'b0000_0010_0000_0000; 5: con<=16'b0000_0100_0000_0000; 4: con<=16'b0000_1000_0000_0000; 3: con<=16'b0001_0000_0000_0000; 2: con<=16'b0010_0000_0000_0000; 1: con<=16'b0100_0000_0000_0000; 0: con<=16'b1000_0000_0000_0000;endcasecase(cnt)0: row<=r[b+0];1: row<=r[b+1];2: row<=r[b+2];3: row<=r[b+3];4: row<=r[b+4];5: row<=r[b+5];6: row<=r[b+6];7: row<=r[b+7];8: row<=r[b+8];9: row<=r[b+9];10: row<=r[b+10];11: row<=r[b+11];12: row<=r[b+12];13: row<=r[b+13];14: row<=r[b+14];15: row<=r[b+15];endcaseendendmodule。

Verilog实现奇数和偶数分频器和半整数及任意小数分频器程序

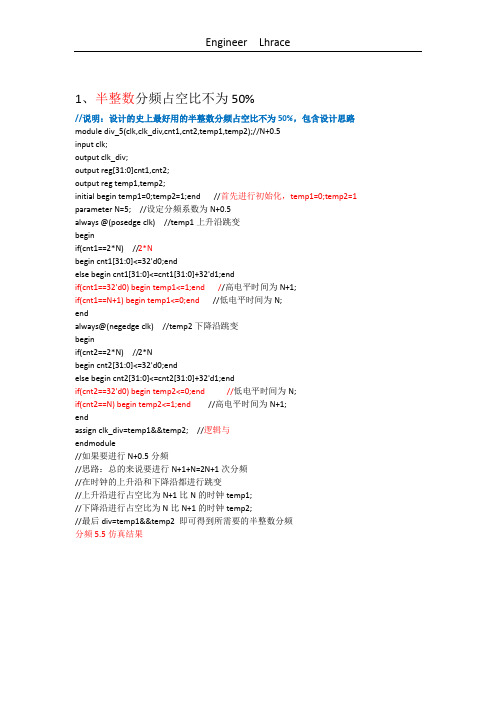

1、半整数分频占空比不为50%//说明:设计的史上最好用的半整数分频占空比不为50%,包含设计思路module div_5(clk,clk_div,cnt1,cnt2,temp1,temp2);//N+0.5input clk;output clk_div;output reg[31:0]cnt1,cnt2;output reg temp1,temp2;initial begin temp1=0;temp2=1;end //首先进行初始化,temp1=0;temp2=1 parameter N=5; //设定分频系数为N+0.5always @(posedge clk) //temp1上升沿跳变beginif(cnt1==2*N) //2*Nbegin cnt1[31:0]<=32'd0;endelse begin cnt1[31:0]<=cnt1[31:0]+32'd1;endif(cnt1==32'd0) begin temp1<=1;end //高电平时间为N+1;if(cnt1==N+1) begin temp1<=0;end//低电平时间为N;endalways@(negedge clk) //temp2下降沿跳变beginif(cnt2==2*N) //2*Nbegin cnt2[31:0]<=32'd0;endelse begin cnt2[31:0]<=cnt2[31:0]+32'd1;endif(cnt2==32'd0) begin temp2<=0;end //低电平时间为N;if(cnt2==N) begin temp2<=1;end //高电平时间为N+1;endassign clk_div=temp1&&temp2; //逻辑与endmodule//如果要进行N+0.5分频//思路:总的来说要进行N+1+N=2N+1次分频//在时钟的上升沿和下降沿都进行跳变//上升沿进行占空比为N+1比N的时钟temp1;//下降沿进行占空比为N比N+1的时钟temp2;//最后div=temp1&&temp2 即可得到所需要的半整数分频分频5.5仿真结果2、奇数分频占空比为50%//说明:奇数分频。

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

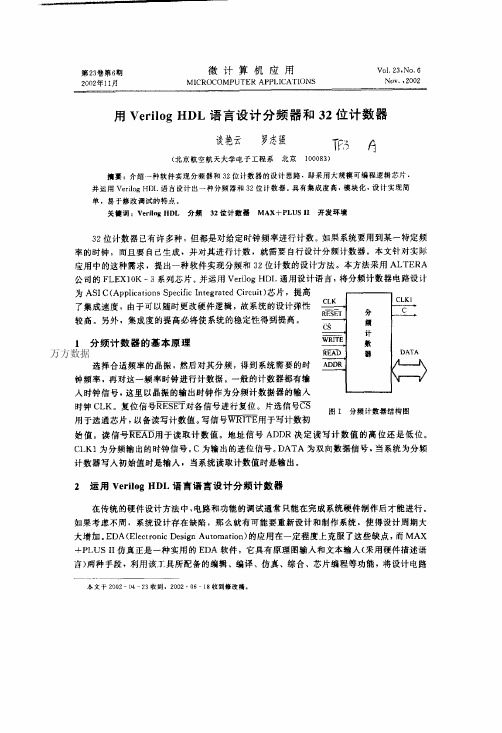

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

Verilog语言实现5分频电路的设计

Verilog语言实现5分频电路的设计1.行为建模方法:使用行为建模方法,可以通过描述电路的功能行为来实现5分频电路。

以下是使用Verilog语言进行行为建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outreg [2:0] counter;counter <= 0;clk_out <= ~clk_out;end else begincounter <= counter + 1;endendendmodule```在该示例中,定义了一个模块`DivideBy5`,包含一个输入端口`clk`和一个输出端口`clk_out`,分别用于输入时钟信号和输出分频后的时钟信号。

`reg [2:0] counter`是一个3位的寄存器,用于计数。

当计数达到5时,即计数器的值为5,会将`counter`复位为0,并将输出时钟信号`clk_out`取反。

否则,计数器的值会自增12.结构建模方法:使用结构建模方法,可以通过组合和顺序电路的连接方式来实现5分频电路。

以下是使用Verilog语言进行结构建模的代码示例:```verilogmodule DivideBy5input wire clk,output wire clk_outwire clk_out_2;wire clk_out_3;wire clk_out_4;DivideBy2 div_by_2 ( .clk(clk), .clk_out(clk_out_2) );DivideBy2 div_by_3 ( .clk(clk_out_2), .clk_out(clk_out_3) );DivideBy2 div_by_4 ( .clk(clk_out_3), .clk_out(clk_out_4) );DivideBy2 div_by_5 ( .clk(clk_out_4), .clk_out(clk_out) );endmodulemodule DivideBy2input wire clk,output wire clk_outreg clk_out;clk_out <= ~clk_out;endendmodule```在该示例中,定义了两个模块`DivideBy5`和`DivideBy2`。

用Verilog HDL语言设计分频器和32位计数器

用Verilog HDL语言设计分频器和32位计数器

谈艳云;罗志强

【期刊名称】《网络新媒体技术》

【年(卷),期】2002(023)006

【摘要】介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片,并运用Verilog HDL语言设计出一种分频器和32位计数器.具有集成度高,模块化,设计实现简单,易于修改调试的特点.

【总页数】2页(P366-367)

【作者】谈艳云;罗志强

【作者单位】北京航空航天大学电子工程系,北京,100083;北京航空航天大学电子工程系,北京,100083

【正文语种】中文

【中图分类】TP3

【相关文献】

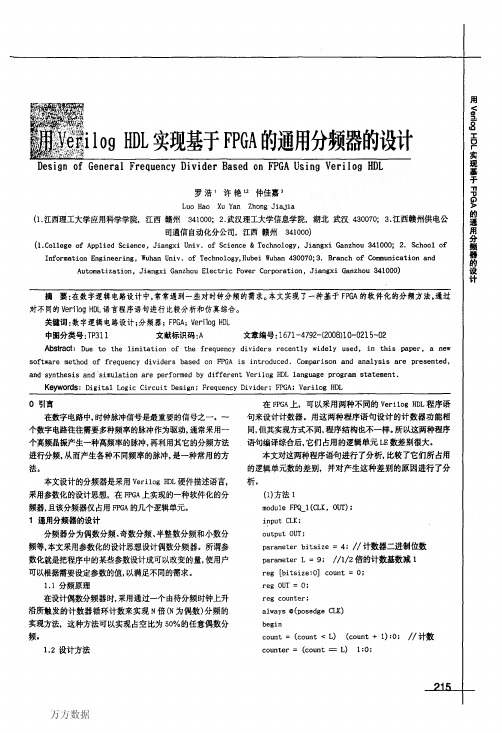

1.用Verilog HDL实现基于FPGA的通用分频器的设计 [J], 罗浩;许艳;仲佳嘉

2.多位格雷码计数器的Verilog HDL描述方法 [J], 李慧静;刘慧文

3.应用Verilog HDL设计等占空比奇数分频器 [J], 徐雷;孙长智;

4.应用Verilog HDL设计等占空比奇数分频器 [J], 徐雷;孙长智

5.Verilog-HDL讲座第六讲用Verilog-HDL做CPLD设计目标板的设计和下载软件的使用 [J], 李媛媛;常晓明

因版权原因,仅展示原文概要,查看原文内容请购买。

数字电子电路数电实验报告基于FPGA的分频器设计

装……订……线基于FPGA的分频器设计一、实验目的1、了解EDA软件在电子设计当中的重要作用EDA:EDA是电子设计自动化(Electronic Design Automation)的缩写,在)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CA T)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术:就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性。

2、熟悉并掌握MAXPLUS II 或QUARTUS II等开发软件的基本使用方法。

3、运用图解法设计分频器电路,并进行电路仿真。

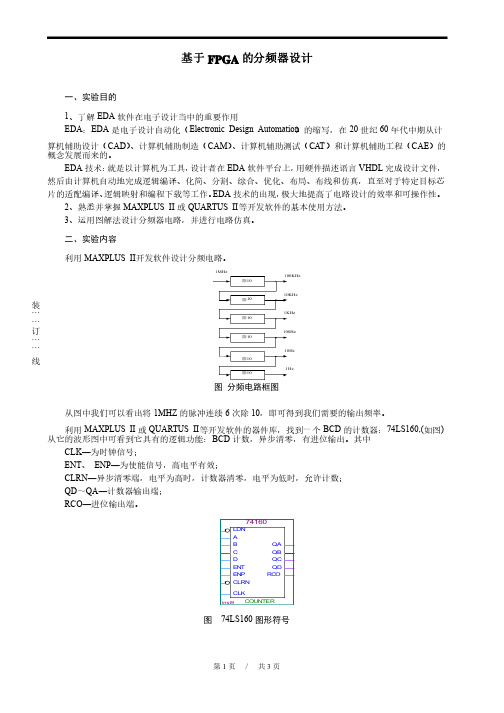

二、实验内容利用MAXPLUS II开发软件设计分频电路。

1MHz除10除10除10除10除10除10100KHz10KHz1KHz100Hz10Hz1Hz图分频电路框图从图中我们可以看出将1MHZ的脉冲连续6次除10,即可得到我们需要的输出频率。

利用MAXPLUS II 或QUARTUS II等开发软件的器件库,找到一个BCD的计数器:74LS160,(如图)从它的波形图中可看到它具有的逻辑功能:BCD计数,异步清零,有进位输出。

其中CLK—为时钟信号;ENT、ENP—为使能信号,高电平有效;CLRN—异步清零端,电平为高时,计数器清零,电平为低时,允许计数;QD~QA—计数器输出端;RCO—进位输出端。

图74LS160图形符号C O U N T E RCLKE N TABCDLDNE N PCLRNQDQAQBQCR C O74160inst9第1页/共3页装……订……线图 74LS160波形图74LS160是一个对输入时钟进行十分频的器件。

当计数器从0计数到9时,RCO 从低电平跳到高电平,在下一个脉冲到来时,RCO 再回到低电平。

分频器电路的Verilog设计

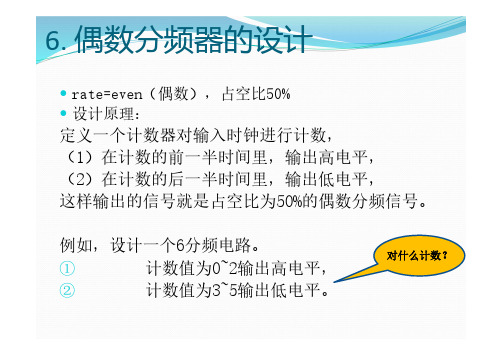

6. 偶数分频器的设计rate=even(偶数),占空比50%设计原理:定义一个计数器对输入时钟进行计数,(1)在计数的前一半时间里,输出高电平,(2)在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,设计一个6分频电路。

对什么计数?①计数值为0~2输出高电平,②计数值为3~5输出低电平。

上升沿计数一个计数周期0112分频module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt<n-1) cnt<=cnt+1;else cnt<=0;endalways@(cnt)beginif(cnt<n/2) clkout<=1'b1;else clkout<=1'b0;end endmodule计数过程判断赋值过程module divder_even(clkin,clkout);parameter n=2;input clkin;output clkout;integer cnt;reg clkout;always@(posedge clkin)beginif(cnt==n/2-1)begincnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule 2分频分析4分频分析二分频四分频知识小结1.移位寄存器的verilog描述。

2.偶数分频的verilog描述。

作业1.设计一个5位串入并出的移位寄存器。

Clear :同步清零;clkin :时钟输入;databit :位输入y[4..0]并行数据输出;2.设计一个4位并入串出的移位寄存器Clear :同步清零;clkin :时钟输入(移位);dataIn :并行数据输入,y :串行数据输出。

用Verilog+HDL实现基于FPGA的通用分频器的设计

要.

暑

工 。 广

实

现

基

于

1'

_口

o

>

的

通

用

分

频

器

的

设

计

万方数据

end

always@(posedge counter)

OUT=’OUT: Endmodule

在方法1中,计数部分采用了?:运算符,这种运算符简 单明了,易于阅读。但在程序中需使用两个always型语句, 才能实现分频后的输出。

中国电力教育,2006 【5]5吴玉昌,胡荣强,王文娟.基于CPLD/FPGA的多功能

分频器的设计与实现[J】.设计应用.2007. 【6】杜刚,孙超,陈安军.基于FPGA技术的16位数字分

频器的设计[J】.仪器仪表学报,2006.

作者简介 罗浩,男,江西理工大学信息工程学院在读研究生,江西

理工大学应用科学学院助教,主要研究方向:通信与信息系 统。

参考文献 [1]I徐欣,于红旗,易凡等.基于FPGA的嵌人式系统设计

【M】.北京:机械工业出版社,2005. [2]张建平,杜学东.一种基于FPGA的分频方法研究

[J】.福建电脑,2006. [3】何静,李清峰.基于FPGA/CPLD的占空比为1:n的n

分频器的设计[J].现代电子技术。2006. [4】杨旭辉.基于FPGA/CPLD的多种分频器的研究【J】.

9

14

8

80

5பைடு நூலகம்

39

16

9

200

6

99

21

11

从表一中可以看出,在实现相同倍数的分频器时,不同 的程序语句占用的FPGA的逻辑单元LE数不同,方法1约是 方法2的两倍。 2结束语

verilog十六分频实现

c.这样的话就可以实现对时钟信号的16分频.

2.测试平台设计

模块设计:

`timescale 1ns/1ns

module div_16(clk,

reset,

dout);

input clk //时钟信号

二、实验设备(环境)及要求

实验软件:ModelSim SE 6.2b

三、实验内容与步骤

1.实验总体设计思路

用一个计数器(counter)来计数,当计数器等于7时,让输出结果翻转,同时计数器置零,如此往下.

a.输入端口为有时钟信号clk以及复位信号reset,输出为dout,先用reset信号把clk和dout都清零.

《FPGA实验》

实验报告

(用计数方法实现一个16分频电路)

学院:物理与信息工程学院

专业:微电子

姓名:汪小东

学号:111000529

一、实验目的及要求

实验目的:进一步熟悉verilog语言,学会熟练操作modelsim软件,并用它进行仿真,为以后的进一步发展打下良好基础.

实验要求:使用计数方法实现一个16分频电路,用Verilog写出电路实现程序以及测试文件.

Endmodule //结束

四、实验结果与数据处理

1.Modelsim仿真结果,波形图。

仿真结果波形图如下:

上图中第一条线是时钟信号(clk),第二条是复位信号(reset),第三条是输出结果(dout),第四条是设置的三位计数器(conuter),复位信号在0时刻清零此时dout和counter都复位,5秒时复位信号失去作用,clk 10ns开始产生,并且周期为20ns,从仿真波形图中可以看出,dout的周期变为clk的16倍,也就是16分频,这正是我们期望的.

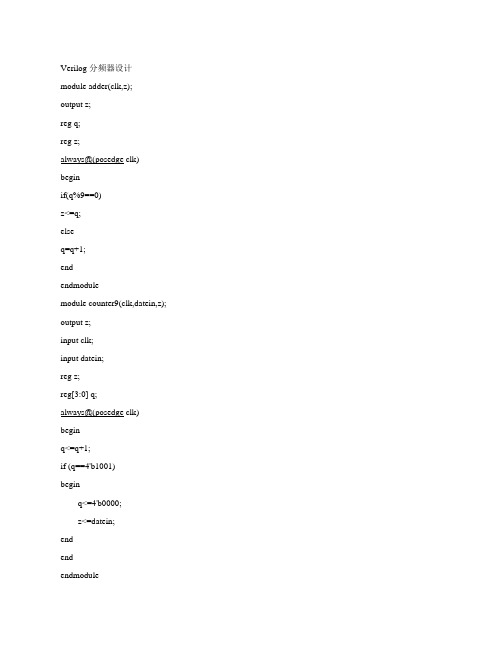

Verilog分频器设计

Verilog分频器设计module adder(clk,z);output z;reg q;reg z;always@(posedge clk)beginif(q%9==0)z<=q;elseq=q+1;endendmodulemodule counter9(clk,datein,z); output z;input clk;input datein;reg z;reg[3:0] q;always@(posedge clk)beginq<=q+1;if (q==4'b1001)beginq<=4'b0000;z<=datein;endendendmodule2008-11-04 19:58分频器是FPGA设计中使用频率非常高的基本单元之一。

尽管目前在大部分设计中还广泛使用集成锁相环(如altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计,但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍然非常流行。

首先这种方法可以节省锁相环资源,再者,这种方式只消耗不多的逻辑单元就可以达到对时钟操作的目的。

偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

module odd_division(clk,rst,count,clk_odd); /*count没必要放在端口中,这里只是为了仿真时观察*/input clk,rst;output clk_odd;output[3:0] count;reg clk_odd;reg[3:0] count;parameter N = 6; /*6分频* /always @ (posedge clk)if(! rst)begincount <= 1'b0;clk_odd <= 1'b0;endelseif ( count < N/2-1)begincount <= count + 1'b1;endelsebegincount <= 1'b0;clk_odd <= ~clk_odd;endendmodule奇数倍分频:归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到N-1)/2进行输出时钟翻转,然后经过(N+1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

【VIP专享】Verilog计数分频

count<=0; end end end endmodule

另一种实现:

module div3(CLKIN,CLKOUT,RESETn);

input CLKIN,RESETn;

output CLKOUT;

wire d;

reg q1,q2;

wire

CLKOUT;

always @(negedge RESETn or posedge CLKIN) begin if (RESETn==1'b0) q1<=1'b0; else q1<=d; //q1 是 d 延迟一个时钟后的信号

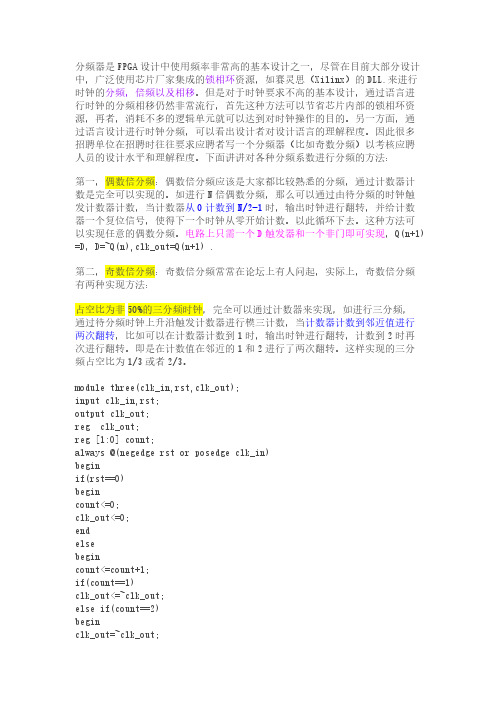

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频 有两种实现方法:

占空比为非 50%的三分频时钟,完全可以通过计数器来实现,如进行三分频, 通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行 两次翻转,比如可以在计数器计数到 1 时,输出时钟进行翻转,计数到 2 时再 次进行翻转。即是在计数值在邻近的 1 和 2 进行了两次翻转。这样实现的三分 频占空比为 1/3 或者 2/3。

module three(clk_in,rst,clk_out); input clk_in,rst; output clk_out; reg clk_out; reg [1:0] count; always @(negedge rst or posedge clk_in) begin if(rst==0) begin count<=0; clk_out<=0; end else begin count<=count+1; if(count==1) clk_out<=~clk_out; else if(count==2) begin clk_out=~clk_out;

实验六-数字频率计的Verilog-HDL语言实现

五邑大学实验报告实验课程名称)数字频率计的Verilog HDL语言实现院系名称:信息工程学院专业名称:通信工程(物联网工程)实验项目名称:EDA实验班级: 110711学号:。

报告人:冯剑波实验六 数字频率计的Verilog HDL 语言实现一、实验目的:1、掌握较复杂数字电路或系统的纯Verilog HDL 实现方法;2、体会纯Verilog HDL 语言输入设计与原理图输入设计的差别。

二、实验原理:【数字频率计是用来测量输入信号的频率并显示测量结果的系统。

一般基准时钟的高电平的持续时间为s T 10 ,若在这0T 内被测信号的周期数为N 则被测信号的频率就是N ,选择不同的0T ,可以得到不同的测量精度。

一般0T 越大,测量精度越高,但一次的测量时间及频率计所需的硬件资源也增加。

三、设计任务与要求:1、设计一个6位频率计,测量范围从1Hz 到99 99 99Hz ,测量结果用6个数码管显示,基准时钟频率为1Hz ;2、只显示测量结果,中间计数过程不显示;结果更新时间2秒一次;3、频率计只设一个复位键,按下该键(reset=0)系统复位,释放该键(reset=1)系统工作,测量并显示结果。

4、显示用静态方式;5、用Verilog HDL 实现上述要求的频率计。

四、设计源程序及注释与仿真结果设计源程序:module pinlvji(oHEX0,oHEX1,oHEX2,oHEX3,oHEX4,oHEX5,clk_50M,clk_1Hz,reset,signal_out); @input clk_50M,reset; //50MHz 时钟输入、复位output[6:0] oHEX0,oHEX1,oHEX2,oHEX3,oHEX4,oHEX5; //数码管0-5,分别显示个、十、百、千、万、十万位的数字output reg clk_1Hz;output reg signal_out; reg signal_in; reg[29:0] cnt;reg[29:0] cnt1; reg count_en; //计数允许,count_en=1时计数,下降沿到来时锁存reg load; reg[3:0] ge,shi,bai,qian,wan,shiwan; reg cout1,cout2,cout3,cout4,cout5;reg[3:0] q0,q1,q2,q3,q4,q5;wire clr; always @(posedge clk_50M) //改变Hz 的范围,自己设定的频率1Hz-999999Hzbegincnt1=cnt1+1;if(cnt1<=25_000_0) begin signal_out=0;signal_in=0;endelse if(cnt1==50_000_0) cnt1=0;【else begin signal_out=1;signal_in=0;endendalways @(posedge clk_50M) //50M分频产生1Hz时钟begincnt=cnt+1;if(cnt<=25_000_000) clk_1Hz=0;else if(cnt==50_000_000) cnt=0;else clk_1Hz=1;end/*被测信号signal_in作为个位的输入,,signal_in上升沿到来时ge位+1;进位输出是cout1,作为十位的输入*/always @(posedge signal_out or posedge reset or posedge clr)~begin if(reset) ge=0;else if(clr) ge=0;else begin if(count_en) begin if(ge==9) begin ge=0;cout1=1;endelse begin ge=ge+1;cout1=0;endendendend/*cout1作为十位的输入,cout1上升沿到来时shi位+1;进位输出是cout2,作为百位的输入*/always @(posedge cout1 or posedge reset or posedge clr)begin if(reset) shi=0;else if(clr) shi=0;¥else begin if(count_en) begin if(shi==9) begin shi=0;cout2=1;endelse begin shi=shi+1;cout2=0;endendendend/*cout2作为百位的输入,cout2上升沿到来时bai位+1;进位输出是cout3,作为千位的输入*/always @(posedge cout2 or posedge reset or posedge clr)begin if(reset) bai=0;else if(clr) bai=0;else begin if(count_en) begin if(bai==9) begin bai=0;cout3=1;endelse begin bai=bai+1;cout3=0;end…endendend/*cout3作为千位的输入,cout3上升沿到来时qian位+1;进位输出是cout4,作为万位的输入*/ always @(posedge cout3 or posedge reset or posedge clr)begin if(reset) qian=0;else if(clr) qian=0;else begin if(count_en) begin if(qian==9) begin qian=0;cout4=1;endelse begin qian=qian+1;cout4=0;endendend;endalways @(posedge cout4 or posedge reset or posedge clr)begin if(reset) wan=0;else if(clr) wan=0;else begin if(count_en) begin if(wan==9) begin wan=0;cout5=1;endelse begin wan=wan+1;cout5=0;endendendendalways @(posedge cout5 or posedge reset or posedge clr)begin if(reset) shiwan=0;<else if(clr) shiwan=0;else begin if(count_en) begin if(bai==9) begin shiwan=9;endelse begin shiwan=shiwan+1;endendendend/*****count_en=1时计数,count_en=0不允许计数********/always @(posedge clk_1Hz or posedge reset)begin if(reset) begin count_en=0;endelse begin count_en=~count_en;load=~count_en;endend//*****count_en下降沿到来时锁存数据****/ always @(negedge count_en)begin q0=ge; q1=shi;q2=bai; q3=qian;q4=wan; q5=shiwan;endassign clr=~clk_1Hz&load;/****调用数码管显示*****/led7s u0(q0,oHEX0);led7s u1(q1,oHEX1);led7s u2(q2,oHEX2);]led7s u3(q3,oHEX3);led7s u4(q4,oHEX4);led7s u5(q5,oHEX5);endmodulemodule led7s(datain,ledout);input[3:0] datain; output reg[6:0] ledout; always begin case(datain)0: ledout<=7'b1000000;1: ledout<=7'b1111001;2: ledout<=7'b0100100;3: ledout<=7'b0110000;)4: ledout<=7'b0011001;5: ledout<=7'b0010010;6: ledout<=7'b0000010;7: ledout<=7'b1111000;8: ledout<=7'b0000000;9: ledout<=7'b0010000;default:ledout<=7'b1000000;endcase endendmodule仿真波型:·五、心得体会虽然我以前上了Verilog HDL语言,但是这都实习中还是碰到了一些问题,通过向老师,向同学寻求帮助和在网上,在图书馆查找相关的资料来一点点解决遇到的问题,从中感觉自己对VHDL语言的理解又进了一步!对硬件描述语言和纯元件语言,如c语言之间的差别又有了更深一层次的理解,不过自我感觉想要对VHDL 语言要很熟练的掌握的话,还需要多多的联系才行的。

Verilog计数分频

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如赛灵思(Xilinx)的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

因此很多招聘单位在招聘时往往要求应聘者写一个分频器(比如奇数分频)以考核应聘人员的设计水平和理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

电路上只需一个D触发器和一个非门即可实现,Q(n+1)=D,D=~Q(n),clk_out=Q(n+1) .第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:占空比为非50%的三分频时钟,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

module three(clk_in,rst,clk_out);input clk_in,rst;output clk_out;reg clk_out;reg [1:0] count;always @(negedge rst or posedge clk_in)beginif(rst==0)begincount<=0;clk_out<=0;endelsebegincount<=count+1;if(count==1)clk_out<=~clk_out;else if(count==2)beginclk_out=~clk_out;count<=0;endendendendmodule另一种实现:module div3(CLKIN,CLKOUT,RESETn);input CLKIN,RESETn;output CLKOUT;wire d;reg q1,q2;wire CLKOUT;always @(negedge RESETn or posedge CLKIN)beginif (RESETn==1'b0)q1<=1'b0;elseq1<=d; //q1是d延迟一个时钟后的信号endalways @(negedge RESETn or posedge CLKIN)beginif (RESETn==1'b0)q2<=1'b0;elseq2<=q1; //q2是q1延迟一个时钟后的信号endassign d=~q1 & ~q2; //d在一个周期内,一个clk为高,另外两个clk为低assign CLKOUT=q2;endmodule电路中,利用两个D触发器和简单的门电路即可实现。

verilog 实现小数分频(小数分频器)代码

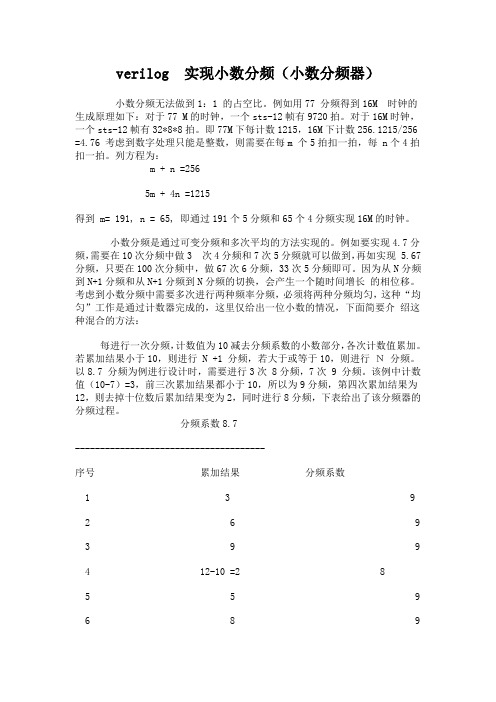

verilog 实现小数分频(小数分频器)小数分频无法做到1:1 的占空比。

例如用77 分频得到16M 时钟的生成原理如下:对于77 M的时钟,一个sts-12帧有9720拍。

对于16M时钟,一个sts-12帧有32*8*8拍。

即77M下每计数1215,16M下计数256.1215/256 =4.76 考虑到数字处理只能是整数,则需要在每m 个5拍扣一拍,每 n个4拍扣一拍。

列方程为:m + n =2565m + 4n =1215得到 m= 191, n = 65, 即通过191个5分频和65个4分频实现16M的时钟。

小数分频是通过可变分频和多次平均的方法实现的。

例如要实现4.7分频,需要在10次分频中做3 次4分频和7次5分频就可以做到,再如实现 5.67分频,只要在100次分频中,做67次6分频,33次5分频即可。

因为从N分频到N+1分频和从N+1分频到N分频的切换,会产生一个随时间增长的相位移。

考虑到小数分频中需要多次进行两种频率分频,必须将两种分频均匀,这种“均匀”工作是通过计数器完成的,这里仅给出一位小数的情况,下面简要介绍这种混合的方法:每进行一次分频,计数值为10减去分频系数的小数部分,各次计数值累加。

若累加结果小于10,则进行 N +1 分频,若大于或等于10,则进行N分频。

以8.7 分频为例进行设计时,需要进行3次 8分频,7次 9 分频。

该例中计数值(10-7)=3,前三次累加结果都小于10,所以为9分频,第四次累加结果为12,则去掉十位数后累加结果变为2,同时进行8分频,下表给出了该分频器的分频过程。

分频系数8.7--------------------------------------序号累加结果分频系数1 3 92 6 93 9 94 12-10 =2 85 5 96 8 97 11-10 =1 88 4 99 7 910 10 8 以下是代码模块://top modulemodule fd89bits( clkin,reset,a,clkout);input clkin;input reset;input a;output reg clkout;wire clkout1,clkout2;fd8bits dut1(clkin,reset,clkout1);fd9bits dut2(clkin,reset,clkout2);always@(posedge clkin) beginif(a)clkout <= clkout1;elseclkout <= clkout2;endendmodule`timescale 1ns / 1psmodule fd8bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 7)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// 9 分频module fd9bits(clk_in,reset,clk_out );input clk_in;input reset;output reg clk_out;reg[3:0] count;always@(posedge clk_in) beginif(!reset)count <= 0;else beginif(count < 8)count <= count + 1;elsecount <= 0;endclk_out <= count[2];endendmodule// testbenchmodule testbench();reg clk_in;reg reset;reg a;wire clk_out;fd89bits dut(clk_in,reset,a,clk_out);initial beginclk_in= 0;reset = 0;#11;reset = 1;forever begina = 1;#60;a = 0;#20;a = 1;#40;a = 0;#20;a = 1;#40;a = 0;#20;endendalways #10 clk_in = ~clk_in; endmodule//result。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

第二个实验:1、打开QuartusII,新建一个工程couter10yjq2、新建一个Verilog HDL文件输入文件couter10yjq.v3、输入程序module couter10 (CLK,CLR,C,Q);input CLK,CLR;output C;output[3:0] Q;reg C=0;reg[3:0]Q=0;always@(posedge CLK )beginif (CLR==1)beginQ<=0;C<=0;endelsebeginQ<=Q+1;endif(Q==9)beginC<=~C;Q<=0;endendendmodule4、设置顶层文件(点settings>general >下拉选couter10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与题意相符,故仿真正确。

第三个实验1、打开QuartusII,新建一个工程couter8yjq2、新建一个Verilog HDL文件输入文件couter8yjq.v3、输入程序module couter8 (CLK,CLR,UPDOWN,C,Q);input CLK,CLR,UPDOWN;output C;output[7:0]Q;reg C;reg[7:0]Q;always@(posedge CLK)beginif (CLR==0)beginC<=0;Q<=0;endelse if (UPDOWN==1)beginif (Q=='b1111111)beginQ<=0;C<=~C;endelse Q<=Q+1;endelsebeginif (Q=='b0000000)beginQ<='b1111111;C<=~C;endelse Q<=Q-1;endendendmodule4、设置顶层文件(点settings>general >下拉选couter8)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真总结:仿真结果与题意相符,故仿真正确。

第四个实验1、打开QuartusII,新建一个工程mcout5yjq2、新建一个Verilog HDL文件输入文件mcout5yjq.v3、输入程序module mcout5 (M1,M0,CLK,out,c,CLR); input M1,M0,CLK,CLR;output c;output[5:0]out;reg c;reg[5:0]M;reg[5:0]N;reg[5:0]out;always@(posedge CLK or posedge CLR) beginif (CLR)beginout<=0;N<=0;endelsebeginN<=M;case({M1,M0})'b00:M<=18;'b01:M<=4;'b10:M<=12;'b11:M<=6;endcaseif(N==M)beginif(out==M)beginout<=0;c<=~c;endelsebeginout<=out+1;endendelsebeginout<=0;c<=0;endendendendmodule4、设置顶层文件(点settings>general >下拉选mcout5)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真总结:仿真结果与题意相符,故仿真正确。

第五个实验1、打开QuartusII,新建一个工程counter2_10yjq2、新建一个Verilog HDL文件输入文件counter2_10yjq.v3、输入程序module counter2_10 (clk,clr,ena,cout,ql,qh);input clk,clr,ena;output cout;output[3:0] ql,qh;reg[3:0]qh,ql;reg cout;always @(posedge clk or posedge clr)beginif(clr)beginqh<=0;ql<=0;cout<=0;endelse if(ena)beginql<=ql+1;if(ql=='b1010)beginql<=0;qh<=qh+1;if(qh=='b1010)beginqh<=0;cout<=~cout;endendendendendmodule4、设置顶层文件(点settings>general >下拉选counter2_10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真总结:仿真结果与题意相符,故仿真正确。