使用fpga设计的电路原理图路

FPGA概述PPT课件

6.底层内嵌功能单元 内嵌专用硬核是相对于底层嵌入的软核而言 的,硬核(Hard Core)使FPGA具有强大 的处理能力,等效于ASIC电路。

•12

1.3 IP核简介

IP(Intelligent Property)核

是具有知识产权的集成电路芯核总称,是 经过反复验证过的、具有特定功能的宏模 块,与芯片制造工艺无关,可以移植到不 同的半导体工艺中。

通道绑定原 理示意图

•28

5.预加重技术 在印制的电路板上,线路是呈现低通滤波 器的频率特性的,为解决高频部分的损失, 就要采取预加重技术。

预加重技术的思想是:在传输信号时,抬高 信号的高频信号,以补偿线路上高频分量的 损失。

•29

没有预加重 的发送波形

•30

预加重后的 发送波形

没有预加重 的接收波形

典型的IOB内部结构示意图

2.可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元 .

CLB的实际数量和特性会依据器件的不同而不同,但是每 个CLB都包含一个可配置开关矩阵,此矩阵由选型电路(多 路复用器等)、触发器和4或6个输入组成。

典型的CLB结 构示意图

3. 数字时钟管理模块(DCM)

目前FPGA中多使用4输入的LUT,所以每一 个LUT可以看成是一个有4位地址线的RAM。当用 户通过原理图或HDL语言描述一个逻辑电路以后, PLD/FPGA开发软件会自动计算逻辑电路的所有可 能结果,并把真值表(即结果)写入RAM,这样,每 输入一个信号进行逻辑运算就等于输入一个地址去 进行查表,找出地址对应的内容,然后输出即可。

DLL简单模 型示意图

Xilinx DLL的典 型模型示意图

在FPGA设计中,消除时钟的传输延迟,实现高扇出 最简单的方法就是用DLL,把CLK0与CLKFB相连 即可。 利用一个DLL可以 实现2倍频输出

基于原理图的十进制计数器的设计(FPGA)

实验一:基于原理图的十进制计数器设计一、 实验目的:1. 熟悉和掌握ISE Foudation 软件的使用;2. 掌握基于原理图进行FPGA 设计开发的全流程;3. 理解和掌握“自底向上”的层次化设计方法;4. 温习数字电路设计的基础知识。

二、 实验原理:完成一个具有数显输出的十进制计数器设计,原理图如图2.1所示。

图2.1 十进制计数器原理图本实验为完成设计,采用了自底向上的设计流程。

自底向上设计是一种设计程序的过程和方法,是在设计具有层次结构的大型程序时,先设计一些较下层的程序,即去解决问题的各个不同的小部分,然后把这些部分组合成为完整的程序。

自底向上设计是从底层(具体部件)开始的,实际中无论是取用已有模块还是自行设计电路,其设计成本和开发周期都优于自顶向下法;但由于设计是从最底层开始的,所以难以保证总体设计的最佳性,例如电路结构不优化、能够共用的器件没有共用。

在现代许多设计中,是混合使用自顶向下法和自顶向上法的,因为混合应用可能会取得更好的设计效果。

一般来说,自顶向下设计方法适用于设计各种规模的数字系统,而自底向上的设计方法则更适用于设计小型数字系统。

十进制计数器七段数码管显示译码器使能控制端时钟端 异步清零端FPGA1、七段数码管译码器的设计七段数码管属于数码管的一种,是由7段二极管组成。

按发光二极管单元衔接方式分为共阳极数码管和共阴极数码管。

本实验使用共阴数码管。

它是指将一切发光二极管的阴极接到一同构成公共阴极(COM)的数码管。

共阴数码管在应用时应将公共极COM接到地线GND上,当某一字段发光二极管的阳极为高电平相应字段就点亮,当某一字段的阳极为低电平相应字段就不亮。

显示译码器,一般是将一种编码译成十进制码或特定的编码,并通过显示器件将译码器的状态显示出来。

根据显示的要求,可以得到七段显示译码器产生的各段LED输出与输入的二进制对应关系:表2.1七段字符显示真值表最小项译码器输出能产生输入变量的所有最小项,而任何一个组合逻辑函数都可以变换为最小项之和的标准形式,故采用译码器和门电路可实现任何单输出或多输出的组合逻辑函数。

基于FPGA的serdes电路之comma和PRBS检测电路设计说明书

基于FPGA的Serdes接口电路设计Comma和PRBS检测方案(仅供内部使用)拟制:谭宇日期:2013/09/13审核:姚亚峰日期:内部资料请勿外传修订记录日期修订版本描述作者2012/09/13 1.00初稿完成谭宇目录1.Serdes接口电路整体结构图 (3)2.概述 (5)2.1.文档版本 (5)2.2.相关标准 (5)2.3.开发环境 (5)3.Serdes接口电路选型 (5)3.1.Serdes芯片架构选型 (5)3.2.Serdes主要性能指标 (7)ma检测电路原理和实现 (7)ma检测电路原理 (7)ma的设计思路 (8)5.PRBS电路原理和实现 (9)5.1.PRBS电路原理 (9)5.2.PRBS电路实现过程 (10)6.说明 (10)Comma和PRBS检测电路设计说明书关键词:Serdes接口电路设计摘要:随着电子行业技术的发展,特别是在传输接口的发展上,原本用于光纤通信的Serdes 技术成为了为高速串行接口的主流。

它是一种时分多路复用(TDM)、点对点(P2P)的串行通信技术。

即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

这种点对点的串行通信技术充分利用传输媒体的信道容量,减少所需的传输信道和器件引脚数目,从而大大降低通信成本。

安华高,博通,飞兆等国外半导体公司均已推出基于独立的Serdes 芯片,而国内目前还基本处于预研阶段。

本文就以基于FPGA的Serdes芯片IP core中Comma和PRBS检测电路部分做详细的介绍和说明。

缩略语清单:Serdes Serializer/Deserializer串行器/解串器PRBS Pseudo-Random Binary Sequence伪随机二进制序列1.Serdes接口电路整体结构图图1.Serdes接口电路整体结构图Serdes接口电路为一个全双工电路,同时又具有点对点的高效传输。

基于FPGA的高速数据采集系统的电路设计

* 收稿 日期 : O O 0 2 2 1 一1 — 6

作 者 简 介 : 建秋 (9 8 , , 东 昌 邑人 , 坊职 业 学 院汽 车 工 程 系讲 师 。 王 16 一) 男 山 潍

一

1 — 6

第 4期

王 建 秋 : 于 F GA 的 高 速数 据 采 集 系统 的 电路 设 计 基 P

通过 对两个 S AM 的交叉 时序法 的控 制 , DR 来达 到对 两个 S RAM“ D 同时” 行数 据 的存储 , 而提 高 了原 进 进 有单 个 的 S RAM 数据 存储 速率 , AD 经理 论 上 的 分析 其 系统 的 存储 速 率 达 到 单个 的 S DR A AM 数 据存 储

来描 述其 内部 逻辑 电路 , 于修 改和 升 级 。如 果 在 高速 数 据 采 集 系统 中采 用 F G 控 制 器 , 会 极 大地 便 P A 将

提 高 系统的稳 定性与 可靠性 。本文设 计 了一 个基 于 F GA 的 高速 数据 采 集 系统 , 其硬 件 电路 部分 进行 P 对

同 , 而保 证 了输 入 时 钟 和 F G 时 钟 以及 S R 从 PA D AM 时 钟 之 间 的零 延 迟 ; P C Q 0C E 2 8 2 8 7具 有 8 5 26个 L s3 个 RAM lcs158 AM i ,8个 内嵌 的乘法 器 , 个 P L 最 大可 使用 12个 IO 口, e,6 bok ,68 8R bt 1 s 2 L , 8 / 多种

C co eI 件 的密度 范 围从 4 0 E和 1 9 0 i R y ln 器 I 6 8L 1 8 8bt AM , 6 4 6 E和 l 5 0 0 i AM 。C c n 器 到 81 L 1 2 0 bt R y l eI o I

基于FPGA的简单音乐电路设计方案

基于FPGA的简单音乐电路设计方案工作任务的陈述与背景一、工作任务的陈述使用层次化设计方法,设计并用FPGA实现一个能循环播放乐曲的音乐电路。

二、工作任务的背景据有关媒体介绍,中国的第一颗人造卫星东方红一号卫星,于1965年开始研制,1970年4月24日进入太空轨道,该星重量超过了苏、美、法、日等前4个国家第一颗卫星重量的总和,在某些技术方面超过上述4个国家第一颗卫星的水平,开创了中国航天史的新纪元。

东方红一号重173公斤,设计寿命为14天,实际寿命达到20天,1970年5月14日停止发送信号。

关键技术包括《东方红》乐音装置、短波天线遥测系统等4项。

其中电子乐音发生器是全星的核心部分,它通过20兆赫兹短波发射系统反复向地面播送“东方红”乐曲的前八小节,全中国人民乃至全世界的人民通过收音机都能听得到。

完成研制东方红乐音装置任务的是中国科学院自动化所的一个小组。

他们首先考虑,用什么样的方法来模拟出“东方红”乐曲。

当时有三种方案提上了台面,一种是八音盒方案,它采用机械齿轮播放音乐;另一种就是把音乐录在磁带机上,但是当时中国还没有小磁带机,都是笨重的大磁带机,不可能装上卫星升空;因此第三种方案自然就是电子音乐,这也是后来被广泛接受的一种方案。

根据上级要求,只需让卫星播放《东方红》前八个小节的旋律。

小组决定在四十秒内连续播放两遍这八个小节,然后发射机就切换成遥测信号,用一个发射机就可以实现交替传送乐曲和遥测信号的目的。

这是国内早期最知名,影响最大的一个音乐电路。

在国内缺乏集成电路,没有微处理器的那个时代,东方红乐音装置全部用晶体管分立元件做成。

有人粗略统计,整个乐音装置全部共用了110多个晶体三极管(绝大多数是3DG6),大约150个二极管(都是2AP10),其他都是电阻电容。

现在,音乐电路广泛用于自动答录装置、手机铃声、集团电话及智能仪器仪表设备中。

作为一个电子系统的一个模块,音乐电路的实现方法有以下几种: (1)购买专用音乐电路片。

基于FPGA的自动调焦电路设计与实现(含PCB图)--毕业设计

h哈尔滨工程大学本科生毕业论文基于FPGA的自动调焦电路设计与实现院(系):信息与通信工程学院专业:电子信息工程学号:学生姓名:指导教师:副教授2009年6月hh摘要随着超大规模集成电路的发展以及现代光学仪器设备在智能化、简便化方面的突破,令数字光学设备迅速普及。

数字信号处理理论的成熟与发展使得基于数字信号处理方式的自动调焦成为可能。

本设计使用FPGA作为数字信号处理与系统控制的核心器件。

将由摄像头输入的模拟电视信号转换为数字电视信号;经过FPGA处理后再将其转换为模拟电视信号输出,并由电视机显示;同时FPGA控制电机的进退实现自动调焦。

系统硬件部分以FPGA为核心,搭载输入视频处理器SAA7111AHZ与数字视频编码器SAA7120以及RAM等其他附属电路。

系统软件部分使用I2C总线实现对输入视频处理器和数字视频编码器的初始化,实现PAL制式模拟电视信号-YUV 数字电视信号-PAL制式模拟电视信号的转换,并使用电视机将其输出。

根据复合视频图像信号的相关原理,对输入视频的中心区域进行灰度熵值的运算,并控制电机的转动方向以阈值法实现自动调焦。

在本设计中,完成了相关的软件和硬件设计,并经过调试后,能够实现较好效果的自动调焦。

关键词:FPGA;灰度熵;输入视频处理器;数字视频编码器hhABSTRACTThe digtal optical equipments become popular,with the development of very-large-scale integrated circuits and the major breakthrough of the modern optical equipments in intelligentizating and facilitating process. The automatic focusing which based on digital signal processing can be realized.In this desgin, FPGA is the key component of digital signal processing and system control.Firstly, an analog TV signal captured by the camera is transformed to a digital TV signal; and then the digtal TV signal is processed by FPGA and finally it is transformed to an analog TV signal output; at the same time, the automatic focusing is realized by the motor controled by FPGA.In the hardware part of the system,FPGA is used as the key component,with accessory circuit such as video input processor, digital video encoder and so on.In the software part, the video input processor and digital video encoder is initialized throgh the I2C bus in order to realize the interconversion of PAL standard analog TV signals and YUV digital TV signals ,which are the output of monitor. According to the theory of composite video signal,the system selects the center part of the input video and calculates its gray region entropy , then control the motor rotation to realize automatic focusing using the thresholding method.hhIn this design, the relevant software and hardware are completed, and can bring automatic focusing into effect well after testing .Key words:FPGA;Gray entropy; Video Input Processor; Digital Video Encoder目hhh 录第1章绪论 (1)1.1 课题背景和意义 (1)1.2 国内外研究现状 (2)1.2.1 概述 (2)1.2.2 国外研究现状 (3)1.2.3 国内研究现状 (4)1.3 主要研究内容 (5)第2章自动调焦系统相关理论 (6)2.1 复合视频图像信号 (6)2.1.1 电视扫描原理 (6)2.1.2 复合视频图像信号的组成 (6)2.1.3 复合视频图像信号主要制式 (8)2.2 I2C总线 (9)2.2.1 概述 (9)2.2.2 I2C总线的主要特点 (10)2.2.3 I2C总线的工作状态及时序 (11)2.3 自动调焦的几种主要方法 (13)2.3.1 测距方法 (13)2.3.2 聚焦检测方法 (14)2.4 基于灰度熵值法的自动调焦算法 (15)2.4.1 灰度熵值提取算法 (15)2.4.2 阈值判断算法 (15)2.5 本章小结 (16)第3章自动调焦系统的硬件设计 (17)3.1 总体方案 (17)3.2 FPGA最小系统 (18)h3.2.1 芯片简介 (18)3.2.2 FPGA的配置 (20)3.3 视频输入处理器及系统 (22)3.3.1 SAA7111AHZ芯片简介 (22)3.3.2 SAA7111AHZ的应用电路 (23)3.4 视频输出处理器及系统 (25)3.4.1 SAA7120芯片简介 (25)3.4.2 SAA7120的应用电路 (26)3.5 其他电路设计 (27)3.5.1 电源电路 (28)3.5.2 外置RAM电路 (28)3.5.3 串口电路 (28)3.5.4 LED指示灯电路 (29)3.6 电路系统的PCB设计 (29)3.7 本章小结 (30)第4章自动调焦系统程序设计 (32)4.1 编程环境 (32)4.1.1 VHDL硬件描述语言特点 (32)4.1.2 VHDL的设计流程 (33)4.1.3 编译环境QuartusII的设计特点 (34)4.1.4 QuartusII开发软件的设计流程 (35)4.2 软件设计总体流程 (36)4.3 视频转换芯片的初始化 (36)4.3.1 I2C总线设计 (37)4.3.2 视频转换芯片的初始化寄存器设置 (37)4.4 自动调焦算法的编程实现 (41)4.5 本章小结 (44)hh第5章系统仿真、调试与性能分析 (45)5.1 系统仿真结果 (45)5.2 系统调试 (46)5.3 系统性能分析 (49)5.4 本章小结 (49)结论 (51)参考文献 (52)致谢 (55)hh第1章绪论1.1课题背景和意义自动调焦,又称为自动对焦、自动聚焦。

FPGA轻松学习用QuartusII通过原理图完成与门电路设计

FPGA轻松学习用QuartusII通过原理图完成与门电路设计打开QuartusII软件,程序主界面如下:1,新建一个工程点击File——>New Project Wizard,打开创建新工程向导,这里你将完成工程的基本设定选项。

1,Project name and directory——工程的名称与目录2,Name of the top-level design entity——顶层设计实体的名称3,Project files and libraries——项目文件与库4,Target device family and device——目标设备的族类5,EDA tool settings——EDA工具设定这里一般设定好工程名称和目录,顶层设计实体名称以及目标设备族类就可以了,其他的暂时直接使用默认项就可以了。

2,新建一个设计文件通过点击File——>New打开新建文件选择框,由于我们这里使用原理图描述实现的,则文件类型选择Design Files——>Block Diagram/Schematic File,就新建了一个原理图文件,将其保存起来,注意命名要跟前面设置的顶层设计实体名称相同。

3,编写设计文件接下来开始在文件中绘制原理图,这里首先完成与门的添加,点击左侧工具栏中的Symbol Tool按钮,打开Symbol选择框,选择primitives——>logic——>and2,点击OK后即可在原理图中添加一个2输入的与门了。

在同样通过Symbol Tool中的加入和primitives——>pin——>output加入输入和输出引脚,然后在原理图中把他们用Orthogonal Node Tool即导线连接起来,双击输入输出引脚,为他们设定好名字,pinA,pinB,pinC,就完成了原理图中的设计。

4,编译(分析综合)点击Processing——>Start——>Start Analysis & Synthesis,进行分析综合,就好像是对程序进行编译,等待片刻,如果没有错误,编译报告会输出出来。

基于FPGA的数字频率计

2.3 方案选择

3单元模块电路设计

3.1电路设计总体框图

本设计主要由8个部分组成,以CPLD芯片部分为核心展开,待测信号输入,由外部电源,复位电路,单片机电路,液晶显示,标准时钟以及JTAG下载各个单元配合起来实现测试频率并在液晶显示屏上实时显示出数字频率信号。

图3.1 电路设计总体框图

3.2标准时钟(100MHz)产生部分

3.7电源部分

CPLD芯片工作电压在3.3V,单片机工作电压为5V。所以,在要求进行电压转换时,用到芯片LM1117进行5V电压到3.3V电压。

3.8单片机部分

3.8.1STC12_LQFP芯片介绍

如图3.8.1所示,STC12系列单片机为增强型8051芯片,1T,单时钟/机器周期,指令代码完全兼容传统8051单片机。通用I/O口(27/23/15个),复位后为:准双向口/弱上拉(普通8051传统I/O口)可设置成四种模式:准双向口/弱上拉,推挽/强上拉,仅为输入/高阻,开漏每个I/O口驱动能力均可达到20mA,但整个芯片最大不得超过55mA。ISP(在系统可编程)/IAP(在应用可编程),无需专用编程器,无需专用仿真器可通过串口(P3.0/P3.1)直接下载用户程序,数秒即可完成一片,EEPROM功能,看门狗定时器内部集成MAX810 专用复位电路(外部晶体20M 以下时,可省外部复位电路)。时钟源:外部高精度晶体/ 时钟,内部R/C 振荡器

表2-1显示了每个设备的行和列数,以及行和列毗邻地区的快闪记忆体数量的EPM570,EPM1270和EPM2210器件。长排满行延长从一排I/ O块到其他。简短的行毗邻超滤膜块,其长度是在列的宽度显示。

每一个LAB包括驱动控制信号LES的专用逻辑。控制信号包括两个时钟,两个时钟使能,两个异步清除,1同步清除,异步预置/负载,同步载荷,加/减控制信号,提供了一次10个控制信号最大。虽然同步负载和清除的信号通常用于执行时计数,也可以用于其他功能。

FPGA芯片中的交叉开关设计

FPGA芯片中的交叉开关设计李兴政1,2,杨海钢1(1.中国科学院电子学研究所传感技术国家重点实验室,北京100080;2.中国科学院研究生院,北京100039)摘要:作为一种可重复使用的器件,现场可编程门阵列(FPGA)受到越来越多的关注,它以面积为代价换取使用的灵活性。

在FPGA芯片的设计中,通过分析交叉开关结构的特点,将传输管逻辑应用于其中。

采用这种传输管结构的交叉开关,大大降低了芯片实现所需的晶体管数目,减小了芯片的版图面积,从而提高了FPGA芯片的面积效能。

关键词:现场可编程门阵列;交叉开关;传输管逻辑;晶体管;面积效能中图分类号:T P331.2文献标识码:A文章编号:100423365(2007)0420606204Design of Intercross Switch in FPGA ChipLI Xing2zheng1,2,YANG H ai2gang1(1.State Key Lab of Tr ansdu cer T echnolog y,Institute of Electronics,T he Chinese Academ y of Sciences,Beijing100080;2.Gr adu ate Sch ool,Th e Chinese Aca demy of Sciences,Beijing100039,P.R.China)Abstr act:T he cha racteristics of FP GA.s intercross swit ch st ruct ur e were analyzed,to which pass2tr ansistor log2 ic was applied.The proposed pass2tr ansistor intercross swit ch circuit r educed the number of tr ansistors,and so it occupies smaller chip area.By using this cir cuit,the area efficiency of FP GA chip was improved.Key words:F PGA;Inter cross switch;Pass2transistor logic;Tr ansistor;Area efficiencyEEACC:12651引言现场可编程门阵列(Field Progr ammable Gate Array,FPGA)是美国Xilinx公司于1984年开发的一种通用型用户可编程器件(Programmable Logic Device,PLD)。

基于FPGA的可调谐激光器控制电路设计

控制技术・ 120 ・计算 机测 量与控制 2021 29(4)Computer Measurement & Control文章编号 1671 - 4598(2021)04 - 0120 -06 DOI :10.16526/ki.11 — 4762/tp.2021. 04.024 中图分类号:TN248文献标识码:A基于FPGA 的可调谐激光器控制电路设计孔市委,任乾钰,王军,贾平岗(中北大学电子测试技术重点实验室,太原030051)摘要:可调谐激光器是光纤光栅解调系统中最主要的部件之一,其输出波长和功率的稳定性影响整个解调系统的性能;文中 对MG —Y 可调谐激光器的调谐原理进行了分析,设计了一种基于FPGA 的可调谐激光器控制电路;使用温度控制芯片ADN8834对MG —Y 激光器进行温度控制,通过改变电流源的输出电流,控制激光器的输出波长;利用光谱分析仪采集激光器的输出波长,并对激光器的输出波长进行标定,制作“波长一电流”查询表;FPGA 通过调用“波长一电流”查询表,实现激光器的波长在1 527〜1 567 nm 范围内以20 pm 间隔连续线性扫描。

同时搭建光纤布拉格光栅解调系统,验证了可调谐激光器解调 光纤光栅中心波长的可行性。

关键词:MG —Y 激光器;波长控制;温度控制;“波长一电流”查询表Design of Tunable Laser Control Circuit Based on FPGAKong Shiwii , Ren Qianyu , Wang Jun , Jia Pinggang(Science and Technology on Electronic Test & Measurement Laboratory ,North University of China , Taiyuan 030051, China )Abstract : Tunable laser is one of the most important components in the fiber Bragg grating demodulation system. The stability ofits output wavelength and power affects the performance of the whole demodulation system. In this paper , the tuning principle of MG —Ytunablelaserisanalyzed , andatunablelasercontrolcircuitbasedonFPGAisdesigned Thecircuitusesatemperaturecontrol chipADN8834tocontrolthetemperatureofthe MG —Ylaser , andcontrolsoutputwavelengthofthelaserbychangingtheoutputcurrent of the current source. The output wavelength of the laser is analyzed by spectrum analyzer , and the output wavelength of la ser is calibrated , and the wavelength 一 current query table is made. The wavelength of the laser can be scanned continuously in the range of 1527 〜1567 nm at the interval of 20 pm by FPGA calling the wavelength 一current query table. At the same time , a fiberBragg grating demodulation system was built to verify the feasibility of the tunable laser to demodulate the center wavelength of the f — bergratingKeywords : Mg 一 Y laser ; wavelength control ; temperature control ; "wavelength —current" query table0引言随着光纤传感技术的迅速发展及其在各工程领域的广 泛应用3],光纤传感在全球范围内得到了大量的关注,在工程应用、学术研究等方面吸引着许多专家学者34]。

FPGA现代数字系统设计1

I/O I/O

Flash

I/O

SDRAM

FPGA

CPU CPU DSP

DSP

集成化设计发展趋势

5.动态可重构方向发展

动态重构是指能在运行过程中实时配置的可重构。 对于时序变化的数字逻辑系统,其时序逻辑的发 生不是通过调用芯片内不同区域、不同逻辑资源 组合而成的,而是通过对具有专门缓存逻辑资源 的FPGA进行局部或全局的芯片逻辑的动态重构 而快速实现的。 动态系统结构的FPGA具有缓存逻辑(Cache Logic),在外部逻辑的控制下,通过缓存逻辑 对芯片逻辑进行全局或局部的快速修改,通过有 控制重新布局布线的资源配置来加速实现系统的 动态重构

数字系统集成化的主要方法: 数字系统集成化的主要方法:

COMS反相器原理图与标准库

COMS反相器原理图

COMS反相器标准库(0.35)

数字系统集成化的主要方法: 数字系统集成化的主要方法:

基于标准单元库的数字集成电路版图

数字系统集成化的主要方法: 数字系统集成化的主要方法:

SOC设计 设计

SOC(system on chip)系统集成芯片; SOC是在ASIC的基础上发展起来的,与一般 ASIC相比,具有很多独特的优点,不再是功能 单一的单元电路,而是一个有某种应用目的的 单片电子系统 SOC是21世纪微电子技术领域在芯片级上的必 然发展方向就是集成电路(IC)向集成系统 (Integrated System),

状态机设计利用EDA软件,在可视化图形状态描述

中,生成需要的VHDL或Verilog语言。

数字系统集成化的主要方法: 数字系统集成化的主要方法:

IP模块使用采用设计好的模块进行系统搭建,快速

FPGA实验报告

实验报告课程名称: FPGA技术实验名称:用状态机实现序列检测器的设计姓名:学号:班级:指导教师:实验题目一、实验原理1、实验目的:用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。

2、实验内容:应用有限状态机设计思路,检测输入的串行数据是否是“010000”,本次实验由顶层文件、串行检测、并行数据转串行、数码管显示四个模块组成。

图3.1整体模块方块图3、序列检测器的原理说明:序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出A,否则输出b。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

例3-1描述的电路完成对特定的序列数"100101"的检测的部分HDL代码。

当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“A”,否则仍然输出“b”。

4、系统共包括4个模块:4.1、并行数据转串行数据模块(xulie.v)1)、输入端口:clk-----系统时钟,由按键K2通过消抖模块后提供。

din6-----6bits输入数据,需在时钟控制下,串行输出。

reset----系统复位信号,当reset=1’b1时,系统输出复位,否则系统正常工作。

2)、输出端口:din----------1bit输出信号3)、操作要求及功能描述:1、异步复位,在时钟控制下,将并行输入数据din6[5:0],按照din[5],din[4],din[3],din[2],din[1],din[0]的顺序输出至串行检测模块的输入端口din。

2、根据设计要求,先画出并行数据转串行数据模块的状态转移图,在此基础上写出HDL代码。

3、比较实验指导书提供并行数据转串行数据模块(xulie.v)的参考代码,总结有限状态机的HDL4.2、串行检测模块(schk.v)1)、输入信号:DIN-----1bit的串行输入数据CLK-----同步输入时钟CLR ------异步清零信号,当CLR=1,系统输出置0,否则,系统正常工作2)、输出信号:AB--------4bits数据,如果系统检测到6’b100101的串行输入,AB=4’b1010,否则,AB=4’b1011。

基于FPGA双路EnDat2.2编码器的接口设计

基于FPGA双路EnDat2.2编码器的接口设计孙大海;艾华【摘要】在数控系统中EnDat2.2接口协议因其高速率、高智能和高可靠性而得到广泛应用.针对数控系统对EnDat2.2协议的接口系统的需要和替代厂家昂贵接口板卡,分析了Endat2.2通信协议,采用FPGA开发了双路独立EnDat2.2译码模块,并集成了CRC校验功能,设计了双路绝对式编码器的数据传输电路,并在LC181光栅尺上进行了应用和测试.测试结果显示该电路可以快速准确地传输数据,证明了该接口电路的可行性.【期刊名称】《液晶与显示》【年(卷),期】2014(029)005【总页数】6页(P745-750)【关键词】EnDat2.2;FPGA;CRC;编码器【作者】孙大海;艾华【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春130033;中国科学院大学,北京100049;中国科学院长春光学精密机械与物理研究所,吉林长春130033【正文语种】中文【中图分类】TP394.1;TH691.91 引言光电编码器是一种光、机、电紧密结合的精密数字位移传感器,已经广泛应用于数控机床、回转台、伺服传动、机器人、雷达、军事目标测定等装置和设备中,并在工业、国防、航天等部门起着关键作用[1-2]。

光电编码器主要分为增量式和绝对式2种。

增量式编码器通过计数设备确定其位置,而绝对式编码器的每个机械位置对应于一个惟一的绝对编码,所以它无需记忆。

绝对式编码器在抗干扰和可靠性方面大大优于增量式编码器, 所以绝对式编码器在测量系统中的应用更广泛。

但是绝对式编码器每一次输出的数据量较增量式编码器多而复杂,由于精度高、位数多的特点决定绝对式编码器通信方式只能采取串行传输方式,而且还要遵循一定的通信协议。

目前世界上几大主要的编码器生产厂商都有自己的一套通信协议,如Heidenhain公司的EnDat协议,Danaher公司的Biss协议,SICK|STE- GMANN公司的HIPERACE协议等等[3]。

基于FPGA的数字电路实验报告

·4位累加器

1.设计方案

需要用两个模块,一个用来进行保存工作,即累加器,另一个用来实现数据相加,即加法器。这样即可每次把数据加到总和里,实现累加器的工作。

2.原理说明及框图

基本原理为书上的结构图。只要实现了两个主要模块,再用线网连接即可。

State1

0

0

State1

State10

State1

0

0

State10

Empty

State101

0

0

State101

State1010

State1

0

0

State1010

Empty

Empty

0

1

经过状态化简,上面状态已经为最简状态。

状态装换图:

在用HDL代码实现时,利用always块和case语句实现有限状态机。

答:用两个异或门,比较计数器的输出与一个加数的大小,若相等时则输出低电平到累加器的使能端,则可停止累加。

实验9序列检测器的设计

·实验目的

掌握利用有限状态机实现时序逻辑的方法。

1实验原理:

有限状态机(FSM)本质上是由寄存器和组合逻辑电路构成的时序电路。次态由当前状态和输入一起决定,状态之间的转移和变化总是在时钟沿进行。有限状态机分为Moore型和Mealy型。Moore型有限状态机输出仅由当前状态决定;Mealy型有限状态机输出由当前状态和输入同时决定。

·思考题

1.给出锁存器的定义,它与边沿触发器的区别是什么?

答:锁存器是一种对脉冲电平敏感的存储单元电路,它可以在特定输入脉冲电平作用下改变状态。边沿触发器只有在固定的时钟上升沿或者下降沿来临时改变状态。可以通过锁存器实现边沿触发器。

FPGA_原理图输入方法

图4-6 选择最后实现本项设计的目标器件

图4-7 对工程文件进行编译、综合和适配等操作

选择编译器

编译窗

消去Quartus适配操作

选择此项

消去这里的勾

完成编译!

步骤5:时序仿真

首先选择此项, 为仿真测试新 建一个文件

选择波形 编辑器文件

(1) 建立波形文件。

从SNF文件中 输入设计文件

的信号节点

图4-10 在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

(4) 设定仿真时间。

选择END TIME 调整仿真时间

区域。

图4-11 设定仿真时间

选择60微秒 比较合适

(5) 加上输入信号。

(6) 波形文件存盘。

用此键改变仿真 区域坐标到合适

位置。

点击‘1’,使拖黑 的电平为高电平

图4-30 测频时序控制电路

图4-31 测频时序控制电路工作波形

4.2.4 频率计顶层电路设计

图4-32 频率计顶层电路原理图(文件:ft_top.gdf)

图4-33 频率计工作时序波形

4.2.5 设计项目的其他信息和资源配置

(1) 了解设计项目的结构层次

图4-34 频率计ft_top项目的设计层次

(2) 计数器电路实现

图4-25 调出元件74390

图4-26 从Help中了解74390的详细功能

(3) 波形仿真

图4-27 两位十进制计数器工作波形

4.2.2 频率计主结构电路设计

图4-28 两位十进制频率计顶层设计原理图文件

图4-29 两位十进制频率计测频仿真波形

4.2.3 测频时序控制电路设计

4.3 参数可设置LPM兆功能块

FPGA原理图方式设计流程图

2 Quartus II软件的使用、开发板的使用本章将通过3个完整的例子,一步一步的手把手的方式完成设计。

完成这3个设计,并得到正确的结果,将会快速、有效的掌握在Altera QuartusII软件环境下进行FPGA设计与开发的方法、流程,并熟悉开发板的使用。

2.1 原理图方式设计3-8译码器一、设计目的1、通过设计一个3-8译码器,掌握祝组合逻辑电路设计的方法。

2、初步了解QuartusII采用原理图方式进行设计的流程。

3、初步掌握FPGA开发的流程以及基本的设计方法、基本的仿真分析方法。

二、设计原理三、设计容四、设计步骤1、建立工程文件1)双击桌面上的Quartus II的图标运行此软件。

开始界面2)选择File下拉菜单中的New Project Wizard,新建一个工程。

如图所示。

新建工程向导3)点击图中的next进入工作目录。

新建工程对话框4)第一个输入框为工程目录输入框,用来指定工程存放路径,建议可根据自己需要更改路径,若直接使用默认路径,可能造成默认目录下存放多个工程文件影响自己的设计,本步骤结束后系统会有提示(当然你可不必理会,不会出现错误的)。

第二个输入框为工程名称输入框。

第三个输入框为顶层实体名称输入框,一般情况下保证工程名称与顶层实体名称相同。

设定完成后点击next。

指定工程路径、名称5)设计中需要包含的其它设计文件,在此对话框中不做任何修改,直接点击next。

工程所需其它文件对话框6)在弹出的对话框中进行器件的选择。

在Device Family框中选用Cyclone II,然后在Available device框中选择EP2C35F484C8,点击next进入下一步。

器件选择界面7)下面的对话框提示可以勾选其它的第三方EDA设计、仿真的工具,暂时不作任何选择,在对话框中按默认选项,点击next。

第三方EDA工具选择8)出现新建工程以前所有的设定信息后,点击finish完成新建工程的建立。

基于Quartus II的电路设计过程图文详解

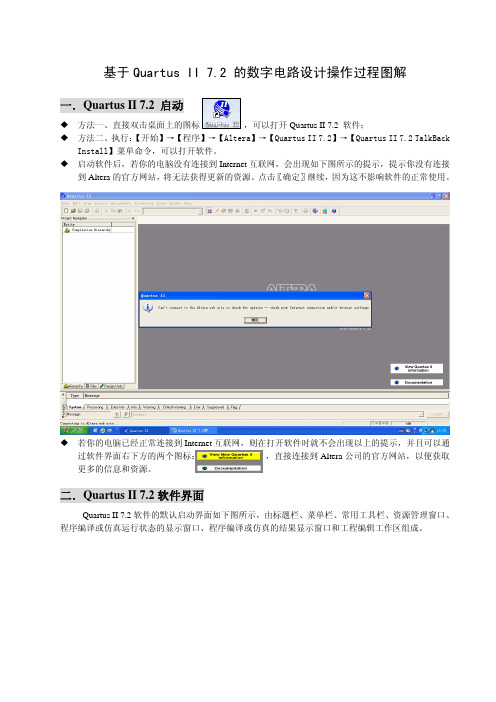

基于Quartus II 7.2 的数字电路设计操作过程图解一.Quartus II 7.2 启动方法一、直接双击桌面上的图标,可以打开Quartus II 7.2 软件;方法二、执行:【开始】→【程序】→【Altera】→【Quartus II 7.2】→【Quartus II 7.2 TalkBack Install】菜单命令,可以打开软件。

启动软件后,若你的电脑没有连接到Internet互联网,会出现如下图所示的提示,提示你没有连接到Altera的官方网站,将无法获得更新的资源。

点击〖确定〗继续,因为这不影响软件的正常使用。

若你的电脑已经正常连接到Internet互联网,则在打开软件时就不会出现以上的提示,并且可以通过软件界面右下方的两个图标:,直接连接到Altera公司的官方网站,以便获取更多的信息和资源。

二.Quartus II 7.2软件界面Quartus II 7.2软件的默认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、资源管理窗口、程序编译或仿真运行状态的显示窗口、程序编译或仿真的结果显示窗口和工程编辑工作区组成。

三.Quartus II 7.2软件使用1. 新建项目工程使用QuartusII7.2设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CPLD、FPGA)中。

因软件在完成整个设计、编译、仿真和下载等这些工作过程中,会有很多相关的文件产生,为了便于管理这些设计文件,我们在设计电路之前,先要建立一个项目工程(New Project),并设置好这个工程能正常工作的相关条件和环境。

建立工程的方法和步骤如下:(1)先建一个文件夹。

就在电脑本地硬盘找个地方注意:文件夹的命名及其保存的路径中不能有中文字符。

(2)再开始建立新项目工程,方法如右图点击:【File】菜单,选择下拉列表中的【New Project Wizard...】命令,打开建立新项目工程的向导对话框。