根据ADS的低噪放大器设计

ADS设计低噪声放大器的详细步骤课件PPT

ADS软件基本操作

01

创建新工程

通过菜单栏或工具栏选择“文件”->“新建”->“工程”,命名并选

择工程保存位置。

02 03

创建电路图

在工程浏览器中右键单击“Circuit Design”文件夹,选择“New”>“Circuit Design”,命名并选择保存位置。在电路图编辑器中绘制 电路图,使用元件库添加元件符号,并连接电路。

菜单栏包含文件、编辑、视图、仿真 等常用命令。

工具栏提供了常用命令的快捷方式, 方便用户快速执行操作。

工程浏览器用于管理工程文件和电路 元件,方便用户组织和查找相关资源。

电路图编辑器用于绘制和编辑电路图, 支持多种元件符号和连线方式。

仿真结果显示窗口用于显示仿真结果 和分析数据,支持多种图表和报告输 出。

03 低噪声放大器设计基础

低噪声放大器概述

01

低噪声放大器是一种电子器件, 用于放大微弱信号,通常用于接 收机前端,提高信号的信噪比。

02

低噪声放大器通常采用晶体管作 为放大元件,通过合理的设计和 匹配电路,实现低噪声、高线性 度和宽频带放大。

低噪声放大器设计原理

01

02

03

04

低噪声放大器设计主要关注噪 声系数、增益和线性度等性能

设置仿真参数

在仿真结果显示窗口中设置仿真参数,如仿真类型、扫描参数、收敛方 法等。

ADS软件基本操作

运行仿真

点击仿真结果显示窗口中的 “Simulate”按钮,开始运行仿真 。仿真完成后,结果将显示在仿真结 果显示窗口中。

分析仿真结果

可以使用仿真结果显示窗口中的图表 和报告工具对仿真结果进行分析和评 估。根据需要调整电路参数或重新进 行仿真,以达到最佳性能。

ADS设计低噪声放大器的详细步骤

由于sp模型本身已经对应于一个确定的直流工作 点,因此在做S参数扫描的时候无需加入直流偏 置。 观察sp模型晶体管的参数显示,在此例中,标定 的频率适用范围为0.1~5.1GHz,在仿真的时候要 注意。超出此范围,虽然软件可以根据插值等方 法外推除电路的特性,但是由于模型已经失效, 得到的数据通常是不可置信的。 在本例中,要在 控件中作相应的修改。

3.2晶体管S参数扫描-sp模型

点击 ,激活的是图 形显示方式,在左边所 列的参数列表中选择需 要的参数,如:S(1,1) 后,在点击 将其 加入右边的显示列表。

3.2晶体管S参数扫描-sp模型

然后会弹出数据显示 的格式,对于S(1,1), 选择dB。

3.2晶体管S参数扫描-sp模型

得到S(1,1)的显示如图所示

按照下图所示接入晶体管,连线按键为 ,注 意确认线完全接好,由于此晶体管发射极有两 个管脚,在此处接一个即可。

3.1晶体管直流工作点扫描

按Simulate键 ,开 始仿真,这时会弹出 一个窗口,该窗口会 现实仿真或者优化的 过程信息。如果出现 错误,里面会给出出 错信息,应该注意查 看。

3.1晶体管直流工作点扫描

3.3 SP模型仿真设计-输出匹配设计

各种文件的命名 电路的布局以及参数的设置和选择 要有合理的设计顺序 物理概念要明确,不要在无意义的地方花时间

要记住你在使用的是软件

比如:按照加工精度,有些线条太细是不能实现的,另外追求小数点后 面N位的精确也是无聊的。 注意仿真中使用模型的适用范围,比如:小信号模型就不能用来看三阶 交调等非线性的曲线(看了也是错的),微带线仿真的时候,注意要 L>W,软件中的模型才是对的。等等。 要按照先局部后整体的优化,切忌直接全局优化,最好能够预先计算设 置优化元件的初值。 要注意仿真的数值稳定性,对于对参数以来敏感的仿真结果在最后制作 的时候是很难实现的。适当的时候需要考虑改系统拓扑。 养成不明白就多看看help的习惯

基于ads仿真的低噪声放大器设计论文

基于ads仿真的低噪声放大器设计论文论文题目:基于ADS仿真的低噪声放大器设计摘要:低噪声放大器在无线通信系统中具有至关重要的作用,能够提高信号传输的质量和可靠性。

本论文基于ADS仿真平台对低噪声放大器的设计进行研究和优化,采用一种新颖的设计方法,以降低放大器的噪声系数,提高系统的性能。

首先,通过对低噪声放大器的原理和特性进行深入分析,确定了设计的目标和要求。

然后,利用ADS仿真工具进行电路设计和参数优化,并进行了相应的性能评估。

最后,通过实验验证了设计的有效性和可行性。

关键词:低噪声放大器、ADS仿真、噪声系数、性能评估、实验验证1.引言低噪声放大器在无线通信系统中起着关键作用,能够提高信号传输的质量和可靠性。

在设计低噪声放大器时,关注的主要指标是放大器的噪声系数。

低噪声放大器的设计需要考虑到多种因素,包括频率响应、幅度稳定性、增益平坦度等。

本论文旨在通过ADS仿真工具来实现低噪声放大器的设计和评估,优化其性能。

2.低噪声放大器设计原理3.ADS仿真工具的应用ADS是Agilent技术公司开发的一种射频和微波电路设计与仿真软件,具有强大的仿真和优化功能。

在本论文中,将使用ADS仿真工具来实现低噪声放大器的设计和优化。

通过合理选择元器件和调整电路参数,我们可以得到一个满足设计要求的低噪声放大器。

4.低噪声放大器设计和优化首先,在ADS中建立低噪声放大器的电路模型,包括源极、基极和负载等部分。

然后,通过电路参数的优化,使得在给定的频带内,低噪声放大器的噪声系数降至最低,并达到最佳的增益。

5.性能评估通过仿真数据对设计的低噪声放大器进行性能评估。

主要评估指标包括增益、噪声系数、频率响应以及其他性能参数。

比较设计方案的优缺点,选择和调整最佳的方案。

6.结果分析与讨论对仿真结果进行分析和讨论,评估设计的低噪声放大器方案的可行性和有效性。

对于不符合要求的设计方案,可以对电路参数进行进一步优化,以获得更好的性能。

基于ADS低噪声放大器设计及仿真

基于ADS低噪声放大器设计及仿真ADS是一种通用的射频、微波电路、系统设计和仿真工具,可以用于设计和仿真低噪声放大器。

在设计和仿真低噪声放大器时,有几个重要的步骤需要遵循。

首先,需要选择合适的低噪声放大器结构。

常见的结构包括共源共栅结构、共源共栅共板结构等。

在选择结构时,需考虑频率范围、增益、噪声系数等参数要求。

其次,需要选择适当的放大器器件。

可以选择P摄放大器、N型放大器、电离横流晶体管(HEMT)等。

在选择器件时,需考虑器件的噪声系数、增益特性、非线性特性等。

接下来,进行电路设计。

可以利用ADS提供的电路设计工具来设计低噪声放大器的电路。

根据选择的放大器结构和器件来设计电路的拓扑结构和参数。

设计完成后,需要进行电路的仿真。

可以利用ADS提供的仿真工具来仿真电路的性能。

通过仿真可以调整电路参数,优化低噪声放大器的性能。

在进行仿真时,可以分别对放大器的增益、噪声系数和非线性特性进行仿真。

可以通过特定的测试电路来测试放大器的增益和噪声系数,并分别将测试结果与设计指标进行比较。

在进行仿真时,还可以调整放大器的输入和输出匹配网络,以优化放大器的频率响应和增益。

可以逐步调整匹配网络的参数,并进行反复的仿真和优化,直到满足设计要求。

最后,还可以进行电路的布局和布线设计。

可以利用ADS提供的布局工具来设计电路的布局和布线。

通过优化布局和布线,可以减少电路的电磁干扰和信号损耗,提高低噪声放大器的性能。

综上所述,基于ADS进行低噪声放大器的设计和仿真可以帮助工程师快速设计出满足要求的低噪声放大器,并通过仿真来测试和优化放大器的性能。

ADS设计低噪声放大器详细步骤

ADS设计低噪声放大器详细步骤低噪声放大器(Low Noise Amplifier,LNA)是无线通信系统中一个重要的组成部分,其功能是将接收到的微弱信号放大,以便后续的处理和解调。

设计低噪声放大器需要考虑多个因素,包括噪声系数、增益、带宽、稳定性等。

下面是一个详细的设计步骤,用于设计低噪声放大器。

1.确定设计规格:a.确定工作频率范围:通常情况下,设计LNA需要确定工作频率的范围,以便选择合适的器件和电路结构。

b.确定增益和噪声系数要求:根据系统需求,确定LNA的增益和噪声系数的要求。

一般来说,增益越高,噪声系数越低,但二者之间存在一定的折衷关系。

2.选择器件:根据设计规格,选择适当的射频器件。

常见的射频器件包括双极性晶体管(BJT),高电子迁移率晶体管(HEMT),甲乙基氮化镓场效应晶体管(GaAsFET)等。

3.确定电路结构:根据选择的器件和设计规格,确定LNA的电路结构。

常见的LNA电路结构包括共源极结构、共栅极结构和共基极结构。

根据不同的结构,可以实现不同的增益和噪声系数。

4.进行器件参数提取:使用器件模型,从所选器件中提取器件的S参数(散射参数)、Y参数(混合参数)等。

这些参数将在后续的仿真和优化中使用。

5.进行电路仿真:使用电路仿真软件(如ADS,Spectre等),根据设计的电路结构和选取的器件参数,进行电路的仿真。

可以通过改变电路参数和器件参数,来优化电路的性能。

6.进行电路优化:在仿真过程中,可以进行电路参数的优化。

优化的目标可以是噪声系数、增益、带宽等。

通过反复地优化,寻找最佳的电路参数。

7.器件布局和仿真:根据优化后的电路参数,进行射频电路的布局设计。

布局需要考虑信号和功率的传输、射频电感和电容的布线、射频耦合以及射频接地等因素。

8.器件特性提取:根据布局后的射频电路,提取各个节点的特性参数,如增益、输入输出阻抗、稳定性等。

9.进行电路仿真验证:使用仿真软件进行电路的验证,比较仿真结果与设计目标的一致性。

ADS设计低噪声放大器的详细步骤课件

系统集成与优化

讨论了未来低噪声放大器在 系统集成中的优化方法,包 括功耗、尺寸和可靠性等方 面的改进。

标准化与可靠性

探讨了未来低噪声放大器设 计的标准化和可靠性问题, 以提高产品的互操作性和稳 定性。

THANKS

感谢观括菜单栏、 工具栏、工作区和状 态栏等部分。

菜单栏

菜单栏包括文件、编 辑、视图、仿真、设 计等常用命令。

工具栏

工具栏提供了常用命 令的快捷方式,方便 用户快速操作。

工作区

工作区是用户进行电 路设计和仿真的主要 区域。

状态栏

状态栏显示当前操作 的状态和提示信息。

04

对信号的影响。

设计实例二:复杂低噪声放大器

总结词

自动增益控制

复杂低噪声放大器在简单低噪声放大器的 基础上增加了更多的功能和优化措施,以 适应更复杂的应用需求。

通过反馈控制电路,实现增益的自动调整 ,确保输出信号的稳定。

抑制谐波失真

多频段设计

通过使用负反馈技术,减小信号的谐波失 真,提高信号质量。

针对不同频段的应用需求,设计多频段低 噪声放大器,实现宽频带信号的放大。

确定功耗

根据应用场景和便携性要求, 设定低噪声放大器的功耗,以

确保设备的续航能力。

选择合适的器件

选择合适的晶体管

根据设计目标和工艺条件,选择合适 的晶体管类型和型号,以满足性能和 成本要求。

选择合适的电阻和电容

根据电路设计和性能要求,选择合适 的电阻和电容,以确保电路的稳定性 和性能。

建立电路模型

课程目标

1

了解低噪声放大器的基本概念、原理和应用。

利用ADS设计低噪声放大器LNA

利用ADS 设计LNA低噪声放大器设计的依据和步骤:•满足规定的技术指标噪声系数(或噪声温度);功率增益;增益平坦度;工作频带;动态范围输入、输出为标准微带线,其特征阻抗均为50Ω步骤:• 放大器级数(对于我们,为了便于设计和学习,通常选择一级) • 晶体管选择 • 电路拓扑结构 • 电路初步设计•用CAD 软件进行设计、优化、仿真模拟一、低噪声放大器的主要技术指标1.LNA 的噪声系数和噪声温度 放大器的噪声系数NF 可定义如下outout in in N S N S NF //=式中,NF 为微波部件的噪声系数;S in ,N in 分别为输入端的信号功率和噪声功率; S out ,N out 分别为输出端的信号功率和噪声功率。

噪声系数的物理含义是:信号通过放大器之后,由于放大器产生噪声,使信噪比变坏;信噪比下降的倍数就是噪声系数。

通常,噪声系数用分贝数表示,此时)lg(10)(NF dB NF =放大器自身产生的噪声常用等效噪声温度T e 来表达。

噪声温度T e 与噪声系数NF 的关系是)1(0-⋅=NF T T e 式中,T 0为环境温度,通常取为293K 。

2.LNA 的功率增益、相关增益与增益平坦度微波放大器功率增益有多种定义,比如资用增益、实际增益、共扼增益、单向化增益等。

对于实际的低噪音放大器,功率增益通常是指信源和负载都是50Ω标准阻抗情况下实功率增益的大小还会影响整机噪声系数,下面给出简化的多级放大器噪声系数表达式: (112)13121+-+-+=G G N G N N N f f f f其中:f N -放大器整机噪声系数;321f f f N N N ,,-分别为第1,2,3级的噪声系数;21G G ,-分别为第1,2级功率增益。

从上面的讨论可以知道,当前级增益G 1和G 2足够大的时候,整机的噪声系数接近第一级的噪声系数。

因此多级放大器第一级噪音系数大小起决定作用。

作为成品微波低噪音放大器的功率增益,一般是20-50dB 范围。

基于ADS的低噪放大器设计

基于ADS的低噪放大器设计低噪放大器(LNA)是无线通信系统和射频电路中非常重要的组成部分,其主要功能是接收到的微弱信号进行放大并降低噪声水平。

在LNA设计中,使用高度集成的射频集成电路技术(ASIC)来实现高性能的LNA是相对常见的方法之一、本文将基于ADS软件进行低噪放大器的设计。

在ADS软件中,设计LNA的第一步是选择适当的放大器结构。

常见的放大器结构包括共源放大器、共栅放大器和共源共栅放大器等。

在选择放大器结构时,需要根据电路的噪声要求、增益要求和频率范围来决定。

在本文中,我们将选择共源放大器结构进行LNA的设计。

第二步是进行器件的建模和参数选择。

在ADS软件中,我们可以使用S参数模型或者使用器件的原理模型来进行建模。

对于MOSFET器件,我们可以使用BSIM3或者BSIM4模型。

在选择模型时,需要考虑器件的性能和仿真的准确性。

此外,还需要选择合适的器件尺寸和电流偏置点,以满足低噪声和高增益的要求。

第三步是进行射频传输线的设计和匹配网络的设计。

在LNA的输入端,通常需要使用一个传输线来实现输入的匹配。

在ADS软件中,我们可以使用Smith图或者阻抗匹配工具来设计和优化传输线。

另外,在输出端也需要进行匹配网络的设计,以实现合适的阻抗匹配。

在设计匹配网络时,可以使用传统的L型、π型或者香蕉型网络,也可以使用阻抗变换器来实现匹配。

第四步是进行直流偏置电路的设计。

在共源放大器中,需要使用直流偏置电路来提供适当的电流偏置点。

直流偏置电路的设计通常包括电流源和电流镜。

在ADS软件中,我们可以使用电流源和电流镜元件来设计直流偏置电路。

根据仿真结果,可以调整电流源和电流镜的尺寸和电流偏置点,以满足设计的要求。

第五步是进行电路的仿真和性能评估。

在ADS软件中,可以使用S参数仿真、噪声仿真和交流仿真来评估LNA的性能。

通过调整各个元件的参数,可以得到合适的增益、噪声系数和带宽等性能指标。

在设计中,需要注意平衡增益和噪声系数的关系,以及增益、带宽和稳定性的平衡。

基于ads的低噪声放大器设计

基于ADS 的低噪声放大器设计[摘要]伴随着无线通信和CMOS 工艺的发展,让基于CMOS 工艺下的射频集成电路设计成为目前研究热点。

本文主要是设计低噪声放大器,决定着接收机整体性能的关键模块。

它需要具有低噪声、良好的增益、线性度、较低的功耗和合适的输入输出匹配。

本文是基于TSMC 0.18umCMOS 工艺并运用电感源极负反馈与共源共栅结构的结合作为设计低噪声放大器的基本框架,并采用ADS 软件对电路图进行仿真,对初步仿真结果进行进一步分析,处理的难点在于这些参数是密不可分的,因此要对它们进行折衷的考虑分析、优化调谐操作等等。

仿真结果为:在5.2GHz 处,输入输出回波放射系数与都小于-30dB, 增益值11S 22S 为14.106dB ,功耗为38mA ,噪声系数为1.228dB,1dB 压缩点为-11.2021S dBm,三阶互调点为-2.5dBm 。

以上结果均满足预先的设计指标要求。

[关键词] 低噪声放大器 ADS 仿真 CMOS 工艺 电感源极负反馈共源共栅Low Noise Amplifier design besed on ADSZheng pengdaNO: 2011850022, Electronic science and technology major, 2015,Information Engineering College of Jimei UniversityAbstract: With the development of wireless communication technologies and CMOS tec-hnolo gy, let radio frequency integrated circuit design based on CMOS process has become the hot topic of the current research. This paper is to design the low noise amplifier whi-cth is the key to t he overall performance of the receiver module. It has required low noise,good gain and linearity, l ow power consumption, the appropriate input and output matching. This paper is based on TSMC 0.18 um CMOS process and cascode topology with induct-ive source degenration negative feedb ack as the basic framework of the design of low noi-se amplifier. The circuit diagram of low noise amplifier with ADS software simulation. Forpr-eliminary simulation results for further analysis, deal with thedifficulty is that these paramet-ers are inseparable, so want to compromise their consideration analysis, optimization andtuning operation and so on. Simulation results : at 5.2 GHz, input and output echo radiati-on coefficient and are less than 30 dB, the gain value of 14.106 dB, power consumptionis 38 ma, noise coefficient is 1.228 dB, 1 dB compression poi-nt for -11.20 dBm, The thirdorder intermodulation point of 2.5 dBm. These results can satisfy the requirements of desi-gn index of the advance.Key words : Low Noise Amplifier, ADS simulation, CMOS technology, Cascode topology with inductive source degenration引言 (1)第1章低噪声放大器的基本原理以及性能参数 (2)1.1 基本概念 (2)1.2 低噪声放大器性能参数的介绍 (3)第2章低噪声放大器的方案设计 (7)2.1 电感源极负反馈结构的采用以及相应的参数介绍 (7)2.2 共源共栅结构(Cascode)的低噪声放大器 (8)2.3 单端和差分放大器 (9)第3章低噪声放大器的电路设计与仿真结果 (11)3.1 低噪声放大器的电路图设计 (11)3.1.1 低噪声放大器设计的性能指标要求 (11)3.1.2 低噪声放大器(LNA)的电路图 (12)3.2 仿真结果电路图 (12)3.3 仿真结果分析 (13)3.3.1 DC直流仿真 (13)3.3.2 S参数的仿真 (14)3.3.3 S 参数的调谐模式 (16)3.3.4 1dB压缩点仿真 (19)3.3.5 三阶互调仿真 (21)3.3.6 低噪声放大器的仿真结果指标值 (22)结论 (23)致谢语 (24)[参考文献] (25)近年来,随着无线通信技术被大规模应用到社会生活中的各个领域,如:GPS全球卫星定位系统、无线局域网WLAN、雷达、遥感遥控、移动通信、无线接入系统(蓝牙)、高速语音、蜂窝式个人通信与基地站、智能交通系统等等,射频无线通信技术在现代生活中就扮演着举足轻重的角色,它的高度机动性和灵活性使它的应用日益广泛。

基于ADS低噪声放大器设计及仿真

基于ADS低噪声放大器设计及仿真ADS是一种电路仿真工具,可用于设计和仿真电子电路。

低噪声放大器在许多应用中非常重要,特别是在无线通信和信号处理中。

本文将介绍如何基于ADS进行低噪声放大器的设计和仿真。

首先,需要明确低噪声放大器的设计目标和性能指标。

低噪声放大器的主要目标是提供高增益和低噪声,以传输和放大信号时尽可能降低噪声干扰。

因此,设计低噪声放大器的时候需要考虑以下指标:1.增益:放大器应具有足够的增益来放大信号,使其达到所需的信号水平。

2.噪声系数:噪声系数是一种量化噪声性能的指标,它表征了放大器引入的噪声功率与输入信号功率之比。

低噪声放大器应该具有较低的噪声系数以降低信号的噪声干扰。

3.带宽:放大器的带宽决定了它能够传输的频率范围。

对于无线通信和信号处理应用,放大器需要具有足够宽的带宽来传输高频信号。

设计低噪声放大器的第一步是选择适当的放大器拓扑结构。

常见的低噪声放大器拓扑结构包括共源极、共栅极和共基极。

在ADS中,可以使用S参数模型来模拟这些拓扑结构,并进行频率和噪声分析。

在选择了适当的拓扑结构之后,需要设计放大器的电路参数,如电流源偏置、电流源阻抗以及电容。

这些参数将直接影响放大器的性能。

接下来,使用ADS进行电路仿真。

可以将放大器的电路图导入ADS,并添加合适的仿真器和分析器。

一般来说,需要进行频率响应、增益和噪声分析。

在进行噪声分析时,需要输入合适的噪声模型,并设置合适的参数。

仿真完了之后,可以通过改变电路参数和拓扑结构来优化低噪声放大器的性能。

一般来说,可以尝试改变电容和电流源的值,以及优化电流源阻抗和偏置电流。

最后,可以根据仿真结果进行实际电路的制作和测试。

由于ADS可以生成精确的电路参数和特性,因此可以根据仿真结果进行电路制造,并通过实验进行性能验证。

综上所述,基于ADS进行低噪声放大器的设计和仿真可以帮助工程师优化放大器的性能,以满足特定应用的需求。

通过合理选择拓扑结构、优化电路参数和进行全面的电路仿真,可以设计出具有高增益和低噪声的低噪声放大器。

基于ADS低噪放大器设计

基于ADS低噪放大器设计ADS(差分开关放大器)是一种常用于模拟电路中的低噪声放大器。

本文将以ADS为基础,详细介绍低噪声放大器的设计。

低噪放大器(low noise amplifier,LNA)是一种特殊类型的放大器,其主要功能是将输入信号放大到合适的水平,并尽量减少引入到信号中的噪声。

在无线通信系统中,LNA被广泛应用于接收机前端,以提高接收灵敏度和系统性能。

因此,设计一个低噪声放大器对于提高系统性能至关重要。

首先,在设计LNA之前,需要对所需的规格进行明确定义。

这些规格通常包括增益、噪声指标(如噪声系数和等效噪声电阻)以及带宽。

根据这些规格,可以选择合适的放大器拓扑结构。

ADS作为一种常见的放大器架构,其基本工作原理是将信号差分输入到放大器的两个输入端口,并从输出端口获取放大的差分信号。

为了减少噪声的引入,放大器采用了差动输出结构。

在设计ADS低噪声放大器时,可以采取以下步骤:1.选择合适的材料和器件参数:在设计LNA时,需要选择低噪声系数的材料和器件参数。

这些参数包括电流和电压的工作点以及电流源和电容等的尺寸。

3.设计输入和输出匹配网络:在LNA的输入和输出端口上设计合适的匹配网络,以确保最大化输入和输出信号的功率传递以及最小化噪声的引入。

常用的匹配网络包括L型网络和π网络。

4.进行直流操作点分析:在设计LNA时,需要进行直流操作点分析,以确保放大器在电流和电压的工作点范围内正常工作。

5.进行交流分析和噪声分析:通过相关软件(如ADS)进行交流分析和噪声分析,以评估放大器的增益、噪声系数以及其他性能指标。

6.优化设计参数:根据分析结果,优化设计参数以满足所需的规格。

这可能涉及对材料和器件参数进行微调,调整匹配网络或重新选择放大器拓扑结构。

7.进行模拟和实验验证:使用电路模拟软件进行模拟验证,并进行实验验证以验证设计的性能。

需要注意的是,设计LNA需要一定的电路设计和分析知识,以及熟练的电路模拟工具操作技能。

基于ADS的低噪声放大器设计与仿真

基于ADS的低噪声放大器设计与仿真低噪声放大器(Low Noise Amplifier,简称LNA)是一种用于放大微弱信号的模拟电路。

在通信系统、雷达系统和无线传感器网络等应用中,LNA被广泛使用。

设计和仿真低噪声放大器可以通过多种方式实现,而其中一种常见的方法是基于开环电压增益的放大器设计技术。

下面将介绍如何基于ADS (Advanced Design System)软件进行LNA的设计与仿真,以实现低噪声和高增益。

首先,选择适当的晶体管器件。

根据所需的频率范围和特性要求,选择合适的晶体管型号。

ADS软件提供了多种晶体管模型,可以根据需要进行选择。

其次,进行电路拓扑设计。

根据晶体管的输入和输出阻抗要求,选择合适的匹配网络。

同时,还需要设计适当的偏置电路,以确保晶体管工作在最佳工作点。

然后,进行S参数仿真。

使用ADS软件的S参数仿真工具,对电路进行S参数仿真。

通过调整匹配网络和偏置电路,优化电路的S参数,以获得最佳的增益和带宽。

接下来,进行噪声参数仿真。

使用ADS软件的噪声参数仿真工具,对电路进行噪声参数仿真。

根据要求,选择适当的噪声参数模型,以评估电路的噪声性能。

然后,进行稳定性分析。

使用ADS软件的稳定性分析工具,对电路进行稳定性分析。

通过调整反馈网络和补偿网络,确保电路的稳定性。

最后,进行时域和频域仿真。

使用ADS软件的时域仿真和频域仿真工具,对电路进行时域和频域分析。

通过调整电路参数,优化电路的动态性能和频率响应。

需要注意的是,在整个设计过程中,应根据需要进行多次优化。

可以通过改变电路拓扑、调整匹配网络和偏置电路等方式进行优化。

总结起来,基于ADS的低噪声放大器设计与仿真主要包括晶体管选择、电路拓扑设计、S参数仿真、噪声参数仿真、稳定性分析、时域和频域仿真等步骤。

通过多次优化,可以实现低噪声和高增益的设计要求。

基于ADS的低噪声放大器设计与仿真

基于ADS的低噪声放大器设计与仿真低噪声放大器(Low-Noise Amplifier, LNA)是射频电路中非常重要的一个部分,主要用于放大信号并减小信号中的噪声。

在无线通信系统中,LNA的性能对整体系统的灵敏度和性能有着较大影响。

因此,设计和优化LNA的性能是一个重要的任务。

为了设计和仿真低噪声放大器,我们可以使用射频电路设计工具ADS (Advanced Design System)。

以下是基于ADS的LNA设计和仿真步骤的详细说明:1.设定设计规格:首先,我们需要确定LNA的设计规格,包括增益、带宽、输入和输出阻抗以及噪声指标等。

这些规格将指导后续的设计和优化。

2.选择合适的器件模型:在ADS中,我们可以从器件库中选择合适的射频器件模型。

这些器件模型通常由芯片制造商提供,并包含了器件的电性能和行为特性。

3.组装电路拓扑:在ADS设计环境中,我们可以通过拖拽和连接器件模型,以及添加连接线和连接器等来组装电路拓扑。

根据设计规格,我们可以选择串联或并联的方式来组装放大器电路。

4.添加偏置电路:为了使LNA正常工作,我们需要添加适当的偏置电路。

这些偏置电路可以是直流电源、偏置电阻和偏置电容等。

5. 设计匹配网络:为了确保LNA的输入和输出阻抗与源和负载匹配,在ADS中,我们可以使用S参数和Smith图等工具来设计和优化匹配网络。

6.仿真性能指标:在设计完成后,我们可以使用ADS的模拟仿真工具来评估LNA的性能指标,如增益、噪声指标、稳定性和带宽等。

这些仿真结果可以帮助我们了解LNA的行为特性,识别并改进潜在的问题。

7.优化设计:根据仿真结果,我们可以进行一系列的设计优化,包括调整组件值、优化匹配网络、改变电路拓扑等。

通过不断地迭代优化,我们可以逐步接近设计规格的要求。

8.布局和封装:当设计满足规格要求后,我们可以进行布局设计和封装。

在ADS中,我们可以使用高级工具来完成布局和封装过程。

9.重新仿真和验证:在布局和封装完成后,我们需要重新进行仿真和验证。

基于ADS的低噪放大器设计

v .. . ..xxx研究生射频电路课程报告基于ADS的低噪放大器设计学生:xxx学号:xxx指导教师:xxx专业:电子与通信工程Xxxxxx二O一三年十一月目录 (1)1 引言 (2)1.1低噪声放大器设计理论 (2)1.2低噪声放大器设计步骤 (2)1.3本次设计主要性能指标 (2)1.4小结 (3)2 低噪声放大器设计 (4)2.1晶体管的选择和下载 (4)2.2直流分析 (4)2.3偏置电路的设计 (5)2.4稳定性分析 (6)2.5噪声系数圆和输入匹配 (8)2.6最大增益的输出匹配 (12)2.7匹配网络的实现 (14)2.8原理图仿真 (15)2.9小结 (15)1.1 低噪声放大器设计理论低噪声放大器的设计目标就是在选择适当的晶体管后,通过设计合适的输入输出匹配网络来达到极低的噪声系数的同时获得一定的增益,通常在设计中采用折中的方案来达到设计要求。

在LNA的设计中,需要考虑的最重要的几个因素如下:放大器的稳定性:设计射频放大器时,必须优先考虑电路稳定性。

稳定性是指放大器抑制环境变化维持正常工作特性的能力。

在设计中,绝对稳定系数K 必须大于1,放大器才能达到绝对稳定。

放大器的功率增益:对输入信号进行放大是放大器最重要的任务,因此在放大器的设计中增益指标的完成很是重要,而我们通常所说的增益主要指转换功率增益G。

放大器输入输出驻波比:驻波比反映了信源与晶体管及晶体管与负载之间的失配程度,所以设计时要求驻波比要保持在特定指标之下。

放大器的噪声:对放大器来说,噪声的存在对整个设计有重要影响,在低噪声的前提下对信号进行放大是对放大器的基本要求。

1.2 低噪声放大器设计步骤晶体管的选择、下载与安装;直流分析;偏置电路设计;稳定性分析;噪声系数圆和输入匹配;匹配网络的实现;原理图仿真。

1.3 本次设计主要性能指标中心频率fo=5.8GHz;带宽B=300MHz;增益G=15dB;噪声系数Nf小于等于3dB;Zin=Zout=50Ω。

基于ads 的低噪声放大器设计与仿真

基于ADS的低噪声放大器设计与仿真一、实验背景和目的 (4)1.1 低噪声放大器 (4)1.1.1 概念 (4)1.1.2 主要功能 (4)1.1.3 主要应用领域 (5)1.2 低噪声放大器的研究现状 (5)1.3 本实验报告的主要研究内容和内容安排 (6)二、低噪声放大器的原理分析与研究 (7)2.1 低噪声放大器的基本结构 (7)2.2 低噪声放大器的基本指标 (7)2.2.1 噪声系数 (8)2.2.2 增益 (9)2.2.3 输入输出驻波比 (9)2.2.3 反射系数 (9)2.2.4 放大器的动态范围(IIP3) (10)2.3 低噪声放大器设计设计的基本原则 (10)2.3.1 低噪声放大管的选择原则 (10)2.3.2 输入输出匹配电路的设计原则 (10)三、低噪声放大器的设计 (14)3.1 放大器设计的主要流程 (14)3.2 低噪声放大管的选择 (15)3.3 稳定性计算 (16)3.4 输入输出匹配电路电路设计 (17)3.5 偏置电路 (18)3.6 电路中需要注意的一些问题 (18)四、设计目标 (20)五、ADS软件仿真设计和结论 (21)5.1 ADS仿真设计 (21)5.1.1 直流分析DC TRacing (21)5.1.2 偏置电路的设计 (21)5.1.3稳定性分析 (22)5.1.4噪声系数园和输入匹配 (22)5.1.5最大增益的输出匹配 (25)5.2 结论分析 (30)需要仿真源文件,请在空间留言一、设计的背景和目的1.1 低噪声放大器在无线通信系统中,为了提高接受信号的灵敏度,一般在接收机前端放置低噪声放大器用来提高增益并降低系统的噪声系数。

1.1.1 概念低噪声放大器是噪声系数很低的放大器。

一般用作各类无线电接收机的高频或中频前置放大器,以及高灵敏度电子探测设备的放大电路。

在放大微弱信号的场合,放大器自身的噪声对信号的干扰可能很严重,因此希望减小这种噪声,以提高输出的信噪比。

基于ADS的低噪放大器设计

基于ADS的低噪放大器设计

一、引言

随着通信技术的发展,低噪放大器的性能变得越来越重要。

为了满足

低噪放大器的需求,许多技术都被开发出来,其中最有效的技术之一就是

基于自适应数字信号处理(ADS)的低噪系统设计。

基于ADS的低噪放大

器设计能够以最低的噪声水平实现最优的性能。

本文将对基于ADS的低噪

放大器设计方法进行详细的阐述,具体来说,将介绍ADS低噪放大器设计

的基本原理、各种技术指标以及设计要点。

二、ADS低噪放大器设计的基本原理

基于ADS的低噪放大器设计的基本原理是使用数字信号处理技术,实

现放大器的自适应控制,最小化放大器的噪声水平。

数字信号处理的基本

原理是通过将输入信号的频率特征采样,根据采样点建立模型来模拟信号

的动态变化,使得系统可广泛应用于实时信号处理。

具体来说,采用ADS

技术来设计低噪放大器时,首先将输入信号采样,然后按照采样点建立模型,利用模型来估计信号动态变化,再根据估计的动态变化来控制放大器

的参数,从而最小化放大器的噪声水平。

三、ADS低噪放大器设计的技术指标

要想实现ADS低噪放大器设计,除了采用基本的数字信号处理技术外,还要确保其他几项技术指标达到较高的水平。

ADS设计低噪声放大器的详细步骤

ADS设计低噪声放大器的详细步骤设计低噪声放大器的详细步骤:第1步:明确设计要求在设计低噪声放大器之前,首先需要明确设计要求。

这包括频率范围、放大增益、输入和输出阻抗、噪声系数等。

明确设计要求有助于确定设计流程和选择适当的元器件。

第2步:选择适当的放大器拓扑选择正确的放大器拓扑对于设计低噪声放大器至关重要。

常见的低噪声放大器拓扑包括共源极、共栅极和共漏极三种。

根据设计要求选择合适的放大器拓扑。

第3步:计算输入匹配电路在低噪声放大器中,输入匹配电路起到匹配输入信号源和放大器的作用。

输入匹配电路通常由电容、电感和微带线构成。

通过计算输入匹配电路可以保证输入信号最大的功率传输。

第4步:计算输出匹配电路类似于输入匹配电路,输出匹配电路也起到匹配放大器和负载的作用。

输出匹配电路也通常由电容、电感和微带线构成。

通过计算输出匹配电路可以使放大器输出功率最大化。

第5步:确定元器件参数在设计低噪声放大器时,需要确定各个元器件的参数。

这包括电容、电感、微带线的尺寸、负载电阻等。

选择合适的元器件参数可以满足设计要求,并使放大器具有较低的噪声。

第6步:模拟电路设计在模拟电路设计中,可以使用一些常见的电路设计软件,如ADS、CST等。

通过电路设计软件可以模拟和优化低噪声放大器的性能。

优化过程中需要注意输入和输出匹配、放大增益和噪声系数等指标。

第7步:布局设计和电磁兼容性完成模拟电路设计后,需要进行PCB布局设计。

布局设计需要考虑到电磁兼容性和噪声干扰等问题。

合理的布局设计可以降低噪声的干扰,提高放大器的性能。

第8步:制作和调试完成布局设计后,进行PCB板的制作和元器件的焊接。

完成后对放大器进行调试和测试。

调试可以通过信号源输入和示波器测量输出信号来进行。

第9步:优化和改进在进行测试后,可能发现放大器的性能还有待改进。

根据测试结果可以进行优化和改进。

可能需要对元器件进行更换或调整电路参数等。

第10步:测试验证最后对设计的低噪声放大器进行测试验证。

ADS设计低噪声放大器LNA

ADS设计低噪声放大器LNA低噪声放大器(LNA)是无线通信系统中的一种关键元件,它起到增益和降低接收信号噪声的作用。

在LNA设计中,主要目标是实现高增益和低噪声系数,以提高系统灵敏度和性能。

本文将介绍LNA的基本原理和设计过程。

LNA的基本原理是利用放大器的特性放大输入信号,并在尽可能少的增加噪声的情况下提高信号质量。

其主要性能指标包括增益、噪声系数、带宽和输入输出阻抗等。

在设计LNA之前,首先需要确定设计参数,包括频率范围、增益、噪声系数和输入输出阻抗等。

其中,频率范围由所应用的无线通信系统确定,增益和噪声系数根据系统要求确定,输入输出阻抗由系统匹配要求决定。

LNA的一种常用设计方法是利用CMOS工艺。

CMOSLNA设计中的一个关键问题是电流源的选择,它直接影响增益和噪声系数。

在设计过程中,需要平衡增益和噪声系数之间的矛盾,选择适当的电流源类型和参数。

另一种常见的LNA设计方法是利用混频器技术,即将输入信号与本地振荡信号混合,从而将所需放大的频率转换到中频。

混频器技术可以有效地降低输入信号频率,减少噪声和非线性影响。

在LNA设计中,信号和噪声之间的平衡是一个关键问题。

在选择放大器类型和参数时,需要考虑信号和噪声功率比的最佳平衡点,以实现最佳性能。

另外,LNA的输入输出匹配也是设计过程中的一个重要问题。

输入输出阻抗的匹配可以最大限度地提高信号传输效率,并减少信号反射和损耗。

在LNA设计中,还需要考虑电源噪声的影响。

电源噪声可以通过适当选择电源滤波和稳压器来减小。

最后,LNA设计的最终目标是实现高增益和低噪声系数。

在设计过程中,可以采用一些优化技术来提高LNA性能,例如使用负反馈技术、优化器件尺寸和电流源参数等。

总结起来,设计低噪声放大器LNA需要考虑多个因素,包括频率范围、增益、噪声系数和输入输出阻抗等。

在设计过程中,需要平衡增益和噪声系数,选择适当的放大器类型和参数,并考虑输入输出匹配和电源噪声等因素。

基于ADS仿真的低噪声放大器设计

基于ADS仿真的低噪声放大器设计类别:模拟技术1 引言低噪声放大器(LNA)位于射频接收机的前端,其主要功能是对微弱信号进行低噪声放大。

在低噪声放大器的设计过程中,要综合考虑其放大能力、噪声系数和匹配等因素,这需要大量的理论计算和smith圆图分析,给设计工作带来困难。

Advanced Design System(ADS)软件是Agilent公司在HPEESOF系列EDA软件基础上发展完善的综合设计软件,内含很多进行小信号放大器设计的控件,能实现大量的计算和smith圆图分析。

以下将介绍如何利用ADS设计和仿真低噪声放大器。

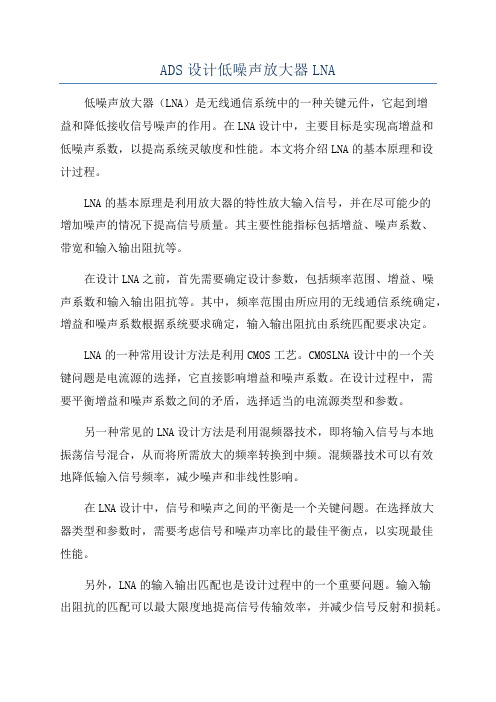

2 低噪声放大器的设计理论图1是放大器电路原理框图,其中r 表示源反射系数,r 表示负载反射系数。

不同的r 和r。

.将影响放大器的稳定性、噪声系数、增益、驻波等参数。

设计放大器的过程就是根据放大器的s参数,以及噪声系数、增益、驻波等的要求来确定TS和TL,然后根据TS和TL 确定输入、输出匹配网络。

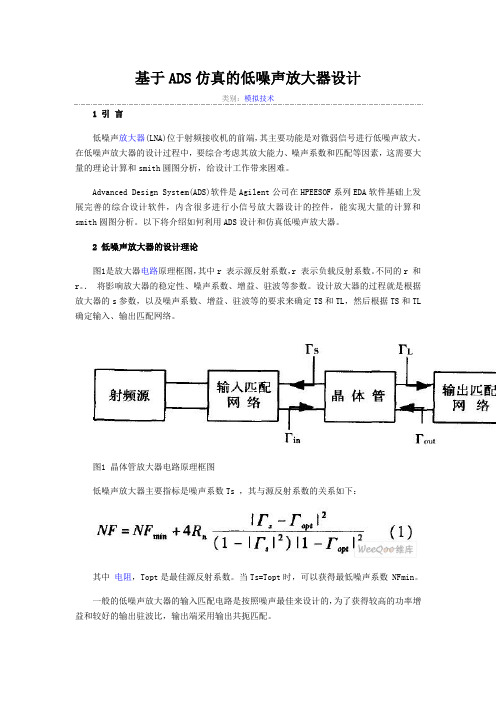

图1 晶体管放大器电路原理框图低噪声放大器主要指标是噪声系数Ts ,其与源反射系数的关系如下:其中电阻,Topt是最佳源反射系数。

当Ts=Topt时,可以获得最低噪声系数 NFmin。

一般的低噪声放大器的输入匹配电路是按照噪声最佳来设计的,为了获得较高的功率增益和较好的输出驻波比,输出端采用输出共扼匹配。

3 低噪声放大器设计仿真和优化3.1 设计目标低噪声放大器设计的关键是电路的第一级。

对于低噪声放大器的第二级及后续电路,可以使用MMIC微波单片放大器来完成,其设计相对来说比较简单。

利用ATF一33143完成电路第一级的设计目标是:频率:1260MHz一1280MHz;增益:≥10dB;噪声系数:≤0.5dB;输入驻波比:≤1.5;输出驻波比:≤1.5。

3.2 仿真设计(1)建立模型上网下载ATF一33143的器件手册,其器件手册中提供了标准模型 J。

(2)确定工作点及偏置电路根据芯片在各直流工作点条件下的性能选择直流工作点。

ADS设计低噪声放大器的详细步骤解析

ADS设计低噪声放大器的详细步骤解析低噪声放大器(Low Noise Amplifier,LNA)是一种用于放大小信号并且噪声系数较低的放大器。

在射频领域,LNA是一个非常重要的组件,广泛应用于无线通信、雷达、卫星通信等各种系统中。

以下是设计低噪声放大器的详细步骤解析:1.确定设计规格:首先,需要明确设计放大器的应用和要求,包括频率范围、增益、噪声系数、功率消耗等。

这些规格将在接下来的设计过程中起到指导作用。

2.选择放大器类型:根据设计规格,选择合适的放大器类型。

常见的放大器类型包括共源极放大器、共源极共栅放大器、共栅共源极放大器等。

3.确定工作频率:根据设计要求,确定放大器的工作频率范围。

这个步骤中需要考虑系统的频率计划、抗干扰能力以及现有系统中的其他无线电频率。

4.确定增益要求:根据设计要求,确定放大器需要提供的增益。

增益通常由设计要求中给出的最小信号到最大信号的目标增益范围定义。

5.噪声分析:根据设计要求,对放大器的噪声特性进行分析。

噪声分析是设计低噪声放大器的关键步骤之一,可以通过建立噪声模型和使用噪声参数进行计算来完成。

6.噪声匹配:根据噪声分析结果,进行噪声匹配。

噪声匹配的目的是使输入噪声电阻等于输出噪声电阻,从而达到最佳的噪声性能。

7.确定电源电压与电流:根据设计要求和选取的放大器类型,确定放大器的电源电压与电流。

这个步骤中需要考虑放大器的功率消耗和供电要求。

8.确定器件参数:根据选定的放大器类型、工作频率和增益要求,选择合适的器件进行设计。

常见的器件参数包括截止频率、最大功率、最大电流等。

9.进行电路仿真:使用电路仿真工具(如ADS等),对设计的放大器进行仿真。

仿真可以帮助分析和优化放大器的性能,例如增益、噪声系数等。

10.进行电路优化:根据仿真结果,对放大器进行优化。

优化的目标可能包括增加增益、降低噪声系数、提高稳定性等。

11.组装与测试:将设计好的放大器电路进行组装,并进行测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

xxx 研究生射频电路课程报告基于ADS 的低噪放大器设计学生:xxx学号:xxx指导教师:xxx专业:电子与通信工程XxxxxxO 一三年十一月目录 (1)1引言 (2)1.1低噪声放大器设计理论 21.2低噪声放大器设计步骤 21.3本次设计主要性能指标 21.4小结 (3)2低噪声放大器设计 (4)2.1晶体管的选择和下载 42.2直流分析 42.3偏置电路的设计 52.4稳定性分析 62.5噪声系数圆和输入匹配82.6最大增益的输出匹配122.7匹配网络的实现142.8原理图仿真152.9小结 (15)1引言1.1低噪声放大器设计理论低噪声放大器的设计目标就是在选择适当的晶体管后,通过设计合适的输入输出匹配网络来达到极低的噪声系数的同时获得一定的增益,通常在设计中采用折中的方案来达到设计要求。

在LNA的设计中,需要考虑的最重要的几个因素如下:放大器的稳定性:设计射频放大器时,必须优先考虑电路稳定性。

稳定性是指放大器抑制环境变化维持正常工作特性的能力。

在设计中,绝对稳定系数K 必须大于1,放大器才能达到绝对稳定。

放大器的功率增益:对输入信号进行放大是放大器最重要的任务,因此在放大器的设计中增益指标的完成很是重要,而我们通常所说的增益主要指转换功率增益Go 放大器输入输出驻波比:驻波比反映了信源与晶体管及晶体管与负载之间的失配程度,所以设计时要求驻波比要保持在特定指标之下。

放大器的噪声:对放大器来说,噪声的存在对整个设计有重要影响,在低噪声的前提下对信号进行放大是对放大器的基本要求。

1.2低噪声放大器设计步骤晶体管的选择、下载与安装;直流分析;偏置电路设计;稳定性分析;噪声系数圆和输入匹配;匹配网络的实现;原理图仿真。

1.3本次设计主要性能指标中心频率fo=5.8GHz;带宽B=300MHz;增益G=15dB;噪声系数Nf小于等于3dB;Zin=Zout=50Q o1.4小结本次对低噪声放大器的设计,使用Agilent 公司的高级设计软件ADS2009 仿真,首先确定了ATF35176晶体管的静态工作点,得到晶体管ATF35176在直流偏置情况下的小信号电路的模型,然后设计了一个在中心频率为 5.8GHz满足指标要求的低噪声放大器。

2低噪声放大器设计2.1 晶体管的选择和下载低噪声放大器的性能取决于有源器件的噪声特性和匹配网络的设计。

HP 公司的ATF35176是一种低噪声神化钱 PHEMT 器件,在理想的工作点下,在12GHz 以下噪声系数为0.75 dB 以下,是一款适用于工作在2~18 GHz 的低噪声放大器, 所以本设计选择了此种晶体管。

另外考虑放大器的增益指标,由于 ATF35176单 级增益可以达到为18dB,而本设计要求增益达到15dB,所以只需要单级电路就 可以达到指标。

ADS2009自带的元器件库里含有ATF35176元器件模型,不需要下载和安装。

2.2 直流分析设计第一步是确定晶体管的直流工作点,根据ATF35176的datasheet ®置DC_FET 控件的参数,连接原理图后进行仿真。

从 ATF35176的数据手册可以得 到噪声Vds 和Ids 的关系,从而确定静态工作点。

在 6GHz 时,当Vds=3V 且 Ids=20mA 时,此时增益大约为16dB,能满足设计要求,那么晶体管的直流工作 点就设为 Vds=3V,ds=20mA 。

PSHWlWAbsolijM ULUimum 11Drain-SourceGs'e-So^fce Vottogt Drain Qjment Total OtaipAben ** RF Input Pgwtfr CMfl 帕1 曰帕lure StQf^gt TtmcwfBtuf*V QSI D P T P*>1**K T QH T JTQ +4 V-3 V klM 225mW *10 dBm 15DX •AStolSOX2.1 ATF35176 datasheet□C_FET SIM1VGS Hartze VGS_sl:ap=3 VGS_poirH5r=l5 VDS_slHfL=(JVDS-Slop” g5 gH 鸨= 31日1邛Mg ;DC_FET^r_FET QjmTrBceiiDram图2.3 ATF35176的直流特性2.3 偏置电路的设计创建一个新的原理图,在原理图中放入 ATF35176的模型和DA_FETBias 控 件,选择Transistor Bias Utility 设置偏置电路的属性。

仿真后有三个偏置电路可 以选择。

有两个网络里面,晶体管的源极是有电阻的,但通常低噪放大器的设计 中,源级只接反馈电感(微带线),所以选用第一个偏置网络。

选定网络后,得 到了偏置子电路,按照子电路画出偏置原理图,其中偏置子电路中一些电阻值不 是常规标称值,仅是理论计算结果,用相近的常规标称值代替。

X3一一'4D !"E hfe rkenm 1 ta updjie 阊物的MS.0««4«»mA 1.1.354 V Ug e= UI 5 汗 7图2.4偏置电路原理图图2.6完成后的偏置电路原理图2.4稳定性分析1.进行S参数的仿真,添加控件Term、StabFact MaxGain。

放大器的直流和交流之间的通路要添加射频直流电路,它的实质是一个无源低通电路,使直流偏置信号能传输到晶体管引脚,而晶体管的射频信号不能进入直流通路,在这里先用【DC—Feed!直流电感代替。

同时,直流偏置信号不能传到两端的Term, 需加隔直电容,【DC_Block】隔直电容代替。

图2.7加入理想直流扼流和射频扼流的原理图图2.8最大增益和稳定系数曲线仿真结束后,显示 MaxGainl 和Stabfactl 两个图表中观察,从图2.8我们可 以看出,在5.8GHz 时,最大增益为18.042dB,稳定系数为K=0.646,绝对稳定 系数K<1,说明电路不稳定。

2 .当电路不稳定时,可以采用负反馈电路形式解决问题,提高绝对稳定系数。

本次设计中在漏极添加用联电感作为负反馈。

通过反复调节反馈电路,也就是用 联电感的数值,使其在整个工作频率范围内稳定。

!¥__L■ , । g tJ3m2『七 gdOOGH 工mi|帖平$总1OGW 上M.:A?4mW 八心厂5£500-上 MfiavGaln 1^-16 042 mH陋厂5至0&也11Q 及丽1=17 833g e#图2.9晶体管源级添加负反馈后的原理图m2■rvipieOOGMz siarrai r i=:i ”mH f'eipSBiOGHz Y 制alirWiIRCW nrno E3 G 软”1上 川;7E 涧1看16氐ZJmn•卡-力・.・ b.n "fl r - = i 53 .接下来把理想的DC_Feed DC_Block 和源极的两个电感改成实际的器件 和微带线。

本设计选用MuRata (日本村田公司)的电感和电容。

本设计中电源部分 用了扼流电感LGQ18和GRM18 ,对射频信号进行阻隔和旁路。

然后用给定的电 感值算出等效的传输线的长度(l = U1L,其中L 是电感值即0.3nH, Z O 是微ZO 、r带线特征阻抗,得到l=0.58mm )。

全部换成真实器件和微带线后,稳定系数和增 益基本达到要求。

图2.12最大增益和稳定系数曲线2.5噪声系数圆和输入匹配当最大增益和稳定系数达到指标后,接下来就要设计一个适当的输入匹配网络来实现最小噪声系数。

先进行仿真,在数据显示窗口面板,输入等式:cird^DaiA=n9<j&lrch9{NFmiir<mdxh1PX)i J l D^lNFmin[indK]l Sop4LindA].ltelindK^5O St)GaCind &-ga_cITE I e (S[me*i| klajdUainl |indx|-;U 0,S 1 2 31 51)Lwi图 2.11 全部换成真实器件后的原理图(ie-J=5 SOOGKU stabF ^11=1 WEmi帕中5mDGH±l.'lHXGain1 =mlO gSGSDGH 上Mar^air1 = l3IH11D5XHZ.MS!KGainl=l5 121它们代表的意思分别是返回值是前面定义的 ml 的频率,即5.8GHz;返回噪声系数圆;返回增益圆。

-二GflC" * A41SoCiK 看/南J 125.175WtSfMiH* 徽皿重事■而.中上彳口 +过4蝴rnF■ os pirn 5> 11白工 le £“H 印 J .47.53StM Kgur<=0Jit2525B■npcdEf aJT 《知rgtlM ・会一一 「■:..: I ! J. QUirWWmhfi peddfit± ■. a + BLlda * a 3蚪图2.14 circleData 和GaCircle 的史密斯圆图查看史密斯圆图,选择合适的阻抗值,在设计时,必须在增益和噪声系数之 间做一个权衡,而低噪放大器,首先要考虑最小噪声系数。

那么最优的输入端阻 抗就定为 m5点的阻抗(43.15+j*25.60 Q),通过使用DA_Smith Chart Match 工具, 对电路进行输入匹配。

P^nNufnb^GPyi 3 B5 :;A2XJAf^'Srri1hC 2切工⑻图 2.14 加入 DA_Smith Chart Match 工具, Xi ■与 EM” - -T-Ittfh 1■ ,■, linD-0 Rough-O nmC3.Iwn ..IwM "H UE M'Z"5D &iri图 2.15 设置DA_Smith Chart Match 参数图2.16设置Smith Chart Utility 工具的阻抗o-■P M -P1Nim*1Ir.n5I.L=1 pTLIN , -TL2Z*50 OhmE-17:OF«5,B GHtoPEP2Num»2图2.18匹配子线路EH片 m 白「1 t=5TPtetf 5,SD0GI-Le# 平rrl 尸?; 7 15图2.19匹配后输入阻抗TI9 lTEq^5EnflGRzdB(S(2,))1C 您屋蛇5 3mHi-:1R5(1 l)> VD022.6最大增益的输出匹配输出端的匹配需要此时晶体管的输出端阻抗,插入Zin控件,查看输出阻抗的实部和虚部,得到输出阻抗为28.109-j*12.593Q,为了达到最大增益,输出匹配要50Q匹配到Zin的共腕。