4511;中文规格书,Datasheet资料

MW6S004NT1;中文规格书,Datasheet资料

RF Power Field Effect TransistorN-Channel Enhancement-Mode Lateral MOSFETDesigned for Class A or Class AB base station applications with frequencies up to 2000 MHz. Suitable for analog and digital modulation and multicarrier amplifier applications.•Typical Two-Tone Performance @ 1960 MHz, 28 Volts, I DQ = 50 mA, P out = 4 Watts PEP Power Gain — 18 dB Drain Efficiency — 33%IMD — -34 dBc•Typical Two-Tone Performance @ 900 MHz, 28 Volts, I DQ = 50 mA, P out = 4 Watts PEP Power Gain — 19 dB Drain Efficiency — 33%IMD — -39 dBc•Capable of Handling 5:1 VSWR, @ 28 Vdc, 1960 MHz, 4 Watts CW Output Power Features•Characterized with Series Equivalent Large-Signal Impedance Parameters •On-Chip RF Feedback for Broadband Stability •Integrated ESD Protection •RoHS Compliant•In Tape and Reel. T1 Suffix = 1000 Units per 12 mm, 7 inch Reel.Table 1. Maximum RatingsRatingSymbol Value Unit Drain-Source Voltage V DSS -0.5, +68Vdc Gate-Source Voltage V GS -0.5, +12Vdc Storage Temperature Range T stg -65 to +150°C Operating Junction TemperatureT J150°CTable 2. Thermal CharacteristicsCharacteristicSymbol Value (1,2)Unit Thermal Resistance, Junction to CaseCase Temperature 76°C, 4 W PEP , Two-Tone Case Temperature 79°C, 4 W CWR θJC8.88.5°C/WTable 3. ESD Protection CharacteristicsTest MethodologyClass Human Body Model (per JESD22-A114)1C (Minimum)Machine Model (per EIA/JESD22-A115) A (Minimum)Charge Device Model (per JESD22-C101)IV (Minimum)1.MTTF calculator available at /rf. Select Software & Tools/Development Tools/Calculators to access MTTF calculators by product.2.Refer to AN1955, Thermal Measurement Methodology of RF Power Amplifiers. Go to /rf. Select Documentation/Application Notes - AN1955.Document Number: MW6S004NRev. 4, 6/2009Freescale Semiconductor Technical DataMW6S004NT1Table 4. Moisture Sensitivity LevelTest MethodologyRating Package Peak TemperatureUnit Per JESD 22-A113, IPC/JEDEC J-STD-0203260°CTable 5. Electrical Characteristics (T A = 25°C unless otherwise noted)CharacteristicSymbolMinTypMaxUnitOff CharacteristicsZero Gate Voltage Drain Leakage Current (V DS = 68 Vdc, V GS = 0 Vdc)I DSS ——10μAdc Zero Gate Voltage Drain Leakage Current (V DS = 28 Vdc, V GS = 0 Vdc)I DSS ——10μAdc Gate-Source Leakage Current (V GS = 5 Vdc, V DS = 0 Vdc)I GSS——500nAdcOn CharacteristicsGate Threshold Voltage(V DS = 10 Vdc, I D = 50 mAdc)V GS(th) 1.22 2.7Vdc Gate Quiescent Voltage(V DS = 28 Vdc, I D = 50 mAdc)V GS(Q)— 2.7—Vdc Fixture Gate Quiescent Voltage (1)(V DD = 28 Vdc, I D = 50 mAdc, Measured in Functional Test)V GG(Q) 2.23 4.2Vdc Drain-Source On-Voltage(V GS = 10 Vdc, I D = 50 mAdc)V DS(on)—0.270.37VdcDynamic CharacteristicsReverse Transfer Capacitance(V DS = 28 Vdc ± 30 mV(rms)ac @ 1 MHz, V GS = 0 Vdc)C rss —21—pF Output Capacitance(V DS = 28 Vdc ± 30 mV(rms)ac @ 1 MHz, V GS = 0 Vdc)C oss —25—pF Input Capacitance(V DS = 28 Vdc, V GS = 0 Vdc ± 30 mV(rms)ac @ 1 MHz)C iss—30—pFFunctional Tests (In Freescale Test Fixture, 50 ohm system) V DD = 28 Vdc, I DQ = 50 mA, P out = 4 W PEP , f1 = 1960 MHz, f2 = 1960.1 MHz, Two-Tone Test Power Gain G ps 16.51820dB Drain EfficiencyηD 2833—%Intermodulation Distortion IMD —-34-28dBc Input Return LossIRL—-12-10dBTypical Performance (In Freescale 900 MHz Demo Board, 50 ohm system) V DD = 28 Vdc, I DQ = 50 mA, P out = 4 W PEP , f = 900 MHz, Two-Tone Test, 100 kHz Tone Spacing Power Gain G ps —19—dB Drain EfficiencyηD —33—%Intermodulation Distortion IMD —-39—dBc Input Return LossIRL—-12—dB1.V GG = 11/10 x V GS(Q). Parameter measured on Freescale Test Fixture, due to resistive divider network on the board. Refer to Test Circuit Schematic.MW6S004NT1Figure 1. MW6S004NT1 Test Circuit SchematicZ70.210″ x 1.220″ Microstrip Z80.054″ x 0.680″ Microstrip Z90.054″ x 0.260″ Microstrip Z100.025″ x 0.930″ MicrostripPCBArlon CuClad 250GX-0300-55-22, 0.020″, εr = 2.5Z10.054″ x 0.430″ Microstrip Z20.054″ x 0.137″ Microstrip Z30.580″ x 0.420″ Microstrip Z40.580″ x 0.100″ Microstrip Z50.025″ x 0.680″ Microstrip Z60.210″ x 0.100″ MicrostripV SUPPLYTable 6. MW6S004NT1 Test Circuit Component Designations and ValuesPartDescriptionPart Number Manufacturer C1100 nF Chip Capacitor CDR33BX104AKYS Kemet C2, C3, C6, C79.1 pF Chip Capacitors ATC100B9R1CT500XT ATC C4, C510 μF, 50 V Chip Capacitors GRM55DR61H106KA88B Murata C810 μF, 35 V Tantalum Chip Capacitor T490D106K035AT Kemet R1 1 k Ω, 1/4 W Chip Resistor CRCW12061001FKEA Vishay R210 k Ω, 1/4 W Chip Resistor CRCW12061002FKEA Vishay R310 Ω, 1/4 W Chip ResistorCRCW120610R0FKEAVishayMW6S004NT1Figure 2. MW6S004NT1 Test Circuit Component LayoutMW6S004NT1TYPICAL CHARACTERISTICS1420191716G p s , P O W E R G A I N (d B )100.1TWO−TONE SPACING (MHz)1100Figure 6. Intermodulation Distortion Productsversus Tone Spacing 26P in , INPUT POWER (dBm)1618222414Figure 7. Pulsed CW Output Power versusInput PowerI M D , I N T E R M O D U L A T I O N D I S T O R T I O N (d B c )181520MW6S004NT1TYPICAL CHARACTERISTICSA C P R (dB )−70P out , OUTPUT POWER (WATTS) AVG.50−2040−3030−4020−5010−600.01110Figure 8. Single-Carrier CDMA ACPR, Power Gainand Drain Efficiency versus Output PowerP out , OUTPUT POWER (WATTS) CWFigure 10. Power Gain versus Output Power 7151906171618234G p s , P O W E R G A I N (d B )1800−250f, FREQUENCY (MHz)Figure 11. Broadband Frequency Response−5−10−15−20210020502000195019001850S 11 (d B )851ηD , D R A I N E F F I C I E N C Y (%), G p s , P O W E R G A I N (d B )0.118.517.516.515.5MW6S004NT1TYPICAL CHARACTERISTICS25010790T J , JUNCTION TEMPERATURE (°C)Figure 12. MTTF versus Junction TemperatureThis above graph displays calculated MTTF in hours when the device is operated at V DD = 28 Vdc, P out = 4 W PEP, and ηD = 33%.MTTF calculator available at /rf. Select Software & Tools/Development Tools/Calculators to access MTTF calculators by product.106105104110130150170190M T T F (H O U R S )210230MW6S004NT1f = 1930 MHzZ o = 10 ΩZ loadZ sourcef = 1990 MHzf = 1930 MHzf = 1990 MHzV DD = 28 Vdc, I DQ = 50 mA, P out = 4 W PEPfMHzZ sourceWZ loadW1930 1.96 - j5.348.78 + j6.961960 1.89 - j5.108.93 + j7.461990 1.82 - j4.859.11 + j7.97Z source=Test circuit impedance as measured fromgate to ground.Z load=Test circuit impedance as measured fromdrain to ground.Z source Z loadOutputMatchingNetworkFigure 13. Series Equivalent Source and Load ImpedanceMW6S004NT1Table 7. Common Source Scattering Parameters (V DD = 28 V, 50 ohm system)I DQ = 50 mAf MH S 11S 21S 12S 22MHz |S 11|∠φ|S 21|∠φ|S 12|∠φ|S 22|∠φ5000.649-116.3407.902105.4200.056-73.7500.548-33.5705500.695-121.6807.50298.7900.053-80.5700.593-41.4806000.733-126.5607.11192.3800.049-87.0100.632-48.8906500.770-131.340 6.69986.2900.045-93.2800.669-56.0007000.800-135.740 6.30280.4500.041-99.1200.701-62.8107500.827-140.030 5.92274.8500.038-104.8500.727-69.2908000.848-143.950 5.55269.6300.035-110.1100.750-75.3508500.866-147.690 5.22064.5800.032-115.2200.770-81.1309000.882-151.140 4.89159.9700.029-119.9600.786-86.5709500.895-154.560 4.59755.4900.026-124.7900.800-91.73010000.907-157.590 4.31551.2400.024-129.0900.813-96.66010500.916-160.540 4.06047.1700.022-133.3700.824-101.34011000.923-163.310 3.81943.3400.020-137.4600.833-105.79011500.929-165.930 3.60139.6500.018-141.4400.840-110.05012000.935-168.430 3.39836.1100.017-145.3300.847-114.17012500.938-170.770 3.21032.7400.015-149.5400.851-118.06013000.942-173.030 3.03629.4900.014-153.4300.856-121.88013500.945-175.140 2.87526.3600.013-157.4600.859-125.52014000.948-177.170 2.72823.3300.012-161.9100.863-129.02014500.951-179.090 2.59020.4400.011-166.1800.866-132.39015000.953179.030 2.46417.6400.010-170.6300.869-135.65015500.954177.270 2.34714.9200.009-174.8900.872-138.76016000.955175.570 2.24012.3200.008179.9500.875-141.75016500.956173.980 2.1399.7400.008173.9200.877-144.65017000.957172.350 2.0477.2500.007167.7100.880-147.48017500.957170.800 1.958 4.8100.007161.8100.882-150.18018000.958169.340 1.879 2.4400.006155.3700.884-152.76018500.959167.920 1.8060.2600.006148.9400.886-155.23019000.959166.510 1.736-1.9800.005142.6300.887-157.58019500.960165.200 1.668-4.3100.005136.7400.888-160.05020000.959163.800 1.611-6.2400.005129.9100.890-162.07020500.959162.420 1.555-8.2900.005123.8100.891-164.19021000.958161.170 1.504-10.2700.005118.2000.892-166.14021500.958159.840 1.456-12.2100.005112.7400.893-168.06022000.957158.560 1.412-14.1300.005108.4600.894-169.84022500.957157.160 1.372-16.0100.005103.8400.896-171.61023000.955155.870 1.334-17.8700.00599.3100.896-173.26023500.954154.510 1.300-19.7000.00595.3600.897-174.83024000.953153.120 1.268-21.5100.00591.0300.898-176.39024500.953151.7301.238-23.2500.00587.4600.899-177.840MW6S004NT1Table 7. Common Source Scattering Parameters (V DD = 28 V, 50 ohm system) (continued)I DQ = 50 mAf MH S 11S 21S 12S 22MHz |S 11|∠φ|S 21|∠φ|S 12|∠φ|S 22|∠φ25000.952150.340 1.211-25.1200.00684.1600.899-179.27025500.950149.010 1.187-26.9200.00680.7800.897179.42026000.949147.380 1.166-28.6500.00677.8800.897178.12026500.948145.920 1.144-30.4200.00774.6700.898176.84027000.944144.200 1.121-32.3100.00771.3600.896175.48027500.944142.790 1.105-34.2300.00767.9800.897174.06028000.943141.020 1.088-36.0000.00763.9500.897172.93028500.941139.410 1.073-37.8700.00761.2300.896171.63029000.940137.640 1.058-39.7600.00859.8100.896170.33029500.938135.900 1.045-41.6800.00858.2800.896169.04030000.937133.8601.032-43.6100.00856.7400.895167.510分销商库存信息: FREESCALEMW6S004NT1。

XL4501规格书(中文版)

宽输入电压范围n输出电压从1.25V到32V可调n最小压差0.3Vn固定150KHz开关频率n最大5A开关电流n内置功率MOSn出色的线性与负载调整率n内置恒流环路n内置频率补偿功能n内置输出短路保护功能n内置输入过压保护功能n内置热关断功能n TO263-5L封装应用n车载充电器n电池充电器n LCD电视与显示屏n便携式设备供电n通讯设备供电n降压恒流驱动n显示器LED背光n通用LED照明描述XL4501是一款高效降压型DC-DC转换器,可工作在DC8V到36V输入电压范围,低纹波,内置功率MOS。

XL4501内置固定频率振荡器与频率补偿电路,简化了电路设计。

PWM控制环路可以调节占空比从0~100%之间线性变化。

内置输出过电流保护功能。

内部补偿模块可以减少外围元器件数量。

图1.XL4501封装150KHz 36V 5A开关电流自带恒流环路降压型DC-DC转换器XL4501 引脚配置图2. XL4501引脚配置表1.引脚说明引脚号引脚名称引脚描述1 GND 接地引脚。

2 FB 反馈引脚,通过外部电阻分压网络,检测输出电压进行调整,参考电压为1.25V。

3 SW 功率开关输出引脚,SW是输出功率的开关节点。

4 CS 输出电流检测引脚(IOUT=0.11V/RCS)。

5 VIN 输入电压,支持DC8V~36V宽范围电压操作,需要在VIN与GND 之间并联电解电容以消除噪声。

150KHz 36V 5A开关电流自带恒流环路降压型DC-DC转换器XL4501 方框图图3. XL4501方框图典型应用图4. XL4501系统参数测量电路150KHz 36V 5A开关电流自带恒流环路降压型DC-DC转换器XL4501典型应用(降压LED恒流驱动)ILED=0.11V/RCS图5.XL4501系统参数测量电路(LED恒流驱动)订购信息产品型号打印名称封装方式包装类型XL4501E1 XL4501E1 TO263-5L 800只每卷XLSEMI无铅产品,产品型号带有“E1”后缀的符合RoHS标准。

TEA1753TN1,518;中文规格书,Datasheet资料

2.4 Flyback green features

Valley switching for minimum switching losses (NXP patented) Frequency reduction with adjustable minimum peak current at low-power operation to maintain high efficiency at low output power levels

3 ofductors

TEA1753T

HV start-up flyback controller with integrated PFC controller

5. Block diagram

3)&'5,9(5 3)& GULYHU

TEA1753T

HV start-up DCM/QR flyback controller with integrated DCM/QR PFC controller

Rev. 3 — 24 August 2012 Product data sheet

1. General description

The TEA1753T is the third generation of green Switched Mode Power Supply (SMPS) controller ICs. The TEA1753T combines a controller for Power Factor Correction (PFC) and a flyback controller. Its high level of integration allows the design of a cost-effective power supply with a very low number of external components. The special built-in green functions provide high efficiency at all power levels. This efficiency applies to quasi-resonant operation at high-power levels, quasi-resonant operation with valley skipping, as well as reduced frequency operation at lower power levels. At low-power levels, the PFC switches off to maintain high efficiency. During low-power conditions, the flyback controller switches to frequency reduction mode and limits the peak current to an adjustable minimum value. This mode ensures high efficiency at low-power and good standby power performance while minimizing audible noise from the transformer. The controller is switched to the power-down mode for no-load operation. In this mode, the controller is shut down for very low standby power applications. The TEA1753T is a Multi-Chip Module, (MCM), containing two chips. The proprietary high-voltage BCD800 process which makes direct start-up possible from the rectified universal mains voltage in an effective and green way. The second low voltage Silicon On Insulator (SOI) is used for accurate, high-speed protection functions and control. The TEA1753T enables the design of highly efficient and reliable supplies with power requirements of up to 250 W using the minimum number of external components. Remark: All values provided throughout this data sheet are typical values unless otherwise stated.

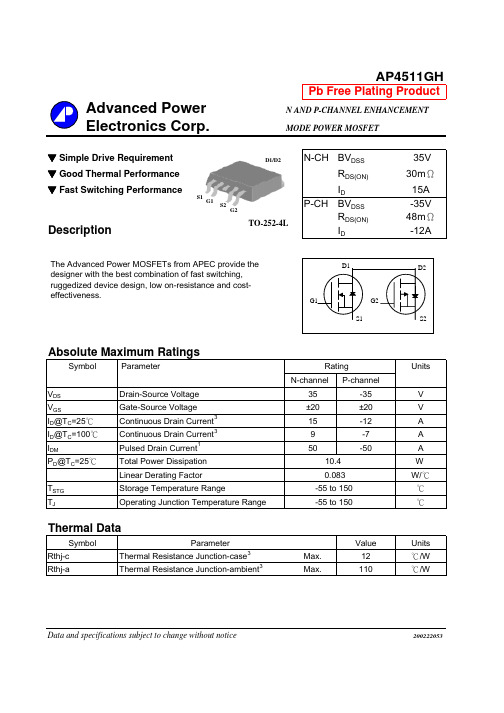

AP4511GH资料

25

Q G , Total Gate Charge (nC)

Fig 7. Gate Charge Characteristics

100

100us

10

ID (A)

1

T C =25 o C Single Pulse

1ms

10ms 100ms

DC

0.1

0.1

1

10

100

V DS , Drain-to-Source Voltage (V)

Parameter Forward On Voltage2 Reverse Recovery Time2

Reverse Recovery Charge

Test Conditions IS=-6A, VGS=0V IS=-6A, VGS=0V dI/dt=-100A/µs

Min. Typ. Max. Units

BVDSS

ΔBVDSS/ΔTj

RDS(ON)

VGS(th) gfs IDSS

IGSS Qg Qgs Qgd td(on) tr td(off) tf Ciss Coss Crss Rg

Drain-Source Breakdown Voltage VGS=0V, ID=250uA

Breakdown Voltage Temperature Coefficient Reference to 25℃, ID=1mA Static Drain-Source On-Resistance2 VGS=10V, ID=8A

Fig 6. Gate Threshold Voltage v.s. Junction Temperature

元器件交易网

N-Channel

14

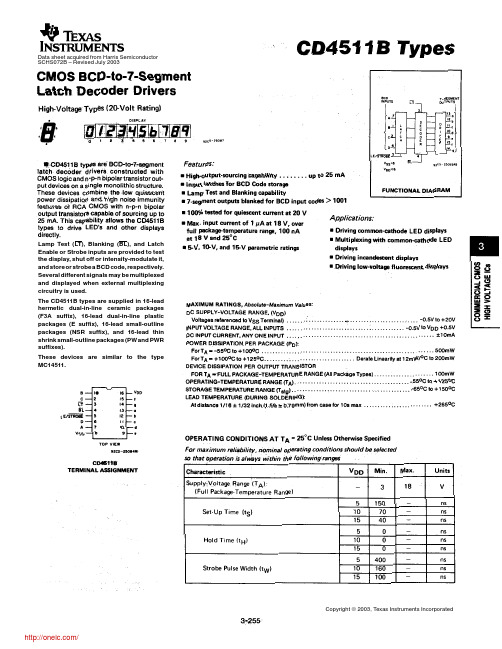

CD4511BNSR;CD4511BPWR;CD4511BE;CD4511BPWRE4;CD4511BPWRG4;中文规格书,Datasheet资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)CD4511BE ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeCD4511BEE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg Type CD4511BF ACTIVE CDIP J161TBD A42N/A for Pkg Type CD4511BF3A ACTIVE CDIP J161TBD A42N/A for Pkg Type CD4511BNSR ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BNSRE4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BNSRG4ACTIVE SO NS162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPWE4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMCD4511BPWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant CD4511BNSR SO NS 162000330.016.48.210.5 2.512.016.0Q1CD4511BPWRTSSOPPW162000330.012.46.95.61.68.012.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) CD4511BNSR SO NS162000367.0367.038.0CD4511BPWR TSSOP PW162000367.0367.035.0分销商库存信息:TICD4511BNSR CD4511BPWR CD4511BECD4511BPWRE4CD4511BPWRG4CD4511BNSRE4 CD4511BNSRG4CD4511BEE4CD4511BPW CD4511BPWE4CD4511BPWG4。

4511GM

-

9

-

S

-

- -1 uA

-

- -25 uA

-

- ±100 nA

- 10 16 nC

-

2

- nC

-

6

- nC

- 10 - ns

-

6

- ns

- 26 - ns

-

7

- ns

- 690 1100 pF

- 165 - pF

- 130 - pF

- 5.2 7.8 Ω

Source-Drain Diode

Symbol VSD trr Qrr

The SO-8 package is universally preferred for all commercialindustrial surface mount applications and suited for low voltage applications such as DC/DC converters.

50

T A = 150 o C

40

30

20

10V 7.0V 5.0V

4.5V

10

V G =3.0V

0

0

1

2

3

4

5

V DS , Drain-to-Source Voltage (V)

Fig 2. Typical Output Characteristics

1.8

1.6

ID=7A

V G =10V

1.4

1.2

Min. Typ. Max. Units

-

- 1.2 V

- 18 - ns

- 12 - nC

AP4511GM

CD4511中文资料

A→Y

-

BI → Y

-

BI → Y

-

LT → Y LT → Y

-

tTHL 传输转换时间

-

tTLH 传输转换时间

-

tW LE 脉冲宽度

400 160 100 150 70 40 0 0 0

tSU 建立时间

-

ns

tH 保持时间

-

ns

C1 输入电容 (任一输入端)

7.5

pF

动态特性(TA=25℃) : 参数 tPLH 传输延 迟时间 tPHL 传输延 迟时间 tPLH 传输延 迟时间 tPHL 传输延 迟时间 tPLH 传输延 迟时间 tPHL 传输延 迟时间 A→Y 测试条件 CL=50pF RL=200k tr=20ns tf=20ns VDD(V) 最小 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 规范值 最大 1040 420 300 800 350 300 700 350 250 300 150 100 500 250 170 310 185 160 100 75 65 ns ns ns 单位

BI

LE

输出消隐控制端 数据锁定控制 灯测试 正电源 地 数据输出端

LT

VDD Vss Ya~Yg 功能表

静态特性: 参数 IoH (mA) VOL 输出低电 平电压 (最大) VOH 输出高电 平电压 (最小) VIL 输入低电平 电压 (最大) VIH 输入高电平 电压 (最小) VOH 输出高电 平驱动电压 (最小) 测试条件 V0 (V) V1 (V) 5/0 10/0 15/0 5/0 10/0 15/0 VDD (V) 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 10.0 15.0 5.0 4.0 3.8 -3.55 3.4 9.0 8.85 8.7 8.6 14.0 13.9 13.75 13.65 0.64 1.6 4.2 5.0 10.0 20.0 0.61 1.5 4.0 ±0.1 5.0 10.0 20.0 4.0 9.0 14.0 -55℃ -40℃ 规范值 25℃ 0.05 85℃ 125℃ 单 位 V

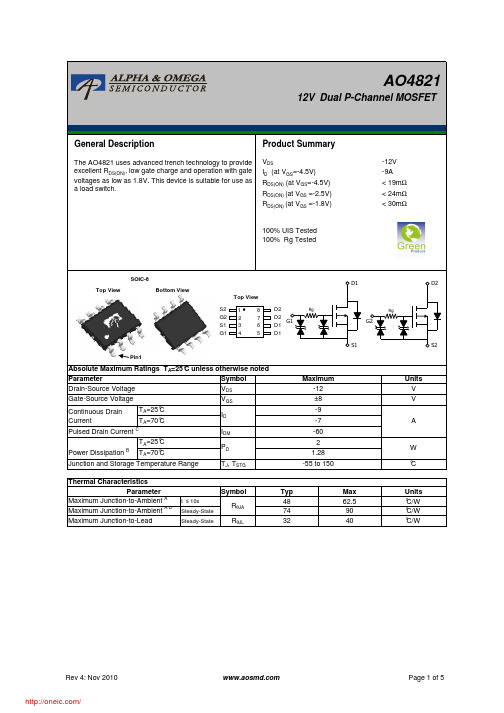

AO4821;中文规格书,Datasheet资料

100% UIS Tested 100% Rg TestedSymbol V DS V GSI DM T J , T STGSymbolt ≤ 10s Steady-State Steady-StateR θJLW 2Maximum Junction-to-Lead°C/W°C/W Maximum Junction-to-Ambient A D 329040Maximum Junction-to-Ambient A T A =25°C T A =70°C Power DissipationBP D Pulsed Drain Current CContinuous Drain CurrentT A =25°C AI D -9-7-60V MaximumUnits Parameter Absolute Maximum Ratings T A =25°C unless otherwise noted V ±8Gate-Source Voltage Drain-Source Voltage -12°C/W R θJA 487462.5°CThermal Characteristics Units ParameterTyp Max 1.28T A =70°CJunction and Storage Temperature Range -55 to 150G1S1G2S2D1D1D2D224513867 Top ViewSOIC-8Top View Bottom ViewPin1G1D11S1RgG2D2S2RgSymbolMin Typ Max Units BV DSS -12VV DS =-12V, V GS =0V-1T J =55°C-5I GSS ±10µA V GS(th)Gate Threshold Voltage -0.35-0.53-0.85V I D(ON)-60A 1619T J =125°C22271924m Ω2330m Ωg FS 45S V SD -0.56-1V I S-3A C iss 139017402100pF C oss 230334435pF C rss 120200280pF R g0.9 1.3 1.7k ΩQ g (4.5V)151923nC Q gs 3.6 4.5 5.4nC Q gd 35.37.4nC t D(on)240ns t r 580ns t D(off)7µs t f 4.2µst rr 182226ns Q rr141720nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery TimeDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-4.5V, V DS =-5V V GS =-4.5V, I D =-9AReverse Transfer Capacitance I F =-9A, dI/dt=500A/µsV GS =0V, V DS =-6V, f=1MHz SWITCHING PARAMETERS Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions I DSS µA V DS =V GS I D =-250µA V DS =0V, V GS = ±8V Zero Gate Voltage Drain Current Gate-Body leakage current Forward Transconductance Diode Forward VoltageR DS(ON)Static Drain-Source On-Resistancem ΩI S =-1A,V GS =0VV DS =-5V, I D =-9A V GS =-1.8V, I D =-6AV GS =-2.5V, I D =-8A Gate resistanceV GS =0V, V DS =0V, f=1MHzTurn-Off Fall TimeTotal Gate Charge V GS =-4.5V, V DS =-6V, I D =-9AGate Source Charge Gate Drain Charge Body Diode Reverse Recovery Charge I F =-9A, dI/dt=500A/µsMaximum Body-Diode Continuous CurrentInput Capacitance Output CapacitanceTurn-On DelayTime DYNAMIC PARAMETERS Turn-On Rise Time Turn-Off DelayTime V GS =-4.5V, V DS =-6V, R L =0.67Ω,R GEN =3ΩA. The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design.B. The power dissipation P D is based on T J(MAX)=150°C, using ≤ 10s junction-to-ambient thermal resistance.C. Repetitive rating, pulse width limited by junction temperature T J(MAX)=150°C. Ratings are based on low frequency and duty cycles to keep initialT J =25°C.D. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.E. The static characteristics in Figures 1 to 6 are obtained using <300µs pulses, duty cycle 0.5% max.F. These curves are based on the junction-to-ambient thermal impedence which is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, assuming a maximum junction temperature of T J(MAX)=150°C. The SOA curve provides a single pulse ratin g.TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS5101520Q g (nC)Figure 7: Gate-Charge Characteristics-V G S (V o l t s )24681012-V DS (Volts)Figure 8: Capacitance Characteristics C a p a c i t a n c e (p F )VdsCharge Gate Charge Test Circuit & WaveformD iode RVVddVddVR esistive S w itching Test C ircuit & W aveform s分销商库存信息: AOSAO4821。

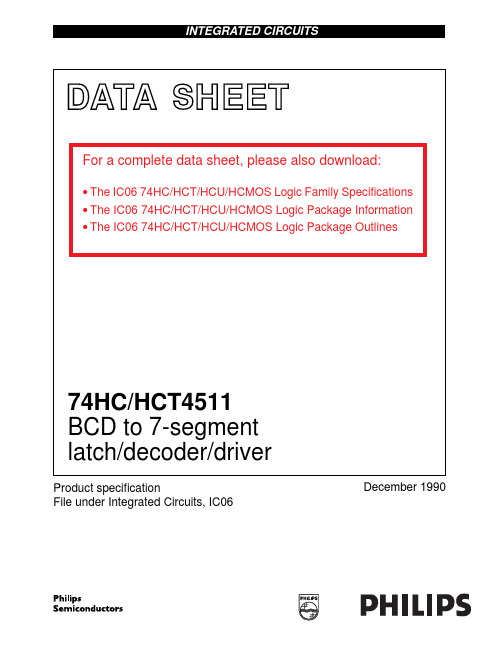

74HC4511_DataSheet

DATA SHEETProduct specificationFile under Integrated Circuits, IC06December 199074HC/HCT4511BCD to 7-segment latch/decoder/driverFor a complete data sheet, please also download:•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications •The IC06 74HC/HCT/HCU/HCMOS Logic Package Information •The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURES•Latch storage of BCD inputs •Blanking input •Lamp test input•Driving common cathode LED displays •Guaranteed 10 mA drive capability per output •Output capability: non-standard •I CC category: MSI GENERAL DESCRIPTIONThe 74HC/HCT4511 are high-speed Si-gate CMOSdevices and are pin compatible with “4511” of the “4000B”series. They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT4511 are BCD to 7-segmentlatch/decoder/drivers with four address inputs (D 1 to D 4),an active LOW latch enable input (LE), an active LOW ripple blanking input (BI), an active LOW lamp test input (LT), and seven active HIGH segment outputs (Q a to Q g ).When LE is LOW, the state of the segment outputs (Q a to Q g ) is determined by the data on D 1 to D 4.When LE goes HIGH, the last data present on D 1 to D 4 are stored in the latches and the segment outputs remain stable.When LT is LOW, all the segment outputs are HIGHindependent of all other input conditions. With LT HIGH, a LOW on BI forces all segment outputs LOW. The inputs LT and BI do not affect the latch circuit.APPLICATIONS •Driving LED displays•Driving incandescent displays •Driving fluorescent displays •Driving LCD displays•Driving gas discharge displaysQUICK REFERENCE DATAGND =0 V; T amb =25°C; t r =t f =6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D =C PD ×V CC 2×f i +∑(C L ×V CC 2×f o ) where:f i =input frequency in MHz f o =output frequency in MHz ∑(C L ×V CC 2×f o )=sum of outputs C L =output load capacitance in pF V CC =supply voltage in V2.For HC the condition is V I =GND to V CCFor HCT the condition is V I =GND to V CC −1.5 VSYMBOL PARAMETER CONDITIONS TYPICAL UNITHCHCTt PHL / t PLHpropagation delay C L =15 pF; V CC =5VD n to Q n 2424ns LE to Q n 2324ns BI to Q n 1920ns LT to Q n1213nsC I input capacitance3.5 3.5pF C PD power dissipation capacitance per latchnotes 1 and 26464pFORDERING INFORMATIONSee“74HC/HCT/HCU/HCMOS Logic Package Information”.PIN DESCRIPTIONPIN NO.SYMBOL NAME AND FUNCTION3LT lamp test input (active LOW)4BI ripple blanking input (active LOW)5LE latch enable input (active LOW)7, 1, 2, 6D1 to D4BCD address inputs8GND ground (0 V)13, 12, 11, 10, 9, 15, 14Q a to Q g segments outputs16V CC positive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.Fig.3 IEC logic symbol.FUNCTION TABLENote1.Depends upon the BCD-code applied during the LOW-to-HIGH transition of LE.H =HIGH voltage level L =LOW voltage level X = don’t careINPUTSOUTPUTS DISPLAYLE BI LT D 4D 3D 2D 1Q a Q b Q c Q d Q e Q f Q g X X L X X X X H H H H H H H 8X L H X X X X L L L L L L L blank L L L L H H H H H H H H L L L L L L L L L L H H L H L H H L H H H H H H H H L H H L H H H L H L H L L L L L H H 0123L L L L H H H H H H H H L L L L H H H H L L H H L H L H L H L H H L L H H H H H L H H L L L H L H H H L H H H L 4567L L L L H H H H H H H H H H H H L L L L L L H H L H L H H H L L H H L L H H L L H L L L H L L L H H L L H H L L 89blank blank L L L L H H H H H H H H H H H H H H H H L L H H L H L H L L L LL L L LL L L LL L L LL L L LL L L LL L L Lblank blank blank blankH HHXXXX(1)(1)Fig.4 Functional diagram.Fig.5 Logic diagram. Fig.6 Segment designation.Fig.7 Display.DC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standard, excepting V OH which is given belowI CC category: MSINon-standard DC characteristics for 74HCVoltages are referenced to GND (ground=0 V)SYMBOL PARAMETERT amb (°C)UNITTESTCONDITIONS74HCV CC(V)V I−I O(mA) +25−40to+85−40to+125min.typ.max.min.max.min.max.V OH HIGH level output voltage 3.983.603.843.353.703.10V 4.5V IH orV IL7.510.0V OH HIGH level output voltage 5.605.484.805.455.344.505.355.204.20V 6.0V IH orV IL7.510.015.0AC CHARACTERISTICS FOR 74HC GND=0 V; t r=t f=6 ns; C L=50 pFSYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayD n to Q n 772822300605137575644509077ns 2.04.56.0Fig.8t PHL/ t PLH propagation delayLE to Q n 742722270544633068584058169ns 2.04.56.0Fig.9t PHL/ t PLH propagation delayBI to Q n 612218220443727555473306656ns 2.04.56.0Fig.10t PHL/ t PLH propagation delayLT to Q n 411512150302619038332254538ns 2.04.56.0Fig.8t THL/ t TLH output transition time19767515139519161102219ns 2.04.56.0Figs 8, 9 and10t W latch enable pulse widthLOW 801614114310020171202420ns 2.04.56.0Fig.9t su set-up timeD n to LE 6012101454751513901815ns 2.04.56.0Fig.11t h hold timeD n to LE 0−11−4−3ns 2.04.56.0Fig.11DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standard, excepting V OH which is given below I CC category: MSINon-standard DC characteristics for 74HCT Voltages are referenced to GND (ground =0 V)Note to HCT typesThe value of additional quiescent supply current (∆I CC ) for a unit load of 1 is given in the family specifications.To determine ∆I CC per input, multiply this value by the unit load coefficient shown in the table below.SYMBOLPARAMETERT amb (°C)UNITTEST CONDITIONS74HCT V CC (V)V I−I O (mA)+25−40to +85−40to +125min.typ.max.min.max.min.max.V OHHIGH level output voltage3.983.603.843.353.703.10V4.5V IH or V IL 7.510.0INPUT UNIT LOAD COEFFICIENT LT,LE BI, D n1.500.30AC CHARACTERISTICS FOR 74HCT GND=0 V; t r=t f=6 ns; C L=50 pFSYMBOL PARAMETERT amb(°C)UNITTEST CONDITIONS74HCTV CC(V)WAVEFORMS +25−40to+85−40to+125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delayD n to Q n28607590ns 4.5Fig.8t PHL/ t PLH propagation delayLE to Q n27546881ns 4.5Fig.9t PHL/ t PLH propagation delayBI to Q n23445566ns 4.5Fig.10t PHL/ t PLH propagation delayLT to Q n16303845ns 4.5Fig.8t THL/ t TLH output transition time7151922ns 4.5Figs 8, 9 and10t W latch enable pulsewidthLOW1652024ns 4.5Fig.9t su set-up timeD n to LE1251518ns 4.5Fig.11t h hold timeD n to LE0−400ns 4.5Fig.11AC WAVEFORMSFig.8Waveforms showing the input (D n ,LT) to output (Q n ) propagation delays and the output transition times.(1)HC : V M =50%; V I =GND to V CC .HCT:V M =1.3 V; V I =GND to 3 V.Fig.9Waveforms showing the input (LE) to output (Q n ) propagation delays and the latch enable pulse width.(1)HC : V M =50%; V I =GND to V CC .HCT:V M =1.3 V; V I =GND to 3 V.Fig.10Waveforms showing the input (BI) to output(Q n ) propagation delays.(1)HC : V M =50%; V I =GND to V CC .HCT:V M =1.3 V; V I =GND to 3 V.Fig.11Waveforms showing the data set-up andhold times for D n input to LE input.The shaded areas indicate when the input is permitted to change for predictable output performance.(1)HC : V M =50%; V I =GND to V CC .HCT:V M =1.3 V; V I =GND to 3 V.APPLICATION DIAGRAMS Fig.12Connection to common cathode LED display readout.Fig.13Connection to common anode LED display readout.Fig.14 Connection to incandescent display readout.(1) A filament pre-warm resistor to reduce thermal shock and to increase effective cold resistance of the filament is recommended.Fig.15 Connection to fluorescent display readout.Fig.16 Connection to gas discharge display readout.Fig.17Connection to LCD display readout.(Direct DC drive is not recommended as it can shorten the life of LCD displays).PACKAGE OUTLINESSee“74HC/HCT/HCU/HCMOS Logic Package Outlines”.。

AG7111规格书DataSheet_V1P0

AG71113to 1 HDMI/DVI/DisplayPort Dual-mode SwitchData Sheet V1.03 to 1 HDMI/DVI/DP++ Switch Change HistoryVersion Date Notes1.02016/12/22First ReleaseCopyrightCopyright© 2016 Algoltek, Inc. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Algoltek, Inc. or its affiliates. All rights are reserved and contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Algoltek, Inc. or its affiliates.3 to 1 HDMI/DVI/DP++ SwitchIndexFeatures ........................................................................................................................................ - 1 - Process and Packaging ................................................................................................................. - 1 - Applications .................................................................................................................................. - 1 - General Description ..................................................................................................................... - 1 - 1. System Block and Functional Description ................................................................................ - 2 - PIN Assignment ........................................................................................................................ - 3 - PIN Description ......................................................................................................................... - 4 - 2. Electrical Characteristics .......................................................................................................... - 5 - Absolute Maximum Rating ....................................................................................................... - 5 - Normal Operating Conditions .................................................................................................. - 6 - I/O Specification ....................................................................................................................... - 6 - 3. Packing and Marking Specification .......................................................................................... - 7 - Marking .................................................................................................................................... - 7 - Package Drawing ...................................................................................................................... - 8 - LQFP-EP 48L ...................................................................................................................... - 8 - QFN 48L ............................................................................................................................ - 9 - 4. References .............................................................................................................................. - 10 -3 to 1 HDMI/DVI/DP++ SwitchList of FigureFigure 1 Application for 3 to 1 HDMI/DP++ Switch ............................................................. - 2 - Figure 2 System Block Diagram ........................................................................................... - 2 - Figure 3 PIN Assignment ..................................................................................................... - 3 - Figure 4 Marking ................................................................................................................. - 7 - Figure 5 LQFP-EP 48L Package Drawing ............................................................................... - 8 - Figure 6 QFN 48L Package Drawing ..................................................................................... - 9 -List of TableTable 1 Describes the IP related IO ports ............................................................................ - 5 - Table 2 Absolute Maximum Rating ...................................................................................... - 5 - Table 3 Normal Operating Conditions ................................................................................. - 6 - Table 4 I/O Specification ...................................................................................................... - 6 -3 to 1 HDMI/DVI/DP++ Switch●Implement auto equalization design for supportingFeatures●Single voltage supply 3.15V ~ 5.5V● Support both AC coupled and DC coupled inputs ● Support HDMI, DVI and DisplayPort input ● Compatible to HDMI 1.4b specification●Compatible to DisplayPort Dual-Mode Standard version 1.1 ●Maximum TMDS throughput up to 3.4Gbps per lane (Total 10.2 Gbps) ●Maximum pixel clock rate up to 340MHz ● Support 4K2K@30Hz resolution ● Support Deep Color ● RC embedded to leave out external crystal ● 5V to 3.3V/1.2V regulator embedded ●Integrated 50 ohm termination resistors at eachhigh speed signal input ● Support 3 GPOs for port enable LED indicators ●Support GPI to select between Auto or MCU mode(Refer to AG7110 application note) ● Automatic HDMI plug-in detection ●Built-in port activate circuits for switching between source devices without the external MCU ●Support external MCU interface for remote controller application ● Suspend mode implemented for power savingcables with different lengths●Implement signal extension design to support long cables●Advanced design to enhance noise immunity for cascade applicationProcess and Packaging● 48-pin LQFP-EP/QFN 7X7mm package size●Extended commercial temperature range (0°C to +70°C)Applications●Projectors● A/V receivers● Set-Top boxes● Game consoles● Televisions/Monitors● Media Centers●PCs/NotebooksGeneral DescriptionThe Algoltek AG7111 chip is a digital video interface (DVI) or high-definition multimedia interface (HDMI) or DisplayPort dual-mode switch which allows up to 3 DisplayPort or DVI or HDMI ports to be switched to a single display sink device. The maximum bandwidth is 3.4Gbps per lane and provides Deep Color supporting. Its low power operation allows no external power source required in most applications. AG7111 is available in a space-saving, 48-pin LQFP and QFN package and operates over the extended 0°C to +70°C temperature range.Version: 1.03 to 1 HDMI/DVI/DP++ SwitchFigure 1Application for 3 to 1 HDMI/DP++ Switch1.System Block and Functional DescriptionFigure 2System Block Diagram3 to 1 HDMI/DVI/DP++ Switch PIN AssignmentFigure 3PIN Assignment3 to 1 HDMI/DVI/DP++ Switch PIN DescriptionPin#Pin name Type Description1RX2HPD Output Port 2 Hot Plug detector output2RX2SDA Bidirectional Port 2 DDC Data3RX2SCL Bidirectional Port 2 DDC Clock4RX2CKM Input Port2 Clock TMDS negative input5RX2CKP Input Port2 Clock TMDS positive input6RX2D0M Input Port2 Data TMDS negative input7RX2D0P Input Port2 Data TMDS positive input8RX2D1M Input Port2 Data TMDS negative input9RX2D1P Input Port2 Data TMDS positive input10RX2D2M Input Port2 Data TMDS negative input11RX2D2P Input Port2 Data TMDS positive input12BUTTONS Input1) RX EQ select2) Port switch without the external MCU13RX1HPD Output Port 1 Hot Plug detector output14RX1SDA Bidirectional Port 1 DDC Data15RX1SCL Bidirectional Port 1 DDC Clock16RX1CKM Input Port1 Clock TMDS negative input17RX1CKP Input Port1 Clock TMDS positive input18RX1D0M Input Port1 Data TMDS negative input19RX1D0P Input Port1 Data TMDS positive input20RX1D1M Input Port1 Data TMDS negative input21RX1D1P Input Port1 Data TMDS positive input22RX1D2M Input Port1 Data TMDS negative input23RX1D2P Input Port1 Data TMDS positive input24AVDD3Power VDD 3V25TXD2P Output Data TMDS positive output26TXD2M Output Data TMDS negative output27TXD1P Output Data TMDS positive output28TXD1M Output Data TMDS negative output29TXD0P Output Data TMDS positive output30TXD0M Output Data TMDS negative output3 to 1 HDMI/DVI/DP++ SwitchPin#Pin name Type Description31TXCKP Output Clock TMDS positive output32TXCKM Output Clock TMDS negative output33TXSCL Bidirectional Output Port DDC Clock34TXSDA Bidirectional Output Port DDC Data35TXHPD Input Output Port Hot Plug detector36RXSEL Input RX Input Port select by the external MCU37AVDD5Power VDD 5V38RX3HPD Output Port 3 Hot Plug detector output39RX3SDA Bidirectional Port 3 DDC Data40RX3SCL Bidirectional Port 3 DDC Clock41RX3CKM Input Port3 Clock TMDS negative input42RX3CKP Input Port3 Clock TMDS positive input43RX3D0M Input Port3 Data TMDS negative input44RX3D0P Input Port3 Data TMDS positive input45RX3D1M Input Port3 Data TMDS negative input46RX3D1P Input Port3 Data TMDS positive input47RX3D2M Input Port3 Data TMDS negative input48RX3D2P Input Port3 Data TMDS positive inputePad Ground GroundTable 1Describes the IP related IO ports2.Electrical CharacteristicsAbsolute Maximum RatingSymbol Parameter Min Max Unit AVDD55V Power Input-0.36VHBM (JESD22-A114-B)±8KV ESD MM (JESD22-A115-C)±400VCDM (JESD22-C101-C)±500V Latch-up LU (JESD78)±200mATable 2 Absolute Maximum Rating3 to 1 HDMI/DVI/DP++ Switch Normal Operating ConditionsSymbol Parameter Min Typ.Max Unit AVDD55V Power Input 3.155 5.5VTa Ambient Temperature02570Icc*Normal Operation Supply Current85mAV IH=V DD, V IL=V DD-0.4V, V ICM=3.1V, R T=50Ω, V DD=3.3VData input: 1.485Gbps HDMI data pattern Clockinput: 148.5MHz clockTable 3Normal Operating ConditionsI/O SpecificationParameter Test Conditions Min Typ.Max Unit Status pin: TXHPD(input), RXHPD(output)V IH LVTTL input High-level voltage2 5.3VV IL LVTTL input Low-level voltage00.8VV OH LVTTL High-level output voltage I OH = -8 mA 2.4 5.3VV OL LVTTL Low-level output voltage I OL = 8 mA00.4V Differential: RXCK/D0~D2,TXCK/D0~D2V L TMDS –VL<= 165MHz 2.7 2.9VV L TMDS –VL> 165MHz 2.6 2.9VV off TMDS – VOFF AVCC-10mV AVCC+10mV VR T Input termination resistance455055ΩTable 4I/O Specification3 to 1 HDMI/DVI/DP++ Switch 3.Packing and MarkingSpecification MarkingFigure 4Marking3 to 1 HDMI/DVI/DP++ Switch Package DrawingLQFP-EP 48LFigure 5LQFP-EP 48L Package Drawing3 to 1 HDMI/DVI/DP++ Switch QFN 48LFigure 6QFN 48L Package Drawing3 to 1 HDMI/DVI/DP++ Switch4.ReferencesHDMI 1.4b SpecificationVESA DisplayPort Dual-Model Standard Version 1.1。

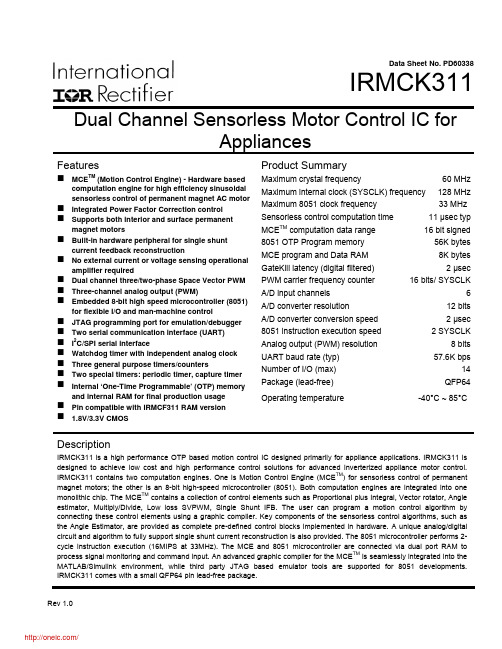

IRMCK311TR;中文规格书,Datasheet资料

Data Sheet No. PD60338IRMCK311 Dual Channel Sensorless Motor Control IC forAppliancesFeaturesMCE TM (Motion Control Engine) - Hardware based computation engine for high efficiency sinusoidal sensorless control of permanent magnet AC motor Integrated Power Factor Correction controlSupports both interior and surface permanent magnet motorsBuilt-in hardware peripheral for single shunt current feedback reconstructionNo external current or voltage sensing operational amplifier requiredDual channel three/two-phase Space Vector PWM Three-channel analog output (PWM)Embedded 8-bit high speed microcontroller (8051) for flexible I/O and man-machine controlJTAG programming port for emulation/debugger Two serial communication interface (UART)I2C/SPI serial interfaceWatchdog timer with independent analog clockThree general purpose timers/countersTwo special timers: periodic timer, capture timer Internal ‘One-Time Programmable’ (OTP) memory and internal RAM for final production usagePin compatible with IRMCF311 RAM version1.8V/3.3V CMOS Product SummaryMaximum crystal frequency 60 MHz Maximum internal clock (SYSCLK) frequency 128 MHz Maximum 8051 clock frequency 33 MHz Sensorless control computation time 11 μsec typ MCE TM computation data range 16 bit signed 8051 OTP Program memory 56K bytes MCE program and Data RAM 8K bytes GateKill latency (digital filtered) 2 μsec PWM carrier frequency counter 16 bits/ SYSCLK A/D input channels 6 A/D converter resolution 12 bits A/D converter conversion speed 2 μsec 8051 instruction execution speed 2 SYSCLK Analog output (PWM) resolution 8 bits UART baud rate (typ) 57.6K bps Number of I/O (max) 14 Package (lead-free) QFP64 Operating temperature -40°C ~ 85°CDescriptionIRMCK311 is a high performance OTP based motion control IC designed primarily for appliance applications. IRMCK311 is designed to achieve low cost and high performance control solutions for advanced inverterized appliance motor control. IRMCK311 contains two computation engines. One is Motion Control Engine (MCE TM) for sensorless control of permanent magnet motors; the other is an 8-bit high-speed microcontroller (8051). Both computation engines are integrated into one monolithic chip. The MCE TM contains a collection of control elements such as Proportional plus Integral, Vector rotator, Angle estimator, Multiply/Divide, Low loss SVPWM, Single Shunt IFB. The user can program a motion control algorithm by connecting these control elements using a graphic compiler. Key components of the sensorless control algorithms, such as the Angle Estimator, are provided as complete pre-defined control blocks implemented in hardware. A unique analog/digital circuit and algorithm to fully support single shunt current reconstruction is also provided. The 8051 microcontroller performs 2-cycle instruction execution (16MIPS at 33MHz). The MCE and 8051 microcontroller are connected via dual port RAM to process signal monitoring and command input. An advanced graphic compiler for the MCE TM is seamlessly integrated into the MATLAB/Simulink environment, while third party JTAG based emulator tools are supported for 8051 developments. IRMCK311 comes with a small QFP64 pin lead-free package.TABLE OF CONTENTS1 Overview (5)2 IRMCK311 Block Diagram and Main Functions (6)3 Pinout (8)4 Input/Output of IRMCK311 (9)4.1 8051 Peripheral Interface Group (10)4.2 Motion Peripheral Interface Group (10)4.3 Analog Interface Group (11)4.4 Power Interface Group (11)4.5 Test Interface (12)5 Application Connections (13)6 DC Characteristics (14)6.1 Absolute Maximum Ratings (14)6.2 System Clock Frequency and Power Consumption (14)6.3 Digital I/O DC Characteristics (15)6.4 PLL and Oscillator DC Characteristics (15)6.5 Analog I/O DC Characteristics (16)6.6 Under Voltage Lockout DC Characteristics (17)6.7 AREF Characteristics (17)7 AC Characteristics (18)7.1 PLL AC Characteristics (18)7.2 Analog to Digital Converter AC Characteristics (19)7.3 Op Amp AC Characteristics (19)7.4 SYNC to SVPWM and A/D Conversion AC Timing (20)7.5 GATEKILL to SVPWM AC Timing (21)7.6 Interrupt AC Timing (21)7.7 I2C AC Timing (22)7.8 SPI AC Timing (23)7.8.1 SPI Write AC timing (23)7.8.2 SPI Read AC Timing (24)7.9 UART AC Timing (25)7.10 CAPTURE Input AC Timing (26)7.11 JTAG AC Timing (27)7.12 OTP Programming Timing (28)8 I/O Structure (29)9 Pin List (32)Dimensions (35)10 Package11 Part Marking Information (36)Information (36)12 OrderingTABLE OF FIGURESFigure 1. Typical Application Block Diagram Using IRMCK311 (5)Figure 2. IRMCK311 Internal Block Diagram (6)Figure 3. IRMCK311 Pin Configuration (8)Figure 4. Input/Output of IRMCK311 (9)Figure 5. Application Connection of IRMCK311 (13)Figure 6. Clock Frequency vs. Power Consumption (14)Figure 7 Crystal oscillator circuit (18)Figure 8 Voltage droop of sample and hold (19)Figure 9 SYNC to SVPWM and A/D conversion AC Timing (20)Figure 10 GATEKILL to SVPWM AC Timing (21)Figure 11 Interrupt AC Timing (21)Figure 12 I2C AC Timing (22)Figure 13 SPI AC Timing (23)Figure 14 SPI Read AC Timing (24)Figure 15 UART AC Timing (25)Figure 16 CAPTURE Input AC Timing (26)Figure 17 JTAG AC Timing (27)Figure 18 OTP Programming Timing (28)Figure 19 All digital I/O except motor PWM output (29)Figure 20 RESET, GATEKILL I/O (29)Figure 21 Analog input (30)Figure 22 Analog operational amplifier output and AREF I/O structure (30)Figure 23 VPP programming pin I/O structure (30)Figure 24 VSS and AVSS pin structure (31)Figure 25 VDD1 and VDDCAP pin structure (31)Figure 26 XTAL0/XTAL1 pins structure (31)TABLE OF TABLESTable 1. Absolute Maximum Ratings (14)Table 2. System Clock Frequency (14)Table 3. Digital I/O DC Characteristics (15)Table 4. PLL DC Characteristics (15)Table 5. Analog I/O DC Characteristics (16)Table 6. UVcc DC Characteristics (17)Table 7. AREF DC Characteristics (17)Table 8. PLL AC Characteristics (18)Table 9. A/D Converter AC Characteristics (19)Table 10. Current Sensing OP Amp AC Characteristics (19)Table 11. SYNC AC Characteristics (20)Table 12. GATEKILL to SVPWM AC Timing (21)Table 13. Interrupt AC Timing (21)Table 14. I2C AC Timing (22)Table 15. SPI Write AC Timing (23)Table 16. SPI Read AC Timing (24)Table 17. UART AC Timing (25)Table 18. CAPTURE AC Timing (26)Table 19. JTAG AC Timing (27)Table 20. OTP Programming Timing (28)Table 21. Pin List (32)1 OverviewIRMCK311 is a new International Rectifier integrated circuit device primarily designed as a one-chip solution for complete inverter controlled appliance dual motor control applications. Unlike a traditional microcontroller or DSP, the IRMCK311 provides a built-in closed loop sensorless control algorithm using the unique Motion Control Engine (MCE TM) for permanent magnet motors. The MCE TM consists of a collection of control elements, motion peripherals, a dedicated motion control sequencer and dual port RAM to map internal signal nodes. IRMCK311 also employs a unique single shunt current reconstruction circuit to eliminate additional analog/digital circuitry and enables a direct shunt resistor interface to the IC. The sensorless control is the same for both motors with a single shunt current sensing capability. Motion control programming is achieved using a dedicated graphical compiler integrated into the MATLAB/Simulink TM development environment. Sequencing, user interface, host communication, and upper layer control tasks can be implemented in the 8051 high-speed 8-bit microcontroller. The 8051 microcontroller is equipped with a JTAG port to facilitate emulation and debugging tools. Figure 1 shows a typical application schematic using IRMCK311.IRMCK311 is intended for volume production purpose and contains 64K bytes of OTP (One Time Programming) ROM, which can be programmed through a JTAG port. For a development purpose use, IRMCF311 contains a 48k byte of RAM in place of program OTP to facilitate an application development work. Both IRMCF311 and IRMCK311 come in the same 64-pin QFP package with identical pin configuration to facilitate PC board layout and transition to mass productionFigure 1. Typical Application Block Diagram Using IRMCK3112 IRMCK311 Block Diagram and Main FunctionsM o t i o n C o n t r o l B u sFigure 2. IRMCK311 Internal Block DiagramIRMCK311 contains the following functions for sensorless AC motor control applications:• Motion Control Engine (MCE TM )o Proportional plus Integral block o Low pass filtero Differentiator and lag (high pass filter) o Ramp o Limito Angle estimate (sensorless control) o Inverse Clark transformation o Vector rotator o Bit latch o Peak detect o Transitiono Multiply-divide (signed and unsigned)o Divide (signed and unsigned)o Addero Subtractoro Comparatoro Countero Accumulatoro Switcho Shifto ATAN (arc tangent)o Function block (any curve fitting, nonlinear function)o16-bit wide Logic operations (AND, OR, XOR, NOT, NEGATE)o MCE TM program and data memory (6K byte). Note 1o MCE TM control sequencer• 8051 microcontrollero Three 16-bit timer/counterso16-bit periodic timero16-bit analog watchdog timero16-bit capture timero Up to 36 discrete I/Oso Eleven-channel 12-bit A/DFive buffered channels (0 – 1.2V input)One unbuffered channel (0 – 1.2V input)o JTAG port (4 pins)o Up to three channels of analog output (8-bit PWM)o Two UARTo I2C/SPI porto 64K byte Note 1program One-Time Programmable memoryo2K byte data RAM. Note 2Note 1: Total size of OTP memory is 64K byte, however MCE program occupiesmaximum 8K byte which will be loaded into internal RAM at a powerup/bootprocess. Therefore only 56K byte OTP memory area is usable for 8051microcontroller.Note 2: Total size of RAM is 8K byte including MCE program, MCE data, and 8051data. Different sizes can be allocated depending on applications.3 PinoutXTAL0XTAL1P1.1/RXD P1.2/TXDVDD1VSS VDD2P1.3/SYNC/SCKP1.4/CAPP 3.6/R X D 1P 3.7/T X D 1FPWMVL FPWMUL V S SV D D 2A V D DA V S SA I N 0A R E FP 2.7/A O P W M 1P 2.6/A O P W M 0CPWMUH CPWMVH CPWMWH CPWMUL CPWMVL CPWMWL CGATEKILL VDD1VSS I F B C OI F B C +I F B C -P L L V S SP L L V D DR E S E TN CT C KP 5.3/T D IP 5.2/T D OP 5.1/T M SS D A /C S 0S C L /S O -S I /V P PP 5.0/P F C G K I L LP F C P W M V S SFGATEKILL FPWMWL VAC-VAC+VACO IPFCO IPFC+IPFC-I F B F OI F B F +I F B F -P3.0/INT2/CS1C M E X TFPWMVH FPWMUHFPWMWH A I N 1P 3.2/I N T 0Figure 3. IRMCK311 Pin Configuration4 Input/Output of IRMCK311All I/O signals of IRMCK311 are shown in Figure 4. All I/O pins are 3.3V logic interface except A/D interface pins.Figure 4. Input/Output of IRMCK3114.1 8051 Peripheral Interface GroupUART InterfaceP1.1/RXD Input, Receive data to IRMCK311, can be configured as P1.1P1.2/TXD Output, Transmit data from IRMCK311, can be configured as P1.22nd channel Receive data to IRMCK311, can be configured as P3.6 P3.6/RXD1 Input,P3.7/TXD1 Output,2nd channel Transmit data from IRMCK311, can be configured as P3.7Discrete I/O InterfaceP1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock P1.4/CAP Input/output port 1.4, can be configured as Capture Timer inputP3.0/INT2/CS1 Input/output port 3.0, can be configured as external interrupt 2 or SPIchip select 1P3.2/INT0 Input/output port 3.2, can be configured as external interrupt 0Analog Output InterfaceP2.6/AOPWM0 Input/output, can be configured as 8-bit PWM output 0 withprogrammable carrier frequencyP2.7/AOPWM1 Input/output, can be configured as 8-bit PWM output 1 withprogrammable carrier frequencyCrystal InterfaceXTAL0 Input, connected to crystalXTAL1 Output, connected to crystalReset InterfaceRESET Inout, system reset, needs to be pulled up to VDD1 but doesn’t requireexternal RC time constantI2C/SPI InterfaceSCL/SO-SI/VPP Output, I2C clock output, SPI SO-SII2C Data line, Chip Select 0 of SPISDA/CS0 Input/output,P3.0/INT2/CS1 Input/output port 3.0, can be configured as external interrupt 2 or SPIchip select 1P1.3/SYNC/SCK Input/output port 1.3, can be configured as SYNC output or SPI clock 4.2 Motion Peripheral Interface GroupPWMCPWMUH Output, motor 1 PWM phase U high side gate signalCPWMUL Output, motor 1 PWM phase U low side gate signalCPWMVH Output, motor 1 PWM phase V high side gate signalCPWMVL Output, motor 1 PWM phase V low side gate signalCPWMWH Output, motor 1 PWM phase W high side gate signalCPWMWL Output, motor 1 PWM phase W low side gate signalFPWMUH Output, motor 2 PWM phase U high side gate signalFPWMUL Output, motor 2 PWM phase U low side gate signal分销商库存信息: IRIRMCK311TR。

4511芯片

4511芯片

4511芯片是什么?

4511芯片是一种数字集成电路芯片,常用于驱动7段数码管显示器。

其内部集成了BCD(二进制码十进制数)-七段数码管译码器,可以将BCD码转换为七段数码管的输入信号,从而实现数字的显示。

4511芯片的引脚功能:

4511芯片具有16个引脚,其中重要的引脚功能如下:

- A, B, C, D:用于输入BCD码,确定要显示的数字。

- a, b, c, d, e, f, g:用于控制七段数码管的7个段的开关。

- aG, bG, cG, dG:用于控制小数点的开关。

- LT:用于控制显示器的段刷新。

4511芯片的工作原理:

在芯片输入端口A, B, C, D上输入BCD码,芯片会自动解码输入,然后根据解码结果控制a, b, c, d, e, f, g这7个输出端口以及小数点的亮灭,从而驱动7段数码管显示对应的数字。

通过不断修改输入信号,就可以实现数字的多次更新显示。

4511芯片的应用:

由于其方便实现数字显示功能,4511芯片被广泛用于电子计算器、数字时钟、温度计、电压计等需要数字显示的场合。

通过与其他逻辑门等芯片的组合和连接,还可以实现更加复杂的数字逻辑功能。

总结:

4511芯片是一种集成电路芯片,主要功能是将输入的BCD码

转换为七段数码管的控制信号,从而实现数字的显示。

其工作原理是通过输入信号的不断修改,控制不同段的开关状态,从而实现数字的多次更新显示。

由于其方便、简单且可靠的特点,4511芯片被广泛应用于各种需要数字显示的场合。

MC14513BCPG;中文规格书,Datasheet资料

−

0.05

0

0.05

−

0.05

Vin = 0 or VDD

“1” Level

VOH

5.0

4.1

10

9.1

− −

4.1 9.1

5.0 10

15

14.1

−

14.1

15

−

4.1

−

Vdc

−

9.1

−

−

14.1

−

Output Voltage — RBO Output “0” Level

Vin = VDD or 0

IOHmax

25

mA

Current (Source) per Output

Maximum Continuous Output Power POHmax

50

mW

(Source) per Output (Note 2)

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. Temperature Derating: Plastic “P and D/DW”

Vin = 0 or VDD

“1” Level

CD4511中文资料_数据手册_参数

Data sheet acquired from Harris Semiconductor SCHS072

IMPORTANT NOTICE

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability. TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

PT19-21BL41TR8;中文规格书,Datasheet资料

Technical Data Sheet 0.8mm Height Flat Top PhototransistorPT19-21B/L41/TR8Features․Fast response time ․High photo sensitivity ․Small junction capacitance ․Pb free ․The product itself will remain within RoHS compliant version.Descriptions․PT19-21B/L41/TR8 is a phototransistor in miniature SMD package which is molded in a black with flat top view lens. The device is Spectrally matched to visible and infrared emitting diode.Applications․Miniature switch ․Counters and sorter ․Position sensor ․Infrared applied system ․EncoderDevice Selection Guide LED Part No.PTChip MaterialSiliconLens ColorBlackEverlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 1 of 10/PT19-21B/L41/TR8Package DimensionsEmitter CollectorNotes: 1.All dimensions are in millimeters 2.Tolerances unless dimensions ±0.1mmAbsolute Maximum Ratings (Ta=25℃)Parameter Collector-Emitter Voltage Emitter-Collector-Voltage Collector Current Operating Temperature Storage Temperature Soldering Temperature *1 Power Dissipation at(or below) 25℃Free Air Temperature Symbol VCEO VECO IC Topr Tstg Tsol Pc Rating 30 5 20 -25 ~ +85 -40 ~ +85 260 75 Units V V mA ℃ ℃ ℃ mWNotes: *1:Soldering time≦5 seconds.Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 2 of 10/PT19-21B/L41/TR8Electro-Optical Characteristics (Ta=25℃)Parameter Rang Of Spectral Bandwidth Wavelength Of Peak Sensitivity Collector-Emitter Breakdown Voltage Emitter-Collector Breakdown Voltage Collector-Emitter Saturation Voltage Collector Dark Current Symbol λ0.5 λP BVCEO BVECO VCE(sat) ICEO Condition ----IC=100μA Ee=0mW/cm2 IE=100μA Ee=0mW/cm2 IC=2mA Ee=1m W/cm2 VCE=20V Ee=0mW/cm2 VCE=5V Ee=1mW /cm2 VCE=5V IC=1mA RL=1000Ω Min 730 --30 Typ --940 --Max 1100 ----Unit nm nm V5 --------------0.4 100V V nAOn State Collector Current Rise Time Fall TimeIC(ON) tr tf0.3 -----0.6 15 15-----mAμS ---Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 3 of 10/PT19-21B/L41/TR8Typical Electro-Optical Characteristics CurvesFig.1 Collector Power Dissipation vs. Ambient Temperature Fig.2 Spectral Sensitivity100 80 60 40 20 0 -25 0 25 50 75 85 1001.0 Ta=25 C 0.8 0.6 0.4 0.2 0 700 800 900 1000 1100 1300Fig.3 Relative Collector Current vs. Ambient TemperatureFig.4 Collector Current vs. Irradiance160 140 120 100 80 60 40 20 0 0 10 20 30 40 50 60 70210 C 1 0.10.010.001 0.010.11210Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 4 of 10/PT19-21B/L41/TR8Typical Electro-Optical Characteristics CurvesFig.5 Collector Dark Current vs. Ambient Temperature Fig.6 Collector Current vs. Collector-Emitter Voltage1014 1210 1010 8 6104 210 0 25 50 75 1000 01234Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 5 of 10/PT19-21B/L41/TR8Precautions For Use1. Over-current-proof Customer must apply resistors for protection , otherwise slight voltage shift will cause big current change ( Burn out will happen ). 2. Storage 2.1 Do not open moisture proof bag before the products are ready to use. 2.2 Before opening the package, the LEDs should be kept at 30℃ or less and 90%RH or less. 2.3 The LEDs should be used within a year. 2.4 After opening the package, the LEDs should be kept at 30℃ or less and 70%RH or less. 2.5 The LEDs should be used within 168 hours (7 days) after opening the package. 2.6 If the moisture absorbent material (silica gel) has faded away or the LEDs have exceeded the storage time, baking treatment should be performed using the following conditions. Baking treatment : 60±5℃ for 24 hours. 3. Soldering Condition 3.1 Pb-free solder temperature profile3.2 Reflow soldering should not be done more than two times. 3.3 When soldering, do not put stress on the LEDs during heating. 3.4 After soldering, do not warp the circuit board.Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 6 of 10/PT19-21B/L41/TR84.Soldering Iron Each terminal is to go to the tip of soldering iron temperature less than 280℃ for 3 seconds within once in less than the soldering iron capacity 25W. Leave two seconds and more intervals, and do soldering of each terminal. Be careful because the damage of the product is often started at the time of the hand solder. 5.Repairing Repair should not be done after the LEDs have been soldered. When repairing is unavoidable, a double-head soldering iron should be used (as below figure). It should be confirmed beforehand whether the characteristics of the LEDs will or will not be damaged by repairing.Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 7 of 10/PT19-21B/L41/TR8Reliability Test Item And Condition The reliability of products shall be satisfied with items listed below. Confidence level:90% LTPD:10% NO. Item Test Conditions Test Hours/ Sample Failure Cycles 1 REFLOW Soldering TEMP.:260℃±5℃ 5secs 2 Temperature Cycle H : +100℃ L : -40℃ 3 Thermal Shock H :+100℃ L :-10℃ 4 High Temperature Storage 5 Low Temperature Storage 6Mins Sizes 22pcs 22pcs IC(ON)≦L×0.8 L:Lower 22pcs Specification Limit 0/1 Judgement Criteria 0/1 0/1 Ac/Re15mins 50Cycles 5mins 15mins 5mins 50Cycles 10secs 5mins 1000hrs 1000hrs 1000hrs 1000hrsTEMP.:+100℃ TEMP.:-40℃22pcs 22pcs 22pcs 22pcs0/1 0/1 0/1 0/16 DC Operating Life VCE=5V 7 High Temperature/ 85℃ / 85% R.H High HumidityEverlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 8 of 10/PT19-21B/L41/TR8Package DimensionsTaping DimensionsEmitter CollectorUnit:mmEverlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 9 of 10/PT19-21B/L41/TR8Packing Quantity Specification1.3000Pcs/1Volume,1Volume/1Bag 2.10Boxes/1CartonLabel Form SpecificationCPN: Customer’s Production Number P/N : Production Number QTY: Packing Quantity CAT: Ranks HUE: Peak Wavelength REF: Reference LOT No: Lot Number MADE IN TAIWAN: Production PlacePT19-21B/L41/TR8RoHS RoHS RoHS RoHS RoHS RoHSNotes1. Above specification may be changed without notice. EVERLIGHT will reserve authority on material change for above specification. 2. When using this product, please observe the absolute maximum ratings and the instructions for using outlined in these specification sheets. EVERLIGHT assumes no responsibility for any damage resulting from use of the product which does not comply with the absolute maximum ratings and the instructions included in these specification sheets. 3. These specification sheets include materials protected under copyright of EVERLIGHT corporation. Please don’t reproduce or cause anyone to reproduce them without EVERLIGHT’s consent.EVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Tucheng, Taipei 236, Taiwan, R.O.C Tel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 Everlight Electronics Co., Ltd. Device No:DTT-019-165 Prepared date:07-25-2005Rev 2Prepared by jaine tsai:Page: 10 of 10/分销商库存信息: EVERLIGHTPT19-21B/L41/TR8。

西门子 SIMATIC FM 451 说明书

通道: 物理单位: 驱动器:

轴: 编码器:

1 mm 控制模式: 目标范围: 监视时间: 稳定范围: 稳定速度: 正方向切换差程: 负方向切换差程: 正方向关断差程: 负方向关断程:

线性轴/旋转轴: 软件限制开关: 旋转轴末端: 编码器类型:

(仅将此通道接线) (3 个小数位) 1 1,000 mm 2.000 ms 1,000 mm 30,000 mm/min > 正方向关断差程: > 负方向关断差程: > 1/2 x 目标范围 > 1/2 x 目标范围 成功完成基本程序后,确定正 负方向上切换/关断差程相应 的设备专用值,然后修改这些 参数使其适合系统要求。 取决于应用 取决于应用 取决于应用 选择要使用的编码器。 其它全部的编码器设置是设备 和工厂特定的。

SIMATIC FM 451

入门指南

10/2005

A5E00432649-01

安全技术提示

为了您的人身安全以及避免财产损失,必须注意本手册中的提示。人身安全的提示用一个警告三角表示,仅与财产 损失有关的提示不带警告三角。警告提示根据危险等级由高到低如下表示。

危险 表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

可通过增减切换差程与关断差程来提高定位精度。通过增加目标范围也可获得“已达到位置 – 停止”消息。调整上述参数直到获得“已达到位置 – 停止”消息,并使得实际定位值与增量位置相 当接近而趋于相等。不要减少您为正切换/关断差程所确定的值。

选择负增量来确定负切换和关断差程。

选择更改参数 > 驱动器,打开驱动器参数视图,然后在相关参数中输入所确定的值。

在 SIMATIC 管理器中,选择文件 > 打开... > 库,打开FMx51LIB库。 将 FC0、FC1 和 UDT1 从 FMx51LIB 库的块容器复制到项目的“块”容器。 选择插入 > S7 块 > 数据块,将 DB1 插入到项目的“块”容器中,并选择插入 > S7 块 > 组织块 插入 OB100。 打开 DB1,然后通过为其指定的用户专用 UDT1 进行编程。这就是生成通道 DB 的过程。 打开视图 > 数据视图。选择“实际值”列,然后为 DB1 中的参数 MOD_ADDR 设置十进制地址, 并在 CH_NO 参数中设置通道号 1。 选择文件 > 保存保存 DB1,然后单击文件 > 退出退出 DB 编辑器。 接下来,打开项目中的 OB100 和 OB1 并调用 OB100 中的 FC0 和 OB1 中的 FC1。对这些 FC 进行相应编程(请参阅手册): OB100: CALL FC0 DB_NO := 1 OB1: CALL FC 1 DB_NO := 1 RET_VAL := MW0 单击文件 > 保存,保存 OB100 和 OB1。 在项目中,选择 FC0、FC1、DB1、OB1 和 OB100 块。 选择 PLC > 下载,将程序下载到 CPU。 测试: 使用“监视和修改变量”功能来监视所选通道。 在符号编辑器中,为 DB1 分配一个名为 “ABS” 的符号。 选择项目的“块”容器。单击插入 > S7 块 > 变量表插入变量表 VAT1,然后单击确定来确认输入。 打开变量表 VAT1,然后在“符号”、“状态格式”和“控制值”列中进行输入:

DTC114YEBTL;中文规格书,Datasheet资料

Max. 0.3 0.3 0.88 0.5 13 5.7 -

Unit V V mA mA kW MHz

*1 Characteristics of built-in transistor *2 Each terminal mounted on a reference footprint

© 2012 ROHM Co., Ltd. All rights reserved.

Data Sheet

EMT3F

D

A

x

S A

b e

HE

E

c

e

A2

A

A1

S

l1

b2

Patterm of terminal position areas

MILIMETERS MIN MAX 0.65 0.85 0.00 0.10 0.60 0.80 0.21 0.36 0.08 0.18 1.50 1.70 0.76 0.96 0.50 1.50 1.70 0.37 0.35 0.55 0.10 MILIMETERS MIN MAX 1.05 0.46 0.65 INCHES MIN 0 0.024 0.008 0.003 0.059 0.03 0.02 0.059 0.015 0.014 INCHES MIN MAX 0.041 0.018 0.026 0.022 0.004 0.067 MAX 0.004 0.031 0.014 0.007 0.067 0.038

DIM A A1 A2 b c D E e HE L Lp x DIM e1 b2 l1

Dimension in mm/inches

© 2012 ROHM Co., Ltd. All rights reserved.

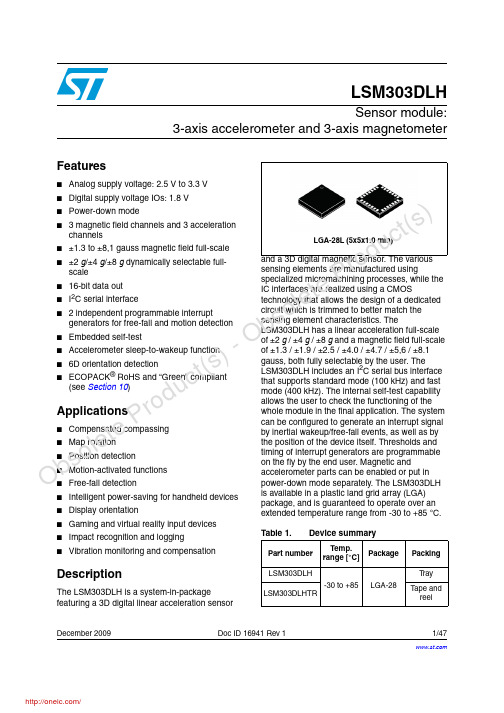

LSM303DLHTR;LSM303DLH;中文规格书,Datasheet资料

LGA-28L (5x5x1.0 mm)

and a 3D digital magnetic sensor. The various sensing elements are manufactured using specialized micromachining processes, while the IC interfaces are realized using a CMOS technology that allows the design of a dedicated circuit which is trimmed to better match the sensing element characteristics. The LSM303DLH has a linear acceleration full-scale of ±2 g / ±4 g / ±8 g and a magnetic field full-scale of ±1.3 / ±1.9 / ±2.5 / ±4.0 / ±4.7 / ±5,6 / ±8.1 gauss, both fully selectable by the user. The LSM303DLH includes an I2C serial bus interface that supports standard mode (100 kHz) and fast mode (400 kHz). The internal self-test capability allows the user to check the functioning of the whole module in the final application. The system can be configured to generate an interrupt signal by inertial wakeup/free-fall events, as well as by the position of the device itself. Thresholds and timing of interrupt generators are programmable on the fly by the end user. Magnetic and accelerometer parts can be enabled or put in power-down mode separately. The LSM303DLH