国际空间站上使用的两种计算机

国际空间站比中国空间站大多少

国际空间站比中国空间站大多少先来看一下外形,通过图片可以看到,国际空间站的外形比我们空间站的外形要大得多,体积上可能达到我们的四倍以上。

我国的空间站是90吨,而国际空间站的吨级是420吨,重量上快达到我们的五倍。

国际空间站长110米,宽88米,我国的核心舱全长16.6米,最大直径为4.2米。

国际空间站比我们的空间站大就说明比我们的空间站厉害吗?其实还真不是这样,国际空间站虽然是我们的四倍以上大,但是对比天和空间站舱室大小是差不多的,主要是大在了这个惊人的独立桁架上。

我国空间站的结构和国际空间站的结构不同。

我国的舱体对接是采用了积木式布局,这是第三代空间站的主要特征,这种紧密连接性结构非常利于节省空间。

而国际空间站采用的是大型桁架结构,是第四代空间站的标志性做法,这种结构让它看上去有非常大体积,非常耗费空间。

毕竟我国的是单个国家搞,讲究务实;国际空间站就不一样了,全球多个国家合作,财力上也是不用担心的,自然面子工程做的特别好。

第二点就是国际空间站和我国的轨道维持方式不一样,并且这个空间站能源利用率也不一样。

两个空间站都是在400公里的LEO轨道上运行,但是这个轨道存在稀薄的空气,就会导致在这个高度运行的航天器会产生摩擦,长时间的摩擦会造成航天器的逐渐减速,这样就会动力减少而造成高度不断下降甚至坠入大气层,需要对航天器进行轨道维持。

中国空间站的轨道维持方式主要依靠对接在其尾部的进步号货运飞船来实现,国际空间站本身就拥有动力系统,也是采用很先进的电推系统,这点要比中国的空间站先进。

我国空间站核心舱的太阳翼采用了新材料,这让能源转换率达到了30%;国际空间站由于美国和俄罗斯借接口和标准不一样,能源的利用率不如中国空间站,两者的发电功率都是100千瓦。

第三点就是科研目的和技术不同。

我国空间站科研目的种类非常多,就拿这个巡天望远镜来说吧。

它和我国空间站共轨运行,国际空间站并没有此项目。

这个巡天望远镜清晰度非常高,它的视场是哈勃望远镜的300倍,可以说是非常强大了。

国际空间站各舱段介绍

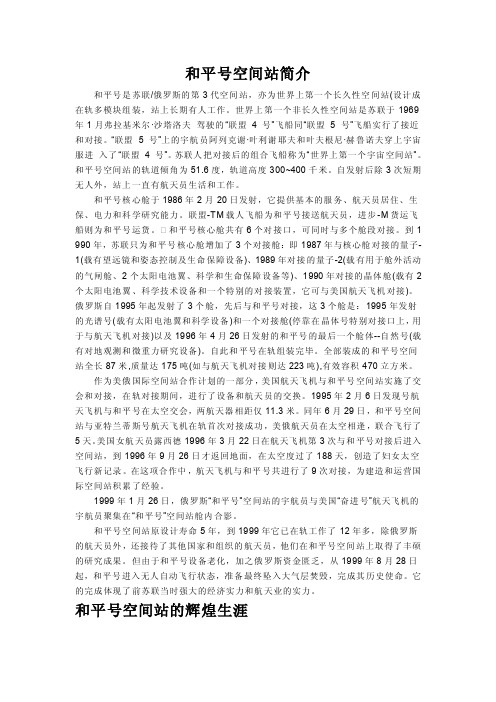

国际空间站作为国际合作空间探索项目,其规模庞大、系统复杂、技术先进。

该项目由16个国家共同建造、运行和使用,是有史以来规模最大、耗时最长且涉及国家最多的空间国际合作项目。

自1998年正式建站以来,经过十多年的建设,于2010年完成建造任务转入全面使用阶段。

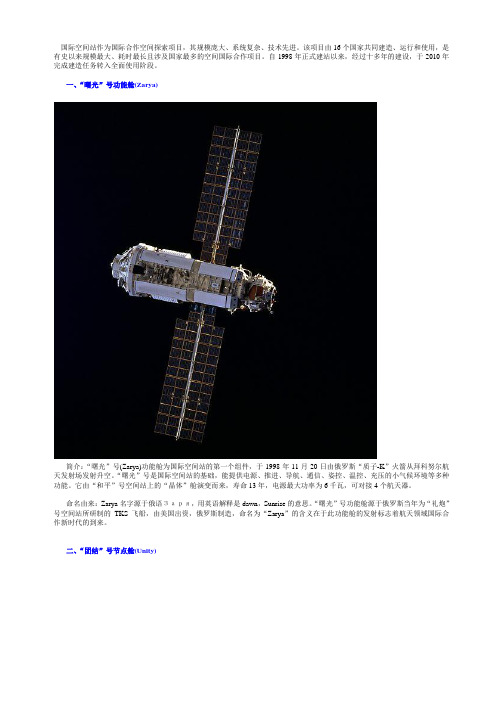

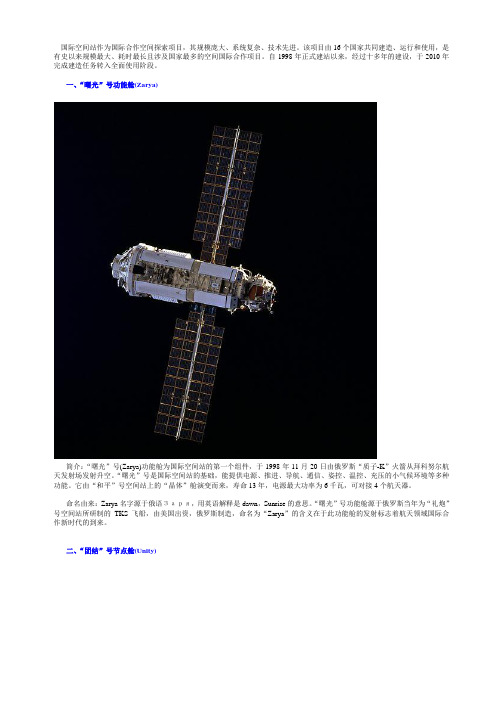

一、“曙光”号功能舱(Zarya)简介:“曙光”号(Zarya)功能舱为国际空间站的第一个组件,于1998年11月20日由俄罗斯“质子-K”火箭从拜科努尔航天发射场发射升空。

“曙光”号是国际空间站的基础,能提供电源、推进、导航、通信、姿控、温控、充压的小气候环境等多种功能。

它由“和平”号空间站上的“晶体”舱演变而来,寿命13年,电源最大功率为6千瓦,可对接4个航天器。

命名由来:Zarya名字源于俄语Заря,用英语解释是dawn,Sunrise的意思。

“曙光”号功能舱源于俄罗斯当年为“礼炮”号空间站所研制的TKS飞船,由美国出资,俄罗斯制造,命名为“Zarya”的含义在于此功能舱的发射标志着航天领域国际合作新时代的到来。

二、“团结”号节点舱(Unity)简介:“团结”号(Unity)节点舱是国际空间站的第二个组件,也是国际空间站的第一个节点舱,于1998年12月4日由“奋进”号航天飞机送入轨道。

舱体长5.49米,直径4.57米,重11612千克,用于存贮货物和调节电力供应,是国际空间站上负责连接6个舱体的主要节点舱。

命名由来:由于该舱是国际空间站的第一个节点舱,因此也常被称为“节点1”(Node 1)。

根据NASA国际空间站计划主任兰迪•布林克利的解释,“Unity”这个名字代表了NASA、波音还有全世界国际空间站团队的共同努力,反映了国际空间站计划中的国际合作。

三、“星辰”号服务舱(Zvezda)简介:“星辰”号(Zvezda)服务舱是国际空间站的核心,是航天员生活和工作的主要场所,“星辰”号服务舱由俄罗斯出资和建造,于2000年7月12日发射,7月26日与国际空间站联合体对接。

空间站

历史沿革

空间站概念的提出可以追溯到1869年,当时Everett Hale为《大西洋月刊》撰写了一则关于“用砖搭建的月 球”的文章。此后,康斯坦丁·齐奥尔科夫斯基和赫尔曼·奥伯特也对空间站进行过设想。1929年Herman Potočnik的著作The Problem of Space Travel(《太空旅行的问题》)出版并风靡了30多年。1951年沃 纳·冯·布劳恩在矿工周刊中刊登了他带有环状结构的空间站设计。二战期间德国科学家曾研究过使用太阳能的 轨道兵器,即所谓的“太阳炮”。按照设想,它将是运行在高度在5100英里(8200千米)的地球轨道的空间站的 一部分。

主要特点

空间站特点是体积比较大、结构复杂,在轨道飞行时间较长,有多种功能,能开展的太空科研项目也多而广。

空间站的特点之一是经济性。例如,所有的空间站都不具有返回地面的功能而是在太空接纳航天员进行实验, 可以使载人飞船成为只运送航天员的工具,从而简化了空间站的结构,既能降低其工程设计难度,又可减少航天 费用。另外,空间站在运行时可载人,也可不载人,只要航天员启动并调试后它可照常进行工作,定时检查,到 时就能取得成果。这样能缩短航天员在太空的时间,减少许多消费,当空间站发生故障时可以在太空中维修、换 件,延长航天器的寿命。增加使用期也能减少航天费用。因为空间站能长期(数个月或数年)的飞行,故保证了 太空科研工作的连续性和深入性,这对研究的逐步深化和提高科研质量有重要作用。

中国空间站总体构型为3个舱段,包括天和核心舱以及问天实验舱、梦天实验舱,整体呈T字构型,能够容纳 3-6名航天员在轨工作生活,建成后整体空间达到110立方米。

空间站

空间站空间站又称航天站、太空站、轨道站。

是一种在近地轨道长时间运行,可供多名航天员巡访、长期工作和生活的载人航天器。

空间站分为单一式和组合式两种。

单一式空间站可由航天运载器一次发射入轨,组合式空间站则由航天运载器分批将组件送入轨道,在太空组装而成。

“数字”空间站1971年4月19日,前苏联发射了第1座空间站礼炮1号,它由轨道舱,服务舱和对接舱组成,呈不规则的圆柱形,总长约12.5米,最大直径4米,总重约18.5吨。

礼炮1号完成使命后于同年10月11日在太平洋上空坠毁。

前苏联一共发射了7座礼炮号空间站。

1982年4月19日礼炮7空间站进入轨道飞行,载人飞行累计达800多天,直到1986年8月才停止载人飞行。

到目前为止,全世界已发射了11个空间站。

其中前苏联共发射8座,美国发射1座,国际联合发射1座,中国发射1座。

和平号空间站原设计寿命5年,到1999年它已在轨工作了12年多,从1999年8月28日起和平号进入无人自动飞行状态,准备最终坠入大气层焚毁,2001年3月23日坠入地球大气层,完成其历史使命,在轨飞行长达15年。

国际空间站以美国和俄罗斯为首,包括加拿大、日本、巴西、比利时、丹麦、法国、德国、英国、意大利、荷兰、西班牙、瑞典、瑞士和爱尔兰共16个国家参与研制。

天宫一号天宫一号是中国第一个目标飞行器和空间实验室,于2011年9月29日21时16分3秒在酒泉卫星发射中心发射,飞行器全长10.4米,最大直径3.35米,由实验舱和资源舱构成。

2011年11月3日凌晨实现与神舟八号飞船的对接任务。

2012年6月18日下午与神舟九号对接成功。

神舟十号飞船也在2013年6月13日13时18分与天宫一号完成自动交会对接。

天宫一号在寿命末期,将主动离轨,陨落南太平洋。

资源舱主要任务是为天宫一号的飞行提供能源保障,并控制飞行姿态实验舱主要负责航天员工作、训练及生活和平号空间站的1997年和2001年1997年·坎坷前行1997年2月23日,和平号上的两台基本电解生氧装置连续出现故障,航天员拉佐特金在量子1号舱内制氧时,制氧设备突然破裂,引起火灾明火燃烧了90秒,烟雾弥漫到整个空间站航天员们都带上了防毒面具浓烟持续了5-7分钟。

和平号空间站简介

和平号空间站简介和平号是苏联/俄罗斯的第3代空间站,亦为世界上第一个长久性空间站(设计成在轨多模块组装,站上长期有人工作。

世界上第一个非长久性空间站是苏联于1969年1月弗拉基米尔·沙塔洛夫驾驶的“联盟 4 号”飞船同“联盟 5 号”飞船实行了接近和对接。

“联盟 5 号”上的宇航员阿列克谢·叶利谢耶夫和叶夫根尼·赫鲁诺夫穿上宇宙服进入了“联盟 4 号”。

苏联人把对接后的组合飞船称为“世界上第一个宇宙空间站”。

和平号空间站的轨道倾角为51.6度,轨道高度300~400千米。

自发射后除3次短期无人外,站上一直有航天员生活和工作。

和平号核心舱于1986年2月20日发射,它提供基本的服务、航天员居住、生保、电力和科学研究能力。

联盟-TM载人飞船为和平号接送航天员,进步-M货运飞船则为和平号运货。

和平号核心舱共有6个对接口,可同时与多个舱段对接。

到1 990年,苏联只为和平号核心舱增加了3个对接舱:即1987年与核心舱对接的量子-1(载有望远镜和姿态控制及生命保障设备)、1989年对接的量子-2(载有用于舱外活动的气闸舱、2个太阳电池翼、科学和生命保障设备等)、1990年对接的晶体舱(载有2个太阳电池翼、科学技术设备和一个特别的对接装置,它可与美国航天飞机对接)。

俄罗斯自1995年起发射了3个舱,先后与和平号对接,这3个舱是:1995年发射的光谱号(载有太阳电池翼和科学设备)和一个对接舱(停靠在晶体号特别对接口上,用于与航天飞机对接)以及1996年4月26日发射的和平号的最后一个舱体--自然号(载有对地观测和微重力研究设备)。

自此和平号在轨组装完毕。

全部装成的和平号空间站全长87米,质量达175吨(如与航天飞机对接则达223吨),有效容积470立方米。

作为美俄国际空间站合作计划的一部分,美国航天飞机与和平号空间站实施了交会和对接,在轨对接期间,进行了设备和航天员的交换。

1995年2月6日发现号航天飞机与和平号在太空交会,两航天器相距仅11.3米。

国际空间站的建设和应用

国际空间站的建设和应用随着科技的快速发展,人类对于宇宙的探索也在不断推进。

国际空间站便是其中一个标志性的项目。

自2000年11月它开始运营以来,国际空间站已经成为人类开展太空探索和应用的重要平台。

本文将探讨国际空间站的建设和应用。

一、国际空间站的建设国际空间站是由五个太空机构共同建设的。

它们分别是:美国宇航局(NASA)、俄罗斯联邦航天局(Roscosmos)、欧洲航天局(ESA)、加拿大航空航天局(CSA)和日本航空航天研究开发机构(JAXA)。

这五个机构为国际空间站提供了大量的资源和技术支持。

国际空间站位于地球轨道,与地球保持距离约400公里。

它的长度和高度相当于一个足球场的大小。

国际空间站是由多个模块组成的,其中大部分是环状的,类似于楼层。

每个模块都有不同的用途和功能,例如,“和谐号”模块用于提供机载实验室和居住区域,而“展望号”模块则用于观察行星和恒星等。

二、国际空间站的应用国际空间站是一个多功能的太空平台。

它不仅为科学研究提供了重要的实验条件,也提供了重要的技术支持和应用平台。

1. 科学研究国际空间站为科学家们提供了独特的实验环境,这使得他们可以进行一些在地球上无法实现的实验。

例如,“磁力荡动星际物理实验”可以模拟太阳风和地球磁场的相互作用,这对于理解太阳风和磁场的本质是非常重要的。

另外,“空间种植实验”研究安全、可靠地在太空中生长食品的能力。

2. 技术支持国际空间站为太空探索提供了重要的技术支持。

例如,“空间梯田”可以提高太空中植物的产量和养分含量,这对于未来在太空中长期生存是非常重要的。

另外,国际空间站也为未来的地球观测任务提供了重要的技术支持。

3. 应用平台国际空间站为航天工程领域提供了重要的应用平台。

例如,“限制抑制子实验”研究的是宇航员在长期太空生活中的身体反应,这对于维护宇航员的健康和抗老化是非常有益的。

三、国际空间站的未来随着科技的发展,国际空间站的应用也在不断扩展。

未来,国际空间站可能成为以下方面的领先者:1. 楼宇建筑技术:国际空间站目前正探讨使用3D打印技术建造太空站。

全国青少年载人航天科技知识竞赛

寻梦“天宫”——全国青少年载人航天科技知识竞赛为激发全国广大青少年对航天科技的兴趣,提高全国青少年对载人航天科技知识的了解,中国科协、中国载人航天工程办公室和中国航天科技集团公司共同举办寻梦"天宫"—全国青少年载人航天科技知识竞赛活动。

本活动是"开启天宫的梦想"—全国青少年载人航天科普系列活动的重要活动之一。

此次知识竞赛采取书面答题和网络答题两种形式。

201161915309151000488 121002000201250/news/SpecialList.aspx?SpecialID=103&SortID=207知识竞赛知识点:1. 什么是空间站?空间站,也称为轨道站或太空站,是一种能长期在地球低轨道上运行的大型载人航天器,航天员可以长期在上面生活和工作,这种大型航天器能在轨道上与飞船或航天飞机对接,由飞船或航天飞机为它运送人员和物资;空间站与飞船或航天飞机的主要区别是它没有主推进系统和着陆设备,因此它不能在轨道上作机动飞行和返回着陆。

根据不同国家和不同的历史阶段,发展空间站有不同的动机和目的。

一般讲一个国家发展空间站主要有四个目的:第一是政治目的,即为了显示国家的综合实力,或者是为了在政治上“压倒”对方,在载人航天领域取得领导地位,上世纪冷战时期,这是美苏发展空间站的主要目的;第二是科技目的,即将空间站作为建在太空的科学实验室,在上面进行各种科学研究和实验;第三是经济目的,利用空间站进行太空生产,或者发展太空旅游;第四是军事目的,将空间站作为建在太空的“军事堡垒”。

知识竞赛知识点:2. 空间站的类型?2011-05-27中国科协青少年科技中心本文被阅读过51次[推荐][打印][保存][大字体][中字体][小字体]按用途分,空间站可分为民用和军用两种类型:民用空间站如前苏联的和平号空间站和美国的国际空间站;军用空间站如前苏联的礼炮2,礼炮3和礼炮5号空间站以及美国空军曾经计划研制的“载人轨道实验室”。

国际空间站各舱段介绍

国际空间站作为国际合作空间探索项目,其规模庞大、系统复杂、技术先进。

该项目由16个国家共同建造、运行和使用,是有史以来规模最大、耗时最长且涉及国家最多的空间国际合作项目。

自1998年正式建站以来,经过十多年的建设,于2010年完成建造任务转入全面使用阶段。

一、“曙光”号功能舱(Zarya)简介:“曙光”号(Zarya)功能舱为国际空间站的第一个组件,于1998年11月20日由俄罗斯“质子-K”火箭从拜科努尔航天发射场发射升空。

“曙光”号是国际空间站的基础,能提供电源、推进、导航、通信、姿控、温控、充压的小气候环境等多种功能。

它由“和平”号空间站上的“晶体”舱演变而来,寿命13年,电源最大功率为6千瓦,可对接4个航天器。

命名由来:Zarya名字源于俄语Заря,用英语解释是dawn,Sunrise的意思。

“曙光”号功能舱源于俄罗斯当年为“礼炮”号空间站所研制的TKS飞船,由美国出资,俄罗斯制造,命名为“Zarya”的含义在于此功能舱的发射标志着航天领域国际合作新时代的到来。

二、“团结”号节点舱(Unity)简介:“团结”号(Unity)节点舱是国际空间站的第二个组件,也是国际空间站的第一个节点舱,于1998年12月4日由“奋进”号航天飞机送入轨道。

舱体长5.49米,直径4.57米,重11612千克,用于存贮货物和调节电力供应,是国际空间站上负责连接6个舱体的主要节点舱。

命名由来:由于该舱是国际空间站的第一个节点舱,因此也常被称为“节点1”(Node 1)。

根据NASA国际空间站计划主任兰迪•布林克利的解释,“Unity”这个名字代表了NASA、波音还有全世界国际空间站团队的共同努力,反映了国际空间站计划中的国际合作。

三、“星辰”号服务舱(Zvezda)简介:“星辰”号(Zvezda)服务舱是国际空间站的核心,是航天员生活和工作的主要场所,“星辰”号服务舱由俄罗斯出资和建造,于2000年7月12日发射,7月26日与国际空间站联合体对接。

航天科技知识普及资料

航天科技知识普及资料航天技术是指将航天器送入太空,以探索开发和利用太空及地球以外天体的综合性工程技术,又称空间技术。

以下是由店铺整理关于航天科技知识的内容,希望大家喜欢!航天科技知识1、建造国际空间站的主要目的及结构?建造国际空间站的目的总的来说就是在太空建立一个永久性的科学实验室,上面能安放各种研究设备和实验仪器,以便航天员利用太空微重力环境长期进行科学研究。

具体地说有5个目的:(1)建造一个世界级的研究实验室,以便进行高质量的科学研究;(2)充分利用太空微重力资源;(3)让航天员能长期在上面工作与生活;(4)探索一种有效的国际合作机制;(5)为发展21世纪的科学技术提供一个理想的“试验平台”。

国际空间站的主要结构:(1)基础桁架,用来安装各舱段、太阳能电池板、移动服务系统及站外暴露试验设施等;(2)居住舱,主要用于航天员的生活居住,其中包括走廊、厕所、淋浴、睡站和医疗设施,由美国承担研制和发射到太空;(3)服务舱,内含科学仪器设备等服务设施,也含一部分居住功能,由俄罗斯研制并发射;(4)功能货舱,内设有航天员生命保障设施和一部分居住功能以及电源、燃料暂存地等,舱体外部设有多向对接口,由俄罗斯研制并发射;(5)多个实验舱,其中美国1个、欧空局1个、日本1个、俄罗斯3个;(6)节点舱(3个),它们由美国和欧洲航天局研制,是连接各舱段的通道和航天员进行舱外活动的出口;(7)能源系统和太阳电池帆板,由美国和俄罗斯提供;(8)移动服务系统(主要是遥操纵机械臂),它由加拿大研制。

2、航天员在空间站上需要完成哪些工作及作息时间?空间站就是一个建在太空的研究实验室,因此航天员在空间站上的一项重要工作就是利用站上的科研仪器或试验设备进行科学研究或实验;另外航天员在空间站上需要完成大量的太空行走(即出舱活动),出舱活动的目的一是组装国际空间站,还有就是对空间站的维修和保养(如前苏联的和平号空间站);第三是日常事务或工作,如完成地面控制中心下达的临时任务,更新站上计算机上的数据,对站上的设备进行测试和检查等。

太空中的生活国际空间站的居住和工作环境

太空中的生活国际空间站的居住和工作环境太空中的生活:国际空间站的居住和工作环境国际空间站(International Space Station,ISS)是人类在太空中进行科学研究和载人任务的重要基地。

作为一个长期居住和工作的空间环境,ISS的居住和工作环境必须经过精心设计和配置,以确保宇航员的安全、健康和生产力。

本文将介绍国际空间站的居住和工作环境,包括空间站的结构与布局、生活条件、设施设备以及多任务工作的挑战等内容。

一、空间站的结构与布局国际空间站由多个模块组成,包括核心模块、实验室模块、舱门和对接口、太阳能板等。

这些模块被连接在一起,形成一个复杂的结构。

整个空间站的布局考虑了空间利用效率、航天器对接、重力和微重力环境等因素。

作为宇航员的居住区域,空间站内部被划分为不同的功能区域,如睡眠区、工作区、卫生间、健身区等。

每个区域都通过通道或舱门相连,方便宇航员的活动和移动。

此外,为了满足宇航员的基本需求,空间站还配备了食品供应区和饮用水循环系统。

二、生活条件在太空中,宇航员需要适应微重力环境和高辐射环境,这对他们的身体和心理健康都有一定的挑战。

为了提供良好的生活条件,国际空间站采取了一系列措施。

首先,空间站内部必须保持适宜的温度和湿度。

由于太空中温度极低,空间站内部设有恒温系统,确保宇航员的舒适度和健康。

同时,湿度的控制也非常重要,以防止水分损失过快。

其次,宇航员的睡眠和休息也需要特别关注。

在没有重力的环境下,宇航员必须通过固定自己的身体和使用特制的睡眠袋来保持在狭小的空间内的睡眠。

此外,为了调节生物钟,宇航员还会定期使用调光灯等设备来模拟日夜变化。

再次,饮食是保持宇航员健康和营养均衡的关键。

由于食物在太空中容易腐败,必须使用特殊的技术和包装来保证食品的新鲜和安全性。

此外,空间站还配备了水循环系统,使宇航员能够获得足够的饮用水。

三、设施设备国际空间站为宇航员提供了一系列工作设施和科学实验设备,以支持他们在太空中进行科学研究和任务执行。

国际空间站的系统组成

指 令 与数 据 处 理 ( D C H)系 统

站 级 控 制 软 件 站 级 控 制 软 件 覆 盖 了空 间 站 的 所 有 部 件 的运 行 , 为 美 国 部 分 所 拥 有 ,其 他 合

作 者 并 不 具 备 。 站 级 控 制 软 件 划 分 为 7种

计算机 ,报 警 与预 警显 示 ,3 台处理 机 , 3

( VM )提 供 1 0 V/c 的一 ,听觉 信 号为 重复 喇 叭声 ;2级 为 报警 ,视觉 信 号为 红色 ,听 觉信 号为警 笛 声 ;3 级 为警示 ,视 觉信 号

为 黄 色 ,听 觉 信 号 为 持 续 声 ;4级 为 提 醒 , 无 告 警 信 号 , 仅 有 系 统 状 态 与 过 程 的 信 息

站载 计算 机 组装 完成 后 ,IS站上将 有 1 0台 以 S 0

上 的 各 种 计 算 机 , 主 要 用 于 采 集 站 上 系 统

人 工作站 计算 机和 乘 员健康 保 障膝上 计算 机 。所 有 计 算 机 显 示 屏 上 的语 言 均 为 英

语 , 计 量 单 位 为 公制 。 如 果 需 要 , 也 可 增

算机 ,报警 与预警 显示 ,3 3台处理 机 ,1 1

条 总 线 , 与美 国共 用 多 链 段 总 线 。 ,

E A 的 COF ( M )有 1种 类 型 的 S AP

通 过乘 员接 口计 算机 指令模 式转 变 。转换

到 临 近 操 作 、 救 生 或 确 保 安 全 乘 员 返 回 的 指 令 也 可 发 自外 部 航 天 器 。站 级 控 制 软 件 只 能 自动 切 换 到 两 种 模 式 : 从 其 他 模 式 到 救 生 模 式 ,从 微 重 力 模 式 到 标 准 模 式 。

佳仪电子产品选型指南-航电分册

佳仪电子产品选型指南——航电分册公司简介成都佳仪电子有限公司成立于2008年5月,是一家专注于嵌入式计算机及航电产品设计、制造、及销售服务的专业公司。

其主要人员有着多年嵌入式计算机及航电产品的应用开发经验。

凭借良好的信誉、持续的知识积累和细致入微的服务,佳仪电子公司产品已广泛应用于航空、航天、中船、电子、兵器、核工业、中科院等军用电子领域。

成都佳仪电子自主研发的产品分为三个产品系列,分别是嵌入式产品系列、航电通信产品系列及cPCI加固系统系列。

佳仪电子嵌入式产品包括PowerPC嵌入式控制器模块,创新结构的PC/104plus、PCI-104、PCIe/104及PCI/104-Express产品。

佳仪电子航电通信产品包括MIL-STD-1553B产品,ARINC429产品,HDLC、CSDB、LVDS、RS422/485/232等串行通信产品。

佳仪电子cPCI加固系列主要包括cPCI加固系统、机箱、背板等产品。

“专攻术业,创新发展”。

佳仪电子以专注和创新为本,在技术和商业模式上不断进取,与时俱进。

“分享共赢,厚德载物”。

佳仪电子始终坚持较高的道德标准,唯有如此,公司发展才能生生不息,基业长青。

MIL-STD-1553产品系列1.1 主要性能特性⏹满足GJB289A-97标准⏹支持多种通用计算机总线:PCI,CPCI/PXI,PC/104,PCMCIA,ISA等⏹自主研发协议芯片⏹单功能、多功能设计⏹每通道**MB板上存储空间⏹多功能卡实现1553B总线仿真⏹单通道、双通道选择⏹事件消息和周期消息处理⏹插入消息实时处理⏹支持Windows98/2000/XP/Linux操作系统⏹支持VC,VB,Delphi,LabVIEW,CVI等编程语言⏹功能强大中文应用程序,方便用户调试和测试使用⏹工业级设计:-40~+85℃1.2 关于MIL-STD-1553MIL-STD-1553是定义数据总线电气和协议特性的美国军方标准,目前国内想对应的最新标准为GJB289A-97。

国际空间站最新科技应用概述

国际空间站最新科技应用概述国际空间站(International Space Station,简称ISS)是迄今为止人类在太空中建造的最大和最复杂的空间结构,也是人类合作与探索的壮举。

这项国际合作的工程拥有一个多国船员,致力于进行科学研究,技术开发和太空探索。

国际空间站的建设始于1998年,至今已经取得了巨大的进展,广泛应用了最新科技,推动了太空科学和技术的发展。

一、生命保障系统技术在国际空间站中,维持船员的生命和健康是至关重要的。

最新的科技应用使得空间站的生命保障系统更加可靠。

这些系统包括空气再循环、水循环、废水处理和垃圾管理等技术。

空气再循环系统利用化学吸附和晶体分离等技术去除二氧化碳、水蒸气和杂质气体,同时释放氧气,确保船员的呼吸空气清新。

水循环系统则将船员使用过的水进行处理和过滤,重复利用,减少对地球淡水资源的需求。

废水处理系统则将船员排泄的尿液和污水进行过滤和杀菌处理,提供干净的饮用水和洗浴水。

垃圾管理系统则通过压缩、烧毁和回收等技术处理废弃物,减少对空间站空间的占用和对资源的浪费。

二、空间科学实验技术国际空间站是进行太空科学实验的理想平台。

最新科技应用使得空间站能够开展多领域的科学实验。

航天器设计师充分考虑一些基本问题,如浮力、引力以及空气和水的行为等,以为研究人员提供尽可能真实的环境。

船员可以进行物理学、生物学、医学和化学等多个领域的实验,探索在太空中独特的物理和化学性质以及生命的适应能力。

例如,在微重力环境中,船员可以研究宇宙射线对人类身体的影响,以及肌肉和骨骼的变化。

这些实验结果有助于我们更好地了解地球和太空的相互作用,为人类未来的太空探索提供了宝贵的数据。

三、航天器对接与维修技术国际空间站不断引入最新的科技应用,以改善航天器的对接和维修技术,确保空间站的正常运行。

航天器对接是实现国际空间站多模块集成的关键技术之一。

最新的对接系统采用了激光测距和图像识别技术,使得不同国家的航天器能够准确对接,并实现气密性和电气连接。

飞船与空间站对接原理

飞船与空间站对接原理原理1:空间交会与对接技术是指两个航天器在空间轨道上会合并在结构上连成一个整体的技术。

广泛用于空间站、空间实验室、空间通信和遥感平台等大型空间设施在轨装配、回收、补给、维修以及空间救援等领域。

意义空间交会与对接是载人航天活动的三大基本技术之一。

所谓三大基本技术就是载人航天器的成功发射和航天员安全返回技术、空间出舱活动技术和空间交会对接技术。

只有掌握它们,人类才能自由出入太空,更有效地开发宇宙资源。

对于国家来说,还能独立、平等地参加国际合作。

在突破并掌握了载人航天的基本技术之后,宇宙飞船的主要用途就是为空间站和月球基地等接送航天员和物资。

在航天领域专家常说的一句话是:“造船为建站,建站为应用。

”至今发射的宇宙飞船大多是作为空间站的天地往返交通工具和长期停靠在空间站上的救生艇。

为了实现宇宙飞船的运输功能,就必须攻克两项关键技术,那就是宇宙飞船与空间站的空间交会技术与对接技术,主要设备是交会测量系统和对接机构。

航天器之间的空间交会对接技术很复杂。

在国外载人航天活动早期,航天器之间的空间交会对接过程中经常发生故障与事故,即使在1997年,俄罗斯的两个航天器还发生过一次重大的空间交会对接事故——“进步M3-4”飞船与“和平”号空间站相撞,使“和平”号空间站上的“光谱”号舱被迫关闭,部分氧气泄漏,动力系统也受到影响。

通过多年的努力,目前美国和苏联/俄罗斯已完全掌握了在地面支持下的载人交会与对接技术。

尤其是苏联/俄罗斯在掌握了空间交会与对接技术以后,先后利用飞船的运输能力发展了几代载人空间站,在空间交会与对接等方面一直占据着技术优势。

虽然起步较晚,但欧洲、日本等国家在空间交会与对接研究方面已取得长足进步,特别是某些单项技术和设备,如地面仿真、对接敏感器等,都取得了惊人的进步。

日本曾于1998年通过两颗卫星成功进行了无人交会与对接在轨试验,2009年又用首个H2转移飞行器实现了与国际空间站的交会对接。

国际空间站的建设及其在空间科技研究中的应用

国际空间站的建设及其在空间科技研究中的应用随着人类探索和科技发展的不断深入,对于太空的探索也变得越来越重要。

在这其中,国际空间站是一个具有重大意义的太空项目。

本文将从国际空间站的建设、运营、科学实验等多个方面进行探讨,以深入了解国际空间站的重要性及其在空间科技研究中的应用。

一、国际空间站的建设国际空间站是由5个国家合作建设的,包括美国、俄罗斯、欧洲、日本和加拿大。

这个项目始于20世纪90年代,目的是为了探索太空领域,促进国际合作,推动科技发展。

国际空间站于1998年11月20日开始建设,并于2000年11月2日正式对外开放。

截至目前,国际空间站已经运营了20年,是人类空间探索的重要成果之一。

国际空间站位于地球的近地轨道上,距离地球约400公里。

它的结构由多个模块组成,包括可以容纳宇航员生活和工作的居住模块、供电模块、实验模块、卫星对接模块等。

整个空间站的体积相当于一个足球场大小。

二、国际空间站的运营国际空间站的运营由多个国家共同负责。

宇航员通常会进行为期6个月的轮流工作,他们会完成维护设备、科学实验等多个任务。

另外,国际空间站还拥有各种高科技设备,例如太阳能板、舱外活动装备等,这些设备也需要进行维护和更新。

由于国际空间站无法直接从地球上获取氧气、水和食品等资源,所以需要进行补给。

此外,国际空间站还需要深入的卫生保健,确保宇航员的身体健康。

因此,国际空间站的运营需要24小时不间断的工作。

三、国际空间站的科学实验国际空间站可进行各种类型的科学实验,它为人类探索太空提供了宝贵的机会。

每个国家都可以使用国际空间站进行研究,这些研究可能包括关于生命科学、物理学、化学、气象学和地球观测等领域。

下面将分别探讨国际空间站在以上几个领域中的应用。

1、生命科学国际空间站可以进行多种类型的生命科学研究。

例如,宇航员的身体反应、长期缺少身体重力的影响、微重力环境下细胞的生长等。

这些研究可以帮助我们更好地理解人类身体的形式、功能与健康,有利于我们更好地预防和治疗疾病。

20世纪世界航天器的发展

匆曾曩器的塞羼中国科学院院士杨嘉墀‘高级工程师庞之浩“(中国空间技术研究院,北京100081)摘要:本文综述了20世纪世界航天器的发展。

内容包括科学探测、地球观测和军事应用的地球卫星、地球轨道和登月的载人飞船。

对人类长期在轨的空间站、运载工具和太阳系探测等也简要地进行了摘述。

关键词:人造地球卫星宇宙飞船空间站航天飞机空间探测器l序曲自古以来,人类一直梦想离开地球,飞向太空,去欣赏那里的美景,探索那里的奥秘,开发那里的资源。

然而,虽然经过无数次勇敢地尝试,但由于技术条件的限制,人类的脚步始终没能离开养育自己的摇篮:地球。

经过祖祖辈辈的努力和科学技术的日新月异,人类终,于在20世纪迈入了通天的门槛,开创了除陆地、海洋和大气层之外的第四个生存环境,大大加速了社会的发展。

从此,各类形形色色的运载火箭、人造卫星、空间探测器、宇宙飞船、空间站和航天飞机等航天运输系统和航天器竞相登天献技,产生了巨大效益,成为具有划时代意义的科技。

它们是现代科技的高度综合,并又推动科技和工业的全面进步。

它们改变了人类的工作、生活甚至思维方式,不但造福现代,还将造福未来。

2人造卫星当空舞运载火箭是人类通天的交通工具。

但开发太空还要靠航天器。

到1998年底,全球共把5134个航天器送入太空,它们分无人航天器和载人航天器两类,其中无人航天器包括人造地球卫星和空间探测器,载人航天器包括载人飞船、空间站和航天飞机。

在20世纪,发射数量最多、用途最广的航天器当数人造地球卫星了,它为人类带来巨大财富,使人类在获取、传输和加工信息资源的广度和深度上产生了质的飞跃。

至今,已研制了科学、技术试验和应用三类卫星。

它们各有千秋,在航天领域均能独树一帜。

科学卫星相当于一个太空天文台,它轻而易举地改变了以往坐地观地、从地观天的传统,摆脱大气层的封锁,实现全波段科学观测,对人类科学认识宇宙有革命性地推动。

它主要包括空间探测卫星和天文卫星,其中前苏联发射的世界第一颗卫星以及美国和中国第一颗卫星均属于前者,后者则谱写了现代天文学的新篇章,“哈勃”空间望远镜是其典型代表。

国际空间站综合医学系统简介

与以往任何航天计划相比,IMedS的能力是非 常强大的。除了电生理学和肺功能测试外,还包括 大量血液生化、尿物理和化学测试。对于急需影像

提供的设备是相辅相成的,并且基本上是加强的, 以确保对ISS乘组人员不间断地实施医学保障。俄 罗斯医学硬件某些组件的第二个目的是进行生物 医学研究,或作为发生医疗意外事件或主设备出现 故障时的备份设备。

CHeCS 系统 CMS

EHS

表1美国提供的乘员医学保障设备(美国乘员保健系统,CHeCS)

设备

描

支持的医疗意外事故,IMedS可以使用ISS人体研 究设备中的多功能超声系统。在人类航天史上,影 像诊断第一次成为降低医疗风险的必须能力。

1美国提供的IMedS组件

CHeCS对抗措施系统(CMS)用来监测乘员 健康,提供对抗措施,同时监控乘员执行对抗措施 的情况。环境健康系统(EHS)监测空气和水质中 的化学和微生物污染物、测量辐射水平,并允许取 样和分析表面微生物和真菌的污染。CHeCS健康 维护系统(HMS)是为了监测乘员的健康、应对乘 员的疾病/伤害、提供预防保健、并确保紧急转移 时的稳定性。

载人航天信息2019年第3期

•航天医学・

国际空间站综合医学系统简介

摘要:虽然国际空间站(ISS)最初的医学供应机构分别提供了医学和对抗措施硬件以及飞行中的医学实 施计划,但它们最终是以整合的方式实施的。国际空间站综合医学系统将整个空间站上的医学保障资产统 一视为ISS IMedSo本文简要介绍了美国和俄罗斯分别对国际空间站综合医学系统所提供的组件。

超级计算机在太空科研中的应用研究

超级计算机在太空科研中的应用研究随着科技的发展,我们的生活发生了很多变化。

科技不仅改善了我们的生活,还为社会带来了诸多各行各业的创新。

其中,超级计算机在科学研究中起了重要的作用。

目前,人类在太空领域中取得了很多的成功,比如Apollo 11号登月计划、国际空间站的建设等,这些都离不开超级计算机在太空科研中的应用研究。

太空科研需要大量数据处理和分析,这就需要用到快速、强大的计算机。

超级计算机,顾名思义,就是计算能力超强的计算机。

它可以完成普通计算机无法完成的复杂计算,从而在科学研究领域中发挥出重要的作用。

在太空科研中,超级计算机可以模拟太空中各种物理现象,预测太空中的行星运动、天体碰撞、恒星爆炸等事件,从而帮助科学家更好地理解宇宙的奥秘。

超级计算机可以帮助太空科学家模拟宇宙中的各种现象,从而更好地理解宇宙。

宇宙是一个充满奥秘的地方,我们对宇宙的认识还相当有限。

想要深入了解宇宙,就需要通过模拟来提出更多的猜测。

超级计算机可以模拟宇宙大爆炸、恒星形成、行星碰撞、黑洞吞噬等现象,从而帮助科学家更好地理解宇宙的起源和演化。

此外,超级计算机还可以计算地球外星球上的气候变化、物质运动、磁力场变化等重要现象,帮助人们更好地了解太阳系中其他星球的状况。

超级计算机在太空科研中还可以帮助科学家更好地分析数据。

太空探索中产生的数据量巨大,需要进行大量的数据处理和分析。

而超级计算机可以帮助科学家更快地处理和分析这些数据,从而在太空探索中提供更准确的数据支持。

比如,超级计算机可以进行雷达数据处理,帮助科学家获取更高解析度的地图,以便更好地了解行星表面的地形。

此外,超级计算机还可以处理遥测数据、卫星图像等数据,更好地支持太空科研工作。

超级计算机在太空科研中的应用还包括卫星设计和探测器设计。

卫星设计和探测器设计需要进行大量的模拟和计算,以确保它们在太空环境下的可靠性和稳定性。

而超级计算机可以帮助科学家进行卫星和探测器的模拟设计,提出更好的设计方案,并在实际飞行前进行测试,确保它们能够在太空中顺利运行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

国际空间站上使用的两种计算机周 林(中国空间技术研究院总体设计部 北京 100086)文 摘 欧空局为国际空间站研制了两个新型的计算机:容错计算机(FT C)和标准有效载荷计算机(SPL C),它们可以满足空间站对计算机的需要,可以方便地构成各分种布式数据管理结构。

文中介绍这两种不同类型的计算机设计。

主题词 国际空间站 容错计算机 有效载荷计算机前 言在过去10年期间,商用电子设备和专用微处理器、存储器芯片以及随后的硬件设备的寿命变得越来越短了。

事实上,每隔半年,计算机的性能就翻一倍。

在使用新技术方面,地面与太空应用新技术的间隙变得越来越宽了。

在将商业产品应用在空间领域时,特殊的空间环境约束不允许将新技术集成在具有安全性、关键性、高可靠性要求的系统功能中。

其主要原因是太空环境对专用处理器和存储器芯片具有高可靠的、抗辐射EEE性能。

于是,只好采取为每一项特殊的空间任务专门设计一种解决方案的方法,这种方法就成了制定研制计划、增加费用的主要驱动力。

因此,软件工程也成了特有的、专用的产品,并且需要专门研制地面支持设备和软件设计的开发环境。

为了避免这种情况,欧空局从加快研制进度和标准化的角度出发,大胆改进了以往传统的设计方法,使地面系统和飞行器上的软件都可使用商业上的产品,将飞行器上的硬件结构制作成标准组件并具有可重构性,使它既能够完成多种太空任务,又能够与商用硬件和软件接口。

对于安全性、关键性任务,最好的设计思想是要求设备容忍故障而不是避免故障。

1 新的设计概念在空间电子学和地面电子学之间(特别是在计算机应用领域)的技术鸿沟将长期存在,这是因为空间电子设备必须经受辐射的考验,因此,某些对辐射敏感的技术就不能用在空间设备上。

从而引起一种新的脱离先前的专门设计的理念,欧空局提出了研制通用型标准计算机的思想。

这种计算机可以普遍应用在空间飞行器上,达到了减少工程费用,缩短设计、开发周期的目的。

这种计算机首先在国际空间站计算机设计中得到了验证。

这种新的设计理念具有下列关键特性:¹在两级水平上积木化:即首先在EU RO标准尺寸的基板上集成基本功能;然后,用钩将第二层板固定在基板的上部,该板称为夹层板;º开放式计算机结构;»可以选择寄存在一个主板上的功能,便于改变各板的连接方式;¼精密的设备接口标准:VEM(工业内部计算机总线标准),MIL-STD-1553B接口,以太网接口,RS-422接口,视频接口。

½选用商用宽温型处理器(SPARC),使其具有抗辐射的能力。

但是,在设计CPU计板结构时,应考虑使其将来能够适应小型化设计的变化。

¾使用标准商用实时操作系统,确保与商用软件产品、地面设备和软件开发环境兼容。

收稿日期:2004-03-22¿将输入/输出功能与中央处理单元(CPU )分离,这就意味着使用具有智能化的外围接口,减少CPU 的负担,可以随着任务的需要,增加数据流量。

À将软件进行分层,定义各层之间的接口。

典型的软件层次如下:板级支持软件包(硬件到软件接口);操作系统与硬件驱动;对外通信用接口协议软件。

由于这些新的设计理念,出现了安全性、关键性任务要求的容错计算机设计和国际空间站实验设备用标准有效载荷处理器两种计算机设计方案。

2 容错计算机为了满足空间任务的要求——高可靠性、高效率和抗辐射,欧空局设计了容错计算机(FTC)。

它是一个按照标准规格设计的计算机,可以向用户提供极强的处理能力,可以容忍两个不同时出现的故障。

为了进行通信,FTC 装备了六套MIL -STD -1553B 总线接口,支持同步包传输(SPT )协议。

2.1 拜占庭故障算法一台FT C 由多台相同的计算机(含硬件和软件)组成,每台都占有一个单独的外壳,称为故障保留区(FCR )。

它们同步操作、执行相同的用户任务软件。

依靠所设计的容错策略,四个FCR (如果要求容忍两个故障)可以连接成一个FTC 。

这种设计的基础称为拜占庭故障算法。

按照这个理论,如果满足下述条件,一台计算机就可以隔离F 个任意故障。

这些条件是:¹计算机必须有3F+1个故障保留区(FCR);º这些故障保留区(FCR)必须通过2F +1个不相交的路径相连;»数据必须在FCR 区和按照拜占庭故障算法设计的表决器之间交换F +1次;¼所有FCR 的同步必须限制在一个有限的偏差内。

在FT C 的硬件、软件设计中,已经严格地、一致地证明了这一理论的正确性。

例如当F=1时,FT C 由四个FCR 组成,该FTC 可以处理一个任意的故障。

如果一个故障具有暂时性的特点,即由一个单一事件的干扰产生的,那么在检测到这个故障时,就将这个故障屏蔽起来,FT C 继续运行。

如果在100m s 时间帧内相同的故障发生n 次,可以认定为固定故障,就自动地隔离(或使之无效)有故障的FCR,FT C 继续在三个FCR 结构上运行。

在这种结构中,通过多数表决检测并隔离故障。

在这个意义上,这种设计能够满足容忍两个故障的要求。

2.2 容错计算机系统使用一个供电母线和开关,就可以支持具有一个、二个、三个或者四个FCR 的FT C 。

每个FCR 机箱都可以互换,在运行期间可以重新集成。

一个FT C 上的所有的FCR 通过一个交叉捷连互相连接,其功能是:¹需要表决的数据交换;º由一个容错时钟完成软件处理和数据分配的同步;»由剩余的FCR(4-FCR 结构)对故障的FCR 进行容错表决、隔离(Reset)。

图1 FTC 交叉连接为了避免故障在FCR 之间扩散,采用电性能隔离的点对点连接实现交叉捷连。

图1表示一个完整的、具有四个FCR 的FT C 结构,并且描述了交叉捷连的互连方式及连接到M IL -ST D -1553B 总线的接口原理。

每个FCR 都是一个独立的处理器,该处理器运行用户应用软件(U AS)。

为了减轻用户的故障管理功能,该处理器同时负责故障管理和M IL-ST D-1553B 总线接口的管理。

如图2所示,FCR 具有三层结构。

VM E 工业标准总线将故障管理层和应用层严格地分开。

该应用层电路板(ALB)设计基于抗辐射、与SPARC兼容的ERC32芯片,并使用标准实时操作系统Vx w orks,构成用户应用软件平台。

故障管理层(FM L)电路板和航空电子学接口(AV I)的电路板设计在T805/20M Hz的基板上。

FM L PCB提供故障管理功能,为FCR交叉捷连提供电性去耦接口。

AVI电路板提供用户M IL-STD-1553B总线的物理接口。

为了便于测试,需要装载监控程序(Debug)和故障注入软件,ALB和AVI电路板提供双向串行测试接口。

3 通用型标准有效载荷计算机在空间技术中,标准有效载荷计算机(SPLC)代表一种新颖的设计思想,可以完全满足有效载荷的需求。

如图3所示,SPLC驻留在有效载荷和国际空间站(ISS)数据管理系统之间,它结束了以前费用高、耗时多的传统的设计方法,结束了为每个新的有效载荷项目单独地、专门地开发一个计算机的历史。

3.1 SPLC的关键性能SPLC的关键性能包括下列4项,即¹根据有效载荷任务的需要,利用符合空间环境要求的标准计算机芯片构成一个标准的计算机系统。

º为了兼顾有效载荷和ISS之间的通信,基于M IL-ST D-1553B总线、以太网接口,或是CCSDS数据包协议,使用已经鉴定的接口软件。

»具有一个标准化、一致性的软件开发环境和地面支持设备。

¼基于开放式VME总线标准的商用操作系统VxWo rks。

该操作系统具有成熟的能力,特别是在研制非标准设备时也可以集成VxWo rks,并在其上开发应用软件。

这种理念允许在有效载荷设计开发中使用一个全新的方法,显著地减少了开发周期、费用和风险,为ISS使用有效载荷标准计算机打下了良好的基础。

3.2 SPLC方案如图4所示,SPLC基于宽范围的工业标准VM E总线,包括VME板和几个可选择的多层板,其外壳与FCR相同。

多层板方案允许对输入和输出板进行高密度的封装,从而减少了质量和设备的体积。

3.3 标准计算机配套板除了计算机主板外,根据任务需要,可以选择下列配套板。

为了与ISS数据管理系统通信,可以选用MIL-STD-1553B总线接口板和以太网接口板。

在1553B总线多层板上还提供一个冗余总线I/F。

为了减轻主CPU对低级I/O控制的负担,该卡具有智能控制功能。

在软件研制期间,为了实现空间和地面的快速数据通信,提供一个以太网接口板,与网络的接口可以用AUI信号接口或者采用10Base-T集线器。

以太网多层卡采用商用设备改装,为了检查在轨辐射影响下的失效特性,设备必须经受耐辐射测试,从而推算出在低地球轨道上的耐受失效率。

为了防止电流剧烈增加时锁定效应破坏控制器和驱动器设备,特地设计一个防锁定电路保护板。

同时,为了防止设备产生过热,还安装了专用的热电偶或热管。

为了让航天员观察数据,并向航天员提供一个命令I/F,将搭接控制台连到一个以太网I/F上。

可以同时使用两个以太网接口。

为了直接控制有效载荷硬件,应插入两个多层板。

一个用于模拟量输入,读取从0到5V范围内的电压输入。

另一个用于数据输入和输出。

控制实验并读取状态信息。

用户根据需要选择I/O通道,可以预先设定数据采集速率。

为了采集高速数据,专门研制了一个高速多路选择板,它能够直接与ISS高速多路选择器相连。

为了将视频数据传送到舱内高速多路选择器,专门设置了一个模拟视频接口。

为了用热敏电阻采集温度参数,使用一个扩展模拟输入板。

为了进行数据存储和回放,在SPLC中使用了VM E板。

海量存储器提供85M字的存储能力,使用冗余闪存PCM CIA卡。

由于可能发生锁定效应,设计时采取了防护措施。

闪存对于单粒子翻转是很敏感的,这些翻转事件可以用PCM CIA卡控制器检测出来。

如果在一个字内出现2bit的错误,也可以纠正过来。

SPLC标准外壳有5槽的铝箱和8槽的铝箱两种结构。

其上部有盖板,内置VM E底板和电源,内部采用传导致冷的VM E板。

为了进行SPLC软件研制、调整和测试,设置一个基于经典测试方法的SDE/EGSE板。

该板安装在具有VM E总线的机箱内的空槽上,利用板上的激励源和测试功能,进行SPLC功能性测试和运行检查。

3.4 SPLC的状态根据最恶劣的发射和操作环境(阿里安运载火箭、航天飞机、SPLC计算机已用在美国实验室、哥伦比亚舱)的要求制定实验条件。

SPLC中选用的I/O卡、CPU、VM E扩展接口、海量存储器和外壳都已作过环境实验(振动、热真空和电磁兼容性实验)。