Cadence_SPB16.2中文教程

cadence中文教程整理版

第一章.Cadence cdsSPICE的使用说明Cadence cdsSPICE 也是众多使用SPICE内核的电路模拟软件之一。

因此他在使用上会有部分同我们平时所用到的PSPICE相同。

这里我将侧重讲一下它的一些特殊用法。

§ 1-1 进入Cadence软件包一.在工作站上使用在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作。

Icfb调出Cadence软件。

出现的主窗口如图1-1-1所示:图1-1-1Candence主窗口二.在PC机上使用1)将PC机的颜色属性改为256色(这一步必须);2)打开Exceed软件,一般选用xstart软件,以下是使用步骤:start method选择REXEC(TCP-IP) ,Programm选择Xwindow。

Host选择10.13.71.32 或10.13.71.33。

host type选择sun。

并点击后面的按钮,在弹出菜单中选择command tool。

确认选择完毕后,点击run!3)在提示符ZDASIC22> 下键入:setenv DISPLAY 本机ip:0.0(回车)4)在命令行中(提示符后,如:ZUEDA22>)键入以下命令icfb&↙(回车键)即进入cadence中。

出现的主窗口如图1-1-1所示。

以上是使用xstart登陆cadance的方法。

在使用其他软件登陆cadance时,可能在登录前要修改文件.cshrc,方法如下:在提示符下输入如下命令:vi .cshrc↙(进入全屏幕编辑程序vi)将光标移至setevn DISPLAY ZDASIC22:0.0 处,将“ZDASIC22”改为PC机的IP,其它不变(重新回到服务器上运行时,还需按原样改回)。

改完后存盘退出。

然后输入如下命令:source .cshrc↙(重新载入该文件)以下介绍一下全屏幕编辑程序vi的一些使用方法:vi使用了两种状态,一是指令态(Command Mode),另一是插入态(Insert Mode)。

Cadence SPB v16.2 安装及完整破解详细说明

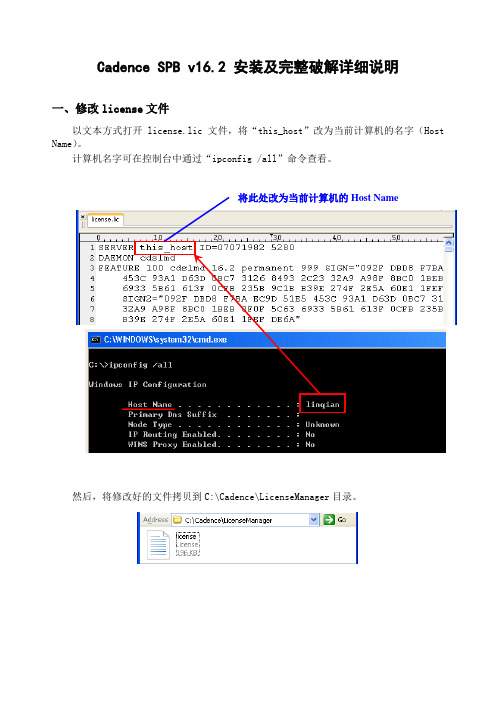

Cadence SPB v16.2 安装及完整破解详细说明一、修改license 文件以文本方式打开license.lic 文件,将“this_host ”改为当前计算机的名字(Host Name )。

计算机名字可在控制台中通过“ipconfig /all ”命令查看。

然后,将修改好的文件拷贝到C:\Cadence\LicenseManager 目录。

Host Name二、准备安装程序Cadence SPB v16.2共有三张安装光盘,将所有安装文件解压到同一目录下,分别对应\Disk1、\Disk2、\Disk3三个独立文件夹。

三、安装License Manager双击setup.exe,启动安装向导。

选择安装License Manager。

安装过程会提示选择License文件,选择先前修改好的那个license.lic。

在License Server Data中的Port Number框内,保留“5280”即可;但本身可能会在数字后留有若干空格,必须将这些空格删除,否则点“Next”会报错。

License Manager安装成功后,可以看到在license.lic文件中修改过的计算机名。

启动LmTool工具来设定License Manager。

在Service/License File选项卡中选择“Configuration using Services”。

在Config Services选项卡中的Path to the license file框中载入先前修改过的license.lic文件。

点击“Save Service”并确认保存。

在Start/Stop/Reread选项卡中可启动或停止License Manager服务。

软件正常工作时要保证服务处于启动状态。

四、正式安装Cadence套件在安装向导中选择“Product Installation”。

建议在安装前关闭所有的杀毒软件和防火墙,否则有些配置文件无法写入。

Cadence Allegro 16.2规则设置

Spacing规则(约束)Rexdlutarm@2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:1直接的:Net中写数值,2 间接的:创建Constraint Set,然后Assign给Net;这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

使用第二种约束设置方式的约束设置步骤:1约束的对象2约束的内容3给对象分配内容1这3个步骤默默的引导着所有间接约束的设置。

基本约束预备先理解:Net class2Net class-classRegionRegion-classRegion-class-classBus……现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:Creat & Set之后3给Net分配规则:更高级的约束:What Can U Think?有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

CADENCEPCB设计中文教程

CADENCEPCB设计中文教程CADENCE是一种著名的电子设计自动化(EDA)工具,广泛应用于PCB (Printed Circuit Board,印刷电路板)设计。

CADENCE PCB设计软件在工业界具有广泛的应用,设计工程师可以使用CADENCE软件来设计和制造高品质的电路板。

本教程将向您介绍CADENCE PCB设计的基本概念和步骤。

一、CADENCEPCB设计的基本概念1.原理图设计:首先,在CADENCE工具中,您需要绘制电路的原理图。

原理图是电路的图形表示,包含电路中所有元件(如电阻、电容、晶体管等)的符号和连接线,以及它们之间的连接关系。

您可以使用CADENCE工具库中提供的元件符号来绘制原理图。

2.元件库管理:CADENCE提供了一个元件库管理工具,您可以在其中创建和管理自定义的元件库。

通过元件库管理,您可以将常用的元件符号保存在库中,以便在不同的电路设计中重复使用。

3.PCB布局设计:在完成原理图设计后,您需要将电路中的元件布局在PCB上。

PCB是一个具有金属层、绝缘层和焊盘的印刷电路板。

CADENCE提供了一个布局工具,您可以在其中将各个元件放置在PCB上,并绘制它们之间的连接线。

4.线路连接:在CADENCE中,您可以使用布线工具将电路中的元件之间连接起来。

通过布线工具,您可以选择不同的线宽和线间距,并确保线路之间没有短路和断路。

布线完成后,您可以使用CADENCE的自动布线功能来优化线路布线,并提高电路性能。

5.电气规则检查:在完成PCB布局和布线后,您需要进行电气规则检查。

电气规则检查可以帮助您查找布局中的错误,如未连接的元件、未连接的引脚、引脚冲突等。

CADENCE提供了一些强大的电气规则检查工具,可帮助您轻松检查电路的正确性。

6. 制造文件生成:最后,在完成PCB设计后,您需要生成制造文件。

制造文件包括Gerber文件、钻孔文件和BOM(Bill of Materials,物料清单)等。

(整理)Cadence_SPB16.2入门教程——PCB布线.

Cadence_SPB16.2入门教程——PCB布线(一)PCB布线4.1 PCB层叠结构层叠结构是一个非常重要的问题,不可忽视,一般选择层叠结构考虑以下原则:·元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;·所有信号层尽可能与地平面相邻;·尽量避免两信号层直接相邻;·主电源尽可能与其对应地相邻;·兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在 50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:·元件面、焊接面为完整的地平面(屏蔽);·无相邻平行布线层;·所有信号层尽可能与地平面相邻;·关键信号与地层相邻,不跨分割区。

基于以上原则,对于一个四层板,优先考虑的层叠结构应该是:·S ←信号·G ←地平面·P ←电源层·S ←信号对于一个六层板,最优的层叠结构是:·S1 ←信号·G1 ←地平面·S2 ←信号·G2 ←地平面·P ←电源层·S4 ←信号对于一个八层板,有两种方案:方案 1:方案2:·S1 ←信号S1 ←信号·G1 ←地平面G1 ←地平面·S2 ←信号S2 ←信号·G2 ←地平面P1 ←电源层·P ←电源层G2 ←地平面·S3 ←信号S3 ←信号·G3 ←地平面P2 ←电源层·S4 ←信号S4 ←信号方案2主要是比方案1多了一个电源层,在电源比较多的情况下可以选择方案2。

对于更多层的结构也是按照上面的原则来定,可以参考其它的资料。

下面以SMDK6410核心板(设计为八层板)来设置层叠结构,包括规则设置,PCB布线等。

打开程序->Cadence SPB 16.2->PCB Editor,然后打开在第3 章布局好的PCB文件。

Cadence快速入门视频教程的SPB_16.2版本一

2. 教程内容

3. 软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 Layout Plus SmartRoute Calibrate:OrCAD 自带的 PCB 布线工具,功能不如 PCB Editor 强大 PCB Editor:Cadence 的 PCB 布线工具 PCB Librarian:Cadence 的 PCB 封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的 PCB 信号完整性信号仿真的工具 SigXplorer:Cadence 的 PCB 信号完整性信号仿真的工具

接下来,设置输入管脚的正负属性 :点击 Toolbar 的 Place Text,或者菜单 Place/Text,如下图:

输入-,点击 OK,再输入+,点击 OK, 如下图: 接下来放置管脚,如下图:

现在,完成了 NE5532 中两个运放中的一个,现在编辑另一个:

Ctrl+N,或者 View/Next Part,如下图:

4. 软件列表

5. 开始学习 Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图:

里面有很多选项,应该是对应不同的 License

本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL 是所有可选程序中,功能最强大的,但不知道,强在哪里;而且 本教程的原理图文件可以使用上表中不同的程序打开 6. 选择 OrCAD Capture CIS,启动后显示下图

Cadence SPB使用方法

Cadence SPB使用方法1.在用OrCad Capture CIS画电路原理图时,不同电路图页面之间的信号互联,单信号线(wire)用分页端口连接器(Off Page Connector)实现互联,总线(Bus)用端口(Port)实现互连(也可以用分页端口连接器(Off Page Connector))。

2.特别注意:在FPGA原理图设计中,在为FPGA设计原理图符号时,一般要将FPGA分为多个部分,这时一定要注意在管脚功能划分时,要将Bank2中用于配置的管脚,包括:配置模式选择管脚M0、M1,CCLK,DIN,INIT_B等与TMS,TCK,TDO,TDI 等一起划分到FPGA的配置(Configuration)部分。

3.在OrCad Capture CIS中制作原理图符号时,如果器件有多个(两个以上)管脚名称(pin name)相同,在保存该元件时就会弹出以下警告信息:因为ORCAD的封装(原理图符号)是有规则的,只有管脚为POWER属性才能同名,比如VCC,GND的管脚名等等,很好理解,这些属性在画PCB的时候默认的是同一个网络,是要连接在一起的,如GND连GND,VCC连VCC,有时候有很多的空脚NC 最好用NC1,NC2...来描述,避免不必要的错误,有的甚至连POWER属性的管脚名都不做重复的。

如果忽略这些这些警告信息,则当使用这些元件符号画电路图,在生成网表(Create Netlist)时就会产生错误:#79 Error [ALG0050] Duplicate Pin Name "SW" found on Package LM2852Y , U21 Pin Number 9: SCHEMATIC1, POWER SUPLLY (1.80, 3.20). Please renumber one of these.这时选中设计,可以利用accessories菜单的libcorrectionutil->library verification / correction来批量修改重复管脚定义(即:批量把重复的管脚名改为不同)。

破解Cadence SPB16.2 PSpice有的选项功能变灰色无法使用问题

破解Cadence SPB16.2 PSpice有的选项功能变灰色无法使用问题,以下操作后就能解决,自己在XP系统验证过可行。

1、用UltraEdit软件打开Cadence安装目录:Cadence\LicenseManager\license.dat以下有两个同样的删除一个(在3191行开始)。

FEATURE xilEdif cdslmd 16.2 permanent 999 SIGN="092F DBD8 F7BA EC9D 51E5 \ 453C 93A1 D63D 0BC7 3126 8493 2C23 32A9 A98F 8BC0 1BEB 0F0F 5C63 \6933 5B61 613F 0CFB 235B 9C1B B39E 274F 2E5A 60E1 1FEF DE6A" \SIGN2="092F DBD8 F7BA EC9D 51E5 453C 93A1 D63D 0BC7 3126 8493 2C23 \32A9 A98F 8BC0 1BEB 0F0F 5C63 6933 5B61 613F 0CFB 235B 9C1B \B39E 274F 2E5A 60E1 1FEF DE6A"2、删除以下一个(在2459行开始)。

FEATURE PSpiceBasics cdslmd 16.2 permanent 999 SIGN="092F DBD8 F7BA EC9D 51E5 \ 453C 93A1 D63D 0BC7 3126 8493 2C23 32A9 A98F 8BC0 1BEB 0F0F 5C63 \6933 5B61 613F 0CFB 235B 9C1B B39E 274F 2E5A 60E1 1FEF DE6A" \SIGN2="092F DBD8 F7BA EC9D 51E5 453C 93A1 D63D 0BC7 3126 8493 2C23 \32A9 A98F 8BC0 1BEB 0F0F 5C63 6933 5B61 613F 0CFB 235B 9C1B \B39E 274F 2E5A 60E1 1FEF DE6A"注意......注意......注意......注意......注意......注意......注意:以上操作后必须重新启动计算机。

Cadence SPB 16.2 Guide

Cadence SPB 16.2安装指南将此处改为你的计算机名(1)用记事本打开Crack目录的license.lic文件,将Server后ID前的那段文字改成你的计算机名。

先选择安装License Manager(2)运行Setup程式,首先安装License Manager。

(4)此处保留5280的端口数即可,但程式本身会留一些空格,直接点Next会 报端口错误,鼠标点击此框,按Del删除所有内容和空格后再填入5280即可。

(6)启动LmTools工具来设定License Manager刚才修改过的计算机名(5)License Manager安装成功后可以看到我们在Lic文件中修改过的计算机名(7)启动LmTools后选择Using Service而不是License File(8)把修改好的license.lic文件复制到Cadence安装目录的License Manager目录下(9)Path to the license file,点击Browese选择刚刚复制到LicenseManager的目 录的那个lic文件。

(10)选择完成后点击Save Service,然后在如下对话框确认“是”。

(11)在此启动或停止License Manager服务,软件正常工作时要保证服务处于启动状态。

(12)以上完成后,选择Product Installation。

(13)安装过程中如果有提示要选择什么授权文件,一律掠过点Next,如果一般只使用公司的lib文件,建议就不要安装自带的lib了,因为安装的时间很漫长。

(14)这步很重要,在license path文本框中填入5280@hostname即可,这里的hostname 就是之前修改lic文件时用的那个计算机名。

(15)把crack目录下的crack.exe程式拷贝到Cadence的安装目录下,然后运行,直到黑色 命令提示符窗口自动关闭。

(16)最后,重新启动系统,安装完成。

Cadence_Allegro16.2学习记录

Cadence_Allegro16.2学习记录Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输入Title Block所在的.OLB库文件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输入模版文件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输入正在设计的板的名称,Document Number中输入文件编号,Revision中输入版本号。

3.在添加新页时,模版图纸的上述信息会自动添加Orcad 中快速修改所有零件的Footprint方法一:一页一页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了方法二:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填入,也可以相同封装填一个,然后拖动该黑框的右下角十字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项目设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填入“\tPCBFootPrint”,在Combined property string栏中追加填入“\t{PCB footprint}”,不选Open in Excel,生成.BOM文件后,用excel手工导入.BOM文件,在导入步骤三中选择“文本”方式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有一处地方可输出带有机械尺寸的BOM表,选中顶层项目设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)

Cadence.Allegro.SPB.v16.2破解及安装步骤(已验证可行)严正声明:该破解及安装方法仅用于交流学习该软件,请不要以任何形式用于商业目的,本人不承担任何由个人或企业将此软件用于商业目的而引发的一切法律纠纷所带来后果,如需用于商业目的,请向Cadence 公司购买授权;否则后果自负。

从上一年到现在,一共安装了Cadence.Allegro.SPB.v16.2四次,非常痛惜,由于种种原因,前三次都以失败而告终,通过网上的安装经验及自己的摸索,功夫不负有心人,终于在今天下午将Candence Allego SPB16.2安装成功。

现把安装经验及注意事项分享如下:1.简介Cadence? Allegro是 Cadence 推出的先进 PCB 设计布线工具。

Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品 Capture 的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。

Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电路板布线的种种需求。

2. 安装及破解步骤步骤:一、下载好所需的安装光盘镜像文件,VeryCD网站上有有两个版本,一个是ISO 文件(共有3个ISO文件,占用空间1630MB左右);另个版本是两个BIN文件(占用空间1.10GB左右),本人所用的是第二个版本。

二、将上述文件(两个版本都可以)加载到虚拟光驱中,并打开,运行setup.exe 文件。

三、点击setup 进入安装界面,首先点击Licence Manger.如图所示:四、在首次安装LICENSE MANAGER的时候,安装程序会要求给出LICENSE FILE LOCATION,不要填任何东西,直接点击CANCLE结束这个对话框,如下图所示:五、将LICENSE.DAT复制到CADENCE文件夹中,然后用记事本打开它,将this_host改成你的计算机名称,并保存;六、查看计算机名称,如下图所示,我的计算机名称是 WWW-97F34E33509,而不是 WWW-97F34E33509. 就是说名称不包含末尾的句号!七、将cdslmd.exe复制到刚刚安装的LICENSE MANAGER文件夹中,覆盖原有的相同程序。

Cadence Allegro 16.X 安装说明(正版)

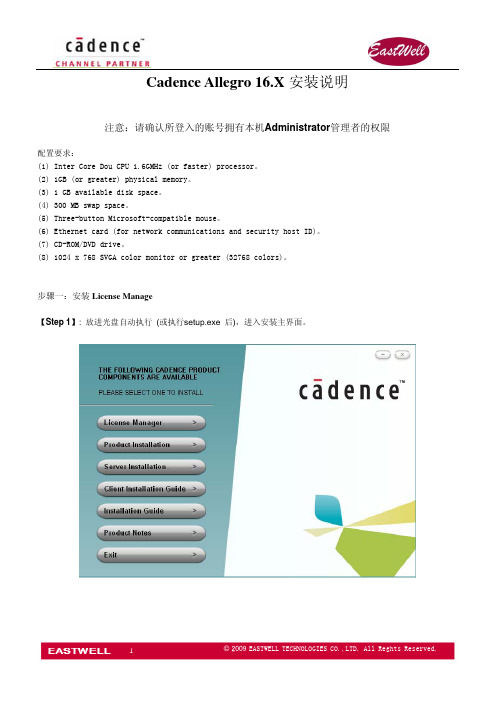

Cadence Allegro 16.X安装说明注意:请确认所登入的账号拥有本机Administrator管理者的权限配置要求:(1) Inter Core Dou CPU 1.6GMHz (or faster) processor。

(2) 1GB (or greater) physical memory。

(3) 1 GB available disk space。

(4) 300 MB swap space。

(5) Three-button Microsoft-compatible mouse。

(6) Ethernet card (for network communications and security host ID)。

(7) CD-ROM/DVD drive。

(8) 1024 x 768 SVGA color monitor or greater (32768 colors)。

步骤一:安装License Manage【Step 1】: 放进光盘自动执行(或执行setup.exe 后),进入安装主界面。

【Step 2】:安装10.80 的license Manager 程序,请按 NEXT 进入下一步。

【Step 3】: 设置licenseManager的安装路径C:\Cadence\licenseManager,请按 NEXT进入下一步(若需要修改请选Change) 。

【Step 4】: 按Install开始安装License Manager。

开始安装License Manager 的相关文件。

【Step 5】:指定License File。

请指到License文件,按 NEXT进入下一步。

Port Number:Cadence默认为5280Host Name:主机名(请注意不能有中文或空格)Log File:License Manager 的信息文件名默认为debug.logOptions Filel:可选文件(一般可不用设定)Vender Daemon Port Number:指定另一个Port Number(一般不用设定)步骤二:安装Products【Step 1】: 放进光盘自动执行后,进入窗口后执行Product installation。

cadence16.2 PCB入门中文学习教程

目录第1章焊盘制作 (1)1.1 用Pad Designer制作焊盘 (1)1.2 制作圆形热风焊盘 (6)第2章建立封装 (10)2.1 新建封装文件 (10)2.2 设置库路径 (11)2.3 画元件封装 (12)第3章元器件布局 (23)3.1 建立电路板(PCB) (23)3.2 导入网络表 (24)3.3 摆放元器件 (26)第4章 PCB布线 (31)4.1 PCB层叠结构 (31)4.2 布线规则设置 (33)4.2.1 对象(object) (35)4.2.2 建立差分对 (36)4.2.3 差分对规则设置 (37)4.2.4 CPU与DDR内存芯片走线约束规则 (39)4.2.5 设置物理线宽和过孔 (45)4.2.6 设置间距约束规则 (52)4.2.7 设置相同网络间距规则 (55)4.3 布线 (56)4.3.1 手工拉线 (56)4.3.2 应用区域规则 (59)4.3.3 扇出布线 (60)4.3.4 差分布线 (62)4.3.5 等长绕线 (64)4.3.6 分割平面 (65)第5章输出底片文件 (70)5.1 Artwork参数设置 (70)5.2 生成钻孔文件 (75)5.3 输出底片文件 (79)第1章焊盘制作1.1 用Pad Designer制作焊盘Allegro中制作焊盘的工作叫Pad Designer,所有SMD焊盘、通孔焊盘以及过孔都用该工具来制作。

打开程序->Cadence SPB 16.2->PCB Editer utilities->Pad Designer,弹出焊盘制作的界面,如图 1.1所示。

图 1.1 Pad Designer工具界面在Units下拉框中选择单位,常用的有Mils(毫英寸),Millimeter(毫米)。

根据实际情况选择。

在Hole type下拉框中选择钻孔的类型。

有如下三种选择:Circle Drill:圆形钻孔;Oval Slot:椭圆形孔;Rectangle Slot:矩形孔。

cadence16.2安装破解

cadence16.2安装破解Cadence SPB 16.2 下载安装破解在⽹上看到许多的招聘公司很多要求掌握cadence软件的操作,于是决定学习cadence软件。

下⾯就cadence SPB 16.2(别名cadence allegro 16.2)下载,安装,破解来加以说明,希望可以帮助到⼤家。

(XP系统)⼀.下载打开⽹址下载三个ISO⽂件(注意要安装迅雷软件)CD1下载⽹址ed2k://|file|%5BCadence.PCB%E8%AE%BE%E8%AE%A1%5D.TLF-SOFT-Cadenc e.Allegro.PCB.Design.v16.2-SHooTERS-CD1.iso|688369664|21d65384b95b9dd1aa4 b9325bd12b518|h=vb5y4jqk6ovw5suzwl5ztsmd4fnkuqg6|/CD2下载⽹址ed2k://|file|%5BCadence.PCB%E8%AE%BE%E8%AE%A1%5D.TLF-SOFT-Cadenc e.Allegro.PCB.Design.v16.2-SHooTERS-CD2.iso|682039296|91c10fa8d760742af1fe a3c2a9929e9c|h=2i5yuoylij44tdcd3g5zxfqfnwlfbnjb|/CD3下载⽹址ed2k://|file|%5BCadence.PCB%E8%AE%BE%E8%AE%A1%5D.TLF-SOFT-Cadenc e.Allegro.PCB.Design.v16.2-SHooTERS-CD3.iso|339585024|6e6dd829b325da850cf 58f0b048992de|h=72mpj752sgqz2qqfkkphh7y4ggx4f23x|/⽹速要给⼒哦,耐⼼等待了!⼆.安装1.需要下载能打开ISO⽂件的软件(例如:DAEMON Tools Lite)依次打开三个⽂件,将其复制到同⼀个⽂件夹中2.在⽂件夹中⽤记事本的⽅式打开SHooTERS中的orcad16.lic⽂件,将开始第⼀⾏的this_host改为你所安装电脑的计算机名(点击我的电脑->属性查询计算机名)改完后点击保存。

Cadence 16.2使用之回注

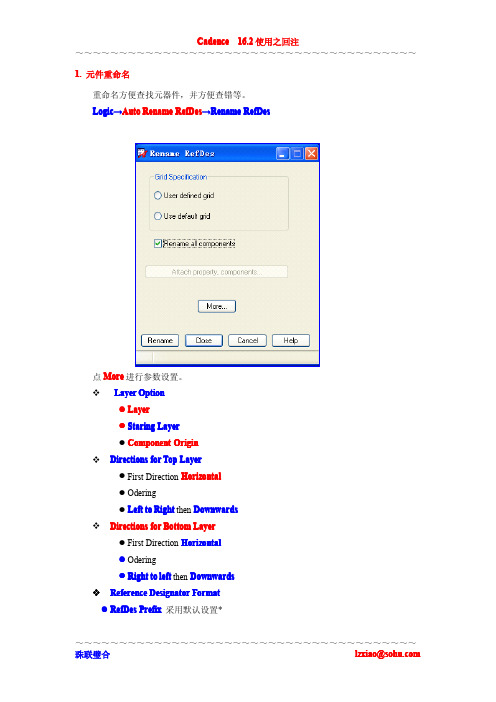

点 More 进行参数设置。 � Layer Option � Layer � Staring Layer � Component Origin � Directions for Top Layer � First Direction Horizontal � Odering � Left to Right then Downwards � Directions for Bottom Layer � First Direction Horizontal � Odering � Right to left then Downwards � Reference Designator Format � RefDes Prefix 采用默认设置*

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 珠联璧合 lzxiao@

Cadence 16.2 使用之回注 ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ � Top Layer Identifier 为空 � Bottom Layer Identifier 为空 � Preserve current Prefixes 前的框勾上 设置完了点 Close 关闭,再点 Rename 进行重命名。 2. 输出新网络表 →Logic, File→Export Export→ 选择 Cadence 下的 Design Entry CIS,选择网络表存放位置。 点 EXPORT Cadence 完成。 3. 回注 →Back annotate,点取 Allegro 打开 Design Entry CIS,选择 Tools Tools→ � � � Netlist 栏选择 netlist 路径 Output 栏选择输出 Rename 的文件路径 Back Annotation 栏勾选 Update Schematic 和 View~~~~~~~~~~~~~~~~~~~~~~~ 珠联璧合 lzxiao@

Cadence_allegro16.2破解说明-总结版

Cadence allegro16.2安装破解2010-6-9 by zkh 1.用记事本打开Crack目录中的license.lic文件,将Server后ID前那段文字改成本机计算机名,并保存。

2.运行Setup,先安装License Manager3.按装一路向下,过程中会提示选择Lic文件,选择第一步修改后保存的Lic文件。

4.接下来弹出的界面中注意:Port Number保留为5280即可,但是后面一般有空格,必须清除5280后面所有的空格。

5.接下来信息为:6.点击Finish安装成功后,启动LmTools工具来设定License Manager7.选择Using Service,而不是License File8.第一步修改好的License文件复制到**Cadence\LicenseManager目录下。

9.在Config Services选项下,设置Path to the license file路径,选择刚刚复制的license.lic文件。

设置完成后点击Save Service,并确认选择“是”。

10.在Start/Stop/Reread选项下,关闭和打开server,最终保持打开状态,状态栏应显示Successful。

11.完成以上步骤,选择Product Installation安装。

12.安装过程中如有提示选择文件,一律点击NEXT掠过,如果一般只使用公司的Lib文件,建议不要安装自带的Lib,安装时间太长。

安装过程中要依次选择CD1.2.3文件。

13.以下这步中,在Lincense Path中输入5280@hostname即可,hostname即第一步修改Lic文件时的计算机名。

14.之后弹出的两个对话框,点击“是”或“否”均可,是关于文件类型的关联。

15.接下来软件开始设置系统环境,时间稍有点长。

16.最后Finish即可17.将光盘1中SHooTERS\ShooTERS.exe 拷贝到安装目录如:C:\Cadence下运行,破解完后重启电脑,为保证正常运行最好停用杀毒软件;基本功能至此破解完毕!。

Allegro16.2新功能教程

Allegro PCB Editor What's New in Release 16.0.Date : 2007/07/16.Author : Jonathan Lee.Revision : 1.0.Version : 16.0.備註:Allegro V16.0 新版本擁有全新的操作介面,使用者在人性化的介面上更能有效率地工作,以下為V16.0新增功能及新介面的介紹。

PCB Editor User Interface變更的部份為:.ToolbarIcon的更新、及工具群組的變更.Fold-Away Windows使工具視窗最大化,平時不使用時,Control Panel會自動收縮.Cadence Branding在SPB系列產品的左上角多了Cadence 商標.Context-sensitive Editing新的pre-selection編輯模式可依被點選物件相關參數設定或可執行之命令,可節省滑鼠遊標在工具列、control panel和物件間移動的時間,此模式可切換下列兩種模式。

A . General Edit Application Mode一般編輯模式,點選物件後會有該物件可執行的相關指令B . Etch Edit Application ModeEtch 相關應用編輯模式,點選物件後,就會自動依物件執行如列表之相關指令.Central Location for Design Parameters常用的設計參數集中在同一個控制界面,新的參數設定界面包含 Display、Design、Text、Etch Edit、Shape and Manufacturing .Color and Visibility EnhancementsAllegro Products Now Support OpenGL Standard支援Open GL顯示,若要最佳效能,基本配備為獨立顯示卡128MB,系統1GB以上的RAMModernization of Color/Visibility User Interface新的顏色層面顯示界面Color Support Extended to 192顏色可支援192色,二個調色盤,每個調色盤為6x16的矩陣,一個調色盤共96色Transparent Graphics Improve Visibility Through the PCB 可設定物件的透明度,使物件透明化,讓重疊的物件更易顯示Quick Access to Commonly Used Subclasses可以將常用的層面設定為我的最愛,自設常用的層面可在同一個畫面作層面控制,而這個新的設定會在local pcbenv內存一個 myfavorites.txt 儲存相關的層面設定。

完整 SPB16.2破解方法与步骤

nolic

nolic

cd %CDSROOT%\tools\pspice

nolic

nolic

如果有,将它们删除。

4,双击crack.bat,多运行几次,至到没有错误出现。

5,进入X:\Cadence\SPB_16.2\tools\capture\下,用解压包中的capture.exe覆盖以前的文件即可,如果想完全破解使软件有仿真功能那么就用下面的方法:用UltraEdit或WinHex打开\capture目录下的capture.exe文件(如果覆盖了就不用管了),还有\pspice目录下的immgr.exe、pspiceaa.exe、pspice.exe、stmed.exe、psp_eng.dll、Magnetic Parts Editor.exe、modeled.exe七个文件,在2进制下查找字串“00 83 C4 0C 8B 45 F8 8B E5 5D C3 55 8B EC 81 EC 84 01 00 00 57 C7 45 F8 00 00 00 00 C7 45 F4 ”,将“55 8B EC” 修改为“33 C0 C3”,保存文件,记住:有一个simsetup.dll的文件一定不能修改,否则仿真的功能就会不全!!!

6,用记事本新建一个空文件,命名为license.dat,放在X:\Cadence\SPB_16.2下.

7,新建系统变量CDS_LIC_FILE,指向X:\Cadence\SPB_16.2\license.dat

8,破解完成!

9,安装hotfix12.每次安装完hotfix后都要再重新破解一下。

10, 最近发现一些网友破解不完全,我特意新修改了批处理文件,将long的批处理做了备份,请大家选择使用即可。——嵌入式公社riverpeak

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2

图 1.3 表贴元件焊盘设置

如果是通孔焊盘,需要填写的参数有: BEGINLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; DEFAULTINTERNAL 层的 Regular Pad,Thermal Relief,Anti Pad; ENDLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.4 所示。 在 BEGINLAYER、DEFAULTINTERNAL、ENDLAYER 三个层面中的 Thermal Relief 可以 选择系统提供的默认连接方式,即 Circle、Square、Oblong、Rectangle、Octagon 五种,在 PCB 中这几种连接方式为简单的‘+’形或者‘X’形。也可以选用自己画的热风焊盘连接 方式,即选择 Flash。这需要事先做好一个 Flash 文件(见第二节)。这些参数的设置见下面的 介绍。

第 2 章 建立封装 .......................................................................................................10

第 3 章 元器件布局 ...................................................................................................23

第 5 章 输出底片文件 ...............................................................................................70

5.1 5.2 5.3 Artwork 参数设置 ......................................................................................................70 生成钻孔文件 .............................................................................................................75 输出底片文件 .............................................................................................................79

图 1.1 Pad Designer 工具界面

在 Units 下拉框中选择单位,常用的有 Mils(毫英寸),Millimeter(毫米)。根据实际情况 选择。 在 Hole type 下拉框中选择钻孔的类型。有如下三种选择: Circle Drill:圆形钻孔; Oval Slot:椭圆形孔; Rectangle Slot:矩形孔。 在 Plating 下拉框中选择孔的金属化类型,常用的有如下两种:

图 1.2 Pad Designer Layers 界面

如果制作的是表贴元件的焊盘将 Singel layer mode 复选框勾上。需要填写的参数有: BEGINLAYER 层的 Regular Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.3用 Pad Designer 制作焊盘

Allegro 中制作焊盘的工作叫 Pad Designer,所有 SMD 焊盘、通孔焊盘以及过孔都用该 工具来制作。 打开程序->Cadence SPB 16.2->PCB Editer utilities->Pad Designer, 弹出焊盘制作的界面, 如图 1.1 所示。

第 4 章 PCB 布线 .......................................................................................................31

PCB 层叠结构 ............................................................................................................31 布线规则设置 .............................................................................................................33 4.2.1 对象(object) ....................................................................................................35 4.2.2 建立差分对 .....................................................................................................36 4.2.3 差分对规则设置 .............................................................................................37 4.2.4 CPU 与 DDR 内存芯片走线约束规则 ..........................................................39 4.2.5 设置物理线宽和过孔 .....................................................................................45 4.2.6 设置间距约束规则 .........................................................................................52 4.2.7 设置相同网络间距规则 .................................................................................55 4.3 布线.............................................................................................................................56 4.3.1 手工拉线 .........................................................................................................56 4.3.2 应用区域规则 .................................................................................................59 4.3.3 扇出布线 .........................................................................................................60 4.3.4 差分布线 .........................................................................................................62 4.3.5 等长绕线 .........................................................................................................64 4.3.6 分割平面 .........................................................................................................65

1

Plated:金属化的; Non-Plated:非金属化的。 一般的通孔元件的管脚焊盘要选择金属化的, 而元件安装孔或者定位孔则选择非金属化 的。 在 Drill diameter 编辑框中输入钻孔的直径。 如果选择的是椭圆或者矩形孔则是 Slot size X,Slot size Y 两个参数,分别对应椭圆的 X,Y 轴半径和矩形的长宽。 一般情况下只要设置上述几个参数就行了,其它参数默认就可以。设置好以后单击 Layers 标签,进入如图 1.2 所示界面。

目 录

第 1 章 焊盘制作 .........................................................................................................1

1.1 1.2 2.1 2.2 2.3 3.1 3.2 3.3 4.1 4.2 用 Pad Designer 制作焊盘 ...........................................................................................1 制作圆形热风焊盘 .......................................................................................................6 新建封装文件 .............................................................................................................10 设置库路径 .................................................................................................................11 画元件封装 .................................................................................................................12 建立电路板(PCB) ......................................................................................................23 导入网络表 .................................................................................................................24 摆放元器件 .................................................................................................................26