第2章 AMBA协议规范

AMBA总线协议2.0总结

3.2

AHB总线互连结构................................................................................................................................. 17

3.3

AHB操作概述.......................................................................................................................................... 18

3.1

什么是AHB总线?................................................................................................................................. 14

3.1.1 一个典型的基于AHB总线的微控制器架构.............................................................................. 15

3.4.3 多重传送(multiple transfer) ........................................................................................................... 20

3.5

控制信号:传送状态HTRANS[1:0] .................................................................................................... 22

基于AMBA总线协议的APB Bridge设计

pan of APB.It is between AHB and APB

critical pan to connect AHB and other

on

peripherals.

as

This dissenation is based

the GS32S CPU of Godson.1

the AHB master.A

公司提出的一个SoC体系机构的丌放标准,用以集成RISC处理器和外设IP核。 它独立于处理器和工艺技术,具有高速、低功耗等特点。同样,它也通过定义这 样一个针对SoC模块的通用总线,加强了设计的重用性,即采用IP核复用技术 简化芯片的设计。

AHB.to.APB桥模块是AHB高速总线上的从模块,也是√蝴BA系统中,CPU

成都理工入学硕士学位论文

1.2各种SoC片上总线的历史和现状

二十世纪末,在微电子及其应用领域发生了一场前所未有的变革,这场变革

是由片上系统(SoC)技术应用和发展引起的。从技术层面看,SoC技术是超大 规模集成电路发展的必然趋势和主流,它以超深亚微米VDSM(Very

Deep

Submjcron)工艺和知识产权IP核复用技术为支撑。 SoC是二十世纪九十年代出现的概念。随着时间的不断推移和SoC技术的

设核处理器,就可以提高从公共设计平台创建产品的定制化能力。因此,实现 OCB的标准化是十分必要的。 近年来,许多公司相继制定了一些OCB标准,其中影响较大的有

CoreConnect总线、AMBA(AdvaIlced Microcontroller

Bus

Architecture)总线、

OCP(0pen Cofe Protoc01)总线和Wishbone总线。其中,AMBA总线是ARM

第2章_AMBA协议规范.

Xilinx All Programmable Zynq-7000 SoC 设计指南

主 讲:何宾 Email:hebin@

AMBA协议规范

AMBA协议是ARM公司制定的用于SOC内IP互联的规范 主要内容

AMBA规范概述、AMBA APB规范、AMBA AHB规范和 AMBA AXI4规范。本章除了详细介A协议规范 ---AMBA V4.0

AMBA规范(版本4)定义了的总线/接口

高级可扩展接口4流(Advanced eXtensible Interface 4

Stream ,AXI4-Stream v1.0)。

高级跟踪总线(Advanced Trace Bus ,ATB v1.1)。

高级外设总线(Advanced Peripheral Bus ,APB v2.0)。

10

AMBA协议规范 ---AMBA V4.0

最新一代的AMBA4接口的目标

适合于高带宽和低延迟设计。 在不使用复杂的桥接方式下,允许更高频率的操作。 满足普遍情况下的元件接口要求。 适用于高初始访问延迟的存储器控制器。 为互联结构的实现提供了灵活性。 与已有的AHB和APB接口向下兼容。

12

AMBA APB协议规范

--AMBA APB写传输

APB写传输包括两种类型:

无等待状态写传输 有等待状态写传输

13

AMBA APB写传输

--无等待写传输

一个基本的无等待状态的写传输

地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

14

AMBA APB写传输

--无等待写传输

T1:写传输开始于地址PADDR,写数据PWDATA,写信号

AMBA

高级微控制器总线架构简介ARM研发的AMBA(Advanced Microcontroller Bus Architecture)提供一种特殊的机制,可将RISC处理器集成在其它IP芯核和外设中,2.0版AMBA标准定义了三组总线:AHB(AMBA高性能总线)、ASB(AMBA系统总线)、和APB(AMBA外设总线)。

AHB(the Advanced High-performance Bus)应用于高性能、高时钟频率的系统模块,它构成了高性能的系统骨干总线(back-bone bus )。

它主要支持的特性是:* 数据突发传输(burst transfer )* 数据分割传输(split transaction )* 流水线方式* 一个周期内完成总线主设备(master )对总线控制权的交接* 单时钟沿操作* 内部无三态实现* 更宽的数据总线宽度(最低32位,最高可达1024位,但推荐不要超过256位)ASB(the Advanced System Bus)是第一代AMBA系统总线,同AHB相比,它数据宽度要小一些,它支持的典型数据宽度为8位、16位、32位。

它的主要特征如下:* 流水线方式* 数据突发传送* 多总线主设备* 内部有三态实现APB(the Advanced Peripheral Bus)是本地二级总线(local secondary bus ),通过桥和AHB/ASB相连。

它主要是为了满足不需要高性能流水线接口或不需要高带宽接口的设备的互连。

APB的总线信号经改进后全和时钟上升沿相关,这种改进的主要优点如下:* 更易达到高频率的操作* 性能和时钟的占空比无关* STA 单时钟沿简化了* 无需对自动插入测试链作特别考虑* 更易与基于周期的仿真器集成APB 只有一个APB桥,它将来自AHB/ASB的信号转换为合适的形式以满足挂在APB 上的设备的要求。

桥要负责锁存地址、数据以及控制信号,同时要进行二次译码以选择相应的APB设备AMBA开放规范AMBA规范AMBA 协议是用于连接和管理片上系统(SoC) 中功能模块的开放标准和片上互连规范。

AMBA_3_APB协议规范

AMBA_3_APB协议规范AMBA(高级微处理器总线)是一种用于系统级互连的开放标准协议,它由ARM公司开发,被广泛应用于嵌入式系统中。

AMBA_3_APB(高级微处理器总线第3代-高性能总线)是AMBA协议的一部分,它定义了一种高性能、低功耗的片内总线协议,用于连接处理器和外设。

1.信号:AMBA_3_APB协议规范定义了一系列信号,包括时钟信号、复位信号、总线控制信号、数据传输信号等。

时钟信号主要包括时钟线以及时钟使能信号,用于控制数据传输的时序。

复位信号用于重置外设以及总线控制器的状态。

总线控制信号用于控制总线的访问权限以及传输模式等。

数据传输信号用于在总线上传输数据。

2.传输:AMBA_3_APB协议规范定义了四种传输类型,分别是单个传输、设置传输、清除传输以及数据传输。

单个传输用于传输单个数据项,例如读取外设的寄存器值。

设置传输用于设置外设的寄存器值,例如写入配置信息。

清除传输用于清除外设的寄存器值,例如重置外设。

数据传输用于传输大量数据,例如读取或写入外设的缓冲区。

3.协议:AMBA_3_APB协议规范定义了一套协议,包括方法、地址空间、读写传输、保持传输、错误传输以及确认传输。

方法用于指示执行的操作类型,包括读、写等。

地址空间用于指定外设的寄存器地址。

读写传输用于实现读取或写入寄存器的操作。

保持传输用于在外设的寄存器繁忙时保持总线传输。

错误传输用于指示总线传输过程中的错误信息。

确认传输用于确认总线传输的完成。

4.时序:AMBA_3_APB协议规范定义了一套时序要求,包括时钟周期、数据有效性以及总线传输的顺序。

时钟周期用于控制数据传输的时序,包括时钟上升沿和下降沿的作用周期。

数据有效性用于指示数据在总线上的有效时间段,以及数据的采样时间。

总线传输的顺序用于指示多个传输之间的先后顺序,以及传输的优先级。

总结起来,AMBA_3_APB协议规范是一种用于连接处理器和外设的高性能、低功耗的片内总线协议。

AMBA_3_APB协议规范

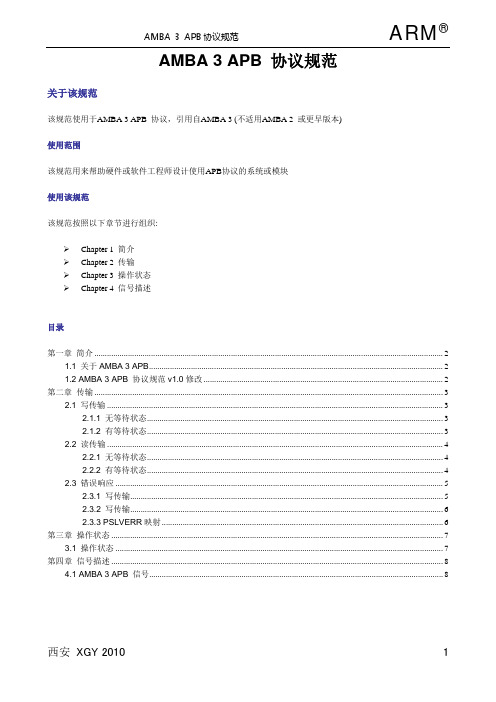

AMBA 3 APB 协议规范关于该规范该规范使用于AMBA 3 APB 协议,引用自AMBA 3 (不适用AMBA 2 或更早版本)使用范围该规范用来帮助硬件或软件工程师设计使用APB协议的系统或模块使用该规范该规范按照以下章节进行组织:Chapter 1 简介Chapter 2 传输Chapter 3 操作状态Chapter 4 信号描述目录第一章简介 (2)1.1 关于AMBA 3 APB (2)1.2 AMBA 3 APB 协议规范v1.0修改 (2)第二章传输 (3)2.1 写传输 (3)2.1.1 无等待状态 (3)2.1.2 有等待状态 (3)2.2 读传输 (4)2.2.1 无等待状态 (4)2.2.2 有等待状态 (4)2.3 错误响应 (5)2.3.1 写传输 (5)2.3.2 写传输 (6)2.3.3 PSLVERR映射 (6)第三章操作状态 (7)3.1 操作状态 (7)第四章信号描述 (8)4.1 AMBA 3 APB 信号 (8)1.1 关于AMBA 3 APBAPB属于AMBA 3 协议系列,它提供了一个低功耗的接口,并降低了接口的复杂性。

APB接口用在低带宽和不需要高性能总线的外围设备上。

APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB 外围设备的设计流程,每个传输至少耗用两个周期。

APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口(AXI)连接。

1.2 AMBA 3 APB 协议规范v1.0修改该版本包括:• 一个准备好信号PREADY, 来扩展APB传输• 一个错误信号PSLVERR, 来指示传输失败2.1 写传输写传输包括两种类型:• 无等待状态• 有等待状态2.1.1 无等待状态图2-1 显示了一个基本的无等待状态的写传输。

图2-1 无等待的写传输地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

AMBAAPB协议规范

AMBA 3 APB 协议规范关于该规范该规范使用于AMBA 3 APB 协议,引用自AMBA 3 (不适用AMBA 2 或更早版本)使用范围该规范用来帮助硬件或软件工程师设计使用APB协议的系统或模块使用该规范该规范按照以下章节进行组织:Chapter 1 简介Chapter 2 传输Chapter 3 操作状态Chapter 4 信号描述目录第一章简介 (2)1.1 关于AMBA 3 APB (2)1.2 AMBA 3 APB 协议规范v1.0修改 (2)第二章传输 (3)2.1 写传输 (3)2.1.1 无等待状态 (3)2.1.2 有等待状态 (3)2.2 读传输 (4)2.2.1 无等待状态 (4)2.2.2 有等待状态 (4)2.3 错误响应 (5)2.3.1 写传输 (5)2.3.2 写传输 (6)2.3.3 PSLVERR映射 (6)第三章操作状态 (7)3.1 操作状态 (7)第四章信号描述 (8)4.1 AMBA 3 APB 信号 (8)1.1 关于AMBA 3 APBAPB属于AMBA 3 协议系列,它提供了一个低功耗的接口,并降低了接口的复杂性。

APB接口用在低带宽和不需要高性能总线的外围设备上。

APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB 外围设备的设计流程,每个传输至少耗用两个周期。

APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口(AXI)连接。

1.2 AMBA 3 APB 协议规范v1.0修改该版本包括:• 一个准备好信号PREADY, 来扩展APB传输• 一个错误信号PSLVERR, 来指示传输失败2.1 写传输写传输包括两种类型:• 无等待状态• 有等待状态2.1.1 无等待状态图2-1 显示了一个基本的无等待状态的写传输。

图2-1 无等待的写传输地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

学习汇报AMBA总线协议书范本

降低硅的下部构造要求以支持用在操作和生产测试时有 效的片上和片外通信

AMBA是为了推出 on-chip bus 的规范,一开始 AMBA1.0只有ASB和APB,为了节省面积, bus协 议都是 tristate 的bus;到 2.0的AHB,为了方便设 计者(tristate bus 需要花更多精力注意 timing), 改用Mux结构,并增加了新特性。

Implement some level of protection

Master

Write data bus

Name HSELx

HRDATA[31:0]

HREADY HRESP[1:0] HBUSREQx HLOCKx HGRANTx

HMASTER[3:0]

HMASTLOCK

HSPLITx[15:0]

1.3 基于AMBA的典型微控制器

基于AMBA的微控制器,包含一个高性能系统中 枢总线(AHB或ASB)和外设总线 APB。

System bus 负责连接ARM之类的embedded processor,DMA controller ,on-chip memory 和其 他interface,或其他需要 high bandwidth 的元件。

阶段学习汇报 ——AMBA总线协议

XBA AHB

3. AMBA APB

1. AMBA 总线简介

1.1 AMBA总线概述

?高级微控制器总线体系(Advanced Microcontroller Bus Architecture)规范定义了在设计高性能嵌入式微控制器 时的一种片上通信标准

Peripheral bus 则用来连接系统的周边元件,该协 议相对AHB要简单很多。与 AHB之间通过桥接器 (Bridge )相连。

amba协议手册

AMBA协议手册一、AMBA概况AMBA(Advanced Microcontroller Bus Architecture)协议,又被称为AMBA 2.0,是一种针对高性能、高吞吐量嵌入式系统设计的总线协议。

它定义了在一个或多个嵌入式处理器和多个外设之间的高效通信方式,广泛应用于各类芯片和集成电路中。

AMBA为微控制器、数字信号处理器(DSP)以及通信和消费电子等多种应用提供了优秀的性能表现。

二、AMBA版本历史AMBA的发展经历了几个重要的版本,每个版本都增加了新的特性和功能。

1.AMBA 1.0:这个版本主要定义了简单的主从设备间的通信方式,包括数据传输和地址协议。

2.AMBA 2.0:在AMBA 2.0中,引入了更复杂的特性,如猝发传输和更高级的地址和数据传输控制。

3.AMBA 3.0:这个版本引入了新的特性,如外部总线的对齐和分区、扩展的地址空间和数据字节宽度的动态调整。

4.AMBA 4.0:随着芯片设计的不断发展和系统性能的持续提高,AMBA 4.0为高带宽总线传输和高频率时钟提供了支持。

三、AMBA组成部分AMBA协议主要包括以下组成部分:1.AXI(Advanced eXtensible Interface):AXI是一种高性能、高吞吐量的总线接口,用于连接主设备和从设备。

它支持多个通道的数据传输,每个通道都有数据写和数据读两个通道。

2.ACE(Advanced Coherency Enhanced):ACE是AMBA的一种扩展,提供了更高级的内存一致性保证,确保在多处理器系统中数据的一致性。

3.APB(Advanced Peripheral Bus):APB是一种简单、低速的总线接口,主要用于连接低速外设。

它基于传统的Peripheral Bus,但提供了更高的性能和更小的芯片面积。

4.AHB(Advanced High-performance Bus):AHB是一种高性能的总线接口,主要用于连接高性能的处理器和高速存储器。

AMBA协议总结

基于 AMBA 的微控制器典型地由一个高性能系统中枢总线(AHB 或者 ASB)组成,能够支持外部存储器带宽,包括 CPU\片上存储器和其他直接数据存取(DMA) 设备。

这条总线为上述单元之间大多数的传输提供高带宽接口。

在这条高性能总线上也有一个桥接器以连接低带宽的 APB,而在 APB 上连接着大多数的系统外设。

1.1 AHB 总线架构Haddr[31:0] Hsel1Hsel2Hrdata[31:0] Haddr1[31:0]Hwdata1[31:0]Master1Hbursteq1Hcontrol1Hgrant1Hmaster[3:0] MUXM2S ArbiterHsel1Haddr[31:0]Slave1Hwdata[31:0] Haddr[31:0]Hwdata[31:0]Hsel2Haddr[31:0]APBBridgeHbursteq2 Hgrant2 Haddr2[31:0] Hwdata2[31:0]Master2Hrdata[31:0] Hcontrol2Hmast[2:0Hready1Hresp1[1:0]Hrdata1[31:0]MUHready2Hresp2[1:0]Hrdata2[31:0] Hwdata[31:0]AHBdecoderAHB 系统设计包括以下的成份:AHB 主机总线主机能够通过提供地址和控制信息发起读写操作。

任何时候只允许一个总线主机处于有效状态并能使用总线。

AHB 从机总线从机在给定的地址空间范围内响应读写操作。

总线从机将成功、失败或者等待数据传输的信号返回给有效的主机。

AHB 仲裁器总线仲裁器确保每次惟独一个总线主机被允许发起数据传输。

即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能根据应用要求而得到执行。

地址、写数据总线多路选择器地址、写数据总线多路选择器根据 Hmaster 总线仲裁结果进行主机地址、写数据的选通输出。

第2章 AMBA协议规范

和PREADY都是高时,PSLVERR才认为是有效的。

24

AMBA APB协议规范

--AMBA APB错误响应

接收到一个错误的交易,可能改变外设的状态(这是由

外设指定的)。

当一个写交易接收到一个错误时,并不意味着外设内的寄存器

没有更新。 读交易接收到一个错误时,能返回无效的数据。

对于一个读错误,并不要求外设将数据总线驱动为0。

12

AMBA APB协议规范

--AMBA APB写传输

APB写传输包括两种类型:

无等待状态写传输 有等待状态写传输

13

AMBA APB写传输

--无等待写传输

一个基本的无等待状态的写传输

地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

14

AMBA APB写传输

--无等待写传输

T1:写传输开始于地址PADDR,写数据PWDATA,写信号

11

--AMBA APB规范

APB属于AMBA 3协议系列,它提供了一个低功耗的接口,

并降低了接口的复杂性。 APB接口用在低带宽和不需要高性能总线的外围设备上。 APB是非流水线结构,所有的信号仅与时钟上升沿相关,这 样就可以简化APB 外围设备的设计流程,每个传输至少消耗 两个周期。 APB可以与AMBA高级高性能总线和AMBA 高级可扩展接口 连接。

LOGO Xilinx大学计划课程

Xilinx All Programmable Zynq-7000 SoC 设计指南

主 讲:何宾 Email:hebin@

AMBA协议规范

AMBA协议是ARM公司制定的用于SOC内IP互联的规范 主要内容

AMBA规范概述、AMBA APB规范、AMBA AHB规范和 AMBA AXI4规范。本章除了详细介绍APB和AHB规范外,还详细

AMBA4_AXI4-Stream协议中文完整翻译

n

以 byte 为单位表示的数据总线的宽度

I

TID 宽度,推荐最大为 8-bits

d

TDEST 宽度,推荐最大为 4-bits

u

TUSER 宽度,推荐的 bit 数为以 byte 为单位表示的接口宽度的整数倍

信号 ACLK ARESETn TVALID

源 时钟源 复位源 主机

TREADY

从机

TDATA[(8n-1):0] 主机

小写 n

在信号名的开头或结尾,表示该信号为低有效

反馈

ARM 欢迎对于本产品及文档的反馈。

反馈关于本产品

如果你有任何关于本产品的看法和建议,请联系你的供应商并给出: 产品名 产品修订版本或版本 提供尽可能多的解释说明信息,如果合适的话,包括问题以及调试过程。

反馈关于内容

如果你有关于内容的意见,请发送邮件给 errata@,并给出: 标题:AMBA 4 AXI4-Stream Protocol Specification 数字:ARM IHI 0051A 你对内容有意见的页码 关于你的意见的一个简洁的解释说明

1 介绍

本章描述了 AXI4-流协议,并给出一些流类型的例子。本章包含以下章节: 关于 AXI4-流协议 数据流

1.1 关于 AXI4-流协议

AXI4-流协议作为一个标准接口,用于连接进行数据交换的组件。接口可以用来连接一个单一的主机,主机向接 收数据的单一从机发送数据。协议也可用于连接若干个主机和从机的组件。协议支持共用一组信号线的多个数据流, 允许构建一个通用互联(generic interconnect),可以执行 upsizing、downsizing 以及路由操作。

使用本文档

本文档包含以下章节: 1 介绍

关于AMBA的笔记2(哥,断奶了)

7.2、Burst 传输AHB 协议规定了 4、8、16beat 传输,以及未定义长度和 single 传输。

其中 beat 数乘以transfer 即为 burst 的长度。

AHB 协议支持 incrementing 和 wrap burst,incrementing 为递增的,没有边界;wrap 将地址划分为传输 burst 长度的边界,超过边界部分折返回边界开始处。

如传输一笔 wrap4 的 burst,字长为 4byte,第一笔传输的地址为 0x34,会在 16byte 绕回,因此 4 笔传输的地址为 0x34,0x38,0x3c,0x30。

表三为 Burst 信号编码说明。

000:SINGLE,单次传输。

001:INCR,未指定的长度递增突发。

010:WRAP4,4次4byte突发传输。

011:INCR4,4次递增突发传输。

100:WRAP8,8次4byte突发传输。

101:INCR8,8次递增突发传输。

110:WRAP16,16次4byte突发传输。

111:INCR16,16次递增突发传输。

Burst 不能超过 1K 地址边界,注意未指定长度的 incrementing burst 不能超过这一地址边界。

图七显示了一笔类型为 WRAP4 的 burst 传输,第一笔传输加入一个等待状态。

7.3传输方向当 HWRITE 信号为高时,进行写数据传输,master 向数据总线写数据;当 HWRITE 信号为低时,进行读数据操作,slave 产生读数据驱动读数据总线。

7.4传输大小HSIZE信号指定了传输大小,从8bits到1024bits,它与HBURST共同决定wrapping burst的地址边界。

表四给出具体编码信息。

7.5.保护控制保护控制信号 HPROT[3:0]为总线接入提供附加信息,用来为需要的模块提供一定级别的保护。

保护控制信号指定传输是读取操作码或数据,特权模式或用户模式。

AMBA_AXI3_v1.0协议中文完整翻译

AXI 协议也支持以下附加的特征: 突发类型 AXI 协议支持三种突发类型,适用于:

正常 memory 访问

回环高速缓存线(wrapping cache line)突发 访问外设 FIFO 位置的流数据 参见第 4 章地址选项。

系统高速缓存支持(System cache support) AXI 协议的高速缓存支持信号允许一个主机向系统级高速缓存提供一个事物的可缓存、可高速缓存,以及可分配 的属性。 参见高速缓存支持。

信号

源

AWID[3:0]

主机

AWADDR[31:0] 主机

AWLEN[3:0] 主机

AWSIZE[2:0] 主机

AWBURST[1:0] 主机

AWLOCK[1:0] 主机 AWCACHE[3:0] 主机

AWPROT[2:0] 主机

AWVALID

主机

AWREADY

从机

描述

写地址 ID。该信号为写地址组信号的 ID tag。 写地址。在一个写突发事物中,写地址总线给出了第一个传输的地址。相应 的控制信号用来决定突发中剩余传输的地址。

突发长度。突发长度给出了一个突发中准确的传输个数。该信息决定了与地 址相对应的数据传送次数。参见表 4-1。 突发大小。该信号表示突发中每个传输的大小。字节选通表示更新哪个字节 通道。参见表 4-2。 突发类型。突发类型和突发大小决定了突发中每个传输的地址是怎么计算 的。参见表 4-3。 锁定类型。该信号为传输的原子特性提供了附加的信息。参见表 6-1。 cache 类型。该信号表示事物的可缓存、可高速缓存、write-through、writeback、以及分配属性。参见表 5-1。 保护类型。该信号表示事物的正常、特权或安全保护级别,以及事物是一个 数据访问还是指令访问。参见保护单元支持。

AMBA总线中文规范

Introduction to AMBA Bus System工研院 / 系統晶片技術㆗心工程師吳欣龍1. 前言本篇文章主要是介紹ARM Limited.公司所推出的AMBA 協定(Advanced Micro-controller Bus Architecture)。

AMBA協定目前是open 且free的,讀者可從ARM的網站()㆘載完整的Specification。

這篇文章並沒有打算說明完整的AMBA協定內容,詳細的Spec.還是請讀者閱讀ARM所提供的文件。

原本的AMBA協定包含了㆕大部分: AHB, ASB, APB, Test Methodology,限於篇幅的關係,我們挑選較重要的AHB, APB加以基本的介紹,並探討AHB的㆒些重要的特性。

2. AMBA 概述AMBA協定的目㆞是為了要推出on-chip bus的規範,㆒開始AMBA 1.0只有ASB與APB,為了節省面積,所以這時候的bus協定都是tristate的bus,而到後來2.0的AHB為了能更方便設計者(trisate bus要花更多精力去注意timing),因此改用bus改用multiplexor的架構,並增加了新的特性。

㆒個以AMBA架構的SOC,㆒般來說包含了 high-performance的system bus - AHB與low-power的peripheral bus - APB。

System bus是負責連接例如ARM之類的embedded processor與DMA controller,on-chip memory 和其他 interface,或其他需要high bandwidth 的元件。

而peripheral bus則是用來連接系統的周邊元件,其protocol相對AHB來講較為簡單,與AHB之間則透過Bridge相連,期望能減少system bus的loading。

㆒個典型的AMBA架構如圖2.1:圖2.13. AHB簡介ARM當初訂定AHB (Advanced High-Performance Bus)主要是想讓它能夠用來當作SOC的z single-clock edge operationz non-tristate implementationz burst transfersz split transactionz multiple bus master以㆘我們將簡單的介紹AHB 的協定及這些特性。

AMBA AHB APB总线协议总结

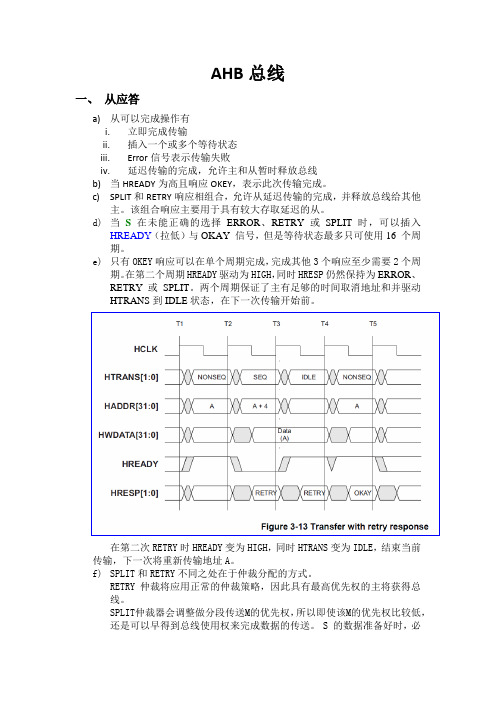

AHB总线一、从应答a)从可以完成操作有i.立即完成传输ii.插入一个或多个等待状态iii.Error信号表示传输失败iv.延迟传输的完成,允许主和从暂时释放总线b)当HREADY为高且响应OKEY,表示此次传输完成。

c)SPLIT和RETRY响应相组合,允许从延迟传输的完成,并释放总线给其他主。

该组合响应主要用于具有较大存取延迟的从。

d)当S 在未能正确的选择ERROR、RETRY 或SPLIT 时,可以插入HREADY(拉低)与OKAY 信号,但是等待状态最多只可使用16 个周期。

e)只有OKEY响应可以在单个周期完成,完成其他3个响应至少需要2个周期。

在第二个周期HREADY驱动为HIGH,同时HRESP仍然保持为ERROR、RETRY 或SPLIT。

两个周期保证了主有足够的时间取消地址和并驱动HTRANS到IDLE状态,在下一次传输开始前。

在第二次RETRY时HREADY变为HIGH,同时HTRANS变为IDLE,结束当前传输,下一次将重新传输地址A。

f)SPLIT和RETRY不同之处在于仲裁分配的方式。

RETRY仲裁将应用正常的仲裁策略,因此具有最高优先权的主将获得总线。

SPLIT仲裁器会调整做分段传送M的优先权,所以即使该M的优先权比较低,还是可以早得到总线使用权来完成数据的传送。

S 的数据准备好时,必须告知仲裁器,让相关M完成其要求。

二、仲裁机制a)主需要持续发出HBUSREQ直到获得GRANGT,对于不定长burst需要持续发出HBUSREQ。

在HGRANT有效后的下一个时钟上升沿可以地址和控制信号放到总线上。

对于需要等待的情况,可以在HGRANT有效后将HREADY拉低,表示需要等待。

b)当在两个主间进行总线移交时,需要在前一个主的倒数第二个地址被采样后(T5沿仲裁器采样到倒数第二个地址),同时切换HGRANT(T6沿主接受到grant信号),移交总线。

The arbiter changes the HGRANTx signals when the penultimate (one before last) address has been sampled. The new HGRANTx information will then be sampled at the same point as the last address of the burst is sampled.三、SPLIT传输当M和主采样到到SPLIT或RETRY响应后(T3沿),M必须立刻完成一个IDLE传输,同时仲裁器将该M的grant信号置为无效。

第2章 嵌入式处理器(第三版)参考答案

第2章嵌入式处理器习题2-1 什么是CISC和RISC,各自有什么特点?答:CISC复杂指令集体系结构,RISC精减指令集体系结构。

CISCRISC一条指令仅执行简单操作,把微处理器能执行的指令数目减少到最低限度,以提高处理速度。

RISC处理器比同等的CISC(复杂指令集计算机)处理器要快50%~75%,CISC一条指令可以执行许多操作。

2-2 冯.诺依曼结构与哈佛结构各自的特点是什么?答:冯·诺依曼结构的处理器使用同一个存储器,即程序和数据共用同一个存储器;而哈佛结构则是程序和数据采用独立的总线来访问程序存储器和数据存储器。

2-3 目前有哪些主要嵌入式内核生产厂商及典型嵌入式内核?ARM处理器核有哪三大特点?答:主要内核厂商有:美国的MIPS公司MIPS处理器内核、美国的IBM与Apple和Motorola 联合开发的PowerPC、Motorola公司独立开发的68K/COLDFIRE、英国的ARM公司ARM处理器内核等等。

ARM内核的三大主要特点如下:(1)功耗低(2)性价比高(3)代码密度高2-4 简述ARM体系结构的技术特征。

答:(1)单周期操作:ARM指令系统中的指令只需要执行简单而和基本的操作,因此其执行过程在一个机器周期内完成。

(2)采用加载/存储指令结构:由于存储器访问指令的执行时间长(通过总线对外部访问),因此只采用了加载和存储两种指令对存储器进行读和写的操作,面向运算部件的操作都经过加载指令和存储指令,从存储器取出后预先存放到寄存器对内,以加快执行速度。

(3)固定的32位长度指令:指令格式固定为32位长度,这样使指令译码结构简单,效率提高。

(4)地址指令格式:编译开销大,尽可能优化,采用三地址指令格式、较多寄存器和对称的指令格式便于生成优化代码。

(5)指令流水线技术:ARM采用多级流水线技术,以提高指令执行的效率。

2-5 简述Thumb、Thumb-2及Thumb-2EE的主要特点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

--AMBA APB规范

APB属于AMBA 3协议系列,它提供了一个低功耗的接口,

并降低了接口的复杂性。 APB接口用在低带宽和不需要高性能总线的外围设备上。 APB是非流水线结构,所有的信号仅与时钟上升沿相关,这 样就可以简化APB 外围设备的设计流程,每个传输至少消耗 两个周期。 APB可以与AMBA高级高性能总线和AMBA 高级可扩展接口 连接。

PRDATA PSLVERR

从接口

从接口 从接口

准备好。从设备使用该信号来扩展APB传输。

读取的数据。当PWRITE位低,在读周期,所选择的从设 备驱动这个总线。这个总线最多个32位宽度。 这个信号表示传输失败。APB外设不要求PSLVERR引脚。 对已经存在和新APB外设设计。当外设不包含这个引脚时, 33 到APB桥的合适的数据拉低。

功能介绍

AMBA协议是一个开放标准的,片上互联规范,用于SoC内功 能模块的连接和管理。它便于第一时间开发带有大量控制器和外

4

设的多处理器设计。

AMBA协议规范

--AMBA V1.0

高级系统总线(Advanced System Bus,ASB) 高级外设总线(Advanced Peripheral Bus,APB)

LOGO Xilinx大学计划课程

Xilinx All Programmable Zynq-7000 SoC 设计指南

主 讲:何宾 Email:hebin@

AMBA协议规范

AMBA协议是ARM公司制定的用于SOC内IP互联的规范 主要内容

AMBA规范概述、AMBA APB规范、AMBA AHB规范和 AMBA AXI4规范。本章除了详细介绍APB和AHB规范外,还详细

AMBA APB写传输

--无等待写传输

地址PADDR,写数据PWDATA和控制信号保持有限,直到 在T3完成传输,结束访问周期。

在传输结束后,使能信号PENABLE变成无效。选择信号

PSEL也变成无效,除非相同的外设立即开始下一个传输。

16

AMBA APB写传输

--有等待写传输

17

AMBA APB写传输

PREADY来扩展传输。

当PENABLE为低的时候,PREADY可以为任何值。

确保外围器件有固定的两个周期来使PREADY为高。

注意:推荐地址和写信号在传输结束后不要立即更改,保持当

前状态直到下一个传输,这样可以降低功耗。

19

AMBA APB协议规范

---AMBA APB读传输

读传输包括以下两种类型

PWRITE和选择信号PSEL,在PSCLK的上升沿寄存。这称为 写传输的建立周期。 T2:使能信号PENABLE和准备信号PREADY,在PSCLK的 上升沿寄存。

当确认时,PENABLE表示传输访问周期的开始。 当确认时,PREADY表示在PCLK的下一个上升沿从设备可以完成 传输。

15

AMBA规范(版本4)定义了的总线/接口

AXI一致性扩展(AXI Coherency Extensions,ACE)。 AXI一致性扩展简化(AXI Coherency Extensions Lite ,ACELite)。 高级可扩展接口4(Advanced eXtensible Interface 4 ,AXI4)。 高级可扩展接口4简化(Advanced eXtensible Interface 4 Lite , AXI4-Lite)。

PWDATA

PSTRB

APB 桥

APB桥

写数据。当PWRITE为高时,在写周期内,外设总线桥单 元驱动写数据总线。

写选通,这个信号表示在写传输时,更新哪个字节通道。 每8个比特位有一个写选通信号。因此,PSTRB[n]对应于 PWDATA[(8n+7):(8n)]。在读传输时,写选通不是活动的。

PREADY

CoreSight片上调试和跟踪解决方案)

7

AMBA协议规范 ---AMBA V4.0

AXI4协议

2009年,Xilinx 同 ARM 密切合作,共同为基于 FPGA 的高

性能系统和设计定义了 AXI4 规范。并且在其新一代可编程门阵

列芯片上采用了高级可扩展接口。

8

AMBA协议规范 ---AMBA V4.0

如果PREADY 为低,保持ACCESS状态。

总线返回IDLE状态,否则进入SETUP状态

31

如果PREADY 为高,则退出ACCESS状态,如果此时没有其它传输请求,

---AMBA3 APB信号及描述

信号 PCLK PRESETn PADDR PPROT 来源 时钟源 系统总线 APB桥 APB桥 描述 时钟 复位。APB复位信号低有效。该信号一般直接与系 统总线复位信号相连。 地址总线。最大可达32位,由外设总线桥单元驱动。 保护类型。这个信号表示交易普通的、剥夺的或者 安全保护级别,以及这个交易是数据访问或者指令 访问。 选择信号。APB桥单元产生到每个外设从设备的信 号。该信号表示从设备被选中,要求一个数据传输。 每个从设备都有一个PSELx信号。

嵌入式微控制器。它被ARM公司和众多的厂商所支持。

3

AMBA协议规范

--AMBA规范导论

应用领域

AMBA用于片上系统(System-on- a-chip, SoC)的片上总线。

自从AMBA出现后,其应用领域早已超出了微控制器设备,现在 被广泛的应用于各种范围的ASIC和SOC器件,包括用于便携设备 的应用处理器。

---AMBA AHB规范 AHB是新一代的AMBA总线,目的用于解决高性 能可同步的设计要求。AHB是一个新级别的总线,高 于APB,用于实现高性能、高时钟频率系统的特征要 求.

AMBA协议规范

34

---AMBA AHB规范

这些要求包括:

猝发传输.

AMBA协议规范

分裂交易.

单周期总线主设备交接.

高级外设总线(Advanced Peripheral Bus,APB)

6

AMBA协议规范 ---AMBA v3.0

在2003年,ARM推出了第三个版本,AMBA3

高级可扩展接口(Advanced eXtensible Interface,AXI3或AXI

v1.0)(用于更高性能的互连)

高级高性能总线简化(Advanced High-performance Bus Lite,AHB-Lite v1.0)。 高级外设总线(Advanced Peripheral Bus,APB v1.0)。 高级跟踪总线(Advanced Trace Bus,ATB v1.0)(用于

SETUP

当传输被请求时,总线进入SETUP状态,选择信号PSELx,被

置位。总线仅在SETUP 状态停留一个时钟周期,并在下一个时

钟周期进入ACCESS状态

30

AMBA APB协议规范

---操作状态

ACCESS

使能信号PENABLE, 在ACCESS状态中置位。在传输从 SETUP状态到ACCESS状态转变的过程中address, write, select和 write data信号必须保持不变。从ACCESS状态退出,由从器件的 PREADY信号控制:

无等待状态读传输 有等待状态读传输

20

AMBA APB读传输

--无等待读传输

在读传输结束以前,从设备必须提供数据。

21

AMBA APB读传输

--有等待读传输

在有等待读传输中,使用PREADY信号来添加两个周期。也可 以添加多个周期。在传输过程中也可以添加多个周期。如果在访 问周期内拉低PREADY信号,则扩展读传输。

高级外设总线(Advanced Peripheral Bus ,APB v2.0)。

10

AMBA协议规范 ---AMBA V4.0

最新一代的AMBA4接口的目标

适合于高带宽和低延迟设计。 在不使用复杂的桥接方式下,允许更高频率的操作。 满足普遍情况下的元件接口要求。 适用于高初始访问延迟的存储器控制器。 为互联结构的实现提供了灵活性。 与已有的AHB和APB接口向下兼容。

和PREADY都是高时,PSLVERR才认为是有效的。

24

AMBA APB协议规范

--AMBA APB错误响应

接收到一个错误的交易,可能改变外设的状态(这是由

外设指定的)。

当一个写交易接收到一个错误时,并不意味着外设内的寄存器

没有更新。 读交易接收到一个错误时,能返回无效的数据。

对于一个读错误,并不要求外设将数据总线驱动为0。

12

AMBA APB协议规范

--AMBA APB写传输

APB写传输包括两种类型:

无等待状态写传输 有等待状态写传输

13

AMBA APB写传输

--无等待写传输

一个基本的无等待状态的写传输

地址、写入数据、写入信号和选择信号都在时钟上升沿后改变。

14

AMBA APB写传输

--无等待写传输

T1:写传输开始于地址PADDR,写数据PWDATA,写信号

22

AMBA APB读传输

--有等待读传输

协议保证在额外的扩展周期时,下面的信号保持不变

地址:PADDR。 写信号:PWRITE。 选择信号:PSEL。

使能信号:PENABLE。

保护类型:PPROT。

23

AMBA APB协议规范

---AMBA PSLVERR

APB错误响应

可以用来指示APB传输错误条件。在读和写交易中,可以发 生错误条件。 在一个APB传输中,在最后一个周期内,PSEL、PENABLE

25

AMBA APB错误响应

--写传输失败的例子