特权同学倾情奉献9G海量FPGA学习资料

FPGA期末复习大题库题库

FPGA期末复习大题库题库一、选择题1、在FPGA中,通常使用哪种编程语言进行编程?(A)Java;(B)C++;(C)Verilog;(D)Python。

2、FPGA的全称是什么?(A)Field Programmable Gate Array;(B)Static Random Access Memory;(C)Dynamic Random Access Memory;(D)General Purpose Computer。

3、在FPGA设计中,我们通常使用哪种硬件描述语言?(A)BCD;(B)Verilog;(C)VHDL;(D)All of the above.二、填空题1、FPGA的中文全称是_________。

2、FPGA是由_________的逻辑单元组成的。

3、在FPGA设计中,我们通常使用_________或_________硬件描述语言。

三、简答题1、简述FPGA的基本工作原理。

2、请描述一下FPGA在嵌入式系统中的应用。

3、请比较FPGA和ASIC的区别和优势。

四、编程题1、请编写一个简单的FPGA程序,实现一个四位二进制计数器。

2、请编写一个FPGA程序,实现一个四输入的AND门阵列。

五、设计题1、设计一个使用FPGA实现的数字频率计,可以测量输入信号的频率并显示结果。

2、设计一个使用FPGA实现的图像处理系统,可以识别输入图像中的特定物体并输出结果。

以上就是FPGA期末复习大题库题库的内容,包含了各种题型,从基础理论到实践应用,全方位地考察了学生对FPGA知识的掌握程度。

希望可以帮助学生们更好地进行FPGA的学习和复习。

管理学期末考试题库在管理学的世界里,知识是浩瀚的,而考试是让我们更好地理解和应用这些知识的关键途径。

以下是我们为管理学期末考试准备的题库,希望能够帮助大家进行最后的复习。

一、选择题1、在管理学中,以下哪个选项最能代表“激励”的概念?A.员工对工作的热情B.员工对工资的期待C.员工对公司的忠诚度D.员工对晋升的期望2、下列哪一项不是计划工作的基本步骤?A.确定目标B.分析环境C.制定实施计划D.确定资源需求3、在组织理论中,以下哪个选项不属于“古典组织理论”?A.泰勒的科学管理理论B.法约尔的行政管理理论C.韦伯的官僚组织理论D.梅奥的人群关系理论二、简答题1、请简述在决策过程中,如何平衡理性与直觉的冲突?2、请说明在计划工作中,如何进行风险评估以及相应的应对策略规划?3、请阐述在组织设计的过程中,如何平衡集权和分权的关系?4、请简述在领导理论中,交易型领导与变革型领导的区别及其优劣?5、请说明在激励理论中,马斯洛需求层次理论的主要内容以及应用。

FPGA可编程逻辑器件芯片XCKU5P-3FFVB676E中文规格书

综述赛灵思 Kintex ® UltraScale+™ FPGA 支持 -3、-2 和 -1 速度等级,其中 -3E 器件性能最高。

-2LE 器件和 -1LI 器件可以 0.85V 或 0.72V 的V CCINT 电压工作,并提供更低的最大静态功耗。

使用以 V CCINT = 0.85V 工作的 -2LE 和 -1LI 器件时,L 器件的速度规格与 -2I 或 -1I 速度等级相同。

以 V CCINT = 0.72V 工作时,-2LE 和 -1LI 器件的性能以及静态和动态功耗都将下降。

DC 和 AC 特性按以下温度范围来指定:扩展级 (E)、工业级 (I) 和军工级 (M)。

除正常工作的温度外或者除非另行说明,否则特定速度等级的所有 DC 和 AC 电气参数都相同(即,-1 速度等级的扩展级器件的时序特性与 -1 速度等级的工业级器件相同)。

但在每个温度范围内,仅限选定的速度等级和/或器件才可用。

本数据手册中的 XQ 参考信息仅适用于 XQ 加固型封装中可用的器件。

请参阅《军用级 UltraScale 架构数据手册:简介》 (DS895),以获取有关 XQ 军用级器件编号、封装和订购的更多信息。

所有供电电压和结温规格均代表最差情况下的规格。

所含参数为常用设计和典型应用的公用参数。

本数据手册属于 Kintex UltraScale+ FPGA 的整体文档集合的一部分,可通过赛灵思网站获取。

DC 特性绝对最大额定值Kintex UltraScale+ FPGA 数据手册: DC 和 AC 开关特性条款中英文版本如有歧义,概以英文版本为准。

•Advance 产品规格:这些规格仅基于仿真,通常在冻结器件设计规格不久后即可使用。

虽然采用此项指定的速度等级被视为相对稳定且保守,但可能发生某些漏报问题。

•Preliminary 产品规格:这些规格基于完整工程采样 (ES) 硅片特性。

采用此项指定的器件和速度等级旨在更加明确地表明期望的量产硅片性能。

FPGA设计实战演练(逻辑篇)- ch9 - 设计仿真

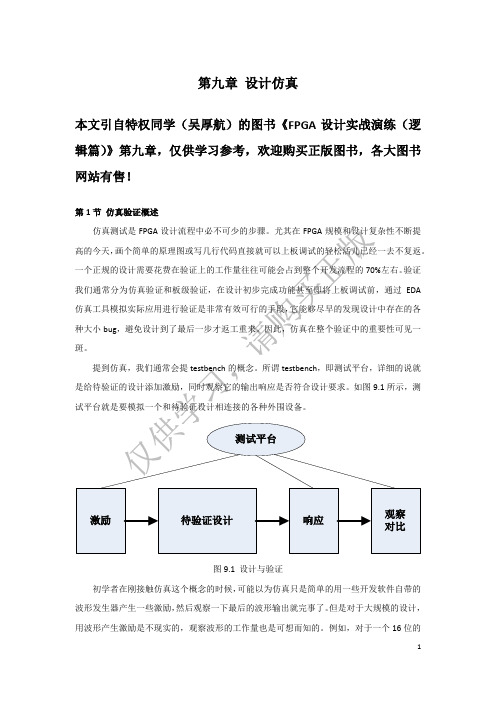

第九章设计仿真本文引自特权同学(吴厚航)的图书《FPGA设计实战演练(逻辑篇)》第九章,仅供学习参考,欢迎购买正版图书,各大图书网站有售!第1节仿真验证概述仿真测试是FPGA设计流程中必不可少的步骤。

尤其在FPGA规模和设计复杂性不断提高的今天,画个简单的原理图或写几行代码直接就可以上板调试的轻松活儿已经一去不复返。

一个正规的设计需要花费在验证上的工作量往往可能会占到整个开发流程的70%左右。

验证我们通常分为仿真验证和板级验证,在设计初步完成功能甚至即将上板调试前,通过EDA 仿真工具模拟实际应用进行验证是非常有效可行的手段,它能够尽早的发现设计中存在的各种大小bug,避免设计到了最后一步才返工重来。

因此,仿真在整个验证中的重要性可见一斑。

图9.1 设计与验证初学者在刚接触仿真这个概念的时候,可能以为仿真只是简单的用一些开发软件自带的波形发生器产生一些激励,然后观察一下最后的波形输出就完事了。

但是对于大规模的设计,用波形产生激励是不现实的,观察波形的工作量也是可想而知的。

例如,对于一个16位的输入总线,它可以有65536种组合,如果每次随机产生一种输入,那用波形岂不累死人。

再说输出结果的观察,对应65536种输入的65536种输出,看波形肯定让人花眼缭乱。

所以,testbench应该有更高效的测试手段。

对于FPGA的仿真,使用波形输入产生激励是可以的,观察波形输出以验证测试结果也是可以的,波形也许是最直观的测试手段,但绝不是唯一手段。

如图9.2所示,设计的测试结果判断不仅可以通过观察对比波形,而且可以灵活的使用脚本命令将有用的输出信息打印到终端或者产生文本进行观察,也可以写一段代码让他们自动比较输出结果。

总之,testbench的设计是多种多样的,它的语法也是很随意的,不像RTL图9.2 验证输出Testbench的编写其实也没有想象中那么神秘,笔者简单的将其归纳为3个步骤。

①对被测试设计的顶层接口进行例化。

fpga内部可用资源

fpga内部可用资源FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,内部集成了大量的可用资源,包括逻辑单元、寄存器、存储器等。

本文将分别介绍FPGA内部的这些可用资源。

1. 逻辑单元:FPGA内部包含大量的逻辑单元(Logic Element),用于实现各种逻辑功能。

逻辑单元通常由多个逻辑门组成,可以实现与、或、非、异或等逻辑运算。

逻辑单元可以根据需要进行编程,以实现不同的功能。

2. 寄存器:FPGA内部还包含大量的寄存器(Register),用于存储数据和状态信息。

寄存器可以存储单个数据位或多个数据位,并且可以进行读写操作。

寄存器的数量和位宽可以根据设计需求进行配置。

3. 存储器:FPGA内部还集成了各种类型的存储器,包括片上存储器(On-chip Memory)和外部存储器接口(External Memory Interface)。

片上存储器通常用于存储中间数据和程序代码,具有较快的访问速度和较小的延迟。

外部存储器接口可以连接外部存储器芯片,用于存储大容量的数据。

4. 数字信号处理器(DSP):FPGA内部还集成了一定数量的数字信号处理器(DSP),用于实现高性能的数字信号处理功能。

DSP可以进行复杂的算术运算和滤波操作,以满足各种信号处理需求。

5. 时钟管理器:FPGA内部还包含时钟管理器(Clock Manager),用于生成和分配时钟信号。

时钟信号是FPGA设计中至关重要的一部分,时钟管理器可以根据设计需求生成多个时钟信号,并对时钟进行分频、倍频等操作。

6. 通信接口:FPGA内部还提供了多种通信接口,包括UART、SPI、I2C、PCI Express等。

这些接口可以与外部设备进行数据交互,实现与外界的通信功能。

7. 乘法器:FPGA内部还集成了大量的乘法器(Multiplier),用于实现乘法运算。

乘法器可以进行定点数和浮点数的乘法运算,具有较高的计算效率和精度。

小梅哥和你一起深入学习FPGA之串口调试(一)

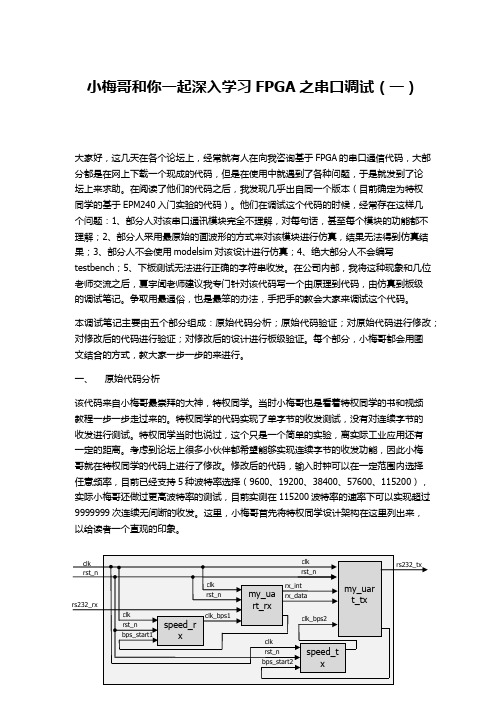

小梅哥和你一起深入学习FPGA之串口调试(一)大家好,这几天在各个论坛上,经常就有人在向我咨询基于FPGA的串口通信代码,大部分都是在网上下载一个现成的代码,但是在使用中就遇到了各种问题,于是就发到了论坛上来求助。

在阅读了他们的代码之后,我发现几乎出自同一个版本(目前确定为特权同学的基于EPM240入门实验的代码)。

他们在调试这个代码的时候,经常存在这样几个问题:1、部分人对该串口通讯模块完全不理解,对每句话,甚至每个模块的功能都不理解;2、部分人采用最原始的画波形的方式来对该模块进行仿真,结果无法得到仿真结果;3、部分人不会使用modelsim对该设计进行仿真;4、绝大部分人不会编写testbench;5、下板测试无法进行正确的字符串收发。

在公司内部,我将这种现象和几位老师交流之后,夏宇闻老师建议我专门针对该代码写一个由原理到代码,由仿真到板级的调试笔记。

争取用最通俗,也是最笨的办法,手把手的教会大家来调试这个代码。

本调试笔记主要由五个部分组成:原始代码分析;原始代码验证;对原始代码进行修改;对修改后的代码进行验证;对修改后的设计进行板级验证。

每个部分,小梅哥都会用图文结合的方式,教大家一步一步的来进行。

一、原始代码分析该代码来自小梅哥最崇拜的大神,特权同学。

当时小梅哥也是看着特权同学的书和视频教程一步一步走过来的。

特权同学的代码实现了单字节的收发测试,没有对连续字节的收发进行测试。

特权同学当时也说过,这个只是一个简单的实验,离实际工业应用还有一定的距离。

考虑到论坛上很多小伙伴都希望能够实现连续字节的收发功能,因此小梅哥就在特权同学的代码上进行了修改。

修改后的代码,输入时钟可以在一定范围内选择任意频率,目前已经支持5种波特率选择(9600、19200、38400、57600、115200),实际小梅哥还做过更高波特率的测试,目前实测在115200波特率的速率下可以实现超过9999999次连续无间断的收发。

许诺分享资源

许诺分享资源分享资源是一项重要的行为,它可以帮助他人获得所需的信息和知识。

我希望通过这篇文章,能够向大家介绍一些我所熟悉的资源,并且希望这些资源能对读者有所帮助。

在我多年的学习和工作经验中,我积累了许多有用的资源。

首先,我想分享一些关于学习的资源。

学习是每个人成长的重要一环,而学习资源的质量直接影响到学习的效果。

我推荐大家使用一些在线学习平台,这些平台提供了丰富多样的课程和学习资料,可以满足不同人的需求。

此外,还有一些开放式课程网站,可以免费获取一些知名大学的课程资源。

这些资源可以帮助我们扩展知识面,提高技能水平。

对于工作而言,我还想分享一些关于职业发展的资源。

在现代社会,职业发展至关重要。

我们可以从一些招聘网站上找到适合自己的职位,并了解相关的行业信息。

此外,一些职业培训机构也提供了一些实用的职业技能培训课程,可以帮助我们提升职业能力。

此外,一些专业书籍和期刊杂志也是我们了解行业动态和学习新知识的重要资源。

除了学习和工作资源,我还想分享一些关于生活的资源。

生活中有很多方面需要我们关注和学习,比如健康、家庭、旅行等等。

我推荐大家使用一些健康管理APP,可以帮助我们记录健康数据和制定健康计划。

此外,旅行是一种放松和享受的方式,我建议大家使用一些旅行社交平台,可以找到旅行灵感和分享自己的旅行经历。

我希望通过分享这些资源,能够帮助到大家。

学习、工作和生活都是一个不断学习和成长的过程,而资源的分享可以让我们更加高效地学习和成长。

希望大家能够善于利用这些资源,不断提升自己的能力和素质。

谢谢大家的阅读!。

FPGA可编程逻辑器件芯片XCZU19EG-2FFVC1760E中文规格书

找FPGA和CPLD可编程逻辑器件,上深圳宇航军工半导体有限公司LPDDR4 GuidelinesLPDDR4 Pin RulesThe LPDDR4 pin rules are for single and dual-rank memory interfaces.•All unused DDR pins can be left unconnected. For example, in an 64-bit interface without ECC, the PS_DDR_DQ64 to PS_DDR_DQ71, PS_DDR_DQS_P8/N8, andPS_DDR_DM8 pins can be left unconnected.•Connect the PS_DDR_ZQ pin to GND using a 240Ω resistor. There should be separate 240Ω resistors at the FPGA and at the DRAM.•To achieve maximum performance, address copy mode is suggested.LPDDR4 Pin Swapping Restrictions•Command/address bits cannot be swapped.•To support write DQS to DQ training, DQ byte lane swapping is not allowed.•To support write DQS to DQ training, DQ bits with bytes 0, 2, and 8 are not allowed to be swapped.•Bits within bytes 1 and 3 can be swapped.LPDDR4 Pinout Example for Supported ConfigurationsTable2-3 shows a pinout example for the LPDDR4 supported configurations. Fortermination details, see the UltraScale Architecture PCB Design Guide[Ref14]. When notbeing used for a memory interface, all pins should be left unconnected with the exception of VCCO_PSDDR and VCC_PSDDR_PLL, which should be tied to GND.RFSoC Data Sheet: DC and AC Switching Characteristics[Ref9], where both VCC_PSINTFP andVCC_PSINTFP_DDR must be connected to the same supply and thus both must be powered to avoid MBIST failure.LPDDR3 GuidelinesLPDDR3 Pin RulesThe LPDDR3 pin rules are for single and dual-rank memory interfaces.•All unused DDR pins can be left unconnected. For example, in an 64-bit interface without ECC, the PS_DDR_DQ64 to PS_DDR_DQ71, PS_DDR_DQS_P8/N8, andPS_DDR_DM8 pins can be left unconnected.•Connect the PS_DDR_ZQ pin to GND using a 240Ω resistor. There should be separate 240Ω resistors at the FPGA and at the DRAM.•To achieve maximum performance, address copy mode is suggested.PS_DDR_A4CA4_A CA4_A CA4PS_DDR_A5CA5_A CA5_A CA5PS_DDR_A6CA6_A CA6_A CA6PS_DDR_A7CA7_A CA7_A CA7PS_DDR_A8CA8_A CA8_A CA8PS_DDR_A9CA9_A CA9_A CA9PS_DDR_A10CA0_B CA0_B Can be left unconnected.PS_DDR_A11CA1_B CA1_B Can be left unconnected.PS_DDR_A12CA2_B CA2_B Can be left unconnected.PS_DDR_A13CA3_B CA3_B Can be left unconnected.PS_DDR_A14CA4_B CA4_B Can be left unconnected.PS_DDR_A15CA5_BCA5_BCan be left unconnected.PS_DDR_A16Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_A17Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_ACT_N CA9_BCA9_BCan be left unconnected.PS_DDR_ALERT_N Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_BA0CA6_B CA6_B Can be left unconnected.PS_DDR_BA1CA7_B CA7_B Can be left unconnected.PS_DDR_BG0CA8_BCA8_BCan be left unconnected.PS_DDR_BG1Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_CK_N0CK_c_A CK_c_A CK_cPS_DDR_CK_N1CK_c_B CK_c_B Can be left unconnected.PS_DDR_CK0CK_t_A CK_t_A CK_tPS_DDR_CK1CK_t_BCK_t_BCan be left unconnected.PS_DDR_CKE0CKE_A and CKE_B CKE0_A and CKE0_B CKE0PS_DDR_CKE1Can be left unconnected.CKE1_A and CKE1_B CKE1PS_DDR_CS_N0CS_n_A and CS_n_B CS0_n_A and CS0_n_B CS0_n PS_DDR_CS_N1Can be left unconnected.CS1_n_A and CS1_n_B CS1_n PS_DDR_DM0DM0_A DM0_A DM0PS_DDR_DM1DM1_A DM1_A DM1PS_DDR_DM2DM2_A DM2_A DM2PS_DDR_DM3DM3_A DM3_A DM3PS_DDR_DM4DM0_B DM0_B Can be left unconnected.PS_DDR_DM5DM1_BDM1_BCan be left unconnected.Table 2‐4:LPDDR3 Supported Pinout Configurations) (Cont’d)Pin NameLPDDR3 64-bitLPDDR3 64-bit (Dual Rank)LPDDR3 32-bit (Dual Rank)PS_DDR_DQS_P6DQS2_t_B DQS2_t_BCan be left unconnected.PS_DDR_DQS_P7DQS3_t_BDQS3_t_BCan be left unconnected.PS_DDR_DQS_P8DQS_t_ECC, can be left unconnected without ECC.DQS_t_ECC, can be left unconnected without ECC.DQS_t_ECC, can be left unconnected without ECC.PS_DDR_ODT0ODT_A and ODT_B ODT_A and ODT_B ODTPS_DDR_ODT1ODT_CA_BCan be left unconnected.Can be left unconnected.PS_DDR_PARITY Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_RAM_RST_N Can be left unconnected.Can be left unconnected.Can be left unconnected.PS_DDR_ZQConnect a 240Ω resistor to GND.(2)Connect a 240Ω resistor to GND.(2)Connect a 240Ω resistor to GND.(2)Table 2‐4:LPDDR3 Supported Pinout Configurations) (Cont’d)Pin NameLPDDR3 64-bitLPDDR3 64-bit (Dual Rank)LPDDR3 32-bit (Dual Rank)。

最新启智电子倾情奉献hnqizhiPPT课件

RXD 位采样脉冲

起始 D0 D1 D2 D3 D4 D5 D6 D7 停止位

RI(中断标志)

80C51串行口的工作方式

三、方式2和方式3

方式2或方式3时为11位数据的异步通信口。TXD为数据发送 引脚,RXD为数据接收引脚 。

起

空

始

闲

位

1帧共11位 数据位9位

停

止

空

位

闲

D0

D7

RB8/TB8

LSB

以便正确地接收和发送数据 。

TXD

M

计 RXD

O

算 RTS 机

D E

DSR

M

电话线

TXD

M

O

RXD 计

D E

RTS 算 机MFra bibliotekDSR

远程通信连接

TXD

计 RXD 算 机 甲

串行通信接口

TXD

RXD 计 算 机 乙

TXD RXD 计4 算5 机6 甲 20

TXD

RXD 4计 5算 6机 20 乙

近程通信连接

80C51串行口的控制寄存器

TI,发送中断标志位。在方式0时,当串行发送第8 位数据结束时,或在其它方式,串行发送停止位 的开始时,由内部硬件使TI置1,向CPU发中断申 请。在中断服务程序中,必须用软件将其清0,取 消此中断申请。

RI,接收中断标志位。在方式0时,当串行接收第8 位数据结束时,或在其它方式,串行接收停止位 的中间时,由内部硬件使RI置1,向CPU发中断申 请。也必须在中断服务程序中,用软件将其清0, 取消此中断申请。

2、有电平偏移 RS-232C总线标准要求收发双方共地。通信距离较大时 ,收发双方的地电位差别较大,在信号地上将有比较大的 地电流并产生压降。

fpga学习心得

FPGA学习心得学习fpga一个多月以来,完全从零开始学习,感觉自己学到的东西真不少,虽然还不是很熟练,不过也对fpga有了很好的了解。

以前一直没有想过要来总结些什么,是感觉自己对于fpga根本就像是一无所知一样,虽然天天在学,不过确实没有一个总体观念,学的东西太混乱也没有一个总体的框架。

到了今天终于觉得自己的学习已经小有成就了,虽然还是没有能够独立设计的自信。

在最初学习的时候最主要就是对于fpga结构的一个基本认识和对硬件描述语言verilog HDL语言的学习。

之所以选择学习fpga是因为在这一学期找工作中发现,现在很多公司都需要会一点fpga方面的知识,在笔试的时候也会偶尔遇到一些用HDL语言编程的试题。

现在很多硬件工程师已经不再是单纯的用传统的方法进行电路的设计,至少现在很多招聘的岗位当中不再是单纯的电路的设计了,很多都涉及到嵌入式和HDL语言。

Fpga现在正在以异常的速度发展,在08年全球金融危机的时候大多数行业都呈现在下滑的趋势,而fpga的厂商如xilinx和altera等公司的收入却呈现出增长的态势。

在我看来fpga必将是将来硬件工程师不可缺少的一项本领,这也就是我学习fpga的原因之一。

一、硬件描述语言:对于硬件描述语言(HDL)语言我选择的是和C语言类似的verilog HDL语言,虽然VHDL语言在很多方面优于verilog HDL语言,但是作为初学,还是先学习一个简单一点的语言,尽量先将所需要学习的东西过一遍,将来等时间允许的时候再去学习VHDL语言,在网上有看到现在出来了一个叫system verilog的语言,据说融合了verilog 和VHDL语言各自的优点,可能将来会成为行业统一的语言吧。

verilog HDL现阶段主要接触的就是对组合逻辑电路和时序电路的描述了。

所接触的程序中以always @ (*)模块居多,几乎是所见过模块的核心部分了,其实在学习这个语言上面也没有花太多的时间,因为有对C语言的学习,所以就先入为主了。

FPGA经典100问之<下载验证 16 问>

FPGA经典100问之<下载验证16问>FPGA是什么?FPGA即现场可编程逻辑门阵列(英语:Field Programmable Gate Array, FPGA),是一个含有可编辑元件的半导体设备,可供使用者现场程式化的逻辑门阵列元件。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

现把历年来众多网友和专家联手打造的FPGA经典100问奉献给大家,包括<HDL 28问>、<仿真20问>、<设计实现31问>、<下载验证16问>、<入门与提高5问>。

初学者必备!FPGA经典100问之<HDL 28问>&<仿真20问>下载点击下载>>45篇博文精粹《菜鸟变高手,草根成长记》点击下载>>特权同学倾力巨献---FPGA学习资料下载汇总1、nios2_cycloneII速度问题yuan_ya问:在EP2C8-208-Pin中,老师把程序放在EPCS4里面,然后映射到SDRAM里面,我的问题是:1.如果没在SDRAM,程序直接在EPCS4里面运行,速度能达到多少?有SDRAM的话,速度达到多少?2.板子里面的CLK是25MHZ,有倍频到100MHZ的一个设置,是不是这个FPGA的速度最大是100MHZ?不是的话那么我们常说的它能跑多少MHZ指的是它的什么速度?谢谢。

ilove314答:这个问题很复杂。

你要去深入了解一般嵌入式系统的工作方式。

从ROM直接启动并运行与从ROM启动但RAM运行,性能差异非常大。

ROM肯定要比RAM慢很多。

另外,SDRAM 的时钟频率不是CPU的运行速率,这个不能对等,你要去了解CPU的工作机制,什么取指、译码、操作等等,这样你才能够去评估系统的运行速率。

查看更多回答与讨论>>2、nios运行时卡死sangreal599问:本人在EDN第一次发帖:我使用的是quartus 11.0和nios IDE 11.0,当run as hardware的时候,卡在下图中半个多小时都没有前进:请问各位大神这是什么原因?1赤子旭升答:可能是连接的问题,你在运行之前,这样操作一下:Debug Configurations ->Target Connection -> Refresh Connections ->Apply 试一下看看吧查看更多回答与讨论>>3、讨教NIOS 2开发板中TFT-LCD 例子的一个问题xdx8088问:关于SF—NIOS 2 开发板,TFT——LCD的例子中,有个问题一直没有想明白,请问下面函数里面为什么y,x address 分别是向左移动10位和1位,根据as_LCDwr 模块内设置,应该是低9位为x 地址,因此应该是y 向左移动9位,x 不需移动吧?急盼高手指点。

读特权同学《深入浅出玩转FPGA》有感

读特权同学《深入浅出玩转FPGA》有感看了特权同学的这本书,感悟颇多,最终使我重新确立了目标。

只是思路有些杂乱,我得慢慢道来: 初识特权同学实在END网站上,因为他的FPGA助学活动,在得到他的35集FPGA教学视频后,得知他已经和北京航空航天大学出版社合作出板了《深入浅出玩转FPGA》一书。

对于国内格式呆板、内容互抄的教科书,我是一直没有任何兴趣的,但是对于这样一个搞过FPGA项目的工程师写出的经验之谈,而且是以随笔的形式写出的书,我是没有任何理由放过的。

也许我最需要的不是一份说教的知识,而是一个可以在我最困难的时候让陪我聊天、给我动力的‘人’,而这个‘人’就隐藏在这本书点点滴滴、洋洋洒洒的文字之间,等着我去感悟。

由于我个人是习惯在当当网买书的,于是当下就去当当网搜索了一下,果然有这本书,售价是31.9元,但由于最近经济的原因我始终没有点下购买的按钮,于是自己买到这本书的计划便搁浅了。

也就是昨天我和一帮兄弟们去吉大的时候,偶然在兄弟那边看到了这本书,于是很爱不释手,当时便决定从兄弟手中‘横刀夺爱’了。

呵呵,于是,这本书便随我来到了理工,被我带到了实验室。

对于这样一本不同于现代呆板教材的书,我是很欣赏的,于是我开始用心去读这本书,去尽量感悟这本书的精髓,破开表面的知识去追求作者要给我们表达的深层次的意义。

很有幸的,我最后的结论是我没有选错书,在这本书中我感悟了很多,虽然我只读了第一个晚上,但这本书给我带来的感悟要比其他书籍在几周甚至几个月给我带来的感悟远远多得多...我感悟了很多,依靠串行触发是解决不了的,于是,我得用并行触发的方式来表达我的思路,首先得解释一下什么是并行触发:并行是指可以在同一时间进行响应,而没有顺序的问题。

于是,在这部分,我拿并行的概念套用一下,下面的这些感悟没有刻意的进行先后排序,既没有重要程度的高低和内容高低的划分,因为我认为:每一点思考都可以带来进步。

下面我就开始慢慢道来:1:它纠正了我对FPGA的认识 说实话,我的兄弟在去年寒假就给我买好了FPGA开发板,我们分配的任务是我在理工主要攻FPGA方向,很惭愧的是当我用原来单片机的方式去学习FPGA时遇到了很大的障碍,这段学习的路进展很缓慢,于是不知不觉已经推迟到了今年暑假。

闽教版(2020)小学信息技术六年级上册《指挥角色听命令》同步练习题附知识点归纳

闽教版(2020)小学信息技术六年级上册《指挥角色听命令》同步练习题附知识点归纳一、课文知识点归纳:1. Scratch中的基本积木类型,如移动、说、停止等。

2. 如何使用“当...发生时”命令来响应事件。

3. 使用“重复”积木实现角色的循环动作。

4. 如何通过设置条件来控制角色的行为。

二、同步练习题。

(一)、填空题。

1. 在Scratch编程中,我们可以使用“______”积木来让角色执行特定的动作。

2. 当我们想要角色听到指令后做出反应,可以使用“______”命令。

3. 如果要让角色在舞台上移动,需要使用“______”积木并指定移动的步数。

(二)、选择题。

1. 以下哪个积木可以用来让角色说一句话?()A. 移动10步B. 说“你好”持续2秒C. 旋转180度2. 在Scratch中,如何让角色停止当前的动作?()A. 使用“删除此积木”B. 使用“播放声音”C. 使用“停止所有脚本”3. 如果你想要角色重复执行某个动作,你应该使用哪个积木?()A. 如果...那么...B. 重复10次C. 随机选择(三)、判断题。

(正确的打“√”,错误的打“×”)1. 在Scratch中,角色只能按照预设的顺序执行命令,不能同时执行多个命令。

()2. 使用“说”积木时,角色会一直说话,直到你手动停止。

()3. 可以通过调整“等待”积木的时间来控制角色动作的快慢。

()(四)、简答题。

1. 描述一下如何让角色在舞台上向右移动100步。

__________________________________________________________________ __________________________________________________________________ __________________________________________________________________ 2.当你想要角色重复执行某个动作,但又希望能在特定条件下停止,你会如何操作?__________________________________________________________________ __________________________________________________________________ __________________________________________________________________三、学习目标:1. 掌握Scratch的基本操作,包括角色的移动和命令的执行。

BJ-EPM实验板介绍

BJ-EPM240CPLD开发板介绍BJ-EPM240学习板是特权同学和知名电子技术网站合作推出的一款FPGA/CPLD入门级学习板,该学习板在EDN助学活动期间以低廉的价格提供给所有注册会员,并且赠送免费的PCB板。

学习板以齐全的资料、良好的代码风格博得了广大网友的一致认可,很适合初学者入门学习。

该板子的一切相关问题都可以在EDN网站的CPLD/FPGA助学小组(网址:/1375/)里进行讨论。

该开发板配套北航出版社2010年6月出版的《深入浅出玩转FPGA》进行深入学习,并且特权同学录制了同名的《深入浅出玩转FPGA》视频教程配套。

1.BJ-EPM240学习板功能框图图1和图2是整板系统的功能框图,从图中可以清楚地看到EPM240T100学习板上丰富的外设资源及其位置分布情况。

图1 BJ-EPM学习板顶层资源分布及功能框图图2 BJ-EPM学习板底层资源分布及功能框图2.BJ-EPM240学习板基本配置●主芯片使用的是 Altera公司的MAX II系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8Kbit Flash的存储空间。

●50MHz有源晶振,作为系统主时钟。

●低电平复位按键,使用EPM240的全局复位管脚。

●8色VGA接口1个,让大家掌握电脑显示器的驱动原理。

●RS232串口1个,通过串口调试助手轻松实现UART通信协议。

●PS/2 接口1个,实现键盘解码,配合串口调试助手在PC机上显示键值。

●70ns快速读写的SRAM芯片IS62LV256-70U,具有32KB存储空间,让大家熟悉SRAM的读写操作。

●EEPROM 芯片AT24C02,让大家熟悉使用verilog进行I2C通信。

●4个独立按键,进行verilog脉冲采样和按键消抖控制。

●4个流水灯,配合4位按键进行Johnson计数器实验。

●蜂鸣器,实现简单的分频计数器。

●2位数码管,使用其进行计数实验。

基于大概念的小学语文单元整体教学设计策略研究——以统编版小学语文五年级上册第一单元为例

基于大概念的小学语文单元整体教学设计策略研究——以统编版小学语文五年级上册第一单元为例

毛晨媛;钟惊雷

【期刊名称】《教师》

【年(卷),期】2024()11

【摘要】大概念统摄下的大单元教学是当下学校教育变革的热点话题,教师需从育人的角度整体思考教学组织逻辑。

文章以统编版小学语文五年级上册第一单元为例,用大概念统摄语文要素学习,提出聚焦单元要素,提炼单元大概念、紧扣单元主题,架构大任务体系、勾连真实生活,设计单元活动、规划评价体系,提升评价质量,以整体性搭建大单元教学的实践路径。

【总页数】3页(P18-20)

【作者】毛晨媛;钟惊雷

【作者单位】湖州师范学院

【正文语种】中文

【中图分类】G623.2

【相关文献】

1.大单元设计下小学语文群文阅读的教学实践研究--以统编版语文五年级下册第一单元为例

2.基于核心素养的小学语文大单元整体教学策略研究——以统编版小学语文教材五年级上册“民间故事”为例

3.基于核心素养的小学语文单元整体教学设计与实施——以统编教材小学语文五年级下册单元整体教学设计为例

4.基于学

习任务群的小学语文单元教学策略探讨——以“统编版”小学语文五年级上册第三单元教学为例

因版权原因,仅展示原文概要,查看原文内容请购买。

SF-EP1C FPGA开发板介绍

SF-EP1C FPGA开发板介绍随着制造工艺不断提高、成本不断下降,FPGA大有替代专用ASIC甚至通用处理器之势。

对于电子行业,学习一门新技术,手头没有板子,只停留在理论上是很难进一步提高的。

而市场上的FPGA/CPLD学习板/开发板更是满天飞,板子的价格、质量、乃至提供的资料例程鲜有令人满意的。

就以价格而言,动辄数百乃至过千使得很多学生朋友望而却步。

市场上非官方的板子大多功能简单,只是带大家跑跑流水灯、数码管、蜂鸣器,功能强点的能做做VGA实验、串口实验或者存储器SRAM\SDRAM\FLASH的实验。

但是他们配套的资料鲜有高质量的好例程,甚至很多都没有详细的注释,让大家学起来很是费劲。

而官方的板子看起来还不错,只可惜咱的腰包都不鼓——买不起。

这个SF-EP1C板子,之所以选择altera的低成本高性价比cyclone系列的FPGA作为主芯片,想必大家都意识到了,成本对于大多数朋友是最敏感的。

而EP1C3T144(标准配置,大家也可以使用EP1C6T144焊接上去,特权同学在硬件电路设计上做到了二者的完全兼容)虽然只有不到3000个LEs,但是大家如果写起代码来就会深有感触,这个规模的逻辑资源也是可以胜任很多应用的。

另外,如果你是个新手,只希望能入门,这块FPGA板子也许不适合你;如果你想学NIOS,那么也可以明白的告诉你,这块板子也不适合你;但是如果你想通过这样一块板子来掌握如何利用FPGA器件本身的各种资源来完成一个像模像样的工程,那么你可以尝试一下。

该开发板在EDN助学活动期间以低廉的价格提供给所有注册会员,并且赠送免费的PCB板。

该板子的一切相关问题都可以在EDN的CPLD/FPGA助学小组(网址:/1375/)里进行讨论。

1.SF-EP1C开发板功能框图如图1和图2所示,SF-EP1C开发板有着比较丰富的外设,也给用户预留了一些可扩展的接口。

图1 SF-EP1C开发板正面资源分布及功能框图图2 SF-EP1C开发板背面资源分布及功能框图2.SF-EP1C开发板基本配置z FPGA使用EP1C3T144C8,硬件电路充分考虑了可升级性,该板子同样适用于EP1C6T144;z板载1Mbit串行配置芯片EPCS1,支持AS和JTAG两种配置方式;z5V/1.5A DC电源供电,内部产生核压1.5V、I/O电压3.3V;z PLL电源电路进行滤波处理,更加稳定可靠;z板载25MHz有源晶振,预留1个未焊接晶振接口;z4个独立按键、2个复用LED;z1个串口;z1个SD卡接口;z1个256色VGA接口;z1个64MBit(4*1M*256Bit) SDRAM;z8位拨码开关;z1个复位按键和1个FPGA重配置按键;z4位数码管,仅使用3个I/O口控制,由两个74HC595芯片实现;z2个20PIN的扩展接口,供大家任意发挥;3.Cyclone器件简介Altera的Cyclone系列可编程门阵列是基于1.5V、0.13um的SRAM全铜工艺制造。

Verilog HDL黑金资料FPGA

根据上面两个例子的三路加法器,一个是由组合逻辑级建模而成,另外一个则是由 RTL 级建模而成。 组合逻辑级建模给人最直接的印象就是模块都不带 “时钟信号” , 反之 RTL 级建模的最大特征性,就是模块都会伴随 “时钟信号” 。当然,笔者不可能仅以“时钟 信号”来区分组合逻辑级建模和 RTL 级建模。 在实际的学习中过于在意区分“什么是组合逻辑级建模,什么是 RTL 级建模”是对学 习没有任何帮助的 (不知道为什么很多参考书都很习注重区分) , 凡是有关 Verilog HDL 语言的建模它们都被需要。话虽如此,但是在这一本笔记里笔者还是比较注重 RTL 级 的建模。

0.2 HDL 语言的层次

有一个很好笑的话题,老师常常都说 HDL 语言的层次是汇编语言和 C 语言的之间。假 设汇编语言是低级语言,C 语言是高级语言,那么 HDL 语言既是不上又不小?啊哈哈 哈,如果站在人类之中它亦是不男也不女。我们不需要为这个无聊的话题,浪费太多思 考的时间。HDL 语言的英文全名是 Hardware Description Language ,中文译名就是硬 件描述语言。事实上无论是汇编语言也好还是 C 语言也好,它们的作用就是用来控制处 理器,反之 HDL 语言的作用只是用来建立一个硬件的模块而已。

module Add_module ( input CLK, input RSTn, input [7:0]A, input [7:0]B, input [7:0]C, Output[15:0]) ; reg [15:0]rTemp; alawys @ ( posedge CLK negedge RSTn ) if( !RSTn ) rTemp <= 4'0; else rTemp <= A + B + C; assign Output = rTemp; endmodule

有声有色的自学利器

有声有色的自学利器作者:刘永渤来源:《中国信息技术教育》2015年第20期在2015年的NOC活动中,我有幸担任数字化学习工具评优赛项的评委。

在全国众多的作品中,祝老师的《声音的采集与加工》学习工具使我眼前一亮,受益匪浅。

该作品是使用Flash软件设计的精品数字化学习工具,将知识与操作互动结合在一起,界面优美,互动性强。

该学习工具不仅让人学会了如何利用GoldWave等相关软件进行声音的采集和后期的加工,更能给人一种美的享受。

它能够让原本对声音的采集与加工一窍不通的人在观看与学习中,潜移默化地了解并掌握这一技能,这正是一节好课最关键、最根本的衡量标准。

尤其值得称赞的是该作品从学生“学”的角度去设计,体现了以学生自主学习为主的新课标思想,以下是我对这一学习工具的认识。

对教材的处理本节的教材内容基本上是音频理论知识和音频处理的相关操作介绍,如果按照教材的先后顺序进行学习,学生很难从需求出发理解学习内容的实际意义,学习兴趣也很难被调动起来。

因此祝老师对教材进行了二次开发,重新编排了学习内容,将对学习内容的了解和掌握适时穿插于整个作品的制作过程中。

让学生带着兴趣探索新知,他们就会对所学内容记忆深刻,而且还能构建出许多课本上没有的新知识。

对教学内容的设计学习工具中的教学内容由主题活动、操作体验、实战练习、学习拓展、协作探究五大环节组成。

主题活动的引入很巧妙,调动学生的兴趣后使之开始体验学习任务。

操作体验后的实战练习分步进行并最终以作品的形式展示。

在完成主题内容的前提下通过学习拓展环节扩充学生的知识储备,开阔学生的视野,进一步提高学生的信息技术应用能力。

最后以小组为单位,组内分工应用学到的知识协作完成探究任务。

五个环节紧凑有序,环环相扣,课堂教学效率很高。

对讲解的考究在讲授新课时,借助互联网的信息资源,展示学生感兴趣的示例,调动学生的多种感官,使学生对音频加工的学习产生兴趣。

在操作体验过程中,采用任务驱动法,利用事先设计好的完成总任务的各个子任务,驱动学生逐一完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

特权同学倾情奉献9G海量FPGA学习资料

本人最恨恶淘宝上那些卖资料的JS了,本来就是网络上免费搜集来的资料,居然还冠冕堂皇的拿来生财。

为此,本人特别将手上所有的资料共享给广大的FPGA爱好者们。

百度网盘下载地址:

/s/1o62lMYY

《深入浅出玩转FPGA》视频教程:35课时

特权同学精心录制的35课时深入浅出FPGA入门、进阶课程。

可配套北航出版社2010年6月上市的《深入浅出玩转FPGA》一书学习。

整部视频先是阐述FPGA的基本概念和学习方法,接着通过相应的开发套件BJ-EPM和SF-EP1C进行实践学习。

是初学者迈入

《特权和你一起学NIOS2》视频教程:20课时

特权同学的又一力作,SOPC的设计与底层逻辑设计不同,这部教程完全以另一种方式带领初学者领悟基于FPGA的嵌入式系统设计,同时也希望借助本教程能使大家熟悉在EDS 软件平台上实现NIOS2的编程和开发。

与本视频完全配套同步的图书《爱上FPGA开发——

Altera官方专题视频教程:38课时

特权fpga技术公开课

Altera官方资料(各类手册和应用笔记)(略)

百度网盘下载地址:

/s/1o62lMYY。