实验报告_频率计

频率计实验报告

频率计实验报告一,实验目的1. 应用AT89S52单片机、单片机的I/O端口外扩驱动器74HC573和74HC138、LED数码管动态显示等实现对外部信号频率进行准确计数的设计。

二,实验要求A.基本要求:使用单片机的定时器/计数器功能,设计频率测量装置。

(1)当被测频率fx<100Hz时,采用测周法,显示频率XXX.XXX;当被测频率fx>100Hz时,采用测频法,显示频率XXXXXX。

(2)利用键盘分段测量和自动分段测量。

(3)完成单脉冲测量,输入脉冲宽度范围是100µs-0.1s。

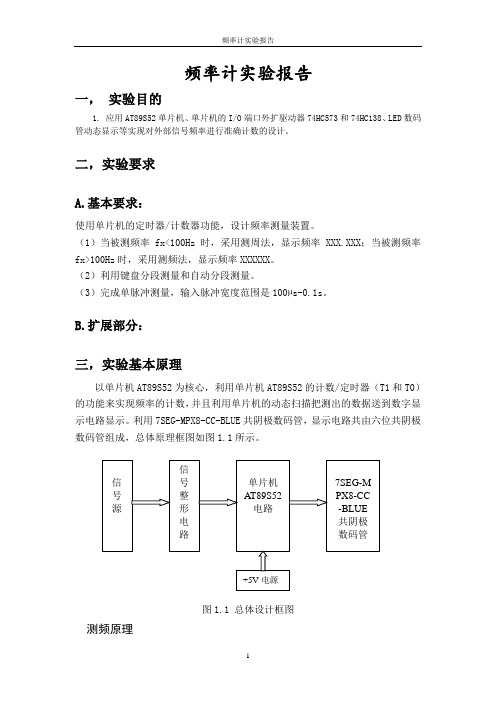

B.扩展部分:三,实验基本原理以单片机AT89S52为核心,利用单片机AT89S52的计数/定时器(T1和T0)的功能来实现频率的计数,并且利用单片机的动态扫描把测出的数据送到数字显示电路显示。

利用7SEG-MPX8-CC-BLUE共阴极数码管,显示电路共由六位共阴极数码管组成,总体原理框图如图1.1所示。

图1.1 总体设计框图测频原理测量频率有测周法和测频法两种。

如图2.2和图2.3所示图1.2测周法 图1.3测频法(1)测频法(T 法):通过测量脉冲宽度来确定频率,适用于高频。

(2)测周法(M 法):是计数器在一定时间内对速度的脉冲数,确定频率,适用于低频。

四,实验设计分析针对要实现的功能,采用AT89S52单片机进行设计,AT89S52 单片机是一款低功耗,高性能CMOS8位单片机,片内含8KB 在线可编程(ISP )的可反复擦写1000次的Flash 只读程序存储器,器件采用高密度、非易失性存储技术制造,兼容标准MCS- 52指令系统及80C52引脚结构。

这样,既能做到经济合理又能实现预期的功能。

在程序方面,采用分块设计的方法,这样既减小了编程难度、使程序易于理解,又能便于添加各项功能。

延时程序等。

运用这种方法,关键在于各模块的兼容和配合,若各模块不匹配会出现意想不到的错误。

首先,在编程之前必须了解硬件结构尤其是各引脚的用法,以及内部寄存器、存储单元的用法,否则,编程无从下手,电路也无法设计。

频率计实验报告

频率计实验报告一、实验目的本次实验的目的是通过设计和搭建频率计电路,掌握频率测量的基本原理和方法,熟悉相关电子元器件的使用,提高电路设计和调试的能力,并深入理解数字电路中计数器、定时器等模块的工作原理。

二、实验原理频率是指周期性信号在单位时间内重复的次数。

频率计的基本原理是通过对输入信号的周期进行测量,并将其转换为频率值进行显示。

常见的频率测量方法有直接测频法和间接测频法。

直接测频法是在给定的闸门时间内,对输入信号的脉冲个数进行计数,从而得到信号的频率。

间接测频法则是先测量信号的周期,然后通过倒数计算出频率。

在本次实验中,我们采用直接测频法。

使用计数器对输入信号的脉冲进行计数,同时使用定时器产生固定的闸门时间。

在闸门时间结束后,读取计数器的值,并通过计算得到输入信号的频率。

三、实验设备与器材1、数字电路实验箱2、示波器3、函数信号发生器4、集成电路芯片(如计数器芯片、定时器芯片等)5、电阻、电容、导线等若干四、实验步骤1、设计电路原理图根据实验要求和原理,选择合适的计数器芯片和定时器芯片,并设计出相应的电路连接图。

确定芯片的引脚连接方式,以及与外部输入输出信号的连接关系。

2、搭建实验电路在数字电路实验箱上,按照设计好的电路原理图,插入相应的芯片和元器件,并使用导线进行连接。

仔细检查电路连接是否正确,确保无短路和断路现象。

3、调试电路接通实验箱电源,使用示波器观察输入信号和输出信号的波形,检查电路是否正常工作。

调整函数信号发生器的输出频率和幅度,观察频率计的测量结果是否准确。

4、记录实验数据在不同的输入信号频率下,记录频率计的测量值,并与函数信号发生器的设定值进行比较。

分析测量误差产生的原因,并尝试采取相应的措施进行改进。

五、实验数据与分析以下是在实验中记录的部分数据:|输入信号频率(Hz)|测量值(Hz)|误差(%)||||||100|98|2||500|495|1||1000|990|1||2000|1980|1|从数据中可以看出,测量值与输入信号的实际频率存在一定的误差。

频率计实验报告(二)

频率计实验报告(二)引言概述:本文是关于频率计实验报告的第二篇。

在上一篇实验报告中,我们介绍了频率计的原理和使用方法。

在本文中,我们将继续讨论频率计的准确性、稳定性以及实验中可能遇到的问题和解决方法。

通过本次实验,我们将深入了解频率计的性能和应用情况。

正文:一、频率计的准确性1. 选择合适的输入信号:合适的输入信号能够提高频率计的准确性。

应根据实际需求选择合适的信号源,例如使用稳定的标准信号源进行校准,或者根据被测信号的特点进行合理选择。

2. 校准频率计:频率计应定期进行校准,确保准确性。

校准过程中需注意输入电平、信号形状等因素对准确性的影响,及时进行调整和校准,提高频率计的准确性。

二、频率计的稳定性1. 加强电源管理:频率计的稳定性与供电电压、电源干扰等因素密切相关。

合理管理电源,选择稳定的供电电压,避免电源波动对频率计稳定性的影响。

2. 提高抗干扰能力:频率计应具备一定的抗干扰能力,可以通过加装滤波器、进行屏蔽等方式减小外部干扰对频率计的影响,提高稳定性。

3. 保持恒温环境:频率计对环境温度敏感,应保持恒温环境,避免温度变化对频率计稳定性的影响。

三、实验中可能遇到的问题及解决方法1. 频率计读数不稳定:可能是由于输入信号波动引起的,可以尝试增加信号源的稳定性或调整信号输入方式。

2. 频率计误差较大:可能是由于输入电平过高或过低导致的,可以通过减小或增大输入信号电平进行调整。

3. 频率计显示故障:可能是由于设备故障引起的,可以检查设备连接是否正常、是否存在损坏等问题,并进行相应维修或更换操作。

四、实验中的注意事项1. 注意输入信号的频率范围:在实验中应选择适合频率范围的输入信号,避免超出频率计的测量范围。

2. 避免过高电压输入:过高的输入电压可能导致频率计损坏或显示异常,需根据设备的额定电压进行输入控制。

3. 防止外界干扰:实验时需注意周围环境的电磁干扰,如尽量远离其他电磁辐射源,以确保测量准确性和稳定性。

频率计的制作实验报告

频率计的制作实验报告实验目的:本实验的目的是通过制作一个简单的频率计,了解频率计的工作原理以及实际应用。

实验仪器与材料:1. 模块化电子实验箱2. 函数信号发生器3. 示波器4. 电压表5. 电阻、电容等基本元件实验原理:频率计是用于测量信号频率的一种仪器。

其基本原理是利用周期性信号的周期长度与频率之间的倒数关系,通过计算周期长度来确定信号的频率。

实验步骤:第一步:搭建电路1. 将函数信号发生器的输出接入电路板上的输入端,作为输入信号源。

2. 将电路板上的元件按照电路图连接,包括电容、电阻等。

确保电路连接正确。

第二步:调试电路1. 将函数信号发生器的频率设置为一个已知的数值,例如1000Hz。

2. 使用示波器测量电路输出端信号的周期长度。

3. 使用计算器计算出信号的频率。

4. 调整电路参数,直到测量到的频率与设定的频率相等。

第三步:验证测量准确性1. 将函数信号发生器的频率调整到其他已知值,例如2000Hz。

2. 重复上述步骤,测量并计算信号的频率。

3. 比较测量到的频率与设定的频率,验证测量准确性。

实验结果与分析:通过实验,我们成功制作了一个简单的频率计。

在调试电路的过程中,我们可以通过测量输出信号的周期长度,并利用频率的倒数与周期长度的关系计算出信号的频率。

通过与设定的频率进行比较,验证了测量的准确性。

实验中可能存在的误差主要来自于电路元件的稳定性以及测量设备的精度。

为了提高测量准确性,可以选择更稳定的元件,并使用更精确的测量设备。

实验结论:本实验通过制作一个简单的频率计,深入了解了频率计的工作原理和实际应用。

通过测量信号的周期长度并计算出频率,我们可以准确地测量信号的频率。

实验结果验证了测量的准确性,并提出了进一步提高准确性的建议。

频率计在电子测量中具有重要的应用价值,可以广泛应用于通信、电子设备维修等领域。

简易频率计实验报告

实验二简易数字频率计实验目的:(1)学会各种简易数字频率计的设计方法(2)学会VHDL的多进程及多层次设计方法实验原理:设计一个四位数字频率计,此频率计共分四档。

一档:0~9999Hz二档:10~99.99kHz三档:100~999.9kHz四档:1~10MHz分频器模块FEN通过对1Hz的时钟的分频得到0.5Hz的时钟信号。

测频模块FTEST,是整个程序的核心,此模块完成在1s的时间内对被测信号计数的功能,并通过输出数据实现自动换挡的功能。

LOCK模块用来锁存数据。

实验内容:在MAX+plusII中用VHDL语言输入FEN2 、MUX21、CD源程序,保存名字与实体名一致,后缀为vhd,选择目标器件为EP1K30TC144-3,然后进行编译、仿真。

参考程序:1、FEN通过对1Hz的时钟的分频得到0.5Hz的时钟信号。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fen ISPORT(clk:IN STD_LOGIC;q:OUT STD_LOGIC);END fen;ARCHITECTURE fen_arc OF fen ISBEGINPROCESS(clk)VARIABLE x:STD_LOGIC;BEGINIF clk'EVENT AND clk='1'THENx:=NOT x;END IF;q<=x;END PROCESS;END fen_arc;波形仿真图:2、FTSET此模块完成在1s的时间内对被测信号计数的功能,并通过输出数据实现自动换挡的功能。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ftest ISPORT(clr,Fx,door:IN STD_LOGIC;alm:OUT STD_LOGIC;q3,q2,q1,q0,dang:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ftest;ARCHITECTURE CORN_ARC OF ftest ISBEGINPROCESS(door,Fx)VARIABLE c0,c1,c2,c3,c4,c5,c6 :STD_LOGIC_VECTOR(3 DOWNTO 0);VARIABLE x:STD_LOGIC;BEGINIF Fx'EVENT AND Fx='1'THENIF door='1'THENIF c0<"1001"THENc0:=c0+1;ELSEc0:="0000";IF c1<"1001"THENc1:=c1+1;ELSEc1:="0000";IF c2<"1001"THENc2:=c2+1;ELSEc2:="0000";IF c3<"1001"THENc3:=c3+1;ELSEc3:="0000";c4:=c4+1;ELSEc4:="0000";IF c5<"1001"THEN c5:=c5+1;ELSEc5:="0000"; IF c6<"1001"THEN c6:=c6+1;ELSEc6:="0000";alm<='1';END IF;END IF;END IF;END IF;END IF;END IF;END IF;ELSEIF clr='0'THENalm<='0';END IF;c6:="0000";c5:="0000";c4:="0000";c3:="0000";c2:="0000";c1:="0000";c0:="0000";END IF;IF c6/="0000"THENq3<=c6;q2<=c5;q1<=c4;q0<=c3;dang<="0100";ELSIF c5/="0000"THEN q3<=c5;q2<=c4;q1<=c3;q0<=c2;dang<="0011";q3<=c4;q2<=c3;q1<=c2;q0<=c1;dang<="0010";ELSEq3<=c3;q2<=c2;q1<=c1;q0<=c0;dang<="0001";END IF;END IF;END PROCESS;END CORN_ARC;波形仿真图:3、LOCK模块LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LOCK ISPORT(A0,A1,A2,A3,A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0);q0,q1,q2,q3,q4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);clk:IN STD_LOGIC);END LOCK;ARCHITECTURE ART OF LOCK ISBEGINPROCESS(clk)BEGINIF(clk'EVENT AND clk='1')THEN q0<=A0;q1<=A1;q2<=A2;q3<=A3;q4<=A4;END IF;END PROCESS;END ART;波形仿真图:顶层仿真波形:实验结果:实现了四位数字频率计的设计。

频率计实验报告频率计实验报告xx011014

频率计实验报告频率计实验报告xx011014 数字逻辑与处理器基础实验三频率计实验实验目的:掌握频率计的原理和设计方法。

实验工具:1 Verilog语言2 Quartus II 9.03 DE2实验板实验设计:1 总体思路以及模块总述设计的基本思路是按照实验指导书上给出的原理图划分模块。

①待测信号产生模块signalinput.v :由指导书给出,用于产生待测信号sigin ;② 1Hz 时钟产生模块clk_1hz.v:通过实验板50MHz 产生1Hz 时钟clk_1hz;③控制信号产生模块control.v :通过1Hz 时钟,产生频率计所需的使能信号en ,同步清零信号reset ,锁存信号la ,生成一个3秒钟的频率计数周期;④十分频模块div_10.v:若量程选择信号sw_2为高电平,则待测信号需进行十分频;⑤计数器模块counter.v :频率计的核心部分,包括四位十进制计数器,以及对应七段译码器的译码器。

这里我把实验指导书中的译码模块整合在了里面,原因是认为在这个设计中单做一个译码模块意义不大,整合在里面翻倒方便一些;⑥信号锁存模块lat.v :当锁存信号la 为高电平时,锁存输出持续显示;⑦顶层模块div.v :进行各分立模块的功能综合;2 模块分述(1) 待测信号产生模块代码:module signalinput(testmode,sysclk,sigin);input [1:0] testmode;//00,01,10,11分别代表4种频率,分别为3125,6250,50,12500Hz ,使用SW1~SW0来控制input sysclk;//系统时钟50Moutput sigin;//输出待测信号reg[20:0] state;reg[20:0] divide;reg sigin;initialbeginsigin=0;state=21"b[***********]000;divide=21"b000000_1111_1010_0000000; endalways@(testmode)begincase(testmode[1:0])2"b00:divide=21"d16000; //3125Hz2"b01:divide=21"d8000; //6250Hz2"b10:divide=21"d1000000; //50Hz2"b11:divide=21"d4000; //12500Hzendcaseendalways@(posedge sysclk)//按divide 分频beginif(state==0)sigin=~sigin;state=state+21"b0_00__0000_0000_0000_0000_10; if(state==divide)state=27"b000_0000_0000_0000_0000_0000_0000; endendmodule可以看出大致由两部分构成:频率选择、分频。

频率计——电子电路实验报告

电子电路实验报告学院(系)电子与信息工程学院专业电子信息工程(中意)学生姓名秦翰学号11523032013 年8 月2日一、数字频率计的原理频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号。

因此数字频率计实际是一个脉冲计数器,即在单位时间里所统计的脉冲个数,所以我们课题研究的主要内容放在计数脉冲电路。

实际应用中测量频率和周期的方法一般可分为无源测频法、有源测频法及计数器法等方法。

计数器法,又分为直接测频法和间接测频法。

(1)直接测频法,即在一定闸门时间内测量被测信号的脉冲个数。

用一标准闸门信号(闸门宽度为T c )对被测信号的重复周期进行计数,计数结果为N x 时,其待测频率为时间T c 为标准闸门宽度(s ),N x 为计数器计出的脉冲个数(重复周期数),测量的精度主要取决于计数N x 的误差。

其特点在于:测量方法简单;待测信号频率越高,精度越高;测量时间越长,误差越小;但当待测信号频率较低时,误差较大。

(2)间接测频法,如周期测频法。

此法是在待测信号的一个周期T x 内,记录标准频率信号变化次数N 0。

这种方法测出的频率是x F =0N /x T (公式2-2) 此法的特点是低频检测时精度高,但高频检测时误差很大。

为了提高T 法高频测量时的精度可通过A 分频使待测信号的周期扩大A 倍。

数字频率计作为数字电路中的一个典型应用,实际的硬件设计用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差、可靠性差。

随着复杂可编程逻辑器件的广泛应用,以EDA 工具作为开发手段,运用VHDL 语言。

将使整个系统大大简化。

提高整体的性能和可靠性。

1.电路的组成及工作原理(1) 电路的组成数字频率计一般都由振荡器、分频器、三级CMOS 反相器、控制器、计数译码器、LED 显示器这几部分组成。

首先晶振信号由振荡器的振荡电路产生一个标准频率信号,经分频器分频得到2Hz 的控制脉冲。

实验报告_频率计

实验报告_频率计数字逻辑与处理器基础实验频率计实验报告姓名:学号:2012011250班级:组号:S2⽬录实验⼋:频率计 (3)⼀、实验⽬的 (3)⼆、实验内容 (3)(⼀) 设计⽅案 (3)1. 待测信号产⽣模块 (3)2. 分频模块 (4)3. 计数器模块 (4)4. 16位锁存器模块 (5)5. 控制信号产⽣模块 (6)6. 译码模块 (7)7. 扫描模块 (8)(⼆) 仿真结果 (9)(三) 实验硬件调试 (10)1. ⾯积与速度的关系清单 (10)2. 综合电路图 (12)3. 实验调试结果 (12)三、实验总结 (13)实验⼋:频率计⼀、实验⽬的掌握频率计的原理和设计⽅法⼆、实验内容(⼀)设计⽅案频率计⽤于对⼀个未知频率的周期信号进⾏频率测量,在1s内对信号周期进⾏计数,即为此周期信号的频率。

频率计内部实现框图如下所⽰,其内部包括频率量程处理模块(10 分频)、时钟频率产⽣模块、控制信号产⽣模块、⼗进制计数器模块、锁存器模块、译码显⽰模块等。

下⾯对⼏个模块分别作出阐释。

1.待测信号产⽣模块系统时钟信号为100MHz,利⽤不同的分频⽐将系统时钟分成四组不同的待测信号:3125Hz,6250Hz,50Hz,12500Hz。

将以上四组信号作频率计的输⼊。

具体代码如下,代码⽂件为siginput.v2.分频模块产⽣三个不同的分频⽐,其中两个将系统时钟分为1Hz信号和1KHz信号,分别作为计数时钟和扫描时钟;另⼀个分频⽐为10,⽤于⾼量程下的测量。

具体代码如下,代码⽂件为divider.v3.计数器模块这是⼀个四位⼗进制的计数器,当待测信号的上升沿来临,在使能信号enable有效,复位信号reset⽆效时开始计数。

具体代码如下,代码⽂件为counter.v4.16位锁存器模块输⼊为计数器产⽣的16位输出,lock信号(⾼电平)有效时输出锁定,否则,输出透明显⽰计数器值。

具体代码如下,代码⽂件为latch_16bits5.控制信号产⽣模块产⽣计数器的使能信号enable(⾼电平有效)、复位清零信号reset(低电平有效)以及锁存器的锁存信号lock(⾼电平锁存,低电平透明输出)。

数字频率计实验报告

电工电子课程设计——数字频率计学生姓名陈卓学号1302060413专业通信工程班级0605指导教师宋学瑞目录第一章技术指标…………………………………………………………第二章整体方案设计…………………………………………………第三章单元电路设计…………………………………………………第四章测试与调整……………………………………………………第五章设计小结………………………………………………………第一章技术指标一.整体功能要求频率计主要用于测量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。

其扩展功能可以测量信号的周期。

二.系统结构要求数字频率计的整体结构要求如图所示。

图中被测信号为外部信号,送入测量电路进行处理、测量,档位转换用于选择测试的项目------频率、周期,若测量频率则自动分档。

数字频率计整体方案结构方框图三、电气指标被测信号波形:正弦波和矩形波。

输入信号电压:0.5~5V测量范围:0~9999Hz和1~100kHz脉冲周期测量范围:100μS~1S具有超量程声、光报警功能显示4位有效数字测量误差小于5%可供选择的元器件见附录第二章整体方案设计现代测量技术及仪器以数字化和智能化为主要发展方向。

数字式时频测量仪器很符合这样的方向。

频率量是几乎不经转换就能得到的数字量,在数字频率计中,被测信号是以脉冲信号方法来传递、控制和计数的,易于做成智能化设备。

数字频率计的基本工作原理是以适当的逻辑电路,使电子计数器在预定的标准时间内累计待测输入信号的脉冲个数,实现频率测量。

频率就是指周期性信号在单位时间内重复出现的次数。

若在一定的时间间隔T内计得这个周期性信号的重复次数N,则其频率可表达为:f=N/T由于计数器可以严格按照上式所表达的频率的定义进行测量,对于上式来说,要测量某个周期现象的频率,就必须解决计数和时间标准问题。

测量方案应至少包括两个部分,即计数部分和时基选择部分。

数字频率计的原理框图如下所示:图A、数字频率计测频原理数字频率计的原理框图如图A所示,从中可以看出测量过程。

数字频率计的设计实验报告

数字频率计的设计实验报告实验名称:数字频率计的设计实验日期:2021年7月1日实验目的:设计并实现一个基于计数器的数字频率计,使用计数器测量输入信号的频率,并将结果显示在数码管上。

实验器材:FPGA开发板、数字频率计模块、计数器模块、数码管模块。

实验原理:1. 计数器模块设计一个计数器模块,用于计数示波器输入脉冲信号的时间。

计数器的计数时间可以根据需要进行调整。

2. 数字频率计模块设计一个数字频率计模块,用于将计数器的计数时间转换为输入信号的频率。

通过计算计数器的计数值来计算频率,并将结果显示在数码管上。

3. 数码管模块设计一个数码管模块,用于将数字频率计模块计算出的频率值转换为可以在数码管上显示的数码。

实验步骤:1. 搭建实验电路将FPGA开发板连接到计数器模块、数字频率计模块和数码管模块。

2. 编写Verilog代码根据上述原理,编写计数器模块、数字频率计模块和数码管模块的Verilog代码。

3. 编译代码并下载到FPGA开发板使用Xilinx Vivado软件将Verilog代码编译成比特流文件,并将比特流文件下载到FPGA开发板中。

4. 测试实验将示波器的输出信号连接到数字频率计的输入端,并将数字频率计连接到数码管。

通过计算数字频率计的输出,验证数字频率计的测量准确性。

实验结果:经过测试,数字频率计的测量准确度在实验误差范围内。

输入不同频率的信号时,数码管能够正确显示频率值。

实验总结:通过本次实验,成功设计并实现了一个基于计数器的数字频率计。

该实验不仅巩固了计数器、数码管等模块的设计知识,也提高了学生的Verilog编程能力。

在实验中,学生还学习了如何使用FPGA开发板进行数字电路实验,以及测试和验证数字电路的方法和技巧。

频率计实验报告1

简易的数字频率计实验报告逻辑与数字系统设计——实验部分作者姓名班级学号一、实验目的1.学习数字系统设计的步骤和方法;2.学习QUARTUS II的编译环境,和VHDL编程语言;3.熟悉ALTERA公司的MAX7000S系列的使用及程序下载方法;二、实验内容本实验要求设计并实现简易的数字频率计电路,要求可以实现以下功能:(1) 频率计的频率测量范围:最低要求0~9999Hz。

(2) 闸门时间为1s,测量结果以十进制数字显示。

(3) 设计一位复位键,对频率计进行清零复位。

(4) 利用实验箱上的四个七段数码管显示频率计结果,要求显示结果稳定,无闪烁。

三、实验任务1. 设计频率计的原理图,完成频率计子模块的功能设计;2. 在QUARTUS II环境下,建立新工程文件;3. 新建VHDL文件,完成各个子模块的VHDL编程,并利用QuartusII的工具生成相应的原理图文件;4. 在QUARTUS II环境下,新建原理图文件(注意:原理图文件名应与新建的工程文件名相同),完成各个模块之间的电路连接;5. 电路的功能仿真,验证设计的正确性;6. 为电路分配输入输出引脚,生成.pof文件;6. 下载.pof文件到MAX7128SL84-15;7. 连接MAX7128SL84-15与实验箱,并利用信号发生器和示波器检验频率计是否正常工作并测试频率计的相对误差;8. 撰写实验报告。

四、考核方法实验成绩由三个部分组成:考核内容所占分值频率计设计合理,编译通过,功能仿真结果正确30分程序可以正常下载,连接实验箱后频率计能够正常工作30分频率计工作稳定性好,误差小,测量范围广(1.2MHz以上)10分实验报告内容详实,叙述准确30分五、实验原理5.1 Max7000S系列开发板简介MAX7000系列是高密度,高性能的CMOS CPLD,采用先进的0.8um CMOS E2PROM技术制造。

MAX7000系列提供600-5000个可用门,引线端子到引线端子的延时为6ns。

频率计实验报告

频率计实验报告专业电子信息工程姓名学号姓名学号姓名学号指导教师设计时间目录引言 .............................................................................................. - 3 - 第一章频率计概述........................................................................ - 3 -1.1数字频率计概述.................................................................. - 3 -1.2频率计设计要求.................................................................. - 4 - 第二章频率计方案设计 ................................................................ - 4 -2.1 方案比较............................................................................ - 4 -2.1.1方案一:单片机频率计(基于A T89S52) ....................... - 4 -2.1.2方案二:CPLD频率计(基于VHDL语言).............. - 5 -2.2方案选择............................................................................. - 6 - 第三章CPLD频率计总体设计 ..................................................... - 6 -3.1 测频的方法 ........................................................................ - 6 -3.2 记数器法测频原理............................................................. - 7 -3.3 设计实现............................................................................ - 7 -3.3.1总体方案...................................................................... - 7 -3.3.2设计的实现 .................................................................. - 8 -3.3.3 VHDL语言编写的程序................................................ - 9 -3.3.4编译与仿真 ................................................................ - 14 -3.3.5程序加载至单片机........................... 错误!未定义书签。

课程设计实验报告(简易频率计)

实验二:简易电子琴一、实验目的(1)学习采用状态机方法设计时序逻辑电路。

(2)掌握ispLEVER 软件的使用方法。

(3)掌握用VHDL 语言设计数字逻辑电路。

(4)掌握ISP 器件的使用。

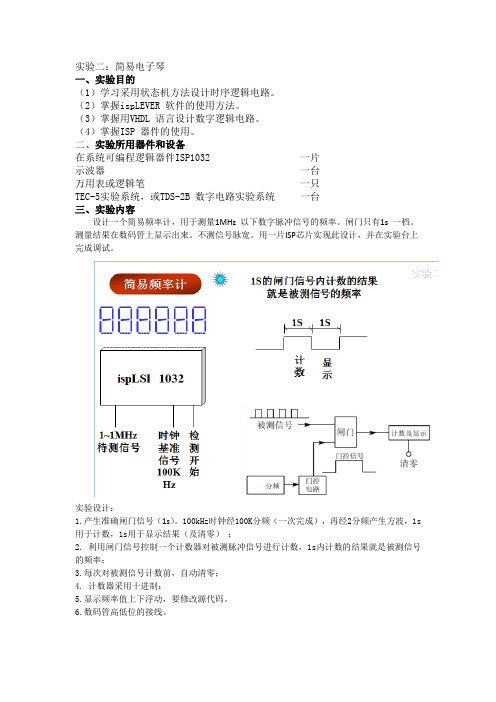

二、实验所用器件和设备在系统可编程逻辑器件ISP1032一片示波器一台万用表或逻辑笔一只TEC-5实验系统,或TDS-2B 数字电路实验系统一台三、实验内容设计一个简易频率计,用于测量1MHz 以下数字脉冲信号的频率。

闸门只有1s 一档。

测量结果在数码管上显示出来。

不测信号脉宽。

用一片ISP芯片实现此设计,并在实验台上完成调试。

实验设计:1.产生准确闸门信号(1s)。

100kHz时钟经100K分频(一次完成),再经2分频产生方波,1s 用于计数,1s用于显示结果(及清零);2. 利用闸门信号控制一个计数器对被测脉冲信号进行计数, 1s内计数的结果就是被测信号的频率;3.每次对被测信号计数前,自动清零;4. 计数器采用十进制;5.显示频率值上下浮动,要修改源代码。

6.数码管高低位的接线。

VHDL源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity fget isport(clk:in std_logic; --输入时钟源 bclk:in std_logic;kout:out std_logic_vector(26 downto 0));end fget;architecture top of fget iscomponent divideport(clk1:in std_logic;cl:out std_logic;co:out std_logic;ro:out std_logic);end component;component gateport(bc1:in std_logic;cl1:in std_logic;co1:in std_logic;op:out std_logic_vector(26 downto 0));end component;component saveport(op1:in std_logic_vector(26 downto 0);ro1:in std_logic;eout:out std_logic_vector(26 downto 0));end component;signal scl:std_logic;signal sco:std_logic;signal sro:std_logic;signal sop:std_logic_vector(26 downto 0);BEGINu1:divide PORT MAP(clk,scl,sco,sro);u2:gate PORT MAP(bclk,scl,sco,sop);u3:save PORT MAP(sop,sro,kout);end;--闸门模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity gate isport(bc1:in std_logic;cl1:in std_logic;co1:in std_logic;op:out std_logic_vector(26 downto 0) --5个8421,一个七段译码);end;architecture art2 of gate iscomponent cnt10 --十进制计数模块port(clk2:in std_logic;en:in std_logic;--使能端clr:in std_logic;--重置qout:out std_logic_vector(3 downto 0 );cout:out std_logic);end component;component seventranse --七段模块port(clk6:in std_logic_vector(3 downto 0 );op2:out std_logic_vector(6 downto 0 ));end component;signal scout1:std_logic;--输出(十进制)signal scout2:std_logic;signal scout3:std_logic;signal scout4:std_logic;signal scout5:std_logic;signal scout6:std_logic;signal qout1:std_logic_vector(3 downto 0);--8421(下同)signal qout2:std_logic_vector(3 downto 0);signal qout3:std_logic_vector(3 downto 0);signal qout4:std_logic_vector(3 downto 0);signal qout5:std_logic_vector(3 downto 0);signal qout6:std_logic_vector(3 downto 0);signal op2: std_logic_vector(6 downto 0);--七段beginr1:cnt10 PORT MAP(bc1,co1,cl1,qout1,scout1);r2:cnt10 PORT MAP(scout1,co1,cl1,qout2,scout2);r3:cnt10 PORT MAP(scout2,co1,cl1,qout3,scout3);r4:cnt10 PORT MAP(scout3,co1,cl1,qout4,scout4);r5:cnt10 PORT MAP(scout4,co1,cl1,qout5,scout5);r6:cnt10 PORT MAP(scout5,co1,cl1,qout6,scout6);t1:seventranse PORT MAP(qout6,op2);process(co1)beginif (co1'event and co1='0') thenop<=op2&qout5&qout4&qout3&qout2&qout1;--结果显示end if;end process;end;--寄存器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity save isport(op1:in std_logic_vector(26 downto 0);ro1:in std_logic;eout:out std_logic_vector(26 downto 0));end entity;architecture art4 of save issignal temp:std_logic_vector(26 downto 0);beginprocess(ro1)beginif ro1'event and ro1='1'then --上升沿判断temp<=op1;end if;eout<=temp;end process;end art4;--十进制计数器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity cnt10 isport(clk2:in std_logic;en:in std_logic;clr:in std_logic;qout:out std_logic_vector(3 downto 0 );cout:out std_logic);end entity;architecture art3 of cnt10 issignal temp:std_logic_vector(3 downto 0 );beginprocess(clk2,en,clr)beginif (clr='1') then --重置时清0temp<="0000";elsif (en='1') thenif(clk2'event and clk2='1')then --上升沿判断进位if(temp="1001")thentemp<="0000";elsetemp<=temp+1;end if;end if;end if;end process;qout<=temp;cout<='1' when temp="1001" else '0';end art3;--分频模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity divide isport(clk1:in std_logic;cl:out std_logic;co:out std_logic;ro:out std_logic);end;architecture art1 of divide issignal preclk:std_logic;signal temp1:std_logic;signal temp2:std_logic;beginp1: process(clk1) --先进行2500分频variable count:integer range 0 to 2500;beginif clk1'event and clk1='1'thenif count=2499 thencount:=0;preclk<='1';else count:=count+1;preclk<='0';end if;end if;end process;p2: process(preclk) --依次二分频实现闸门beginif preclk'event and preclk='1'thentemp2<=not temp2;end if;end process;p3: process(temp2)variable count2:std_logic;beginif temp2'event and temp2='1'thencount2:=not count2;if count2='1'thenco<='1';temp1<='0';else co<='0';temp1<='1';end if;end if;end process;p4:process(temp2)beginif (temp1='1' and temp2='0') thencl<='1';elsecl<='0';end if;end process;ro<=temp1;end;--七段译码器模块library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity seventranse isport(clk6:in std_logic_vector(3 downto 0 );op2:out std_logic_vector(6 downto 0 ));end entity;architecture art5 of seventranse isbeginprocess(clk6)begincase clk6 iswhen "0000"=> op2<="1111110";when "0001"=> op2<="0110000";when "0010"=> op2<="1101101";when "0011"=> op2<="1111001";when "0100"=> op2<="0110011";when "0101"=> op2<="1011011";when "0110"=> op2<="1011111";when "0111"=> op2<="1110000";when others=> op2<="0000000";end case;end process;end art5;四、实验小结:实验要求用闸门信号控制计数器计时,于是在十进制计数器模块中添加使能信号en(en=‘1’计数器进行加1 计数,en=‘0’时计数器保持),将闸门信号作为使能信号接入,即可实现1s计数,1s显示。

数字频率计设计实验报告

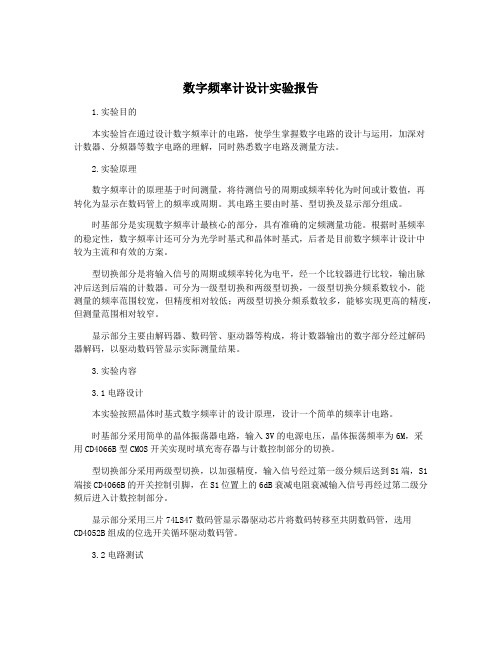

数字频率计设计实验报告1.实验目的本实验旨在通过设计数字频率计的电路,使学生掌握数字电路的设计与运用,加深对计数器、分频器等数字电路的理解,同时熟悉数字电路及测量方法。

2.实验原理数字频率计的原理基于时间测量,将待测信号的周期或频率转化为时间或计数值,再转化为显示在数码管上的频率或周期。

其电路主要由时基、型切换及显示部分组成。

时基部分是实现数字频率计最核心的部分,具有准确的定频测量功能。

根据时基频率的稳定性,数字频率计还可分为光学时基式和晶体时基式,后者是目前数字频率计设计中较为主流和有效的方案。

型切换部分是将输入信号的周期或频率转化为电平,经一个比较器进行比较,输出脉冲后送到后端的计数器。

可分为一级型切换和两级型切换,一级型切换分频系数较小,能测量的频率范围较宽,但精度相对较低;两级型切换分频系数较多,能够实现更高的精度,但测量范围相对较窄。

显示部分主要由解码器、数码管、驱动器等构成,将计数器输出的数字部分经过解码器解码,以驱动数码管显示实际测量结果。

3.实验内容3.1电路设计本实验按照晶体时基式数字频率计的设计原理,设计一个简单的频率计电路。

时基部分采用简单的晶体振荡器电路,输入3V的电源电压,晶体振荡频率为6M,采用CD4066B型CMOS开关实现时填充寄存器与计数控制部分的切换。

型切换部分采用两级型切换,以加强精度,输入信号经过第一级分频后送到S1端,S1端接CD4066B的开关控制引脚,在S1位置上的6dB衰减电阻衰减输入信号再经过第二级分频后进入计数控制部分。

显示部分采用三片74LS47数码管显示器驱动芯片将数码转移至共阴数码管,选用CD4052B组成的位选开关循环驱动数码管。

3.2电路测试将方法频率计电路搭建完成后,接通电源,输入300Hz、3kHz、30kHz和300kHz的信号,观察数码管的测量结果。

并与示波器进行对比,计算相对误差。

4.实验结果通过实验测试,本设计可以稳定地测量300Hz至300kHz范围内的信号频率,并且测量误差相对较小。

频率计实验报告

频次计真验报告之阳早格格创做一,真验脚段1. 应用AT89S52单片机、单片机的I/O端心中扩启动器74HC573战74HC138、LED数码管动向隐现等真止对付中部旗号频次举止准确计数的安排.二,真验央供A.基础央供:使用单片机的定时器/计数器功能,安排频次丈量拆置.(1)当被测频次fx<100Hz时,采与测周法,隐现频次XXX.XXX;当被测频次fx>100Hz时,采与测频法,隐现频次XXXXXX.(2)利用键盘分段丈量战自动分段丈量.(3)完毕单脉冲丈量,输进脉冲宽度范畴是100µs-0.1s. B.扩展部分:三,真验基根源基本理以单片机AT89S52为核心,利用单片机AT89S52的计数/定时器(T1战T0)的功能去真止频次的计数,而且利用单片机的动向扫描把测出的数据支到数字隐现电路隐现.利用7SEG-MPX8-CC-BLUE共阳极数码管,隐现电路共由六位共阳极数码管组成,总体本理框图如图1.1所示.图1.1 总体安排框图测频本理丈量频次有测周法战测频法二种.如图2.2战图2.3所示图1.2测周法 图1.3测频法(1)测频法(T 法):通过丈量脉冲宽度去决定频次,适用于下频.(2)测周法(M 法):是计数器正在一定时间内对付速度的脉冲数,决定频次,适用于矮频.四,真验安排分解针对付要真止的功能,采与AT89S52单片机举止安排,AT89S52单片机是一款矮功耗,下本能CMOS8位单片机,片内含8KB正在线可编程(ISP)的可反复揩写1000次的Flash只读步调保存器,器件采与下稀度、非易得性保存技能制制,兼容尺度MCS- 52指令系统及80C52引足结构.那样,既能搞到经济合理又能真止预期的功能.正在步调圆里,采与分块安排的要收,那样既减小了编程易度、使步调易于明白,又能便于增加各项功能.延时步调等.使用那种要收,关键正在于各模块的兼容战协共,若各模块出有匹配会出现意念出有到的过得.最先,正在编程之前必须相识硬件结构越收是各引足的用法,以及里里寄存器、保存单元的用法,可则,编程无从下脚,电路也无法安排.那是前期准备处事.第二部分是硬件部分:依据念要的功能分块安排安排,比圆输进需要开关电路,输出需要隐现启动电路战数码管电路等.第三部分是硬件部分:先教习明白汇编谈话的编程要收再根据安排的硬件电路举止分块的编程调试,最后完毕步调安排.第四部分是硬件画图部分:安排佳电路后举止画图,包罗电路图战仿真图的画制.第五部分是硬件仿真部分:硬硬件安排佳后将硬件载进芯片中举止仿真,仿真无法完毕时查看硬件步调战硬件电路并举止建改曲到仿真乐成.第六部分是硬件真止部分:连交电路并导进步调查看电路,若与安排的真足一般普遍能真止念要的功能.末尾举止功能扩展,正在已经精确的安排前提上,增加特殊的功能!五,真验央供真止1. 真足安排此次安排主假如应用单片机去安排频次计,硬件部分主要分以下电路模块:隐现电路用8个共阳数码管隐现频次,通过动向扫描举止隐现,进而预防了译码器的使用,共时俭朴了I/0端心,使电路越收简朴.单片机采与AT89S52系列,那种单片机应用简朴,切合频次计安排.电路的总体安排框架如下:2..以下为输进部分样例:正在本真验中主要用用P3心输进按键旗号,还用到了特殊的P0心.对付于P0心,由于其存留下阻状态,为了真止开关功能,给其增加上推电阻,简曲如下图所示:2.2 输出部分本电路的输出旗号为8段共阳极数码管的位选战段选旗号.本真验的数码管是共阳的(为了预防段选旗号出有克出有及启动数码管,故正在P1心连交上推电阻后,再支段选旗号,以普及启动,图中已画出),位选旗号曲交从P2心交进,如下图:各模块拼交推拢,电路总体安排图如下:B.1 步调总体安排本真验用汇编步调完毕.步调总的过程图如下:分散电路图,步调安排的真足思路为:频次计开初处事大概者完毕一次频次丈量,系统硬件皆举止丈量初初化.丈量初初化模块树坐堆栈指针(SP)、处事寄存器、中断统制战定时/计数器的处事办法.定时/计数器的处事最先被树坐为计数器办法,即用去丈量旗号频次.最先定时/计数器的计数寄存器浑0,运止统制位TR 置1,开用对付待测旗号的计数.计数闸门由硬件延时步调真止,从计数闸门的最小值(即丈量频次的下量程)开初丈量,计数闸门中断时TR浑0,停止计数.计数寄存器中的数值通过数制变换步调从十六进制数变换为十进制数.推断该数的最下位,若该位出有为0,谦足丈量数据灵验位数的央供,丈量值战量程疑息所有支到隐现模块;若该位为0,将计数闸门的宽度夸大10倍,沉新对付待测旗号的计数,曲到谦足丈量数据灵验位数的央供.定时/计数器的处事被树坐为定时器办法,定时/计数器的计数寄存器浑0,正在推断待测旗号的上跳沿到去后,运止统制位TR置为1,以单片机处事周期为单位举止计数,曲至旗号的下跳沿到去,运止统制位TR浑0,停止计数.系统硬件安排采与模块化安排要收.所有系统由初初化模块,旗号频次丈量模块,自动量程变换战隐现模块等模块组成.系统硬件过程图如上图所示.B.2 步调主要模块B中断服务子步调T0中断服务子步调过程如图4.2所示.测频时,定时器T0处事正在定时办法,屡屡定时50mS ,则T0中断20次正佳为1秒,即T0用去爆收尺度秒旗号.定时器T1用做计数器,对付待测旗号计数,每秒钟的开初开用T1 ,每秒钟的中断关关T1 .B.2.2 隐现子步调安排隐现子步调将存搁正在隐现慢冲区的频次大概周期值支往数码管上隐现出去,由于所有6位数码管的8根段选线图4.2 T0中断服务子步调 图4.3 T1中断服务子步调并联正在所有由单片机的P0心启动74HC573统制,果此,正在每一瞬间6位数码管会隐现相共的字符,要念每位隐现分歧的字符便必须采与扫描要收轮流面明诸位数码管,即正在每一瞬间只面明某一位隐现字符,正在此瞬间,段选统制心P0输出相映字符.由AT89S52单片机P2.0-P2.2心启动74HC138逐位轮流面明各个数码管,每位脆持1mS ,正在10mS~20mS 之内再面明一次,沉复出有止,利用人的视角久留,佳像6 位数码管共时面明.数码管隐现子步调过程如图所示.图4.4 隐现子步调过程图B量程变换步调使用定时要收真止频次丈量时,中部的待测旗号通过频次计的预处理电路形成宽度等于待测旗号周期的圆波,该圆波共样加至定时/计数器的输进足.处事下电仄是可加至定时/计数器的输进足;当判决下电仄加至定时/计数器的输进足,运止统制位TR置1,开用定时/计数器对付单片机的呆板周期的计数,共时检测圆波下电仄是可中断;当判决下电仄中断时TR浑0,停止计数,而后从计数寄存器读出丈量数据.由隐现电路隐现丈量截止,根据丈量截止推断,举止频次计比较后,举止档位的自动切换,简曲档位自动切换过程图如图所示.图4.5 档位自动切换过程图C. 步调调试及仿真本步调通过Keil单片机开垦仄台真止步调的编译,链交,死成HEX文献.步调再编译历程中不妨创制错位,并即时改正,正在安排时非常要害,使过得被消除正在摇篮中.通过Keil战硬件仿真仄台Proteus的共同,不妨将安排效验仿真出去,根据效验,有脚段的改变安排,劣化步调.c.1 利用Keil硬件真验历程截图:1,建一个工程,并设定与Proteus仿真相关的参数2,编译步调,并死成HEX文献利用Proteus仿真正在验历程截图:1.大于110Hz 测频法调用XXXXXX档2.小于110Hz 测周法调用XXX.XXX档惟有通过亲自试验,动脚去搞,才搞真真掌握那些知识,也让尔对付往日教习的模电知识有了局里的明白.通过那次单片机课程安排,尔从一个单片机试验的门中汉,已经越降为略知一二的新脚.虽然另有很多有关单片机的应用有待教习,然而万变出有离其宗,只消深进相识单片的本理,局部知识面,各个细节,十足安排皆有大概.出有明白要问问共教,更要教会上钩找资料,普遍网上的步调什么的皆出有成能切合央供,然而是不妨教习细节圆里,真止要收,战主要思维.搞真验时另有一个感觉,便是决断要搞了,便要下刻意坐马开初,出有要道尔先上会网、瞅会视频什么的,如果那样搞的话,很大概交下去什么真验皆出钻研,浪费了一下午.搞事要有刻意,千万于出有要偷懒,本去加进搞真验的话仍旧很蓄意义.真验中逢到了很多问题,交下去归纳一下,共共探讨.本次安排用到的主要芯片是AT89S52.单片机用到的是P0心、P1心战P2心,P0心必须交上推电阻,5v供电电压;通过此次安排,尔知讲了鉴于单片机的数字频次计数器的处事过程,并自教了protel硬件的使用要收.收会单片机的使用,模电知识的应用,天然,最大的支获是测验考查自决教习,自决查资料,那对付以去的很多教习、特地是处事有很大的助闲,也算是一个经历吧.以下为简曲真止步调段:#include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned long int//tab1 段选;tab2 位选;tab3 戴小数面的段选uchar codetab1[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};uchar codetab2[]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f};uchar codetab3[]={0xbf,0x86,0xdb,0xcf,0xe6,0xed,0xfd,0x87,0xff,0xef};ulong num,t1,temp;//uchar ;bit mode=0,autoo=1;//mode模式,0测频法,1测周法,autoo表示脚动安排仍旧自动安排void delay(uchar);//延时函数声明void display(ulong); //隐现函数声明void init();//初初化函数声明/***********主函数*****************/void main(){init();//调用初初化函数while(1){if(P2==0xee)//第一个键被按下,采用脚动模式仍旧自动模式{while(P2==0xee);autoo=!autoo;}if(autoo==0)//脚动模式{if(P2==0xed)//第二个键被按下,采用测频法仍旧测周法{while(P2==0xed);mode=!mode;//切换测频次模式temp=0;t1=0;if(mode==0)//模式0,开开定时器1{ET1=1;TR1=1;}else//模式1,关关定时器1{ET1=0;TR1=0;}}}display(num);}}/*********初初化函数*********/void init(){TMOD=0x10;//定时器1采用为模式1EA=1; //开总中断EX0=1;//开中部中断0IT0=1;//下落沿触收ET1=1;//开定时器1中断TR1=1;//定时器1开初处事TH1=(65536-50000)/256; //树坐下八位的初值TL1=(65536-50000)%256; //树坐矮八位的初值P2=0xef;}/***********隐现函数*************/void display(ulong n){uchar qw,bw,sw,wan,qian,bai,shi,ge; //分别表示千万位、百万位...qw = n/10000000;//得到千万位的数字bw = n/1000000%10;//得到百万位的数字sw = n/100000%10;wan = n/10000%10;qian= n/1000%10;bai = n/100%10;shi = n/10%10;ge = n%10;P0=tab2[0];//隐现千万位P1=tab1[qw];delay(1);P0=tab2[1];//隐现百万位P1=tab1[bw];delay(1);P0=tab2[2];//隐现十万位P1=tab1[sw];delay(1);P0=tab2[3];//隐现万位P1=tab1[wan];delay(1);if(mode==1)//测周法{P0=tab2[4];P1=tab3[qian]; //千位戴小数面隐现delay(1);}else{P0=tab2[4];P1=tab1[qian];//测频法千位出有戴小数面隐现delay(1);}P0=tab2[5];//隐现百位P1=tab1[bai];delay(1);P0=tab2[6];//隐现十位P1=tab1[shi];delay(1);P0=tab2[7];//隐现个位P1=tab1[ge];delay(1);}/***********延时函数****************/ void delay(uchar z){uchar x,y;for(x=0;x<z;x++)//延时约1msfor(y=0;y<110;y++);}/*********中部中断0函数***********/void exter0() interrupt 0{if(mode==1){if(temp==1){TH1=(65536-1000)/256;TL1=(65536-1000)%256;ET1=1;TR1=1;t1=0;}if(temp==5) //计数为4{num=4000000/t1;//num为频次的1000倍,那样可有三位小数temp=0;ET1=0; //关关定时器1中断TR1=0; //停止定时器1if(autoo==1) //可自动安排{if(num>=110000){mode=0;ET1=1;//开开定时器1中断TR1=1;//定时器1开初处事}}}}temp++;}/*************定时器1中断函数***********/void t1time() interrupt 3{if(mode==1){TH1=(65536-1000)/256;TL1=(65536-1000)%256;}t1++;if(mode==0){TH1=(65536-50000)/256; //树坐下八位的初值TL1=(65536-50000)%256; //树坐矮八位的初值if(t1==20) //定时1ms{t1=0; //浑整num=temp; //得到频次if(autoo==1) //自动安排模式{if(num<110) //频次小于110Hz,采用测周法{mode=1;ET1=0; //关关定时器1中断TR1=0; //定时器1停止处事}}temp=0; //计数浑整}}}以上便是真验中逢到的主要问题,基础上皆找到了相映的办理之讲.所有真验的历程便是一个办理问题的历程,每天皆办理一些问题,尔的真验也便办理了,天然截止出有要害,功利化的探供截止,会使人暴躁,仍旧享受那份疑易迎刃而解的快感吧!附件:。

频率计实验报告

频率计实验报告姓名: 学号:一、实验目的1.了解频率计的工作原理和实现方法。

2.利用CPLD 和单片机设计制作一台可以测量频率为1Hz~10MHz 信号的频率计,频率精度的基本要求为误差在±1Hz 内,f 为10MHz 时,频率绝对误差不大于1000Hz ;f 小于1000Hz 时,频率绝对误差不大于1Hz 。

3.通过对频率计的程序设计进一步加强对CPLD 和单片机的编程应用能力和电路设计及搭接能力。

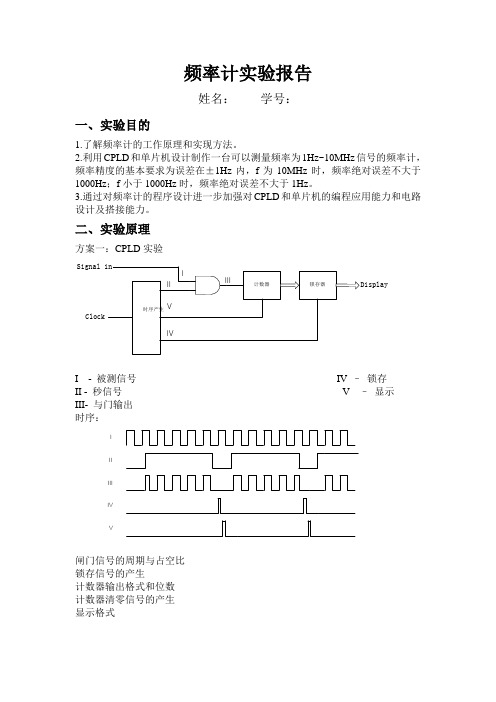

二、实验原理方案一:CPLD 实验I - 被测信号 IV – 锁存 II - 秒信号 V – 显示 III- 与门输出时序:闸门信号的周期与占空比锁存信号的产生计数器输出格式和位数计数器清零信号的产生显示格式计数器时序产生锁存器Signal inClockI II III IV VDisplayI II III IVV方案二:CPLD+单片机由8MHz 的晶振分频至0.8Hz ,作为闸门信号闸门信号:占空比为80%,低电平时间为0.25s ,高电平时间为1s (闸门) 时序与方案1的时序相似,只是锁存器已不存在,无需锁存信号计数器清零信号是在单片机完成读取后给出用选择器的目的在于减少单片机引脚的使用可每次读取一个显示位所对应的数据方案3:CPLD+单片机闸门信号由输入信号同步,因此其时间可变可由闸门时间内输入脉冲出现的数目Ns 和闸门时间内晶振信号脉冲出现的数目Nc 得到输入信号的频率:fs = Ns * fc / Nc适应不同频率的输入信号单片机(或CPLD )感知输入信号的频率范围,并由此调节闸门时间闸门时间的调节必须是在一次完整的计数显示过程后进行无论频率、周期还是时间间隔的数字化测量,均是基于主门加计数器的结构而实现的。

其中主门具有“与门”的逻辑功能。

主门的一个输入端送入的是待检测的信号。

另一端送入的是闸门信号,可以由晶振通过分频得到高电平为1秒,低电平为0.25秒的闸门信号。

其中的1秒钟用于对待测信号的脉冲个数进行检分频链选择器Clock 闸门速度选择触发器计数器计数器选择器选择器Signal in 计数器选择器Signal inClock 分频链单片机Display测,0.25秒则用于传输数据、显示以及计数器的清零。

频率计实验报告

频率计实验报告频率计实验报告引言:频率计是一种用于测量信号频率的仪器。

在电子工程、通信和物理等领域中,频率计被广泛应用于测量和分析各种信号的频率特性。

本实验旨在通过使用频率计来测量不同信号源的频率,并探究其测量精度和适用范围。

实验过程:实验中,我们使用了一台精密频率计和几个不同的信号源。

首先,我们将频率计连接到信号源,并调整频率计的设置以适应不同的信号频率范围。

然后,我们逐个测量每个信号源的频率,并记录下测量结果。

在测量过程中,我们还注意到信号源的幅度对频率计的测量结果是否有影响。

实验结果:通过实验,我们得到了一系列信号源的频率测量结果。

我们发现,在低频范围内,频率计的测量精度较高,能够准确测量信号源的频率。

然而,当信号频率超过一定范围后,频率计的测量精度开始下降,甚至无法准确测量。

这是因为频率计的设计和工作原理决定了其适用范围有限。

进一步分析:在实验中,我们还发现信号源的幅度对频率计的测量结果有一定影响。

当信号幅度较小时,频率计可能无法稳定地测量信号的频率。

这是因为频率计需要足够的信号能量来进行稳定的测量。

因此,在使用频率计进行测量时,我们需要注意信号源的幅度是否满足要求。

实验误差:在实验中,我们还存在一定的测量误差。

这些误差可能来自于频率计本身的精度限制,也可能来自于信号源的不稳定性或其他外界干扰因素。

为了减小误差,我们可以采取一些措施,例如增加测量次数并取平均值,或使用更高精度的频率计。

应用与展望:频率计在现代科学和工程中具有广泛的应用前景。

它可以用于测量和分析各种信号的频率特性,从而帮助我们更好地理解和掌握信号的行为规律。

未来,随着科学技术的不断进步,频率计的测量精度和适用范围将进一步提高,为各个领域的研究和应用提供更多可能性。

结论:通过本次实验,我们深入了解了频率计的工作原理和测量特性。

我们发现频率计在测量低频信号时具有较高的精度,但在高频范围内可能存在测量误差。

同时,我们还注意到信号源的幅度对频率计的测量结果有一定影响。

频率计课程设计实验报告

课程设计报告课程设计名称:电子系统综合课程设计课程设计题目:频率计频率计课程设计实验报告一、设计任务要求1、根本要求:设计一个3位十进制数字显示的数字式频率计,其频率测量范围在1MHz内。

量程分别为10kHz,100kHz和1MHz三档,即最大读数分别为和999kHz。

这里要求量程可以自动转换,详细要求如下:1〕、当读数大于999时,频率计处于超量程状态,此时显示器发出溢出指示〔最高位显示F,其余各位不显示数字〕,下一次测量时,量程自动增大一档。

2〕、当读数小于099时,频率计处于欠量程状态,下一次测量时,量程自动减小一档。

3〕、采用记忆显示方式,即计数过程中不显示数据,待计数过程完毕以后,显示测频结果,并将此显示结果保持到下一次计数完毕,显示时间不小于1s。

4〕、小数点位置随量程变更自动移位。

二、设计方案1、系统功能〔根本功能和附加功能〕根本功能:显示待测频率,LED灯显示小数点,显示待测频率的量程。

附加功能:实现量程自由变化,通过拨码开关控制待测频率大小。

2、系统设计方案说明1、分频模块:由于测频时不同量程档需要不同的时基信号,分频模块是必不可少的。

系统通过试验箱给定的50MHZ的频率通过分频变成0.5HZ,即1秒钟得计数时间,通过1秒钟的记数时间里待测频率上升沿的数量实现频率测定,待测频率通过分频,多路器等实现各频率的测定2 计数模块:想要实现频率的测定,其实就是在1秒钟的计数时间里对待测频率信号上升沿进展计数,所以计数模块是不可缺少的,本计数器需输出指示超量程和欠量程状态的信号。

3 量程控制模块:对待测频率的量程进展判断,确定量程以后,根据不同的量程,在试验箱上显示,我们的设计是4个量程〔1,2,3量程和超量程〕。

:4 BCD译码模块:用到实验箱SOPC上的6个静态共阳数码管中的后三个数码管,并且试验箱内部有译码器,只需要输入4位数就可以在数码管上显示。

三、各模块程序如下:1、分频模块程序:1〕百分频模块程序:module plj(clk,dingshi);input clk;output dingshi;reg [40:0] counter;reg dingshi;always @(posedge clk)beginif (counter==49) //计数时钟上升沿数量,100次时钟周期begin //输出一周期信号,得到100分频信号。

频率计实验报告

频率计实验报告信息工程实验任务及要求:1.设计一个可测量的数字式频率计,测量范围为1Hz-12MHz。

2.用层次化的设计方法设计该电路,编写各个功能模块的程序。

3.仿真各功能模块,通过观察有关波形确认电路设计是否正确4.完成电路设计后,通过在实验系统上下载,验证设计的正确性实验原理分析:根据总的设计图可知:8位十进制数字频率计的设计有一个测频控制信号发生器TESTCTL,8个有时钟使能的十进制数字计数器CNT10,一个32位锁存器REG32B组成。

测频控制信号发生器的设计原理和要求:频率测量的基本原理是计算每秒钟内待测信号的脉冲个数。

这就要求TESTCTL的计数使能信号TSTEN能产生1秒脉宽的周期信号,并对频率计的每一个计数器CNT10的ENA使能端进行不同控制。

当TSTEN高电平时允许计数,低电平时停止计数,并保持所计的数。

在停止计数的期间,首先需要一个锁存信号Load的上跳沿将计数器在前一秒的计数值锁存进32位锁存器REG32B中,且由外部的七段译码器译出并稳定显示。

设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

锁存信号之后,必须有一个清零信号CLR_CNT对计数器进行清零,为下一秒钟的计数操作做准备,测频控制信号发生器的工作时序为周期2秒,占空比为0.5的方波,为了产生的方波,需首先建立一个由D触发器构成的二分频器,在每秒时钟CLK上升沿到来时使其翻转,其中控制信号时钟CLK的频率为1Hz,那么信号TSTEN的脉宽恰好为1秒,可以用作闸门信号,然后根据测频的时序要求,可得出信号Load和CLR_CNT的逻辑描述,在一个计数完成后,即计数使能信号TSTEN在1秒的高电平后,利用其反向值的上升沿产生一个锁存信号Load,0.5秒后,CLR_CNT产生一个清零信号跳沿。

各个模块的源程序如下所示:TESTCTL仿真波形:REG32B仿真波形:分析:设置锁存器的好处是,显示的数据稳定,不会由于周期性的清零信号而不断闪烁。

频率计设计实验报告

频率计设计实验报告频率计设计实验报告智能09012009010993周红蕊一、设计任务设计一个频率计电路,要求有4位十进制数码显示,可测量函数发生器输出的信号频率。

1.可测量9.999KHZ以内的频率并显示。

2.4位数的任意脉冲计数和显示。

3.将灵敏度从100mv提高到5mv。

二、技术要求1. 电源电压:+5V。

2. 输入信号幅度范围:5m v~10 V。

3. 信号输入方式:交流输入。

4. 输入信号波形要求:任意波形周期信号、任意波形脉冲信号。

三、设计器材及仪器1.晶体振荡器。

2.电路芯片(4060、4518、4017、7414、74373、74247)。

3.数码管LA5011。

4.电阻(300、1K、2 K、2M)。

5.电容33pf。

6.稳压电源。

7.信号源。

8.万用表。

9.示波器。

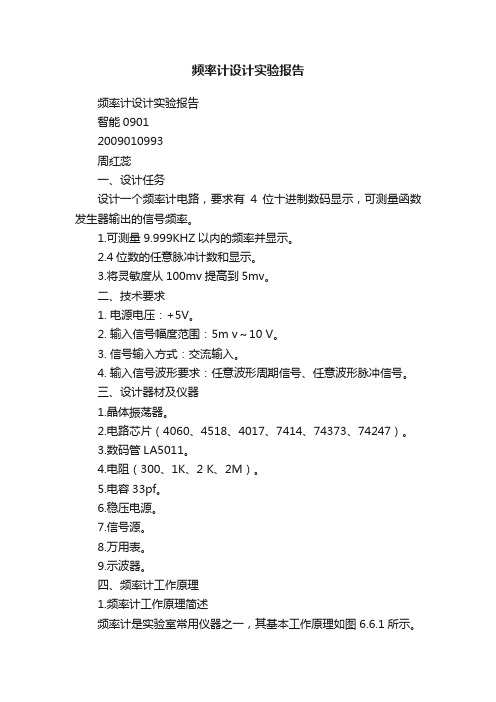

四、频率计工作原理1.频率计工作原理简述频率计是实验室常用仪器之一,其基本工作原理如图6.6.1所示。

首先要有一个稳定而又准确的频率源,用它产生的频率信号经过分频电路后得到标准时间等于一秒的闸门信号,并在闸门信号的后沿由锁存清零控制器产生锁存信号使锁存器锁存数据、产生清零脉冲使计数器清零,以便下一次重新开始计数被测频率信号在闸门开启的一秒钟内可以通过闸门电路进入BCD码计数器进行计数,当闸门信号的后沿到来时计数器停止计数,同时在锁存信号的控制下将计数结果锁存在锁存器中,被锁存的数据经译码驱动电路译码后驱动数码显示电路。

图6.6.1 简易频率计原理框图2.电路分析1)限幅整形电路U i U o频率计的输入信号是各种各样的,既可能有正弦波、矩形波和三角波,也可能有各种周期的、非周期的脉冲波和奇异波。

无论什么波形,要计数准确,起码的条件是信号的信噪比必须足够大。

输入级阻抗要足够高,而且当信号幅度很高时输入级电路不能被烧毁。

因此在信号输入端应有一级高阻输入低噪声前置放大器和限幅器,并且应有一级整形电路,把各种输入信号变成比较规范的矩形波。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字逻辑与处理器基础实验

频率计

实验报告

姓名:

学号:2012011250

班级:

组号:S2

目录

实验八:频率计 (3)

一、实验目的 (3)

二、实验内容 (3)

(一) 设计方案 (3)

1. 待测信号产生模块 (3)

2. 分频模块 (4)

3. 计数器模块 (4)

4. 16位锁存器模块 (5)

5. 控制信号产生模块 (6)

6. 译码模块 (7)

7. 扫描模块 (8)

(二) 仿真结果 (9)

(三) 实验硬件调试 (10)

1. 面积与速度的关系清单 (10)

2. 综合电路图 (12)

3. 实验调试结果 (12)

三、实验总结 (13)

实验八:频率计

一、实验目的

掌握频率计的原理和设计方法

二、实验内容

(一)设计方案

频率计用于对一个未知频率的周期信号进行频率测量,在1s内对信号周期进行计数,即为此周期信号的频率。

频率计内部实现框图如下所示,其内部包括频率量程处理模块(10 分频)、时钟频率产生模块、控制信号产生模块、十进制计数器模块、锁存器模块、译码显示模块等。

下面对几个模块分别作出阐释。

1.待测信号产生模块

系统时钟信号为100MHz,利用不同的分频比将系统时钟分成四组不同的待测信号:3125Hz,6250Hz,50Hz,12500Hz。

将以上四组信号作频率计的输入。

具体代码如下,代码文件为siginput.v

2.分频模块

产生三个不同的分频比,其中两个将系统时钟分为1Hz信号和1KHz信号,分别作为计数时钟和扫描时钟;另一个分频比为10,用于高量程下的测量。

具体代码如下,代码文件为divider.v

3.计数器模块

这是一个四位十进制的计数器,当待测信号的上升沿来临,在使能信号enable有效,复位信号reset无效时开始计数。

具体代码如下,代码文件为counter.v

4.16位锁存器模块

输入为计数器产生的16位输出,lock信号(高电平)有效时输出锁定,否则,输出透明显示计数器值。

具体代码如下,代码文件为latch_16bits

5.控制信号产生模块

产生计数器的使能信号enable(高电平有效)、复位清零信号reset(低电平有效)以及锁存器的锁存信号lock(高电平锁存,低电平透明输出)。

此模块的输入时钟信号,考虑到计数时间问题,没有采用1Hz的counter_clk信号,采用了1KHz的scanning_clk 信号,在时钟的上升沿触发。

故而,计数时要计1000个scanning_clk周期。

每个计数周期(1000个scanning_clk周期),此模块中产生的三个控制信号是一个循环,流程如下:

第一个时钟上升沿到来时

第二个时钟上升沿到来时

复位清零。

第三个时钟上升沿到来时

开始计数。

第1003个时钟上升沿到来时

计数满1000次,停止计数。

第1004个时钟上升沿到来时

锁存器透明输出。

循环上述过程,不断检测待测信号频率

具体代码如下,代码文件为control.v

6.译码模块

搭建七段译码器(本实验要求是八位输出,将小数点位置1即可),对于输入的4bit 数据,该译码器能即时地翻译为相应的数字显示出来。

真值表如下:

具体代码如下,代码文件为segment_4to7.v

7.扫描模块

接下来需要利用上述译码器,结合扫描功能,能让四个数码管显示出给定的四个(不一定相同的)数字。

其中,扫描电路驱动每一位的阳极信号和相应的阴极模式,以高于人眼能察觉的速率不断扫描更新(本实验中为1KHz)。

每一位数字被点亮的时间只有四分之一,但由于眼睛在数字变亮之前感觉不到数字变暗过程,因此感觉数字一直都是亮的。

借助此方法,可以仅用一套数据的输入端口而显示出看起来不同的四个数字。

扫描电路时序关系如下:

具体代码如下,代码文件为scanning_clk

(二)仿真结果

低量程,显示的结果为3125Hz.

低量程,显示的结果为6250Hz

(三)实验硬件调试

1.面积与速度的关系清单

2.综合电路图

3.实验调试结果

经助教验收,实验调试结果正常。

三、实验总结

这是本课程的第一个综合实验,总的来说,难度有点大,耗费时间较多。

该实验的特点是,涉及多个模块,所用到的知识比较综合,比较全面。

我一开始写代码时,先把整个实验分成几个相应的小模块,然后一个一个写,最后综合调试。

但是,我并没有在写完每个模块后分别进行调试,这也导致我最终耗费了大量的时间在debug.开始用modelism仿真时,发现波形不对,于是开始查找代码错误,由于模块太多,根本不知道哪里错了。

就这样一边检查,一边修改,一边调试,可是最后仿真出来的波形还是不对。

再后来,由于仿真太耗时间了,我直接用开发板进行综合调试,综合的结果正确。

但,开发板上的数码管全为0,而且根本就不知道哪里出错了。

没办法,又开始用modelism仿真,这次的仿真一直从下午持续到晚上,我几乎对所有的信号进行了监测,分析,修改,最终,在巨大的努力下,终于调试成功。

最后,只想说,这次实验做得真是不容易……。