多功能数字钟优秀课件

多功能数字钟设计讲义

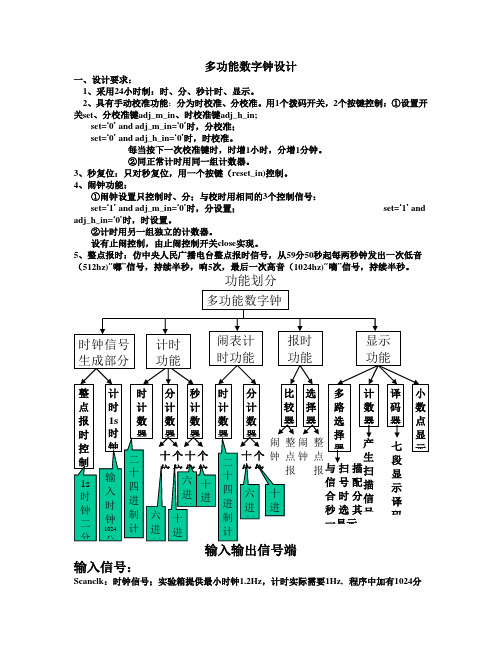

多功能数字钟设计一、设计要求:1、采用24小时制:时、分、秒计时、显示。

2、具有手动校准功能:分为时校准、分校准。

用1个拨码开关,2个按键控制:①设置开关set、分校准键adj_m_in、时校准键adj_h_in;set=‘0’ and adj_m_in=‘0’时,分校准;set=‘0’ and adj_h_in=‘0’时,时校准。

每当按下一次校准键时,时增1小时,分增1分钟。

②同正常计时用同一组计数器。

3、秒复位:只对秒复位,用一个按键(reset_in)控制。

4、闹钟功能:①闹钟设置只控制时、分;与校时用相同的3个控制信号:set=‘1’ and adj_m_in=‘0’时,分设置;set=‘1’ and adj_h_in=‘0’时,时设置。

②计时用另一组独立的计数器。

设有止闹控制,由止闹控制开关close实现。

5、整点报时:仿中央人民广播电台整点报时信号,从59分50秒起每两秒钟发出一次低音(512hz)“嘟”信号,持续半秒,响5次,最后一次高音(1024hz)“嘀”信号,持续半秒。

功能划分输入输出信号端输入信号:Scanclk:时钟信号;实验箱提供最小时钟1.2Hz,计时实际需要1Hz, 程序中加有1024分频,故scanclk频率约为1024Hz。

Set:设置键;设定闹表定时时、分;计时时、分校准;用拨码开关,拨上为定时,拨下为校准。

Reset_in:异步复为信号;只对秒计时复位。

adj_h_in,adj_m_in:时、分校准,闹钟定时控制close:止闹信号;闹钟响后,close为1止闹;用实验箱的拨码开关。

输出信号:scanout::扫描信号;用于顺序点亮6个数码管。

(用1—6位)led_out:七段数码管段码;高位为g。

sound_out:声音输出接喇叭或峰鸣器。

point_out:数码管间的点;隔两个数码管点亮一个。

功能描述通用计数器:LIBRARY ieee;USE ieee.std_logic_1164.all;USE ieee.std_logic_unsigned.all;ENTITY counter ISGENERIC( count_value: INTEGER:=9);PORT(clk,clr,en: IN STD_LOGIC;co : OUT STD_LOGIC;count : OUT INTEGER RANGE 0 TO count_value);END counter;ARCHITECTURE a OF counter ISSIGNAL cnt: INTEGER RANGE 0 TO count_value;BEGINPROCESS (clk,clr)BEGINIF clr = '1' THEN cnt <= 0;ELSIF (clk'EVENT AND clk = '1') THENIF en = '1' THENIF cnt = count_value THEN cnt <= 0;ELSE cnt <= cnt + 1;END IF;END IF;END IF;END PROCESS;co<= '1' when cnt = count_value else '0';count <= cnt;END a;数字钟的实体说明部分LIBRARY ieee;USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all;entity TIMER is PORT(scanclk,reset_in,adj_h_in,adj_m_in,set,close: in std_logic; led_out: out std_logic_vector(6 downto 0); scan_out: out integer range 0 to 5; sound_out: out std_logic; point_out: out std_logic ); end entity;㈠时钟信号生成功能部分signal clk1s: std_logic; --1s 计数时钟 signal cnt: std_logic_vector( 9 downto 0); signal dy : std_logic; --整点报时控制时钟 generat_1s_clock: PROCESS (scanclk) BEGIN IF (scanclk'EVENT AND scanclk = '1') THEN cnt <= cnt + 1; END IF; clk1s <= cnt(9); --scanclk 1024分频 END PROCESS;PROCESS (clk1s,reset) BEGIN IF reset = '1' THEN dy<='0'; ELSIF (clk1s'EVENT AND clk1s = '1') THENLIBRARY ieee;USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all;entity TIMER is PORT(scanclk,reset_in,adj_h_in,adj_m_in,set,close: in std_logic; led_out: out std_logic_vector(6 downto 0); scan_out: out integer range 0 to 5; sound_out: out std_logic; point_out: out std_logic ); end entity;architecture rtl of TIMER isBegindy <= not dy; --clk1s 2分频END IF;END PROCESS;㈡计时功能(用元件例化语句实现)㈡计时功能(用元件例化语句实现)signal reset ,adj_h,adj_m: std_logic;signal c_sh_en, c_ml_en, c_mh_en, c_h_en : std_logic;signal c_h_en1, c_ml_en1 , c_mh_en1 : std_logic;signal enable,disable: std_logic;signal sl,c_ml: integer range 0 to 9;signal c_mh, sh: integer range 0 to 5;signal c_h: integer range 0 to 23;component counter ISGENERIC( count_value: INTEGER);PORT(clk,clr,en : IN STD_LOGIC;co : OUT STD_LOGIC;count : OUT INTEGER RANGE 0 TO count_value);END component;元件例化reset<=not reset_in; --reset_in为按钮输入,通用计数器clr位‘1’状态有效adj_m<=not adj_m_in;adj_h<=not adj_h_in;enable<='1';disable<=‘0’; --用于不需要复位元件的clr端c_ml_en <= (not set and adj_m) or (c_ml_en1 and c_sh_en);c_mh_en <= (c_mh_en1 and c_ml_en);c_h_en <= (not set and adj_h) or (c_sh_en and c_ml_en1 and c_mh_en1 and c_h_en1); CNT1S: countergeneric map( count_value => 9)port map(clk=>clk1s,clr=>reset,en=>enable,co=>c_sh_en,count=>sl);CNT10S: countergeneric map( count_value => 5)port map(clk=>clk1s,clr=>reset,en=>c_sh_en,co=>c_ml_en1,count=>sh);CNT1M: countergeneric map( count_value => 9)port map(clk=>clk1s,clr=>disable,en=>c_ml_en,co=>c_mh_en1,count=>c_ml);CNT10M: countergeneric map( count_value => 5)port map(clk=>clk1s,clr=>disable,en=>c_mh_en,co=>c_h_en1,count=>c_mh);CNT_H: countergeneric map( count_value => 23)port map(clk=>clk1s,clr=>disable,en=>c_h_en,count=>c_h);㈢闹表计时功能描述signal s_ml_en , s_mh_en, s_h_en : std_logic; signal s_mh,: integer range 0 to 5; signal s_ml: integer range 0 to 9; signal s_h: integer range 0 to 23;s_ml_en <= set and adj_m; s_h_en <= set and adj_h; SET1M: countergeneric map( count_value => 9)port map(clk=>clk1s,clr=>disable,en=>s_ml_en,co=>s_mh_en,count=>s_ml); SET10M: countergeneric map( count_value => 5)port map(clk=>clk1s,clr=>disable,en=>s_mh_en,count=>s_mh); SET_H: countergeneric map( count_value => 23)port map(clk=>clk1s,clr=>disable,en=>s_h_en,count=>s_h);㈣显示功能描述clk1sdisableSignal scan:integer range 0 to 5;process (scanclk) beginif scanclk'event and scanclk='1' then if scan = 5 then scan<=0; else scan <= scan + 1; end if; end if; end process;Scan_out<= scan;⒉多路选择器signal hh : integer range 0 to 2; Signal hl,ml,sl: integer range 0 to 9; signal sh,mh: integer range 0 to 5; signal h: integer range 0 to 23;h<=c_h when set = '0' else s_h; hh<=1 when h>=10 and h<20 else 2 when h>=20 else10h 1h 10M 1M 10s 1sScan= 0:sl1:sh 2:ml 3:mh 4:hl 5:hh0;hl<=(h-0) when h<10 else(h-10) when h>=10 and h<20 else(h-20);mh<=c_mh when set = '0' else s_mh;ml<=c_ml when set = '0' else s_ml;②时、分、秒去参加译码的选择Signal hex:integer range 0 to 10;with scan selecthex<=hh when 5,hl when 4,mh when 3,ml when 2,sh when 1,sl when others;⒊七段显示译码signal led: STD_LOGIC_VECTOR (6 downto 0);led_out<= NOT led;with hex selectled<="1111001" when 1, --1"0100100" when 2, --2"0110000" when 3, --3"0011001" when 4, --4"0010010" when 5, --5"0000010" when 6, --6"1111000" when 7, --7"0000000" when 8, --8"0010000" when 9, --9"1000000" when 0, --0"1111111" when others;⒋小数点显示with scan selectpoint_out <='0' when 5,clk1s when 4,'0' when 3,clk1s when 2,'0' when 1,'0' when others;㈤报时、闹铃signal sound,sound1,sound2,sound3: std_logic;sound1 <= cnt(0) when s_ml=c_ml and s_mh=c_mh and s_h=c_h else '0';--闹铃sound2 <= scanclk when c_ml=0 and c_mh=0 and sh=0 and sl=0 and clk1s=‘1’ else ‘0’; ---整点报时(频率scanclk,持续时间半秒)sound3 <= cnt(0) when c_ml=9 and c_mh=5 and sh=5 and dy=‘0’ and clk1s=‘1’ else ‘0’; ---59’ 50’’开始报时(频率610Hz,持续半秒)sound<=sound1 or sound2 or sound3;sound_out <= sound when close = '0' else '0';。

多功能数字钟 课件设计

基础课程设计——多功能数字钟院系:物理与电气工程学院专业:电气工程及其自动化年级:2009级时间:2011-12-10多功能数字钟电路设计与制作摘要数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

目前,数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。

数字钟适用于自动打铃、自动广播,也适用于节电、节水及自动控制多路电器设备。

它是由数子钟电路、定时电路、放大执行电路、电源电路组成。

为了简化电路结构,数字钟电路与定时电路之间的连接采用直接译码技术。

具有电路结构简单、动作可靠、使用寿命长、更改设定时间容易、制造成本低等优点。

从有利于学习的角度考虑,这里主要是以中小规模集成电路设计数字钟的方法。

1系统原理框图数字钟电路系统由主体电路和扩展电路两大部分组成。

其中,主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展部分。

该系统的工作原理是:振荡器产生的稳定高频脉冲信号,作为数字钟的时间基准,再经分频器输出标准秒脉冲。

秒计数器计满60后向分计数器进位,分计数器计满60后向小时计数器进位,小时计数器按照“24翻1”的规律计数。

计数器的输出经译码器送显示器。

计时出现误差时可以用校时电路进行校时、校分。

扩展电路必须在主体电路正常运行的情况下才能进行功能扩展。

其整体系统框图如图1。

图1 多功能数字钟系统组成框图⑴555振荡器电路:555振荡器电路给数字钟提供一个频率稳定准确的1KHz的方波信号,可保证数字钟的走时准确及稳定。

⑵分频器电路:分频器电路将1KHZ的高频方波信号经74LS90分频后得到1Hz的方波信号供秒计数器进行计数。

分频器实际上也就是计数器。

⑶时间计数器电路:时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,时个位和时十位计数器为24进制计数器。

多功能数字钟

电子技术课程设计多功能数字钟学院:专业、班级:姓名:学号:指导老师:2008年12月目录1、设计任务与要求 (2)2、总体框图 (2)3、选择器件 (2)4、功能模块 (3)(1)时钟记数模块 (3)(2)整点报时驱动信号产生模块 (6)(3)八段共阴扫描数码管的片选驱动信号输出模块 (7)(4)驱动八段字形译码输出模块 (9)5、总体设计电路图 (10)(1)仿真图 (10)(2)电路图 (11)(3)管脚图 (11)6、设计心得体会 (12)一、设计任务与要求1、具有时、分、秒记数显示功能,以24小时循环计时。

2、要求数字钟具有清零、调节小时、分钟功能。

3、具有整点报时,整点报时的同时LED灯花样显示。

二、总体框图多功能数字钟总体框图如下图所示。

它由时钟记数模块(包括hour、minute、second 三个小模块)、驱动8位八段共阴扫描数码管的片选驱动信号输出模块(seltime)、驱动八段字形译码输出模块(deled)、整点报时驱动信号产生模块(alart)。

系统总体框图三、选择器件网络线若干/人、共阴八段数码管6个、蜂鸣器、hour(24进制记数器)、minute(60进制记数器)、second(60进制记数器)、alert(整点报时驱动信号产生模块)、seltime(驱动8位八段共阴扫描数码管的片选驱动信号输出模块)、deled(驱动八段字形译码输出模块)。

四、功能模块多功能数字钟中的时钟记数模块、驱动8位八段共阴扫描数码管的片选驱动信号输出模块、驱动八段字形译码输出模块、整点报时驱动信号产生模块。

(1) 时钟记数模块:<1.1>该模块的功能是:在时钟信号(CLK)的作用下可以生成波形;在清零信号(RESET)作用下,即可清零。

VHDL程序如下:LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity hour isport(clk,reset:in std_logic;daout:out std_logic_vector(5 downto 0));end entity hour;architecture fun of hour issignal count:std_logic_vector(5 downto 0);begindaout<=count;process(clk,reset)beginif(reset='0') thencount<="000000";elsif(clk' event and clk='1') thenif(count(3 downto 0)="1001") thenif(count<16#24#) thencount<=count+7;else count<="000000";end if;elsif(count<16#23#) thencount<=count+1;else count<="000000";end if;end if;end process;end fun;<1.2>VHDL程序如下:LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity minute isport(clk,clk1,reset,sethour:in std_logic;enhour:out std_logicdaout:out std_logic_vector(6 downto 0));end entity minute;architecture fun of minute issignal count:std_logic_vector(6 downto 0); begindaout<=count;process(clk,reset,sethour)beginif(reset='0') thencount<="0000000";elsif(sethour='0') thenenhour<=clk1;elsif(clk' event and clk='1') thenif(count(3 downto 0)="1001") thenif(count<16#60#) thenif(count="1011001") thenenhour<='1';count<="0000000"; else count<=count+7;end if;elsecount<="0000000";end if;elsif(count<16#60#) thencount<=count+1;enhour<='0';elsecount<="0000000";end if;end if;<1.3>VHDL程序如下:LIBRARY ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY second ISPORT(clk,reset,setmin:IN STD_LOGIC;enmin:OUT STD_LOGIC;daout:out std_logic_vector(6 downto 0)); END entity second;ARCHITECTURE fun OF second ISSIGNAL count:STD_LOGIC_VECTOR(6 downto 0); BEGINdaout<=count;process(clk,reset,setmin)beginif(reset='0') thencount<="0000000";elsif(setmin='0')thenenmin <=clk;elsif(clk'event and clk='1')thenif(count(3 downto 0)="1001")thenif(count<16#60#)thenif(count="1011001")thenenmin<='1';count<="0000000";ELSE count<=count+7;end if;elsecount<="0000000";end if;elsif(count<16#60#)thencount<=count+1;enmin<='0';elsecount<="0000000";end if;end if;end process;END fun;(2)整点报时驱动信号产生模块该模块功能:在时钟信号(CLK)的作用下可以生成波形,SPEAK输出接扬声器,以产生整点报时发声。

数电课程设计-数字电子钟PPT课件

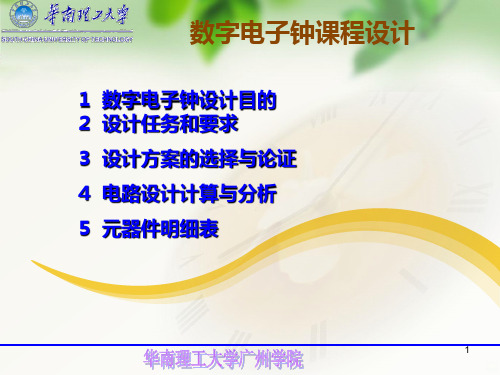

3 设计方案的选择与论证

数字电子钟系统框图如下:

图3.1 数 字 电 子 钟 系 统 框 图

6

3 设计方案的选择与论证

3.1) 时间脉冲产生电路

振荡器是数字钟的核心。振荡器的稳定度及频率的 精确度决定了数字钟计时的准确程度。

由集成逻辑门与RC组成的时钟源振荡器或由集成 电路定时器555与RC组成的多谐振荡器作为时间 标准信号源。

本实验中采用4040来构成分频电路。CD4040计数 为最高为12级2进制计数器,可以将32767HZ的信 号先分频为8HZ,再分为1HZ的信号。如图4.1所示 ,可以直接实现振荡和分频的功能。

16

4 电路设计计算与分析

4.2) 时、分、秒计数器

数字钟的计数电路用两个六十进制计数电路和24进 制计数电路实现的。

数字电子钟设计目的数字电子钟设计目的设计任务和要求设计任务和要求设计方案的选择与论证设计方案的选择与论证电路设计计算与分析电路设计计算与分析元器件明细表元器件明细表11掌握数字钟的设计掌握数字钟的设计22熟悉集成电路的使用方法熟悉集成电路的使用方法11显示显示时时分分秒22可以可以2424小时制或小时制或1212小时制小时制

本设计校时电路是将各个位上的使能端引出接一个 单刀双掷开关,一端(1端)接低位的进位信号,另 一端(2端)接校时电路。校正某位上的时间时,可 以将相应位的开关接到2端,通过拨动校时电路就能 实现校时功能。

12

3 设计方案的选择与论证

3.5) 整点报时电路

一般时钟都应具备整点报时电路功能,即在时间出 现整点前数秒内,数字钟会自动报时,以示提醒。

J2是时校正开关。不校正时,J2开关是连接上面的 ,即连接正常计数。当校正时位时,首先截断正常的 计数通路,然后再进行人工出触发计数加到需要校正 的计数单元的输入端,校正好后,再转入正常计时状 态即可。

多功能数字钟——校时闹钟之欧阳家百创编

电子电路综合实验报告欧阳家百(2021.03.07)——多功能数字钟设计目录设计理念2设计要求3设计目的3设计要求4总体设计概要4振荡器电路4输出波形仿真图如图所示5分频器电路5时间计时单元的设计5译码与显示电路的设计6校时电路的设计6方案一:7方案二:8定时控制电路的设计8·电子系统中常见实际问题的分析9面包板和芯片的测试9时间计数电路的连接与测试9校正电路9主要芯片介绍10主体电路的装调10时钟结果仿真12面包板的使用及注意事项12实验用到的器件13设计理念20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

数字钟已成为人们日常生活中:必不可少的必需品,广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

由于数字集成电路技术的发展和采用了先进的石英技术,使数字钟具有走时准确、性能稳定、集成电路有体积小、功耗小、功能多、携带方便等优点,,因此在许多电子设备中被广泛使用。

电子钟是人们日常生活中常用的计时工具,而数字式电子钟又有其体积小、重量轻、走时准确、结构简单、耗电量少等优点而在生活中被广泛应用,因此本次设计就用数字集成电路和一些简单的逻辑门电路来设计一个数字式电子钟,使其完成时间及星期的显示功能。

本次设计以数字电子为主,分别对1S时钟信号源、秒计时显示、分计时显示、小时计时显示、整点报时及校时电路进行设计,然后将它们组合,来完成时、分、秒的显示并且有整点报时和走时校准的功能。

并通过本次设计加深对数字电子技术的理解以及更熟练使用计数器、触发器和各种逻辑门电路的能力。

电路主要使用集成计数器、译码集成电路、LED数码管及各种门电路和基本的触发器等,电路使用5号电池共电,很适合在日常生活中使用。

数字钟PPT课件

9

74LS161计数器功能表

2021/6/16

10

计数

输入计 计数器输出 对应 输入计 计数器输出 对应

数脉冲 顺序

QD

QC

QB

QA

十进 制数

数脉冲 顺序

QD

QC

QB

QA

十进 制数

0 0000 0 8 1000 8 1 0001 1 9 1001 9 2 0 0 1 0 2 10 1 0 1 0 10 3 0 0 1 1 3 11 1 0 1 1 11 4 0 1 0 0 4 12 1 1 0 0 12 5 0 1 0 1 5 13 1 1 0 1 13 6 0 1 1 0 6 14 1 1 1 0 14

2021/6/16

23

注意事项

在调试时,应分阶段连接调试,一步一步地进 行。例如,先连接好个位的十进制计数器,电 路工作正确后,再接十位的计数器。两者都正 常后,再将60进制计数器连接起来。采用这种 步步为营的接线和调试方法(称为自下而上), 能较容易地发现问题并排除故障。

2021/6/16

24

六十进制计数器(显示秒或分)

2021/6/16

14

24进制计数器(显示小时)

用74LS00

2021/6/16

15

内容

1. 检查译码显示电路的功能。 2. 测试74LS161计数器的功能。 3. 分别连接10进制和6进制计数器。 4. 连接60进制和24进制计数器。

2021/6/16

16

检查译码显示电路的功能

实验中A、B、C、D

悬空,P、L、T可悬

L

空,但最好接高电平。

2021/6/16

18

分别连接10进制和6进制计数器

多功能数字钟

1总体设计1.1总体思路的设计:多功能数字钟只要是以数字的形式显示时间,数字时钟系统由主电路和扩展电路两大部分组成的。

主电路完成数字钟的基本功能,包括24进制的时位,60进制的分位和60进制的秒位。

扩展电路完成数字钟的扩展功能。

振荡器是数字钟的核心,振荡器的频率越高,计时精度越高。

有555构成的多谐振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,在经分频器输出标准脉冲.秒计数器满60后向分数器进位,分数器计满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。

计数器的输出经译码器送显示器。

计时出现误差时可以用校时电路进行校时,校分,校秒。

当然,扩展电路必须在主体电路正常运行的情况下才能进行功能扩展,经过这样每一个单元的设计初步可以完成数字钟的设计。

1.2基本原理:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,已得到广泛的使用。

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

脉冲每来1HZ计数器就进1,由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路。

同时必需以标准的1HZ时间信号作为时钟驱动。

通常使用石英晶体振荡器电路构成数字钟。

图1所示为数字钟的一般构成框图。

⑴晶体振荡器电路:晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

不管是指针式的电子钟还是数字显示的电子钟都使用了晶体振荡器电路。

2)次⑵分频器电路:分频器电路将32768HZ的高频方波信号经32768(15分频后得到1Hz的方波信号供秒计数器进行计数。

分频器实际上也就是计数器。

⑶时间计数器电路:时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒个位和秒十位计数器、分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器。

数字钟设计方案ppt课件

三、 整体方案论证

– 根据设计题目的功能要求,采用自顶向下的拼凑法 可以构成如图1所示的方框图。

• 自顶向下法(Top to Down)

– 首先从系统级设计开始,根据系统级所描述的该系统应具 备的各项功能,将系统划分为单一功能的子系统,再根据 子系统任务划分各部件,完成部件设计后,最后才是元件 级设计。

• AT89C2051采用简单的RC复位电路。

硬件电路设计

• MCU时钟频率直接影响指令执行速度与芯片的功耗。本

课题对执行速度并不要求快,而且希频率低一点可降低功 耗,故选为6MHz,由于机器周期为时钟频率的1/12, 即2µs,为整数值,定时器中断时间亦为2µs的整数倍, 对计时精度有利,何况6MHz的石英晶振为长线器件,价 格较低。

硬件电路设计

• +12V供电由7805降至+5V供系统使用。按LED所有笔段

全亮,所需电流约12.5mA。 • JQX-14F通电时线圈耗电约45mA,AT89C2051 5V供

电时工作电流约12.5mA,电路总电流约70mA。 • 7805压降为7V,管耗为0.49W。其热阻℃/W,即使不

– 优点:避开具体细节,有利于抓住主要矛盾。 – 适用于大型的、复杂的系统设计

整体方案论证

• [方案一] • 直接利用专用时钟芯片计时。

按键

时

MCU

钟

芯

显示

片

整体方案论证

– 该方案的优点是各器件的功能清晰。缺点是所用芯片数多、PCB 面积大、接线多、焊点多。因此可靠性略差,而且成本也较高, 不符合低价位的要求。

阴极动态驱动方式,它共需八根段位口线,两根阴极

驱动口线,即LED需要十根MCU I/O口线。

多功能电子钟PPT

2.手动调节风扇旋转方向 每按一次方向键,风扇转向会在正转 和反转间循环,在液晶上依次用 ‘Z’ 、‘F’表示。

3.根据周边环境气温自动调节速度档位 每按一次温控键,温控会在开启状态 与关闭状态间循环。在液晶上分别用 字母’K’、’G’表示,此时风扇会根据周 边环境气温进行调速。

4.根据需要给风扇设定转动时间 按下定时键,可以设定旋转时间, 当时间到时,风扇会停下来,并通 过蜂鸣器播放音乐,提示用户时间 已到。

1.1显示时间,年月份,而且断电 后可以继续保持时间的流动

1.2显示环境的温度

点击添加文本

特点:单片机断电后时间 继续流动

1.4调节闹钟,及到了闹铃时间,蜂鸣器响, (单片机与单片机通信)小车跳动,可关掉 闹铃,蜂鸣器可调音调(4种)

1.3书写备忘录(只能书写大写的英文字母) 1.5 大运倒计时

SDE

周晓宇与戴东祥

第一节 第二节 智能电风扇 可动可玩游戏多功能电子钟

目录

多功能电子钟作品功能展示

1.1显示时间,年月份,而且断电后可以继续保持时间的流动 1.2显示环境的温度 1.3书写备忘录(只能书写大写的英文字母) 1.4调节闹钟,及到了闹铃时间,蜂鸣器响,(单片机与单片机通 信)小车跳动,可关掉闹铃,蜂鸣器可调音调(4种) 1.5 大运倒计时 1.6玩简陋的扫雷游戏 1.7通过电脑串口助手修改万年历(电脑与单片机通信) 1.8红外遥控小车正转,倒转,转弯等简单动作

遥控器

目录

智能风扇

主要功能如下

1.手动调节速度档位

2.手动调节风扇旋转方向

3.根据周边环境气温பைடு நூலகம்动调节速度档位 4.根据需要给风扇设定转动时间

1.手动调节速度档位 每按一次调速键,速度都在STOP、 SLOW、MID、FAST这四个档位之间 循环。此时液晶上显示字母’ G ’,表示可 进行手动调速。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 00 1

位 信

&

&

号

11 12 13 14

&

&

11 12 13 14

+VDD

9

Q3 Q2 Q1 Q0 LD

CTP

7

1 +VDD

CC40161(2)

CR D3 D2 D1 D0

CTT CP

10

9

Q3 Q2 Q1 Q0 LD

CTP

7

1 +VDD

CR

CC40161(1) D3 D2 D1 D0

CTT CP

分计数器是模M=60的计数器 ➢其计数规律为00—01—…—58—59—00…

时计数器是一个24进制计数器 ➢其计数规律为00—01—…—22—23—00… ➢即当数字钟运行到23时59分时,分的个位 计数器再输入一个脉冲时,数字钟应自动 显示为00时00分。

构成多位计数器的级联方法

进

0 10 1

10

654 3 2

654 3 2

CP

六十进制计数器

• 并行进位(同步) • 优点:速度较快; 缺点:较复杂

构成多位计数器的级联方法

六十进制计数器: 串行进位(异步)

0 10 1

进

位

&

信

11 12 13 14

+VDD

号

9

Q3 Q2 Q1 Q0 LD

ETP

7

CC40161 ETT 10

CR 1

D3 D2 D1 D0 CP

654 3 2

优点:简单

1 00 1

& 11 12 13 14

+VDD

9

Q3 Q2 Q1 Q0 LD

ETP

7

CC40161 ETT 10

CR 1

D3 D2 D1 D0 CP

654 3 2

CP

缺点:速度较慢 出现竞争冒险的可能性较大!

三、多功能数字钟整点报时系统

四、多功能数字钟校时系统

五、多功能数字钟时段控制系统

单击 Configure 按钮进行下载编程。

实验任务

完成数字钟的时、分、秒计数器,并能级联显示。 完成数字钟的扩展功能:闹钟、仿电台、报整点

十字路口交通灯的设计 篮球30秒减法计数器设计

(本设计中选择FLEX1k系列的EP1k30TC144-3器件)

c. 如果不对适配器件的型号进行选择,该软件将自动 选择适合本电路的器件进行编译适配。

(2)编译适配 选择 MAX+plusⅡ\Compiler ,弹出 Compiler 窗口。

单击 Start 按钮开始编译并显示编译结果,生成*. sof下载文件。(此次操作必须使用时序编译)

多功能数字钟

一、实验任务:

用FPGA器件和EDA技术

实现多功能数字钟的设计

已知条件

基本功能

➢ MAX+Plus II软件 ➢ FPGA实验开发装置

➢ 校时、校分

基本功能

➢ 以数字形式显示时、分、 ➢ 仿电台报时

秒的时间;

➢ 小时计数器为24进制;

➢ 分计数器为60进制。

➢ 时段控制

二、多功能数字钟系统的组成框图

秒计数器计满60后 数字“小钟24时电进扩计路计行计制展数数系时 路的数”电器分向出 进统情器规路按计小现行由况的律必照数时主误校下输计须器计体差时才出在计数电时、能经主满器路可校实译体6进和以分现码0电位后扩用、功器路展校校能送正电时秒扩显常向电路展示运分两器计大数部器分进所位组成

1、时、分计数器的设计

管脚的重新分配与定位

选择 MAX+PlusⅡFloorplan Editor选项,即可打开平 面(底层)编辑器窗口,出现如图所示的芯片管脚分配图。

芯片名称区 颜色图例

未赋值节点 和管脚显示

区

器件显示区

选中节点和 管脚区

这是由软件自动分配的,用户可根据需要随意改变管 脚分配,管脚的编辑过程如下。

管脚的编辑过程:

对管脚进行重新分配后,必须再编译一次,否则 下载后的管脚还是自动分配的状态。

对器件的编程下载

a. 选择 MAX+PlusⅡProgrammer 选项,如果是第一次使用, 将出现如图所示的对话框。

硬件类型选择 “ByteBlaster” 并单击 OK 确认。

b. 选择完下载文件后,单击 OK 确定,出现如图所示的编程界 面。

分个位 四、分B十C位D译码模块的介绍

时个位

七段译 码输出

时十位

选择时钟

数码管 选择计 数器

七段BCD译码电路1、BCD译码模块的介绍 数据选择器

8进制加法计数器

2、设计中添加BCD译码模块的过程

1、将../BCD2SEG7/目录 下的文件copy到用户设计 项目目录下

2、在顶层电路中调用元件 符号bcd2seg7.sym到电路 中

资源信号

管脚号 55 54 125 132 133 135 136 137 138 8 10 12 13 82 83 86 88 89 90 78 121

六、电路编译与适配

(1)选择器件 a. 选择 AssignDevice 选项,弹出 Device 对话框。

b. 在 Device Family 下拉列表框中选择适 配器件的系列,在 Devices 中选择器件 的型号,然后单击 OK 按钮。

用鼠标左键按住欲分配的输入、输出端口并拖 到下面芯片的相应管脚上,然后松开,即可完成一 个管脚的重新分配。分配完后需重新编译。

管脚重新分配时须注意的事项: 芯片上有些特殊功能的管脚(如GND、Global

CLK 等),进行管脚编辑时不能使用。

在器件选择时如果选择了Auto,则不允许对管脚 进行再分配。

进行如图所示的连接绘制

五、EP1K30TC144-3 开发试验箱

器 件 引 脚 与 资 源

数码管选择 按键

蜂鸣器 发光二极管

CLK1 CLK2 CLK3 A8 B8 C8 D8 E8 F8 G8 SEL0 SEL1 SEL2 KEY0 KEY1 KEY2 KEYS0 KEYS1 KEYS2 FMQ LED