MSP430时钟系统详解

关于单片机msp430的时钟资料

msp430f5419/38学习笔记之时钟系统(2011-11-30 10:41:30)分类: msp430标签:msp430f541xmsp430f543xucs时钟系统注:msp5419/38中,如果你使用SMCLK做TIMER_A的时钟,那么进入低功耗3或低功耗4是不会把SMCLK关掉的,这点5系列和其他系列的不一样。

UCS模块是一个低成本超低功耗系统,通过选择使用3个部时钟信号,用户可以得到性能和功耗的最佳平衡点。

UCS可以由软件配置其工作模式,如配置成:不需要任何外部器件、使用 1或 2个外部晶振等。

一、时钟系统UCS模块具有5个时钟源:XT1CLK:低频/高频振荡器,既可以与低频 32768HZ钟振、标准晶振、外部振荡器,又可以与外部4M-32MHZ时钟源一起使用,XT1CLK可以作为FLL模块部的参考时钟。

有些芯片XT1CLK只允许使用外部的低频晶振,具体可参考数据手册;XT2CLK:可选高频振荡器,可与标准晶振,振荡器或者 4MHZ~32MHZ外部时钟源一起使用;VLOCLK:部低功耗、低频振荡器,频率典型值为10KHZ;REFOCLK:部低频振荡器,典型值为 32768HZ,可作为 FLL基准时钟源;DCOCLK:可以通过 FLL来稳定的部数字控制振荡器(DCO);DCOCLK经过 FLL 分频后可得DCOCLKDIV。

UCS模块可以提供3种时钟信号:ACLK:辅时钟;MCLK:系统主时钟;SMCLK:子系统主时钟。

二、UCS操作PUC之后,UCS的默认配置模式如下:XT1CLK 选择LF模式下的XT1作为时钟源,ACLK 选择 XT1CLK 作为时钟源;MCLK 选择DCOCLKDIV作为时钟源;SMCLK 选择DCOCLKDIV作为时钟源;FLL操作使能,FLL基准时钟(FLLREFCLK)选择XT1CLK;XIN 和 XOUT作普通IO 口使用,禁止了 XT1 功能,直到 I/O 口重新配置为 XT1 模式;如果有 XT2IN 和XT2OUT,则一并配置为普通 IO 口,禁止 XT2 功能。

关于(单片机)msp430的时钟资料

msp430f5419/38学习笔记之时钟系统(2011-11-30 10:41:30)分类: msp430标签:msp430f541xmsp430f543xucs时钟系统注:msp5419/38中,如果你使用SMCLK做TIMER_A的时钟,那么进入低功耗3或低功耗4是不会把SMCLK关掉的,这点5系列和其他系列的不一样。

UCS模块是一个低成本超低功耗系统,通过选择使用3个内部时钟信号,用户可以得到性能和功耗的最佳平衡点。

UCS可以由软件配置其工作模式,如配置成:不需要任何外部器件、使用1或 2个外部晶振等。

一、时钟系统UCS模块具有5个时钟源:XT1CLK:低频/高频振荡器,既可以与低频 32768HZ钟振、标准晶振、外部振荡器,又可以与外部4M-32MHZ时钟源一起使用,XT1CLK可以作为FLL模块内部的参考时钟。

有些芯片XT1CLK只允许使用外部的低频晶振,具体可参考数据手册;XT2CLK:可选高频振荡器,可与标准晶振,振荡器或者 4MHZ~32MHZ外部时钟源一起使用;VLOCLK:内部低功耗、低频振荡器,频率典型值为10KHZ;REFOCLK:内部低频振荡器,典型值为 32768HZ,可作为 FLL基准时钟源;DCOCLK:可以通过 FLL来稳定的内部数字控制振荡器(DCO);DCOCLK经过 FLL分频后可得DCOCLKDIV。

UCS模块可以提供3种时钟信号:ACLK:辅时钟;MCLK:系统主时钟;SMCLK:子系统主时钟。

二、UCS操作PUC之后,UCS的默认配置模式如下:XT1CLK 选择LF模式下的XT1作为时钟源,ACLK 选择 XT1CLK 作为时钟源;MCLK 选择DCOCLKDIV作为时钟源;SMCLK 选择DCOCLKDIV作为时钟源;FLL操作使能,FLL基准时钟(FLLREFCLK)选择XT1CLK;XIN 和 XOUT作普通IO 口使用,禁止了 XT1 功能,直到 I/O 口重新配置为 XT1 模式;如果有 XT2IN 和XT2OUT,则一并配置为普通 IO 口,禁止 XT2 功能。

MSP430的时钟设置

MSP430的时钟设置MSP430大部分都有三时钟脉冲可供运行时选择,这三个时钟是,1)辅助时钟ACLK;2)系统主时钟MCLK;3)子系统时钟SMCLK。

这三种时钟脉冲的选择主要靠下面三个控制寄存器来完成,这三个控制寄存器是1)控制寄存器DCOCT其存储单元地址是56h;2) 基本始终控制寄存器1,BCSCTL1,地址57h;3) 基本始终控制寄存器2,BCSCTL2,地址58h。

下面对这三个寄存器的控制的软件状态状态进行介绍。

1)控制寄存器DCOCTLDCO2;DCO1;DCO0这三位共八个状态,控制时钟脉冲的8个频段。

000~111对应0~7;频率由低到高8个频段。

MOD.4~MOD.0这5为共32种状态,定义在32个周期中插入插入其他频率。

DCO2=0x80;DCO1=0x40;DCO0=0x20;MOD4=0x10;MOD3=0x08;MOD2=0x04;MOD1=0x02;MOD0=0x01其中TX2OFF为0,开启TX2振荡器,为1关闭;XTS=0开启低频模式,1开启高频模式;DIVA1和DIVA0控制分频模式0 0 不分频0 1 2分频1 0 4分频1 1 8分频TX5V一般设置为0RSEL2~RSEL0三位决定八个频段的不同频率,这样,RSEL2~RSEL0和DCO2~DCO0共可实现8*8=64个不同的频率。

由于430没有位操作,所以定义了每一位状态对应的名称:TX2OFF=0x80TXS=0x40DIVA1=0x20DIVA0=0x10TX5V=0x08RSEL2=0x04RSEL1=0x02RSEL0=0x01也就是每位所在的位置为1,其余位为0,这样,要对某一位操作,就可通过运算,在不改变其他位的情况下,对某一位进行置1或清0(如何做后面讲)。

SELM.1- SELM.0DIVM.1- DIVM.0SELS时钟源选择DIVS.1-DIVS.0 DCOR0 0 默认DCOCLK0 0默认MCLK=DCOCLK00 默认SMCLK=MCLK选择电阻0 1选择DCOCLK0 1 2分频选择SMCLK01 MCLK 2分频内电阻1 0 选择XT2CLK1 0 4分频默认选择DCOCLK10 MCLK 4分频或外电阻1 1 选择LFXTICLK1 18分频11 MCLK 8分频SELM1=0x80;SELM0=0x40;DIVM1=0x20;DIVM0=0x10;SELS=0x08;DIVS1=0x04;DIVS0=0x02;DCOR=0x01;下面看如何让在保证其他位不变的情况下给某一位清0或置1.例1要给BCSCTL2的bit3清0。

第二章 MSP430F149基本时钟系统

DCOR DIVS0 DIVS1 SELS DIVM0 DIVM1 SELM0 SELM1

(0x01) /* DCO 外部电阻使能 */ (0x02) /* SMCLK 2 分频 */ (0x04) /* SMCLK 4 分频*/ (0x08) /* SMCLK 时钟源选择 0:DCOCLK / 1:XT2CLK/LFXT1CLK */ (0x10) /* MCLK 2 分频 */ (0x20) /* MCLK 4 分频 */ (0x40) /* MCLK 时钟源选择 01:DCOCLK*/ (0x80) /* MCLK 时钟源选择 10:有 XT2 则选择 XT2CLK 否则选择 LFXT1CLK*/

/*************************************************

*BCSCTL2 控制位定义

**************************************************/

#define #define #define #define #define #define #define #define

/* Modulation Bit 0 */ /* Modulation Bit 1 */ /* Modulation Bit 2 */ /* Modulation Bit 3 */ /* Modulation Bit 4 */ /* DCO Select Bit 0 */ /* DCO Select Bit 1 */ /* DCO Select Bit 2 */

0——禁止中断

1——允许中断

说明:IE1 中其余位可能被其它模块使用。

5、IFG1:中断标志寄存器 1

7

6

5

4

MSP430F149的时钟操作详解

MSP430F149的时钟操作1)时钟图解图1 内部时钟图解2)内部时钟MSP430F149系统开启时,默认的时钟来源是内部的DCO,然后可以通过用户的软件设置切换到外部的晶体振荡器。

而MSP430F149可以选择的时钟来源可以有三个:1.来自外部高速晶振振动器。

2.来自外部的低速晶振振荡器,其实低速晶体振荡器也可以外接高速晶体振荡器跟第一个一样。

3.来自单片机内部的DCO时钟。

内部的DCO还可以通过DCOX和RSELX来选择其振荡频率。

而初始时,DCOX=3,RESLX=4。

其频率选择如下图:图2 DCO频率选择其中DCO一个为增加10%,RSEL一格增加25%。

MSP430F149内部有三种时钟:1.主系统时钟(MCLK);主系统时钟可以有三个来源。

2.子系统时钟(SMCLK);子系统时钟可以有两个来源:外部高速和DCO。

3.辅助系统时钟(ACLK);只有一个来源:外部低速。

他们都可以进行各自分频。

3)时钟的寄存器。

1.DCOCTLDCOx:选择DCO振荡频率(和RSELx共同决定)。

MODx:调制器的选择。

2.BCSCTL1XT2OFF:是否关闭高频震荡器。

0开;1关。

XTS:选择低速晶体振荡器的工作方式(其实低速晶体振荡器也可以接成高速晶体的)。

0为低;1为高。

DIVAx:选择对辅助系统时钟分频。

XT5V:无用。

RSELx:选择DCO的频率(和DCOx共同决定)。

3.BCSCTL2SELMx:选择主系统时钟的来源。

DIVMx:主系统时钟的分频。

SELS:选择子系统时钟来源。

DIVSx:选择子系统时钟的分频。

DCOR:DCO选择用片内电阻还是用外接电阻。

默认内接。

4.IE1OFIE:检测晶体振荡器是否正常工作使能控制。

0关;1开。

(产生的是非可屏蔽中断。

)5.IFG1:OFIFG:晶体振荡是否正常工作中断标志位。

(就算不打开使能端也只能置位,打开使能端只是能够进行打断CPU,使CPU进入中断程序。

MSP430时钟配置

MSP430 频率(时钟)配置MSP430时钟:1、在MSP430单片机中一共有四个时钟源:(1)LFXT1CLK,为低速/高速晶振源,通常接32.768kHz晶振(2)XT2CLK,可选高频振荡器,外接标准高速晶振,通常是接8Mhz,也可以接400kHz~16Mhz;(3)DCOCLK,数控振荡器,为内部时钟,由RC震荡回路构成,受温度和电压的影响较大;若外部不接稳定的晶振电路,直接由内部时钟工作,则会因环境变化而导致性能不稳定。

(4)VLOCLK,内部低频振荡器,12kHz标准振荡器。

(要得到标准的12k则必须外接32768等晶振)2、在MSP430单片机内部一共有三个时钟系统:(1)ACLK:辅助时钟,通常由LFXT1CLK或VLOCLK作为时钟源,可以通过软件控制更改时钟的分频系数;(2)MCLK:主时钟,为系统内核提供时钟,它可以通过软件从四个时钟源选择或者从四个时钟源分频后选择为主时钟;(3)SMCLK:子时钟,也是可以由软件选择时钟源。

3、MSP430的时钟设置包括3个寄存器,DCOCTL、BCSCTL1、BCSCTL2、BCSCTL3MOD0~MOD4: Modulation Bit,频率的微调。

一般不需要DCO的场合保持默认初始值就行了。

XT5V: 1.DIVA0~DIVA1:选择ACLK的分频系数。

DIVA=0,1,2,3,ACLK的分频系数分别是1,2,4,8;XTS: 选择LFXT1工作在低频晶体模式(XTS=0)还是高频晶体模式(XTS=1)。

XT2OFF: 控制XT2振荡器的开启(XT2OFF=0)与关闭(XT2OFF=1)。

正常情况下把XT2OFF复位就可以了.DCOR: 0,选择内部电阻;1,选择外部电阻DIVS0~DIVS1: DIVS=0,1,2,3对应SMCLK的分频因子为1,2,4,8SELS: 选择SMCLK的时钟源, 0:DCOCLK; 1:XT2CLK/LFXTCLK.DIVM0~1: 选择MCLK的分频因子, DIVM=0,1,2,3对应分频因子为1,2,4,8.SELM0~1: 选择MCLK的时钟源, 0,1:DCOCLK, 2:XT2CLK, 3:LFXT1CLK我用的时候一般都把SMCLK与MCLK的时钟源选择为XT2。

msp430 时钟与休眠模式

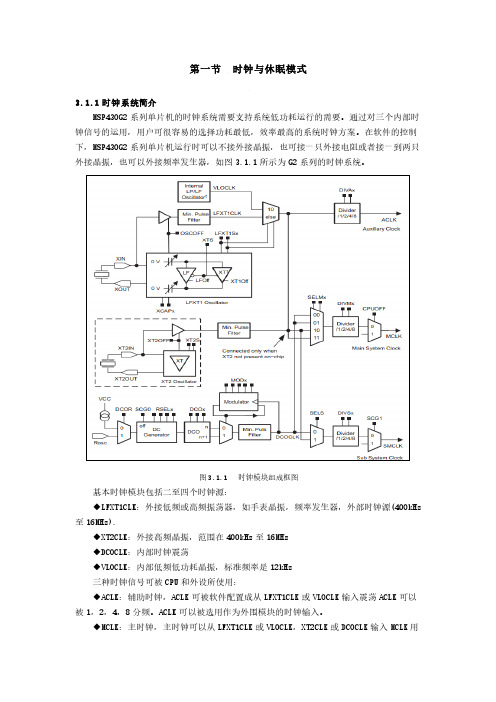

第一节时钟与休眠模式3.1.1 时钟系统简介MSP430G2系列单片机的时钟系统需要支持系统低功耗运行的需要。

通过对三个内部时钟信号的运用,用户可很容易的选择功耗最低,效率最高的系统时钟方案。

在软件的控制下,MSP430G2系列单片机运行时可以不接外接晶振,也可接一只外接电阻或者接一到两只外接晶振,也可以外接频率发生器,如图3.1.1所示为G2系列的时钟系统。

图3.1.1 时钟模块组成框图基本时钟模块包括二至四个时钟源:◆LFXT1CLK:外接低频或高频振荡器,如手表晶振,频率发生器,外部时钟源(400kHz 至16MHz).◆XT2CLK:外接高频晶振,范围在400kHz至16MHz◆DCOCLK:内部时钟震荡◆VLOCLK:内部低频低功耗晶振,标准频率是12kHz三种时钟信号可被CPU和外设所使用:◆ACLK:辅助时钟,ACLK可被软件配置成从LFXT1CLK或VLOCLK输入震荡ACLK可以被1,2,4,8分频。

ACLK可以被选用作为外围模块的时钟输入。

◆MCLK:主时钟,主时钟可以从LFXT1CLK或VLOCLK,XT2CLK或DCOCLK输入MCLK用在CPU系统之中。

◆SMCLK:辅助主时钟。

SMCLK可被选择从LFXT1CLK,VLOCLK,XT2CLK或DCOCLK输入。

SMCLK可以被1,2,4,8分频。

SMCLK可被选用为外围模块的时钟。

如图3.1.1所示为G2系列的时钟系统。

需要说明的是并非每一款G2系列的单片机都具有如上的时钟系统,以下做详细说明:MSP430G22x0:无LFXT1,无XT2,不支持ROSCMSP430G21x1,MSP430G2xx2,MSP430G2xx3:LFXT1不支持HF模式,无XT2,不支持ROSC。

MSP430x21x2:无XT23.1.2 时钟系统的操作在一个PUC信号之后,MCLK和SMCLK开始从DCO(大约在1.1MHz),ACLK从LFXT1CLK (内部电容为6pF)获取时钟。

MSP430时钟分析

MSP430时钟分析最近开始学习MSP430,在所有单片机学习中,时钟的设置无疑是最基本的一项工作!尤其对于现在的单片机,外部有低速,高速两种晶振,内部还有PLL 的内部时钟源,设置好系统工作的时钟则是工作完美开始的表现。

我一共用了两种系列的430 单片机,MSP430F149 和MSP430F437,系列的不同,时钟的设置也略有不同,下面从149 的时钟一步一步来说吧!在f149 中,基础时钟是被叫做basic clock module,其一共有三个时钟源:一个LFXT1CLK,为低速/高速晶振源,通常接32.768khz,也可以接(400khz~8Mhz)一个为XT2CLK,外接标准高速晶振,通常是接8Mhz,也可以接(400khz~8Mhz)还有一个叫DCOCLK,为内部晶振,有RC震荡回路构成。

在430 内部一共有三个时钟系统一个为ACLK,通常由LFXT1CLK 作为时钟源,可以通过软件控制改时钟的分频系树。

一个为MCLK,即Main CLK,一听就知道是主时钟单元,为系统内核提供时钟,它可以通过软件从三个时钟源选择,一个为SMCLK,称作辅助主时钟,也是可以由软件选择时钟源。

Basic Clock Module Registers(基础时钟寄存器)DCO control register DCOCTLBasic clock system control 1 BCSCTL1Basic clock system control 2 BCSCTL2SFR interrupt enable register 1 IE1SFR interrupt flag register 1 IFG1DCOCTL 寄存器是用来配置DCOCLK 的,这里暂且不提BCSCTL1 与BCSCTL2 寄存器则显得比较重要,这两个寄存器控制了你整个系统中430 的工作时钟系统。

BCSCTL1 寄存器:7 654 3 210XT2OFF XTS DIVAx XT5V RSELxXT20FF:用来控制XT2 晶振的开启和关闭,置1 时关闭,置0 时,开启XTS:用来选择低速晶体的工作模式(可忽略)DIVAx:用来选择ACLK 的分频系数XT5V: 无用。

MSP430G2553 系统时钟设置!

MSP430G2553系统学习之系统时钟(ls_core)把MSP430G2553的系统时钟作为系统学习的一篇讲解可见他的重要性,那为什么要把时钟放到第一位呢?学过FPGA的朋友都能体会得到,如果把CPU的所有工作任务作为纵坐标(y轴),那么时钟就是他的横坐标(x轴)了,如下图1 时钟概念所示。

图 1 时钟概念也就是说时钟就是一个微机(小到8位的51单片机大到32位的S3C2440等)在时域上的一个衡量标准。

如果学过FPGA的朋友都很清楚,微机是以对输入的时钟源的脉冲计数的方式来确定时域参数的。

所以,MSP430单片机也一样,拿到他之后首先从时钟入手,一定要养成这种系统学习的好方法,否则再学一百款单片机也是感觉再学新的,做不到举一反三,事半功倍的效果。

如果能够把握这其中的通理,你会有所有的单片机都一样样的感觉,当然学起来也就游刃有余了。

废话不多说了,进入正题。

一、硬件Msp420g2553的系统时钟是由VLOCK、LFXT1CLK和DCOCLK组成,如下图2 系统时钟组成所示:图2 系统时钟组成即2553的系统时钟源有三个分别是片内超低功耗12KHz的内部振荡器;由外部时钟源提供的LFXT1CLK时钟源,也即LanuchPad开发板上未焊接的时钟电路,在这里我们可以焊接一个32.768KHz的低频时钟晶体由2553的XIN引脚输入;片内可数字控制的振荡器DCOCLK,在软件的调节下该时钟的输出范围为0.6MHz到26MHz。

在这三个时钟源的独立工作或是在三个时钟源相互协调配合(是可以通过软件配置的)下为2553系统提供了系统时钟ACLK、MCLK和SMCLK。

ACLK为辅助时钟,由软件选择来自VLOCK、LFXT1CLK之一经过1,2,4,8分频之后得到,为外围模块提供时钟源。

MCLK为主时钟,由软件选择来自VLOCK、LFXT1CLK和DCOCLK之一经过1,2,4,8分频之后得到,为CPU和系统提供时钟。

msp430设置基本时钟系统

/* DCOCTL 的位定义 */ #define MOD0 (0x01) /* Modulation Bit 0 */ #define MOD1 (0x02) /* Modulation Bit 1 */ #define MOD2 (0x04) /* Modulation Bit 2 */ #define MOD3 (0x08) /* Modulation Bit 3 */ #define MOD4 (0x10) /* Modulation Bit 4 */ #define DCO0 (0x20) /* DCO Select Bit 0 */ #define DCO1 (0x40) /* DCO Select Bit 1 */ #define DCO2 (0x80) /* DCO Select Bit 2 */ /* BCSCTL1 的位定义 */ #define RSEL0 (0x01) /* Resistor Select Bit 0 */ #define RSEL1 (0x02) /* Resistor Select Bit 1 */ #define RSEL2 (0x04) /* Resistor Select Bit 2 */ #define XT5V (0x08) /* XT5V should always be reset */ #define DIVA0 (0x10) /* ACLK Divider 0 */ #define DIVA1 (0x20) /* ACLK Divider 1 */ #define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */ #define XT2OFF (0x80) /* Enable XT2CLK */ /* BCSCTL1 的 DIVA 的功能定义 */ #define DIVA_0 (0x00) /* ACLK Divider 0: 0x20) /* MCLK Divider 2: /4 */ #define DIVM_3 (0x30) /* MCLK Divider 3: /8 */ /* BCSCTL1 的 SELM 的功能定义 */ #define SELM_0 (0x00) /* MCLK Source Select 0: DCOCLK */ #define SELM_1 (0x40) /* MCLK Source Select 1: DCOCLK */ #define SELM_2 (0x80) /* MCLK Source Select 2: XT2CLK/LFXTCLK */ #define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */ #endif ///////////////////////////////////////////////// ///////////////////////////////////////////////// //////////////// #include; #include "BoardConfig.h" #include "SetClock.h" // 时钟设置函数// 系统时钟设定 void BCSInit (void) {

MSP430F5系列单片机时钟系统

UCS 模块方框图

3.2 UCS 模块的操作

PUC 复位后,UCS 模块的默认配置如下:

XT1 处于 LF(低频)模式且 模式且被选为 XT1CLK 时钟源。 时钟源。XT1CLK 被选作 ACLK

MCLK 选择 DCOCLKDIV

SMCLK 选择 DCOCLKDIV

FLL 操作使能, 操作使能,XT1CLK 作为 FLL 的参考时钟 FLLREFCLK

式下 XIN 可以连接外部时钟信号输入,XOUT 可以被配置成普通 I/O 口,PSEL 中与 XOUT 相关的位不予考虑。 一旦 PSEL 中与 XIN 相关的位被清零, 则 XIN 和 XOUT 引脚将会被 配置为普通 I/O 口,XT1 功能被禁止。 当地 XT1 被用作 ACLK、 MCLK 或 SMCLK(SELA=0、 SELM=0 或 SELS=0) 或 FLLREFCLK(SELREF=0)和 (XT1OFF=1) 从 LMP3 模式进入 AM (活动) 模 式 时 XT1 被 允 许 , 否 则 XT1 被 禁 止 。 当 XT1OFF=1 时 置 位 OSCOFF(LMP4),将禁止 XT1。如果应用中希望不管 OSCOFF 置位与否都 要使能 XT1,则只需清零 XT1OFF 就可以了。从 LMP4 模式进入 AM 模 式将是 XT1 使能。

对UCS模块进行配置。 UCS模块可以在程序执行过程中的任意时刻被软件进行配置或重 新配置。 3.2.1 UCS模块低功耗应用特点 UCS模块低功耗应用特点 冲突的要求典型的存在于电池供电的MSP430x5xx系列单片机的 应用中:

较低的时钟频率可以实现 较低的时钟频率可以实现节省能源并保持计时 实现节省能源并保持计时

MCLK 可以被配置为片上 DCO 或由 FLL 稳定后的随意频率的时钟, 当要求中断驱动事件时将被激活。 灵活的时钟分配和分频系统调整频 率使之满足个别的时钟要求。 MCLK 可以选择 XT1CLK、 VLOCLK、 REFOCLK、 DCO 或 XT2CLK 中的任何一个有效的时钟。 SMCLK 可以根据外围的要求被配置为来源于晶振或片上 DCO。灵 活的时钟分配和分频系统调整频率使之满足个别的时钟要求。SMCLK 可以选择 XT1CLK、VLOCLK、REFOCLK,DCO 或 XT2CLK 中的任何一个有 效的时钟。

MSP430的时钟系统

MSP430的时钟系统引言:MSP430的教科书通读了一遍,只是对其有一个整体的朦胧感.于是昨天开始准备编些程序试下自己的水平.可对着空荡荡的代码区硬是一个字都写不下去.涉及到细节问题,基本就是无从下手.现把一些细节问题整理在这个专栏里面,以备后面查证.同时觉得自己欠缺的还是一个对总体框架的把握,看来是要多读一些东西了.正文:MSP430根据型号的不同最多可以选择使用3个振荡器。

我们可以根据需要选择合适的振荡频率,并可以在不需要时随时关闭振荡器,以节省功耗。

这3个振荡器分别为:(1)DCO 数控RC振荡器。

它在芯片内部,不用时可以关闭。

DCO的振荡频率会受周围环境温度和MSP430工作电压的影响,且同一型号的芯片所产生的频率也不相同。

但DCO 的调节功能可以改善它的性能,他的调节分为以下3步:a:选择BCSCTL1.RSELx确定时钟的标称频率;b:选择DCOCTL.DCOx在标称频率基础上分段粗调;c:选择DCOCTL.MODx的值进行细调。

(2)LFXT1 接低频振荡器。

典型为接32768HZ的时钟振荡器,直接连接在XIN与XOUT 之间,此时振荡器不需要接负载电容。

也可以接450KHZ~8MHZ的标准晶体振荡器,此时需要接负载电容.LXFT1产生的频率信号为ACLK.低速时钟需要上百毫秒的建立时间才能稳定下来.(3)XT2 接450KHZ~8MHZ的标准晶体振荡器。

外部标准晶体振荡器接在XT2IN和XT2OUT之间,此时需要接负载电容,不用时可以关闭。

低频振荡器主要用来降低能量消耗,如使用电池供电的系统,高频振荡器用来对事件做出快速反应或者供CPU进行大量运算。

MSP430的3种时钟信号:MCLK系统主时钟;SMCLK系统子时钟;ACLK辅助时钟。

(1)MCLK系统主时钟。

除了CPU运算使用此时钟以外,外围模块也可以使用。

MCLK可以选择任何一个振荡器所产生的时钟信号并进行1、2、4、8分频作为其信号源。

第三章 MSP430基本外设1(时钟系统)

MSP430X5XX / 6XX系列时钟系统模块(2/3)

从上图可以看出,MSP430F5XX / 6XX时钟模块有 5 个时 钟输入源: XT1CLK 低频或高频时钟源:可以使用标准晶振,振荡 器或者外部时钟源输入4MHz~32MHz。XT1CLK可以作为 内部FLL模块的参考时钟。 XT2CLK 高频时钟源:可以使用标准晶振,振荡器或者 外部时钟源输入4MHz~32MHz。 VLOCLK 低功耗低频内部时钟源:典型值为10KHZ; REFOCLK 低频修整内部参考时钟源:典型值为 32768Hz,作为FLL基准时钟源; DCOCLK 片内数字控制时钟源:通过FLL模块来稳定。

SMCLK

时钟模块应用举例(MSP430F5XX / 6XX)(2/2)

UCSCTL6 &= ~XT2OFF; // 使能 XT2 UCSCTL6 &= ~(XT1OFF); // 使能 XT1 UCSCTL6 |= XCAP_3; // 配置内接电容值, // 若使输出为32.768KHz,则需要选择XCAP_3 do { UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG); // 清零XT1、XT2、DCO故障标志位 SFRIFG1 &= ~OFIFG; // 清零SFR中的故障标志位 }while (SFRIFG1&OFIFG); // 检测振荡器故障标志位 UCSCTL6 &= ~XT2DRIVE0; // 根据预期的频率,减小XT2的驱动 UCSCTL4 |= SELA_0 + SELS_5; // 选择 SMCLK和ACLK的时钟源 while(1); // 循环等待 }

MSP430G2553时钟,MSP430G2553时钟配置

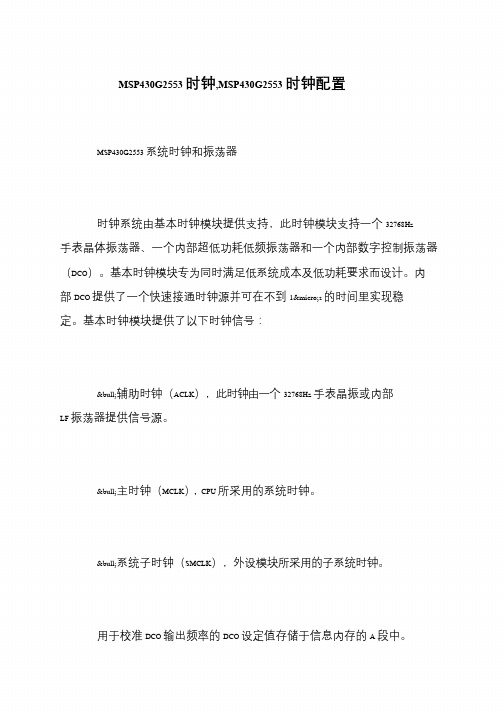

MSP430G2553 时钟,MSP430G2553 时钟配置MSP430G2553 系统时钟和振荡器时钟系统由基本时钟模块提供支持,此时钟模块支持一个32768Hz 手表晶体振荡器、一个内部超低功耗低频振荡器和一个内部数字控制振荡器(DCO)。

基本时钟模块专为同时满足低系统成本及低功耗要求而设计。

内部DCO 提供了一个快速接通时钟源并可在不到1µs 的时间里实现稳定。

基本时钟模块提供了以下时钟信号:•辅助时钟(ACLK),此时钟由一个32768Hz 手表晶振或内部LF 振荡器提供信号源。

•主时钟(MCLK),CPU 所采用的系统时钟。

•系统子时钟(SMCLK),外设模块所采用的子系统时钟。

用于校准DCO 输出频率的DCO 设定值存储于信息内存的A 段中。

主DCO 特性MSP430G2553 时钟1,MSP430G2553 能做到超低功耗,合理的时钟模块是功不可没的。

但是功能强大的时钟模块设置起来也相对复杂一些。

2,MSP430G2553 的时钟源有:(1),外接低频晶振LFXT1CLK:低频模式接手表晶体32768Hz,高频模式450KHz~8MHz;(2),外接高速晶振XT2CLK:8MHz;(3),内部数字控制振荡器DCO:是一个可控的RC 振荡器,频率在0~16MHz;(4),超低功耗低频振荡器VLO:不可控,4~20KHz 典型值为12KHz;3,时钟模块:430 的时钟模块有MCLK SMCLK ACLK :(1),主系统时钟MCLK:提供给MSP430 的CPU 时钟。

可以来自LFXT1CLK XT2CLK DCO VLO 可选,默认为DCO。

(2),子系统时钟SMCLK:提供给高速外设。

可以来自LFXT1CLK XT2CLK DCO VLO 可选,默认为DCO。

(3),辅助系统时钟ACLK:提供给低速外设。

MSP430G2553系统学习之系统时钟

MSP430G2553系统学习之系统时钟把MSP430G2553的系统时钟作为系统学习的一篇讲解可见他的重要性,那为什么要把时钟放到第一位呢?学过FPGA的朋友都能体会得到,如果把CPU的所有工作任务作为纵坐标(y轴),那么时钟就是他的横坐标(x轴)了,如下图1 时钟概念所示。

图 1 时钟概念也就是说时钟就是一个微机(小到8位的51单片机大到32位的S3C2440等)在时域上的一个衡量标准。

如果学过FPGA的朋友都很清楚,微机是以对输入的时钟源的脉冲计数的方式来确定时域参数的。

所以,MSP430单片机也一样,拿到他之后首先从时钟入手,一定要养成这种系统学习的好方法,否则再学一百款单片机也是感觉再学新的,做不到举一反三,事半功倍的效果。

如果能够把握这其中的通理,你会有所有的单片机都一样样的感觉,当然学起来也就游刃有余了。

废话不多说了,进入正题。

一、硬件Msp420g2553的系统时钟是由VLOCK、LFXT1CLK和DCOCLK 组成,如下图2 系统时钟组成所示:图2 系统时钟组成即2553的系统时钟源有三个分别是片内超低功耗12KHz 的内部振荡器;由外部时钟源提供的LFXT1CLK时钟源,也即LanuchPad开发板上未焊接的时钟电路,在这里我们可以焊接一个32.768KHz的低频时钟晶体由2553的XIN引脚输入;片内可数字控制的振荡器DCOCLK,在软件的调节下该时钟的输出范围为0.6MHz到26MHz。

在这三个时钟源的独立工作或是在三个时钟源相互协调配合(是可以通过软件配置的)下为2553系统提供了系统时钟ACLK、MCLK和SMCLK。

ACLK为辅助时钟,由软件选择来自VLOCK、LFXT1CLK之一经过1,2,4,8分频之后得到,为外围模块提供时钟源。

MCLK为主时钟,由软件选择来自VLOCK、LFXT1CLK和DCOCLK之一经过1,2,4,8分频之后得到,为CPU和系统提供时钟。

MSP430 时钟

MSP430单片机的时钟结构是其一大特点,像配置IO口一样,对MSP430单片机的时钟配置同样由很多的寄存器来完成。

我们引入官方的一张图片来描述MSP430单片机的时钟结构:让Cloud为大家解释一下这张图,MCLK是MSP430单片机的主系统时钟,用作CPU的时钟源,它由两个入口可选择,一个是来自上面的选择器,还有一个来自下面的DCO。

DCO翻译过来就是数字控制的RC振荡器,也就是一个可以通过编程来调节其震荡频率的RC振荡器,范围是0-16MHz。

MCLK上面是ACLK,用于外围慢速设备的时钟,MCLK下面是SMCLK,也叫子系统时钟,用于外围快速设备的时钟。

图片中蓝色的文字向我们说明了当MSP430上电后主系统时钟和子系统时钟都是由这个DCO来提供的,默认为1.1MHz (可以通过进一步修改来改变频率)。

而ACLK默认由外部的晶振来提供(LFXT1其实就是我们电路板上可焊接的32.768KHz的晶振,至于为什么是32768大家可以百度,这里并不关心)。

上面还有一个叫做VLO的超低功耗/低频振荡器,用户也可以通过设置来使用它。

一、和以往一样,我们先了解一下MSP430的时钟相关寄存器:1、DCOCTL:DCO控制寄存器这个寄存器用来定义DCO的频率;2、BCSCTL1:基本时钟系统控制寄存器1这个寄存器可以控制XT2的开启关闭,LFXT1的工作模式,ACLK的分频系数,还有DCO振荡器的内部电阻阻值(可以用以调节频率);3、BCSCTL2:基本时钟系统控制寄存器2这个寄存器用来定义MCLK、SMCLK的时钟来源和分频系数,另外还可以定义DCO 的电阻来自内部还是外部;4、BCSCTL3:基本时钟系统控制寄存器3这个寄存器用来定义LFXT1和XT2的工作模式还有外部晶振的负载电容以及LFXT1和XT2振荡器的错误标志(注意:由于G系列单片机没有XT2所以大家不必关心XT2)。

另外还有两个是中断寄存器,但是也和时钟配置相关,在这里我们也拿出几位来学习,在下面的详细说明中就不再加入这两个寄存器的说明了:5、IE1:中断使能寄存器1这个寄存器中第1位OFIE(晶振故障中断使能寄存器)用来允许或禁止晶体故障中断0-禁止中断1-使能中断6、IFG1:中断标志寄存器1这个寄存器中第1位OFIFG(晶振故障中断标志寄存器)用来指示是否有晶振故障的中断产生0-没有发生中断1-有中断事件发生二、下面详细说明每个寄存器的相关配置:1、DCOCTL寄存器配置:DCOCTL DCO控制寄存器76543210 DCO.2DCO.1DCO.0MOD.4MOD.3MOD.2MOD.1MOD.0·7~5-DCO:用来定义DCO的8中不同频率,相邻两种频率相差10%·4~0-MOD:定义在32个DCO周期中插入的Fdco+1周期个数,而在下的DCO周期中为Fdco周期,控制改换DCO和DCO+1选择的两种频率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2

while(1) { P1OUT = 0x40; _delay_cycles(100); P1OUT = 0; _delay_cycles(5000); } }

// 开启 LED // 关闭 LED

2、CPU 运行在晶振(32768Hz)时钟下: 时钟下: 晶体频率为 32768 赫兹,约 3 倍的 VLO。如果我们在前面的代码中使用晶振,指示灯应闪 烁大约每秒一次。 你知道为什么 32768 赫兹是一个标准?这是因为这个数字是 2 的 15 次方, 因此很容易用简单的数字计数电路,以每秒一次获得率 ——手表和其他时间时基。认识到 ACLK 来自外部晶振时钟。 #include <msp430g2231.h> void main(void) { WDTCTL = WDTPW + WDTHOLD; // 关闭看门狗定时器 P1DIR = 0x41; // P1.0 和 P1.6 配置输出 P1OUT = 0x01; // 开启 P1.0 BCSCTL3 |= LFXT1S_0; // LFXT1 = 32768Hz 晶振 while(IFG1 & OFIFG) { IFG1 &= ~OFIFG; // 清除 OSCFault 标志 _delay_cycles(100000); // 为可见的标志延时 } P1OUT = 0; // 关闭 P1 __bis_SR_register(SCG1 + SCG0); // 关闭 DCO BCSCTL2 |= SELM_3 + DIVM_3; // MCLK = 32768/8 while(1) { P1OUT = 0x40; // 开启 LED _delay_cycles(100); P1OUT = 0; / / 关闭 LED _delay_cycles(5000); } } 3、CPU 运行在晶振(32768Hz)和 DCO 时钟下: 时钟下: 最慢的频率,我们可以运行 DCO 约在 1MHz(这也是默认速度) 。因此,我们将开始切换 MCLK 到 DCO 下。在大多数系统中,你会希望 ACLK 上运行的 VLO 或 32768 赫兹晶振。 由于 ACLK 在我们目前的代码是在晶体上运行,我们会打开 DCO 计算。

// 清除 OSCFault 标志 // 为可见标志延时

P1OUT = 0; // P1.6 关闭 // __bis_SR_register(SCG1 + SCG0); // 关闭 DCO BCSCTL2 |= SELM_0 + DIVM_3; // MCLK = DCO while(1) { P1OUT = 0x40; _delay_cycles(100); P1OUT = 0; _delay_cycles(5000); } }

// P1.6 关闭 // P1.6 开启

以下将会分析上面 4 个例子的代码细微差别: 个例子的代码细微差别:

首先让我们看一下 msp430x20x2.h 这个文件中的内容, 由于头文件信息量很大这里就只简单 说明和以上四个代码有关的部分,其余请大家自行阅读。 一、WDTCTL = WDTPW + WDTHOLD; // 关闭看门狗定时器(例 1、2、3、4) 头文件中的相关说明如下: #define __MSP430_HAS_WDT__ SFR_16BIT(WDTCTL); #define WDTIS0 (0x0001) #define WDTIS1 (0x0002) #define WDTSSEL (0x0004) #define WDTCNTCL (0x0008) #define WDTTMSEL (0x0010) #define WDTNMI (0x0020) #define WDTNMIES (0x0040) #define WDTHOLD (0x0080) #define WDTPW (0x5A00)

4

#include <msp430g2231.h> void main(void) { WDTCTL = WDTPW + WDTHOLD; // 关闭看门狗定时器 if (CALBC1_1MHZ ==0xFF || CALDCO_1MHZ == 0xFF) { while(1); // If cal const erased,挂起 } BCSCTL1 = CALBC1_1MHZ; DCOCTL = CALDCO_1MHZ; P1DIR = 0x40; P1OUT = 0; BCSCTL3 |= LFXT1S_2; IFG1 &= ~OFIFG; //__bis_SR_register(SCG1 + SCG0); BCSCTL2 |= SELM_0 + DIVM_3; while(1) { P1OUT = 0x40; _delay_cycles(100); P1OUT = 0; _delay_cycles(5000); } } // Set range // 设置 DCO 模式 // P1.6 配置输出 // P1 关闭 // LFXT1 = VLO // 清除 OSCFault 标志 // 关闭 DCO // MCLK = DCO/8

MSP430 时钟系统 时钟系统讲解 系统讲解

MSP430 时钟: 时钟: 1、在 MSP430 单片机中一共有 单片机中一共有三个或四个时钟源 中一共有三个或四个时钟源: 三个或四个时钟源: (1)LFXT1CLK,为低速/高速晶振源,通常接 32.768kHz,也可以接(400kHz~16Mhz); ( 2) XT2CLK, 可选高频振荡器, 外接标准高速晶振, 通常是接 8Mhz, 也可以接 (400kHz~ 16Mhz); (3)DCOCLK,数控振荡器,为内部晶振,由 RC 震荡回路构成; (4)VLOCLK,内部低频振荡器,12kHz 标准振荡器。 2、在 MSP430 单片机内部一共有三个时钟系统 单片机内部一共有三个时钟系统: 三个时钟系统: (1)ACLK,Auxiliary Clock,辅助时钟,通常由 LFXT1CLK 或 VLOCLK 作为时钟源,可 以通过软件控制更改时钟的分频系数; (2)MCLK,Master Clock,系统主时钟单元,为系统内核提供时钟,它可以通过软件从四 个时钟源选择; (3)SMCLK,Sub-Main Clock,系统子时钟,也是可以由软件选择时钟源。 Basic Clock Module Registers(基础时钟寄存器) DCOCTL ——DCO control register BCSCTL1——Basic clock system control 1 BCSCTL2——Basic clock system control 2 BCSCTL3——Basic clock system control 3 IE1——SFR interrupt enable register 1 IFG1——SFR interrupt flag register 1 3、MSP430 的时钟设置包括 3 个寄存器, 个寄存器,DCOCTL、BCSCTL1、BCSCTL2、BCSCTL3 DCOCTL,DCO 控制寄存器,地址为 56H,初始值为 60H

实例分析

1、CPU 运行在 VLO 时钟下: 时钟下: 这是最慢的时钟,在约 12 千赫兹下运行。因此,我们将通过可视化的 LED 闪烁的红色慢慢 地在约每 3 秒钟率。我们可以让时钟系统默认这种状态,设置专门来操作 VLO。我们将不 使用任何 ALCK 外设时钟在此实验室工作,但你应该认识到,ACLK 来自 VLO 时钟。 #include <msp430g2231.h> void main(void) { WDTCTL = WDTPW + WDTHOLD; // 关闭看门狗定时器 P1DIR = 0x40; // P1.6 配置输出 P1OUT = 0; // 关闭 LED BCSCTL3 |= LFXT1S_2; // LFXT1 = VLO IFG1 &= ~OFIFG; // 清除 OSCFault 标志 __bis_SR_register(SCG1 + SCG0); // 关闭 DCO BCSCTL2 |= SELM_3 + DIVM_3; // MCLK = VLO/8

3

#include <msp430g2231.h> void main(void) { WDTCTL = WDTPW + WDTHOLD;

// 关闭看门狗定时器

if (CALBC1_1MHZ ==0xFF || CALDCO_1MHZ == 0xFF) { while(1); // If cal const erased, 挂起 } BCSCTL1 = CALBC1_1MHZ; DCOCTL = CALDCO_1MHZ; P1DIR = 0x41; P1OUT = 0x01; BCSCTL3 |= LFXT1S_0; while(IFG1 & OFIFG) { IFG1 &= ~OFIFG; _delay_cycles(100000); } // Set range //设置 DCO 模式 // P1.0 和 P1.6 配置输出 // P1.0 开启 // LFXT1 = 32768Hz

DCO2

DCO1 DCO1

DCO0

MOD4

MOD3

MOD2

MOD1

MOD0

DCO0~DCO2: DCO Select Bit,定义了 8 种频率之一,而频率由注入直流发生器的电流定义。 MOD0~MOD4: Modulation Bit,频率的微调。 一般不需要 DCO 的场合保持默认初始值就行了。 BCSCTL1,Basic Clock System Control 1,地址为 57H,初始值为 84H

// P1.6 开启 / / P1.6 关闭

4、CPU 运行在 DCO 时钟下: 时钟下: 最慢的频率,我们可以运行 DCO 约在 1MHz(这也是默认速度) 。因此,我们将开始切换 MCLK 到 DCO 下。 在大多数系统中, 你会希望在 VLO 或者是晶振下运行 ACLK。 由于 ACLK 在我们目前的代码是在 VLO 上运行,我们会打开 DCO 运行。