用FPGA+DSP实现HDLC(高级数据链路控制)功能

基于FPGA+ARM的HDLC协议控制器的设计与实现

基于FPGA+ARM的HDLC协议控制器的设计与实现杨尧;赵立立;侯翔昊【摘要】针对飞控模拟装置中基于HDLC协议通信需求,完成了一种新的基于FPGA+ARM架构HDLC协议控制器的设计.文中首先介绍了HDLC协议的帧结构和循环冗余校验(CRC)原理,然后结合FPGA可进行任意数据宽度操作和ARM编程简单灵活的优点,有效实现了符合HDLC协议的帧结构和CRC校验的应用方法,满足HDLC协议要求.应用结果表明设计能够很好地满足各项功能指标的技术要求.【期刊名称】《电子设计工程》【年(卷),期】2014(022)010【总页数】3页(P91-93)【关键词】HDLC协议;循环冗余校验(CRC)原理;FPGA;ARM【作者】杨尧;赵立立;侯翔昊【作者单位】西北工业大学航天学院,陕西西安710072;西北工业大学航天学院,陕西西安710072;西北工业大学航天学院,陕西西安710072【正文语种】中文【中图分类】TN919高级数据链路控制(HDLC,High-Level Data Control)是一种同步数据传输、面向比特的数据链路层协议,具有差错检测功能强大、高效和同步传输的特点,目前HDLC协议已成为是通信领域中应用最广泛的协议之一,在飞行器设计领域经常用作飞控与舵机,助推器等之间通信的通信协议。

飞行控制模拟装置是在飞行器研制的方案阶段,用于飞行控制系统软件开发及仿真评估,飞行控制软件往往是A级软件,它的任何问题都将造成飞行失效,进而引起整个系统的瘫痪。

采取飞行器控制系统模拟装置进行软件算法验证,对各个分系统软件调试和系统验证,能够加快飞行器设计进度,减少设计风险和成本。

本文研究的HDLC协议控制器用于某型飞行器的飞控模拟装置与舵机控制器之间的通信。

一般而言HDLC协议主要是通过使用专用芯片和软件编程的方式来实现[1]。

目前在市场上有很多专用的HDLC协议处理芯片如MT8952B、MK5025,这些芯片性能可靠但功能针对性太强,适合应用于特定用途的大批量产品中[2]。

HDLC控制协议的FPGA设计与实现

! "# !

图 , $%&’ 协议控制器总体结构图

转换并送入数据总线。 04 - ’.’ 校验 $%&’ 协议使用循环冗余校验,在发送端对信 息进行 ’.’ 编码, 其生成多项式为 "# ’ ( ! ) * ! $ ! "% $ ! & $ " ’.’ 校验模块实际为根据生成多项式所设计的 编码电路。根据循环系统码编码原理,该编码电路 实际上是乘 ! "# 除 ’ ( ! ) 的电路, 其示意图如图 - 所 示。电路的工作过程如下: ( ,)," 级移位寄存器的初始状态全清零,门 , 开、 门 - 关, 然后进行移位。 信息位移入编码电路后, 一方面经或门输出, 一方面则自动乘以 ! "# 后进入除 从而完成乘 ! "# 除 ’ ( ! ) 的功能; ’ ( ! ) 除法电路, ( -)信息位全部移入编码电路后除法完成,此 时 ," 位移位寄存器中的内容就是除法的余式的系 数, 即校验元; ( 0) 门 , 关、 门 - 开, 再经过 ," 次移位后, 把移 位寄存器的校验元全部输出; ( 2)门 , 开、 门 - 关, 送入第二组信息组重复上 述过程。 ’.’ 编码器的核心 8$%& 源代码如下: 444444 % 9 / : ; < =>? @AB % 9 ,# : C DAB > >? / EA 0 FAAG % 9 > H ,: ; < % 9 > : C

$

’()* 协议简介

在 ’()* 通信方式中,所有信息都是以帧的形 式传送的, ’()* 帧格式如表 2 所列。 ( 2)标志字 ’()* 协议规定,所有信息传输必须以一个标 志字开始,且以同一个标志字结束,这个标志字是 %222222%。开始标志到结束标志之间构成一个完整 的信息单位,称为一帧。接收方可以通过搜索 %222222% 来探知帧的开始和结束,以此建立帧同 步。在帧与帧之间的空载期,可连续发送标志字来 做填充。 ( $)信息段及 “ %” 比特插入技术 ’()* 帧的信息长度是可变的,可传送标志字 以外的任意二进制信息。为了确保标志字是独一无 二的, 发送方在发送信息时采用 “ %” 比特插入技术,

介绍一下HDLC(High-Level Data Link Control)高层数据链路协议.doc

介绍一下HDLC(High-Level Data Link Control)高层数据链路协议

HDLC(High-Level Data Link Control)高层数据链路协议是一组用于在网络结点间传送数据的协议。

在HDLC中,数据被组成一个个的单元(称为帧)通过网络发送,并由接收方确认收到。

HDLC协议也管理数据流和数据发送的间隔时间。

HDLC是在数据链路层中最广泛最使用的协议之一。

现在作为ISO的标准,HDLC是基于IBM的SDLC协议的,SDLC 被广泛用于IBM的大型机环境之中。

在HDLC中,属于SDLC 的被称为通响应模式(NRM)。

在通常响应模式中,基站(通常是大型机)发送数据给本地或远程的二级站。

不同类型的HDLC被用于使用X.25协议的网络和帧中继网络,这种协议可以在局域网或广域网中使用,无论此网是公共的还是私人的。

基于FPGA平台的HDLC协议的应用与研究(全文)

基于FPG平台的HDLC协议的应用与研究一、HDLC协议的介绍数据链路层协议根据数据帧操纵的格式可以分为:面向字符的数据链路层协议和面向比特的数据链路层协议。

HDLC协议是一种面向比特的数据链路协议。

在这类面向比特的数据链路协议中,帧头和帧尾都是特定的二进制序列,通过操纵字段来实现对链路的监控,可以采纳多种编码方式实现高效的、可靠的透明传输。

二、基于FPG平台的HDLC协议的实现1、初始模块的实现.在实现HDLC模块以前必须针对其完成初始化的相应流程以后方可正常进入工作运行装填。

这里的初始化具体来说是针对HDLC模块内部的各类寄存器进行参数上的配置,其中主要的寄存器类型有辅助寄存器、地址寄存器等。

而且地址寄存器的初始化尤为重要,一般当对这几类寄存器完成初始化配置后,系统会自动生成一个标识信号,如果信号显示为正常且有效的,那么其代表HDLC的初始化工作已经基本完成,且可以进入到下一步工作状态中。

而辅助配置寄存器的初始化则并不一定需要在该阶段中完成。

2、发送模块的实现。

在HDLC协议中,具体负责差错校检功能的为CRC校检模块,具体的帧发送模块的实现过程为:首先系统与CPU线路开始连接一户,然后数据开始被写入到FIFO 中,如果检测到某条线路正好处于未被资源占用的状态,那么CRC校验模块则开始对FIFO中的数据进行校验和插零程序。

同时,数据经过插零并发送以后,每一个数据序列必须添加包头和包围并以串行的形式被发送端传输出去,并且将帧标志的状态修改为“011111100”,这里笔者将以上组成发送模块的发送端分成四个部分,分别是fifomin、insert_0、crcme以及frme insert 等模块。

3、接收模块的设计。

HDLC协议中的接收模块在功能结构的组成方面和发送模块相类似,主要由CRC校验模块、操纵模块、数据锁存模块以及同步模块组成。

具体来说,系统中的操纵模块针对数据传输中的删零过程以及标识检验过程来进行。

现代交换原理问答题题库

现代交换原理简答题1.简要说明DTMF信号的组成和特点。

DTMF信号是用高、低两个不同的频率来代表一个拨号数字。

DTMF信号的频带范围在话音频带的范围中,所以能通过交换机的数字交换网络和局间数字中继正确传输。

2.什么是电路交换方式?简要说明电路交换方式的特点。

电路交换方式是指两个用户在相互通信时使用一条实际的物理链路,在通信过程中自始至终使用该条链路进行信息传输,并且不允许其它计算机或终端同时共享该链路的通信方式。

电路交换属于电路资源预分配系统,即在一次接续中,电路资源预先分配给一对用户固定使用,不管电路上是否有数据传输,电路一直被占用着,直到通信双方要求拆除电路连接为止。

电路交换的特点是:在通信开始时要首先建立连接;1.一个连接在通信期间始终占用该电路,即使该连接在某个时刻没有信息传送,该电路也不能被其它连接使用,电路利用率低。

2.交换机对传输的信息不作处理,对交换机的处理要求简单,但对传输中出现的错误不能纠正。

3.一旦连接建立以后,信息在系统中的传输时延基本上是一个恒定值。

3.简要说明路由选择的一般原则:路由选择的一般原则是优先选择直达路由,后选迂回路由,最后选择由基干路由构成的最终路由。

4.简要说明本地电话网的含义。

本地电话网是指在同一个长途编号区范围以内的所有交换设备,传输设备和用户终端设备组成的电话网络。

5.什么是随路信令?什么是公共信道信令?随路信令是指用传送话路的通路来传送与该话路有关的各种信令,或传送信令的通路与话路之间有固定的关系。

公共信道信令是指传送信令的通道和传送话音的通道在逻辑上或物理上是完全分开的,有单独用来传送信令的通道,在一条双向的信令通道上,可传送上千条电路的信令消息。

6.简要说明数字程控交换系统中处理机的几种控制结构。

数字程控交换系统中处理机控制结构有分级控制方式,全分散控制方式和容量分担的分布控制方式的。

7.简要说明程控交换软件的基本特点——程控交换软件的基本特点是:实时性强,具有并发性,适应性强,可靠性和可维护性要求高。

基于FPGA的HDLC协议设计

摘要高级数据链路控制(HDLC)协议是数字通信中的重要协议之一。

Altera公司的可编程门阵列(FPGA),设计了一种基于并行机制的高级数据链路控制(HDLC)协议控制系统。

该系统采用模块组合的设计方法,使系统的复杂功能由各个模块组合实现,这种分块处理使得设计层次清晰且易于修改。

该系统有效利用FPGA的内部硬件资源,实现了并行的多通道的HDLC协议报文的生成和解析。

通过分析当前实现HDLC协议的一般方法,指出其存在的一些弊端,提出了一种利用FPGA 编程实现HDLC协议的硬件处理方法,并对FPGA如何实现HDLC协议的帧序列校验——循环冗余校验(CRC)进行了阐述。

模块下载到硬件中测试通过,证实了FPGA实现HDLC协议的可行性,模块编程简单且易于修改使其在应用中具有很大的优越性。

基于在数据通信中为了降低通信线路传输的误码率,需要采用高效能的差错控制方法。

循环冗余校验CRC由于编码简单且有效,是一种最常用的信道编码方。

【关键词】:HDLC协议FPGA CRC校验ABSTRACTHigh level data link control (HDLC) protocol is an important one in digital communication. Altera's programmable gate array (FPGA), design of parallel mechanism based on high level data link control (HDLC) Protocol control system. The system uses a combination of modular design method, complex combination of features from the various modules of the system implementation, this block makes the design is clear and easy to modify. The system effectively uses the FPGA's internal hardware resources, enabling parallel multi-channel HDLC protocol message generation and parsing. Through an analysis of the current implementation of HDLC Protocol General, pointed out that there are some drawbacks, have come up with a hardware processing of the HDLC protocol using FPGA programming methods and verification on FPGA implementation of HDLC protocol using FPGA programming methods and verification on FPGA implementation of HDLC protocol frame sequence-a cyclic redundancy check (CRC) explains. Module downloaded to the hardware test passed, confirm the feasibility of FPGA implementation of HDLC Protocol, application module programming simple and easy to modify so that it has a lot of advantages. In data communication in order to reduce the error rate of the transmission of communication lines, requires the use of high-efficiency error control method. Cyclic redundancy check CRC as the coding is simple and effective, is one of the most common channel coding.【Key words】HDLC protocol FPGA CRC check目录前言 (5)第一章HDLC协议概述 (6)第一节HDLC协议简介 (6)第二节HDLC协议分析 (6)第二章基于FPCA的HDLC协议器设计 (9)第一节FIFO缓存区及端口控制 (9)第二节HDLC协议器 (10)第三章综合和验证及结果 (13)第一节仿真及验证 (13)第二节系统模块图 (14)第三节现象及讨论 (14)心得体会…………………………………………………………………………………….15参考文献 (16)附录 (17)前言在数据通信中,链路层协议种类繁多,从通信方式看,可以分为异步通信和同步通信,同步通信的协议也多种多样,有基于字符的通信协议,比如BSC协议、CD2协议和DDCMP协议等;也有基于比特的通信协议,比如HDLC协议,HDLC (High Levei Data Link Controi)协议是通信领域中应用最广泛的协议之一,它是面向比特的高级数据链路控制规程,具有差错检测功能强大、高效和同步传输的特点。

基于FPGA的HDLC协议实现

万方数据万方数据万方数据710电子器件第32卷5结论本文以FPGA芯片为核心,使用DSP为处理器,通过DS96F175ME、DS96F174ME器件,实现了基于485总线的HDLC协议通讯,该通讯协议数据传输速率可达1Mbit/s。

参考文献:图3ModelSim仿真波形[2]杨怀省,刘卫东,赵艳华.基于DSP平台的AVS自适应环路滤图3中,hdlc—en是使能信号,在仿真过程中一波的研究与实现[J].电子器件,2008,31(3):948—951·軎擘聋送数据信景望t些a_oct≯et篓竖篓篓譬口3萎笳嚣毒嚣篡焉FPG娜A的。

踟RM。

.11通讯模块撇计与号为rLdata_octet;发送时钟为tX_clk;接收时钟为[4]磊赢毒三:二≤n。

nti∞高Au。

盯Gu.de[s].xIuN)(rx_clk;采用的485通讯接口都带有伴随时钟。

rx_2008.idle为空闲状态;rx_flags为标志状态;rx_frame—ok[5]High-SpeedDSPSystemsDesignReferenceGuide[S].Texas为帧结果状态;从仿真结果中可以看到发送数据为Instruments,2005·0x57时,延时后接收数据为0x57,该仿真结果与设[6]李珩·~‘iumDesigner6电路设计实例与技巧[M]·北京:国防计状态相符。

[7]主罢塞篆:芸羹等.Ⅺ。

缸FPGA设计基础[M].西安:西安[8]乔庐峰,王志功.VHDL数字电路设计教程[M].北京:电子工(上接第706页)[2]ZouSiyi,ZhangGuang-chun,wuGuang-ning.TheApplicationofEmbeddedReal—TimeLinuxIntelligentInsulationLineMonitoring[C]//ISEIM2001,2001:201-204.[3]李彪.嵌人式Linux在测控通信系统中的应用研究[D].国防科学技术大学硕f:学位论文,2002,11.[4]SmarTraining1二作室梁如军解字杰等.RedHatLinux9桌面应用[M].机械上业出版社,2003,10.[5]北京飞漫软件技术有限公司.Linux/ttclinux+MiniGUI:嵌入式系统开发原理、T具及过程[M].[6]魏永明.MiniGUl技术白皮书[J][EB/OL].http://www.minigui.org/cdelc.html,2005-05-15.[7]魏永明.MiniGUI的背景发展优势[J][EIS/OL].http://wⅥ慨cILibm.com/developerworks/linux/embed/minigui/minigui一1.html,2005-05—15.[8]魏永明.Minigui编程指南[s][EB/OL].http://www.minigui.com/download/cindex.shtmk[9]魏永明.Minigui用户手册[s][EB/OL].http://wvw.minigui.com/download/eindex.shtmLDo]陈雅秀.Linux指令辞典[M].中国铁道出版社,2001。

基于FPGA的高速同步HDLC通信控制器设计

陈 晨 ,李 志来 , 伟 ,金 光 一 徐

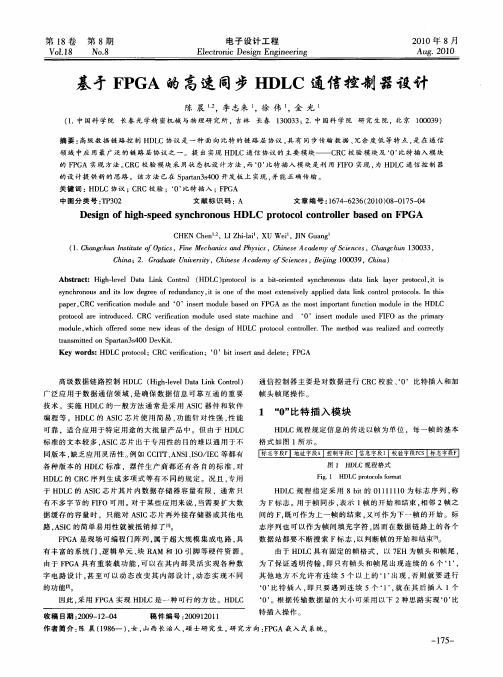

(. 1 中国 科 学 院 长 春 光 学精 密 机械 与 物 理研 究 所 ,吉林 长 春 1 0 3 ; .中国 科 学 院 研 究 生 院 ,北 京 1 0 3 ) 303 2 0 0 9 摘要 : 高级 数 据链 路 控 制 H L D C协 议 是 一 种 面 向 比特 的链 路 层 协议 , 有 同步 传 输 数 据 、 具 冗余 度 低 等 特 点 。 在 通 信 是 领 域 中应 用 最 广 泛 的链 路 层 协议 之 一 提 出实 现 H L D C通信 协议 的 主 要模 块— — C C校 验 模 块 及 ‘ ’ R O 比特 插 入 模 块

s n h o o s a d i o e r e o e u d n y i i o e o e mo te tn i ey a p id d t i k c n r lp oo o s n t i y c r n u n t lw d g e fr d n a c ,t s n ft s xe s l p l aa l o to r tc l.I h s s h v e n p p r C e f ai n mo u e a d ‘ a e . RC v r i t d l n 0’is r mo u e b s d o P st e mo ti ot n u cin mo u e i h i c o n e t d l a e n F GA a h s mp r t n t d l n t e HDL a f o C p oo o r n r d c d r tc l ae i t u e .CR e f a in mo u e u e tt c i e a d ‘ o C v r c t d l s d sa e ma h n n 0’i s r mo u e u e I O s t e p ma y i i o n et d l s d F F a h r r i mo u e. i h of r d s me n w i e s o h e in o L r tc lc nr l r h t o a e l e n o rc l d l wh c f e o e d a ft e d sg f HD C p oo o o t l .T e meh d w s r ai d a d c r t e oe z e y ta s t d o p r n s 0 v t r n mi e n S a a 3 4 0 De Ki t t . Ke r s y wo d :HDL r tc l RC v rf ai n ‘ C p oo o ;C e i t ; 0’b t n e t n ee e P i c o i i s r a d d lt ;F GA

多通道HDLC协议的FPGA实现

收稿日期 :2009203204 ; 修回日期 :2009204201 。 作者简介 :李 娜 (19842) ,女 ,在读研究生 ,主要从事声纳技术方向 的研究 。

图 1 CRC - 16 校验算法原理框图

根据 CCIT T 标准 , 采用 16 比特取反的帧检验序列 CRC EQU = 0000100000010000 。图 1 中输入即逻辑中的 BU FFER

图 2 多通道 HDL C 整体框图 图 2 为系统整体框图 , FP GA 按照 HDL C 协议规程 , 接 收并存储来自集成处理器等 8 个独立通道的数字量 。系统先将 外部输入的 HDL C 数据流由 RS485 电气特性转换为 T TL 电 平 , 在此过程中用光耦进行隔离 , 以避免与外部设备之间的相 互干扰 , 并且 RS485 芯片与光耦器件的相关电源使用由电气 供给的独立 5V 和 5V 地 。HDL C 协议总体结构框图如图 3 所 示 , 每个控制模块由时钟控制 、编码/ 冲突检测 、发送和接收 FIFO 等功能模块组成 。在发送方向和接收方向 , 各有一个 128 字节的 FIFO , 用于串行通道和 CPU 总线接口之间的数据 缓冲 。发送是接收的逆过程 , 这里我们以 HDL C 数据接收为 例进行说明 。

本文首先定义了亮暗目标的区别 , 建立了帧对消规则 。在 研究运动弱小目标和运动噪声的相似性和区别的基础上 , 针对 帧差分结果中噪声的弱相关性 , 利用对消后定点能量积累 , 解 决了能量积累时对目标运动速度的要求 , 克服了帧间差分法中 由于差分帧选择时机不当带来的空洞现象 。并提出组合扰动排 除法 , 大幅度削弱了帧间相互独立的运动噪声点和杂波干扰 。 实验证明该方法具有较好的实时性和准确性 , 提高了运算的速 度和精度 。

HDLC的DSP与FPGA实现-7页文档资料

HDLC的DSP与FPGA实现主题词:HDLC;FPGA;DSP硬件设计引言HDLC(高级数据链路控制)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。

实施HDLC的一般方法通常是采用ASIC器件或软件编程等。

HDLC的ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。

但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。

有的芯片公司还有自己的标准,对HDLC的CRC(循环冗余码校验)序列生成多项式等有不同的规定。

专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIPO(先进先出存储器)可用。

对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC再外接存储器或其他电路,ASIC的简单易用性就被抵销掉了。

HDLC的软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC应用。

但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不易预测。

纯软件HDLC一般只能用于个别路数的低速信号处理。

FPGA采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼顾速度和灵活性,并能并行处理多路信号,实时性能能够预测和仿真。

DSP采用软件技术处理信号,也可以反复编程使用。

DSP、FPGA芯片虽成本略微高于ASIC芯片,但具有货源畅通、可多次编程使用等优点。

在中小批量通信产品的设计生产中,用FPGA和DSP实现HDLC功能是一种值得采用的方法。

HDLC的帧结构和CRC校验为了使FPGA的设计能够实现HDLC的基本功能并能按照各项标准的规定灵活采用不同的cKC校验算法,首先看一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。

以下是ISO/IEC 3309标准规定的HDLC的基本帧结构。

基于FPGA的HDLC协议实现

第32卷 第3期2009年6月电子器件Chinese J ournal Of Elect ron DevicesVol.32 No.3J un.2009Implementation of H DLC Protocol B ased on FPGAL I U Yanj un 1,YA N H ai x i a 2,H E X i n31.Changchun I nstit ute of Optics ,Fine Mechanics and Physics ,Chinese A cadem y of S ciences ,Changchun 130033,China;2.J iL in Universit y Elect ronic Depart ment ,Changchun 130012,ChinaAbstract :In order to implement high speed serial communicatio n ,a co mmunication interface of RS485bus is designed based on FP GA.Between FP GA and DSP ,t here are two FIFO cache ,t he communication data are exchanged by DSP data bus.The PCB card which is centered by t he DSP and FP GA ,and programs t he HDL C protocol wit h V HDL are designed.Experiment result s show t hat t he communication speed can reach 1Mbit/s ,and t he system works stable wit hout error.K ey w ords :FP GA ;RS485;DSP ;HDL C EEACC :6150基于FPGA 的H DLC 协议实现刘岩俊1,闫海霞2,何 昕13(1.中国科学院长春光学精密机械与物理研究所,长春130033;2.吉林大学电子学院,长春130012)收稿日期:2008212217作者简介:刘岩俊(19782),男,助理研究员,博士,主要研究方向是光电测量,liuyanjun @ ;闫海霞(19772),女,讲师,博士,主要研究方向是信号处理;何 昕(19662),男,研究员,博士生导师,主要研究方向是光电测量、数字图像处理,SPIE 、中国光学协会会员摘 要:为了实现高速串行通讯,设计了基于FP GA 的RS485总线的通讯接口,FP GA 与DSP 之间采用双FIFO 进行数据缓存,并且通过DSP 总线与DSP 进行数据交换;开发了以FP GA 和DSP 为核心的原理图与印制电路板,使用V HDL 语言开发了HDL C 通讯协议的控制时序。

基于DSP和FPGA的HDLC协议通讯电路设计

可编程器件应用 电 子 测 量 技 术 EL ECTRONIC M EASU REM EN T TEC HNOLO GY第32卷第6期2009年6月 基于DSP和FPGA的H DLC协议通讯电路设计刘岩俊1 闫海霞2 魏仲慧1(1.中国科学院长春光学精密机械与物理研究所 长春 130033;2.吉林大学电子学院 长春 130012)摘 要:为了实现高速HDL C通讯协议,设计了DSP+FP GA结构的485通讯接口,接口包括DSP、FP GA、485转换等硬件电路,以及DSP与FP GA之间的数据交换程序和FP GA内部状态机;其中DSP用于实现数据控制,FP GA用于实现HDL C通讯协议,DSP与FP GA之间采用XIN TF方式,通过双FIFO缓存进行数据交换。

通过PCI接口连接PC机对系统进行测试,测试结果表明,系统通讯速度为1Mbps,并且工作稳定。

关键词:HDL C;RS485;FP GA;DSP中图分类号:TN409 文献标识码:ADesign of H DLC protocol communication circuitbased on DSP and FPGALiu Yanjun1 Yan Haixia2 Wei Zhonghui1(1.Changchun Institute of Optics,Fine Mechanics and Physics,t he Chinese Academy of Sciences,Changchun130033;2.JiLin University Electronic Depart ment,Changchun130012)Abstract:In order to realize the high speed HDL C communication protocol,a485interface with DSP+FP GA is designed,the interface includes the hardware circuit of DSP,FP GA,485conversion,the program of data exchange,and state machine.DSP control the communication data,FP GA implement the HDL C protocol,The FP GA and DSP exchange data with two FIFO cache by XIN TF interface.The system is tested by PC with PCI interface,experiments results show that the interface works stable with1Mbp s speed.K eyw ords:HDL C;RS485;FP GA;DSP0 引 言高级数据链路控制HDL C是一种面向比特的链路层协议,其最大特点是不需要数据必须是规定字符集,对任何一种比特流,均可以实现透明的传输。

HDLC协议高级数据链路控制协议

HDLC协议高级数据链路控制协议HDLC(High-Level Data Link Control)协议是一种高级数据链路控制协议,被广泛应用于计算机网络和通信领域。

本文将介绍HDLC协议的基本原理、特点和应用,并探讨其在现代通信系统中的重要性。

一、HDLC协议的基本原理HDLC协议是一种数据链路层协议,通过将数据划分为不同的数据帧来实现可靠的数据传输。

它定义了帧的结构、帧的传输方式以及数据的校验等重要内容。

HDLC协议主要包括以下几个方面的内容:1. 帧结构:HDLC协议将数据划分为不同的帧,每个帧包含帧开始标记、地址字段、控制字段、信息字段、校验码等部分。

帧开始标记用于标识帧的开始,地址字段用于标识帧的发送方或接收方,控制字段用于传输控制信息,信息字段用于传输数据,校验码用于检测传输过程中是否出现错误。

2. 帧传输:HDLC协议支持三种帧传输方式,分别是非确认传输、确认传输和多点传输。

非确认传输方式适用于数据传输不需要确认的场景,确认传输方式适用于需要确认的场景,多点传输方式适用于一对多的通信。

3. 数据校验:HDLC协议使用循环冗余校验(CRC)算法对数据进行校验,以确保传输过程中数据的完整性。

CRC算法通过计算数据的校验值,并将其附加在传输的数据帧中,接收方根据校验值验证数据的正确性。

二、HDLC协议的特点HDLC协议具有以下几个特点:1. 高效性:HDLC协议采用了帧封装的方式进行数据传输,可以高效地利用通信资源,提高传输效率。

2. 可靠性:HDLC协议通过数据校验和确认机制,可以确保传输过程中数据的可靠性,减少传输错误。

3. 灵活性:HDLC协议支持多种帧传输方式和多点传输方式,适用于不同的通信场景。

4. 可扩展性:HDLC协议可以通过定义不同的控制字段和功能码来扩展其应用范围,满足不同的通信需求。

三、HDLC协议的应用HDLC协议在计算机网络和通信系统中得到了广泛应用,具有重要的意义。

HDLC协议在FPGA通信系统中的实现

收稿日期:2008-10-13;修回日期:2008-12-08。

作者简介:宋飞(1982-),男,四川成都人,硕士研究生,主要研究方向:计算机网络、信息系统安全; 李志蜀(1946-),男,重庆人,教授,博士生导师,主要研究方向:计算机网络安全。

文章编号:1001-9081(2009)04-1092-03HDLC 协议在FPG A 通信系统中的实现宋 飞,李志蜀(四川大学计算机学院,成都610064)(asfei@yahoo )摘 要:设计了一种基于高级数据链路(HDLC )协议的数据通信系统,并将HDLC 协议在现场可编程门阵列(FPG A )中实现。

该系统可有效利用FPG A 片内硬件资源,无需外围电路,高度集成且操作简单。

着重介绍了系统中最重要的协议发送、接收模块以及”0”比特的插入删除模块的实现方法。

关键词:数据通信;高级数据链路协议;现场可编程门阵列中图分类号:TP393.04 文献标志码:AIm plem en t a ti on of HDLC protocol ba sed on FPGA i n comm un i ca ti on system sS ONG Fei,L I Zhi 2shu(College of Co m puter Science,S ichuan U niversity,Chengdu S ichuan 610064,China )Abstract:A data communicati on syste m based on H igh 2level Data L ink Contr ol (HDLC )p r ot ocol was designed,and then HDLC p r ot ocol in Field Pr ogra mmable Gate A rray (FPG A )was i m p le mented .The syste m can take advantage of FPG A hard ware effectively .It has s ome outstanding advantages,such as high scale integrati on,no need of peri pheral circuit and being easy t o use .This paper e mphatically described the i m p le mentati on methods of trans m itting p r ot ocol and receivingp r ot ocol and the method f or "0"bit inserti on and deleti on .Key words:data communicati on;H igh 2level Data L ink Contr ol (HDLC )p r ot ocol;Field Pr ogra mmable Gate A rray (FPG A )0 引言高级数据链路(H igh 2level Data L ink Contr ol,HDLC )协议是一个在同步网上传输数据、面向比特的数据链路层协议。

基于DSP和FPGA的CANopen-HDLC网关设计与实现

基于DSP和FPGA的CANopen-HDLC网关设计与实现胡四全;吉攀攀;王亚非【期刊名称】《自动化与仪表》【年(卷),期】2012(27)11【摘要】This paper designs a CANopen-HDLC Gateway based on DSP and FPGA. Using a DSP to complete the CANopen slave,a FPGA to complete HDLC optical fiber communication. This paper completed the design of the system hardware and software,and gives the block diagram of hardware and designand software flow chart,a long time running tests in the wind farm. This gateway was designed to complete the communication between the main control system and the core control unit of wind power converter.The practical results shows that the gateway has the advantages of high reliability, strong anti-jamming capability, fast response. The gateway meets the communication needs in the harsh environment.%设计了一种基于DSP和FPGA的CANopen-HDLC网关,用DSP实现CANopen从站功能,FPGA实现HDLC光纤通信.完成了系统的软硬件设计,给出了硬件电路图和软件流程图.应用于风电变流器与主控系统之间的通信,在风电场进行了长时间现场运行测试.实际运行结果表明,该网关具有可靠性高、抗干扰能力强、响应速度快等优点,可以满足恶劣环境下的通信需要.【总页数】4页(P28-30,39)【作者】胡四全;吉攀攀;王亚非【作者单位】合肥工业大学电气与自动化工程学院,合肥230009;许继集团有限公司,许昌461000;许昌市供电公司,许昌461000【正文语种】中文【中图分类】TP273+.5【相关文献】1.基于FPGA/DSP混合平台的数字电视网关 [J], 傅翔;门爱东;杨波2.基于DSP和FPGA的网络转换网关 [J], 陈明;宋宝;唐小琦3.基于DSP技术在家庭网关中的设计与实现 [J], 刘宇刚4.一种基于DSP+FPGA架构的IPTV网关方案研究 [J], 刘小明;彭静5.基于DSP和FPGA的信息化发射平台多协议网关设计 [J], 周永明;刘云秋;许进亮;李向阳;刘显勤因版权原因,仅展示原文概要,查看原文内容请购买。

高级数据链路控制规程(HDLC)

高级数据链路控制规程(HDLC)1.HDLC的特征HDLC是面向比特的传输控制规程,以帧为单位传输数据信息和控制信息,其发送方式为连续发送(一边发一边等对方的回答),传输效率比较高。

2.链路结构HDLC规定链路结构可以分为不平衡型、对称型和平衡型3种。

①不平衡型链路结构由一个主站和多个次站构成(点对多点结构)②对称型链路结构链路两端的站均由主站和次站叠合而成。

命令和响应都是通过同一条物理链路传输。

③平衡型链路结构链路两端均由组合站构成,它们处于同等地位,共同负责链路控制。

每个组合站均能以半双工或全双工的方式向对方发送命令、响应和数据。

3.操作方式与非操作方式HDLC为通信操作定义了两种类型,即操作方式和非操作方式。

(1) 操作方式操作方式有3种:正常响应方式(NRM)异步响应方式(ARM)异步平衡方式(ABM)(2) 非操作方式非操作方式也有3种:正常断开方式(NDM)异步断开方式(ADM)初始化方式(IM)4.HDLC的帧结构在HDLC中,在链路上以帧作为作为传输信息的基本单位。

基本格式5-16 帧的基本格式各字段的作用:(1)标志字段(F)固定为01111110,称为F标志。

用于帧同步,表示一帧的开始和结束。

透明传输:两个F字段之间不允许出现01111110图形。

保证措施:“0”插入和删除技术解决方式:在发送站将数据信息和控制信息组成帧后,检查两个F之间的字段,若有5个连“1”就在第5个“1”之后插入一个“0”。

在接收站根据F识别出一个帧的开始和结束后,对接收帧的比特序列进行检查,当发现起始标志和结束标志之间的序列中有连续5个“1”时,自动将其后的“0”删去,这样可使HDLC帧所传送的用户信息内容不受任何限制。

(2)地址字段(A)地址字段表示数据链路上发送站和接收站的地址。

当站的个数大于256个时,可使用扩充字段,扩充为两个字节(3)控制字段(C)控制字段为8bit,用于表示帧类型、帧编号以及命令、响应等。

HDLC的FPGA实现方法

HDLC的FPGA实现方法

王喜;吴祖民;魏武

【期刊名称】《通信与广播电视》

【年(卷),期】2005(000)003

【摘要】HDLC(高级数据链路控制)的一般实现方法为采用ASIC器件和软件编程等。

应用ASIC器件时设计简单,但灵活性较差;软件编程方法灵活,但占用处理器资源多。

执行速度慢,实时性不易预测。

而FPGA器件则采用硬件处理技术,可以反复编程,能够兼顾速度和灵活性,并能多路并行处理,实时性能能够预测和仿真。

本设计采用Altera公司的FPGA芯片,在QUARTUSⅡ软件平台上实现了

多路HDLC电路的设计,并已在某通信产品中应用成功。

【总页数】7页(P23-29)

【作者】王喜;吴祖民;魏武

【作者单位】熊猫军通四部助理工程师

【正文语种】中文

【中图分类】TN919

【相关文献】

1.基于FPGA的USB-HDLC协议转换器的设计与实现 [J], 杨峰;秦兆涛

2.基于FPGA技术的异步转同步HDLC通信卡实现方法 [J], 王琼;李增有

3.基于FPGA+ARM的HDLC协议控制器的设计与实现 [J], 杨尧;赵立立;侯翔昊

4.HDLC协议的FPGA实现方法 [J], 刘文学;郭玉忠;姜琳琳

5.基于FPGA技术的异步转同步HDLC通信卡实现方法 [J], 王琼;李增有

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用FPGA+DSP实现HDLC(高级数据链路控制)功能

引言

HDLC的ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于

特定用途的大批量产品中。

但由于HDLC标准的文本较多,ASIC芯片出于专

用性的目的难以通用于不同版本,缺乏应用灵活性。

有的芯片公司还有自己的

标准,对HDLC的CRC(循环冗余码校验)序列生成多项式等有不同的规定。

专

用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO(先进先出存储器)可用。

对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC再外接存储器或其他电路,ASIC的简单易用性就被抵销掉了。

HDLC的软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC

应用。

但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不

易预测。

纯软件HDLC一般只能用于个别路数的低速信号处理。

FPGA采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼

顾速度和灵活性,并能并行处理多路信号,实时性能能够预测和仿真。

DSP采用软件技术处理信号,也可以反复编程使用。

DSP、FPGA芯片

虽成本略微高于ASIC芯片,但具有货源畅通、可多次编程使用等优点。

在中

小批量通信产品的设计生产中,用FPGA和DSP实现HDLC功能是一种值得

采用的方法。

HDLC的帧结构和CRC校验

为了使FPGA的设计能够实现HDLC的基本功能并能按照各项标准的规定灵活采用不同的CRC校验算法,首先看一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组。