MTK平台射频高速PCB设计

射频电路PCB设计处理技巧

射频电路PCB设计处理技巧1.地线设计:射频信号的传输对地线的布局和设计要求较高。

尽量使用多层板设计,确保地线的良好连接。

地线应该是厚而宽的,并且应该避免地线上的任何断点或改变形状的地方。

减少地线的长度,以降低地线的阻抗。

对于高频信号,建议使用分割式地线,即将地线分为多段,以减少反射和传导电磁干扰。

2.信号线和电源线的隔离:信号线和电源线在PCB上布局时应尽量相隔一定距离,尤其是高频信号线和高功率电源线。

这样可以减少信号线受到电源线干扰的可能性。

如果无法避免信号线和电源线的交叉,可以采用屏蔽罩、地线隔离等方法来降低干扰。

3.分割信号层和电源层:在多层板设计中,应尽量将信号层和电源层分离。

这样可以避免电源线的干扰对信号的影响。

当然,分割信号层和电源层时需要注意地线的布置,在高频电路中,应将地线布置在相对靠近信号层的位置。

4.PCB阻抗匹配:射频信号的传输需要保持恒定的阻抗,以避免反射和能量损失。

在设计PCB时,可以通过合理选择布线宽度、地线间距等参数来匹配所需的阻抗。

同时,为了减少匹配阻抗带来的干扰,可以在射频电路上添加滤波电容或电感等组件。

5.规避时钟信号干扰:时钟信号在高频射频电路中很容易产生干扰。

为了规避时钟信号干扰,可以在设计PCB时将时钟线与其他信号线相隔离,尽量减少与时钟信号平行的信号线的长度。

同时,可以在时钟信号线旁边添加地线来降低干扰。

6.良好的电源和接地规划:良好的电源和接地规划对射频电路的性能和稳定性至关重要。

尽量减少电源和地线的共享,避免共地引起的干扰。

可以使用独立的电源线来供应射频电路。

此外,电源和地线的连接处应采用短而宽的线路,以降低阻抗。

7.屏蔽处理:在高频射频电路设计中,经常会遇到需要屏蔽的情况。

这时可以使用屏蔽罩或屏蔽板来将信号线隔离开来,避免干扰。

屏蔽罩可以是金属板,也可以是金属层布膜,关键是要保证良好的接地。

8.热管理:在射频电路中,发热问题可能会导致性能下降。

联发科MTK平台发展,各芯片功能介绍及MTK工程模式祥表

┏━设备

┃ ┣━LCD---液晶显示屏(Liquid Crystal Display )

┃ ┃ ┗━主屏幕

┃ ┃ ┣━Set Contrast---设置对比度

┃ ┃ ┃ ┣━LEV 2:3400000

┃ ┃ ┃ ┣━LEV 3:3640000

┃ ┃ ┃ ┣━LEV 4:3650000

┃ ┃ ┃ ┣━LEV 5:3700000

┃ ┃ ┃ ┣━LEV 6:3790000

┃ ┃ ┃ ┣━LEV 7:3890000

┃ ┃ ┃ ┣━LEV 8:9999999

2、 MT6305、MT6305B为电源管理芯片;

3、 MT6129为射频芯片,转换射频信号 ;

RF3146(7×7mm)、RF3146D(双频)、RF3166(6×6mm)为RFMD(美国RF微器件公司在有设五个设计中心,专用射频集成电路(RFIC)供应商 RF Micro Devices, Inc. 公司(Nasdaq 股市代号:RFMD))的功放;

┃ ┃ ┃ ┣━LEV 9:9999999

┃ ┃ ┃ ┗━LEV 10:9999999

┃ ┃ ┣━PWM 1

┃ ┃ ┃ ┣━[Freq 1] 20000

┃ ┃ ┃ ┣━[Duty 1] 20

┃ ┃ ┃ ┣━[Freq 2] 20000

┃ ┃ ┃ ┣━[Duty 2] 40

*#035670766*001# *#035670766*002#

MT芯片的出厂密码为1122!

有一些机器开机输入*#66*#不进测试的。可以在开机瞬间,在按键灯亮和开机音乐响的时候快速按*#*#............*#就可进入测试工程模式祥表:

MTK平台射频电路原理

MTK平台射频电路的关键技术

01

信号完整性技术

MTK平台射频电路采用信号完整 性技术,保证信号在传输过程中

的完整性和稳定性。

03

低噪声放大技术

MTK平台射频电路采用低噪声放 大技术,提高信号的接收灵敏度

。

02

电磁兼容性技术

MTK平台射频电路采用电磁兼容 性技术,降低电路之间的电磁干MTK平台的智能电视解决方案为用户提供 流畅的操作体验和丰富的多媒体功能。

此外,MTK平台还应用于物联网、智能家 居、车载娱乐系统等领域。

02

射频电路基本原理

射频电路的定义与特点

定义

射频电路是指处理射频信号的电子电 路,通常工作在无线通信频段。

特点

射频信号具有频率高、波长短、传播 特性与低频信号不同等特点,因此射 频电路的设计和优化与低频电路有所 不同。

MTK平台射频电路的设计流程

原理图设计

根据需求分析结果,设计出相 应的原理图。

PCB板设计

根据仿真测试结果,设计出相 应的PCB板。

需求分析

根据通信系统的需求,分析射 频电路的功能和技术指标。

仿真测试

对设计的原理图进行仿真测试, 验证其功能和技术指标是否满 足要求。

制作与调试

制作出PCB板上的射频电路, 并进行调试,确保其性能稳定 可靠。

考虑材料特性

根据不同材料的电磁特性,选择合 适的介质、导线和封装,以满足射 频电路的性能要求。

MTK平台射频电路的实现流程

需求分析

明确射频电路的功能需求和技术指标,如工作频率、增益、噪声系数 等。

原理图设计

根据需求分析,使用电路设计软件绘制原理图,并完成元件参数的计 算和选择。

PCB天线设计及射频布局设计指南

引言:概述:PCB天线设计是通过在PCB上布局电路来实现无线电频率的传输和接收。

天线设计的质量直接影响到设备的通信质量和性能。

射频布局是指在PCB电路板上布置射频元件以保证信号传输的稳定性和减少信号干扰。

好的射频布局能够降低噪声和干扰,提高设备的接收灵敏度和发送功率。

正文:一、基本原理1.1天线类型1.2天线参数1.3天线选择与匹配技术1.3.1频带选择1.3.2阻抗匹配1.3.3尺寸约束1.3.4天线方向性1.3.5天线辐射效率二、PCB天线设计2.1天线形状设计2.2天线位置选择2.3天线尺寸优化2.4天线与其他元件的间距设计2.5天线与地板的设计三、射频布局设计3.1射频信号布局准则3.2射频焊盘布局3.3射频走线布局3.4射频电源布局3.5射频地面布局四、PCB天线设计常见问题与解决方法4.1天线频率偏差问题4.2天线辐射模式问题4.3天线干扰和噪声问题4.4天线尺寸限制问题4.5天线输出功率问题五、实例与应用5.1手持设备天线设计实例5.2无线通信设备天线设计实例5.3汽车电子设备天线设计实例5.4IoT设备天线设计实例5.55G通信设备天线设计实例总结:PCB天线设计和射频布局的优化对设备的性能提升至关重要。

通过了解天线设计的基本原理和射频布局技术,工程师们能够更好地实施天线设计和射频布局。

本文从天线基本原理、PCB天线设计、射频布局设计、常见问题与解决方法以及实例与应用方面进行了详细的阐述。

希望这些设计指南能够帮助工程师们更好地进行PCB天线设计和射频布局,提高设备的性能和通信质量。

HY016射频设计4_静态NV生成说明

HY016射频设计4_静态NV生成说明在PCB投板的两周间隙中,射频工程师可以先把静态NV和校准文件准备起来。

这样等板子贴片回来后就可以下载静态NV,验证原理图设计了。

本文对静态NV进行介绍,并详细说明如何生成HY016的静态NV。

目前高通平台,绝大部分射频相关参数是通过NV来进行配置的。

一份静态NV包括如下部分:1、硬件设计对应的RF Card(NV1878)2、射频电路支持的所有频段,包括2G/3G/4G,发射/主接收/分集接收3、每个支持频段的射频相关参数,包括发射和接收的增益等级、切换点、最大最小发射功率、温度补偿、时序控制等一份正确的静态NV是要让射频电路跑起来的必要条件。

RF CardRF Card是硬件和驱动正确关联的关键。

每份不同的硬件设计采用不同的RF Card,比如有些是WTR2965+QFE4373的,有些是WTR4905+QFE4320的,有些支持南美频段,有些支持国内CA。

这些不同的硬件设计,都对应不同的RF Card。

驱动则根据不同的RF Card对硬件做相应的配置。

所以RF Card弄错,往往都会导致开机死机。

RF Card保持在NV1878中。

以HY016南美全频段为例,射频和驱动约定这个设计的RF Card是111,即NV1878=111。

在这个RF Card中,射频采用WTR4905+RDA PhaseII来实现南美全频段。

驱动也需要在这个RF Card下修改代码,使之和硬件相匹配,重点是通过MIPI 和GPIO对芯片的模式和频段进行控制。

若我们使用的是高通的参考设计,那高通会有默认原理图和驱动代码,我们只要沿用这份原理图的RF Card即可。

以8909 QCN_XTT_MBN_NV_sysRFCalDll_8909_JO.3.0_r00046为例,在软件代码如下路径中可以看到高通支持的RFCardQCN_XTT_MBN_NV_sysRFCalDll_8909_JO.3.0_r00046\modem_proc\rftarget_jolokia\msm8909\ qcn(驱动每个基线都会把这部分文档上传到服务器)但这些RF Card都是采用高通的PA进行设计的电路,在成本上会贵不少。

在高速(>100MHz)高密度PCB设计时需要注意串扰的几个方面

在高速(>100MHz)高密度PCB设计时需要注意

串扰的几个方面

在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请介绍在高速(>100MHz)高密度PCB设计中的技巧?

在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。

以下提供几个注意的地方:

1.控制走线特性阻抗的连续与匹配。

2.走线间距的大小。

一般常看到的间距为两倍线宽。

可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。

不同芯片信号的结果可能不同。

3.选择适当的端接方式。

MTK平台射频问题

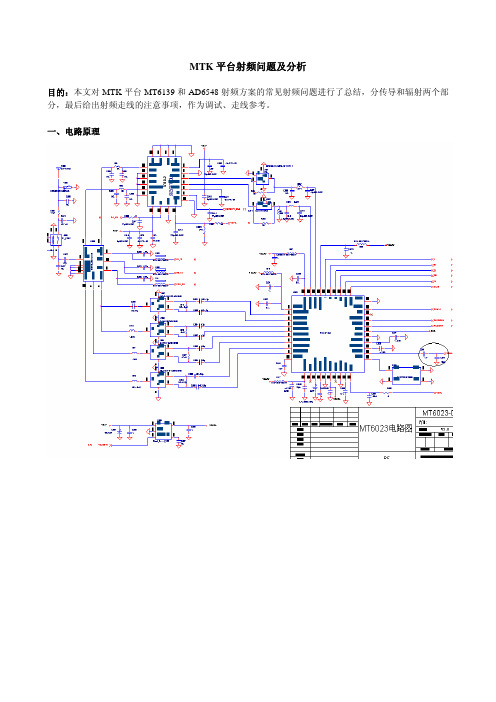

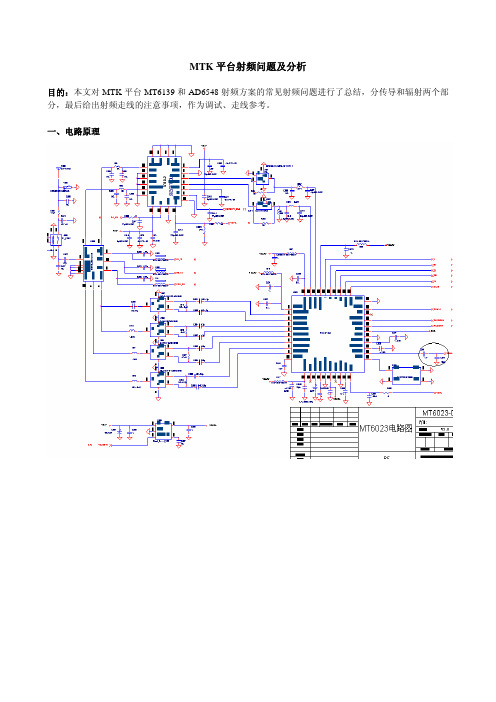

原因分析: 导致传导的相位误差、调制谱 FAIL 需要对 MT6139 的发射架构进行了解。MT6139 的发射部分采用

的 DCT 的发射架构,VCO 的频率范围分别如下:

图. MT6139 和 PA 之间的信号 (红色是 MT6139 到 PA 的信号,黑色是 PA 反射回 MT6139 的信号)

GSM 的 PA 是非线性 PA,虽然效率比较高,但 PA 在大功率的情况下将产生比较大的谐波成分。PA 发射出来的谐波成分沿上图黑色线的传导路径返回了 MT6139,而 MT6139 的 VCO 电路比较容易受到 PA 反射回来的谐波的干扰,产生 VCO PULLING 现象,导致了调制特性变差。对于 GSM900 频段,对调制特 性影响比较大的是反射回来的四次谐波;对于 DCS 频段,对调制特性影响比较大的是反射回来的二次谐 波。

按键灯亮和屏亮的时候,调制谱会出现偏大现象,特别是在中心频率+-1MHz 到+-1.8MHz 的范围。待

按键灯灭之后调制谱指标变小,在屏灭之后调制谱指标进一步的变小,回复到正常的水平。

图. 调制谱在低功率等级 FAIL 原因分析:

按键灯的电源使用 MT6318 的输出,经过 Memory,带进干扰,尝试用改善电源的办法解决。 解决办法:

DCS 频段 PA 与 ASM 之间的 PI 匹配电路

PA 与 ASM 之间匹配电路示意图 解决办法:

调试 PA 和 ASM 之间的 PI 匹配电路,满足当增加该 DAC 数值到最大 1023 的时候,用 8960 测试到的 GSM 各信道最大功率不能达到 33dBn,DCS 各信道最大功率不能达到 31dBm。

射频电路PCB设计布线规范

射频电路PCB设计布线规范1.地面平面布线规范:射频电路的地面平面应尽可能连续,尽量避免划分为多个独立的区域。

如果必须划分地面平面,应使用稳定的参考平面连接它们。

同时,避免地面平面上存在孔洞。

2.射频组件布局规范:高频组件(如射频放大器、射频滤波器等)应尽可能靠近射频天线或射频输入/输出端口。

此外,不同射频组件之间应保持一定的间距,以防止互相的干扰。

3.射频线宽规范:射频线的宽度应根据设计的频率和所使用的介质来确定。

通常,较高的频率需要更宽的线宽,以减小线路的损耗。

具体的线宽可以根据射频设计手册或仿真工具来计算。

4.射频线与地面的连接规范:射频线应尽可能与地面平面接触,以提供一个低阻抗的返回路径。

为了实现这一点,可以采用地面孔和连续的焊盘等设计。

此外,应避免射频线与其他信号线和电源线的交叉。

5.射频线的走线路径规范:射频线应尽量避免在长距离内平行走线,以减小串扰的可能性。

同时,应避免射频线与其他信号线和电源线的交叉,以减小互相的干扰。

6.射频线和射频组件的焊盘设计规范:射频线和射频组件的焊盘应尽可能保持积极的接触,以减小传输信号时的损耗。

可以使用大面积的焊盘和合适的焊料来提高焊接质量。

7.射频电路的屏蔽设计规范:对于敏感的射频电路,应采取屏蔽措施以减小干扰的影响。

可以使用金属屏蔽罩、屏蔽接地平面等方式来实现屏蔽设计。

8.射频电路的电感和电容布局规范:射频电路中的电感和电容元件的位置应遵循尽可能短的连接原则,以减小这些元件的串扰和互相干扰的可能性。

综上所述,射频电路PCB设计布线规范主要包括地面平面布线规范、射频组件布局规范、射频线宽规范、射频线和地面的连接规范、射频线的走线路径规范、射频线和射频组件的焊盘设计规范、射频电路的屏蔽设计规范、射频电路的电感和电容布局规范等。

遵循这些规范可以提高射频电路的性能和可靠性,减小电路的信号损耗和干扰问题。

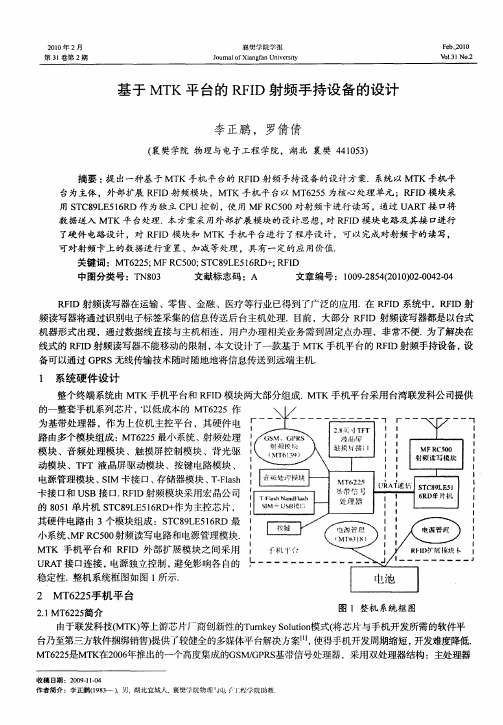

基于MTK平台的RFID射频手持设备的设计

中图分类 号 :T 0 N8 3

文献标 志码 :A

文章编 号 :10 .8 42 1)20 4 -4 0 92 5 (0 00 —0 20

R I 射 频读写 器在运输 、零 售 、金 融 、医疗 等行 业 已得 到 了广泛 的应用 . R I 系统 中 ,R I FD 在 FD FD射

频读写器将通过识别电子标签采集的信息传送后台主机处理.目前 ,大部分 R I 射频读写器都是以台式 FD 机器形式出现 ,通过数据线直接与主机相连,用户办理相关业务需到固定点办理 ,非常不便. 了解决在 为 线式的 R I FDห้องสมุดไป่ตู้频读写器不能移动的限制, 本文设计了一款基于 MT K手机平台的 R I FD射频手持设备 , 设 备可以通过 G R 无线传输技术随时随地地将信息传送到远端主机. PS

李 正 鹏 ,等 :基 于 MT 平 台的 R I 射 频 手 持 设 备 的 设 计 K FD

是AR  ̄一,提供 整机 的主要 控制功 能 ; 一个处 理器是数 字信 号处理器 ( P , 于处 理信道 编译 码 、语 M7 S 另 DS ) 用 音 的压缩 与扩展 . 62 采用2 6B l F G MT 2 5 4 一al 的T B A封装 ,内部集 成 了非 常丰富 固定 的接 口. 计 中用到 的接 口 设 有存储 器接 口、SM卡接 口 、 盘扫描 器 、UAR I 键 T、L D接 口、基带前 端 、 C 音频 前端 、射频控 制 、电源管理 【 2 】 .

21 0 0年 2月

襄 樊学 院学报

J u a f a g a ie st o r l n f n Un v ri n o Xi y

F b, 0 0 e . 1 2

第 3 卷第 2期 1

[电子工程] 案例图解射频PCB设计要点

![[电子工程] 案例图解射频PCB设计要点](https://img.taocdn.com/s3/m/a14f12e3bceb19e8b8f6bafb.png)

在电子产品和设备中,电路板是一个不可缺少的部件,它起着电路系统的电气和机械等的连接作用。

如何将电路中的元器件按照一定的要求,在PCB上排列组合起来,是PCB设计师的主要任务之一。

布局设计不是简单的将元器件在PCB上排列起来,或者电路得以连通就行的。

实践证明一个良好的电路设计,必须有合理的元器件布局,才能使电路系统在实体组合后达到稳定、可靠的工作。

反之,如果元器件布局不合理,它将影响到电路板的工作性能,乃至不能工作。

尤其是在广泛采用集成器件的今天,如果集成电路仍用接线板的方式进行安装,那么,不仅电路的体积庞大,而且无法稳定的进行工作。

因此,在产品设计过程中,布局设计和电路设计前具有同样重要的地位。

下面就射频PCB设计注意事项做个简单的介绍。

一、布局注意事项1)结构设计要求在PCB布局之前需要弄清楚产品的结构。

结构需要在PCB板上体现出来(结构与PCB接触部分,即腔壳位置及形状)。

比如腔壳的外边厚度大小,中间隔腔的厚度大小,倒角半径大小和隔腔上的螺钉大小等等(换句话说,结构设计是根据完成后的PCB上所画的轮廓(结构部分)进行具体设计的(如果结构已批量开模具,就另当别论了))(螺钉类型有M2\M2.5\M3\M4等)。

一般情况,外边腔厚度为4mm;内腔宽度为3mm(点胶工艺的为2mm);倒角半径2.5mm。

以PCB板的左下角为原点,隔腔在PCB上的位置需在格点0.5的整数倍上,最少需要做到格点为0.1的整数倍上。

这样有利于结构加工,误差控制比较精确。

当然,这需要根据具体产品的类型来设计。

如下图所示:(PCB设计完成后的结构轮廓图)2)布局要求优先对射频链路进行布局,然后对其它电路进行布局。

射频链路布局注意事项根据原理图的先后顺序(输入到输出,包括每个元件的先后位置和元件与元件之间的间距都有讲究的。

有的元件与元件之间距离不宜过大,比如π网。

)进行布局,布局成“一”字形或者“L”形。

具体如下图所示:在实际的射频链路布局中,因受产品的空间限制,不可能完全实现“一”字型布局,这就迫使我们将布局成“U”形。

射频板PCB工艺设计规范

印制电路板设计规范——工艺性要求(仅适用射频板)目次前言 (II)1 范围 (1)2 规范性引用文件 (1)3 术语和定义 (1)4 印制板基板 (3)5 PCB设计基本工艺要求 (5)6 拼板设计 (6)7 射频元器件的选用原则 (7)8 射频板布局设计 (7)9 射频板布线设计 (9)10 射频PCB设计的EMC (14)11 射频板ESD工艺 (18)12 表面贴装元件的焊盘设计 (19)13 射频板阻焊层设计 (19)附录A (21)附录B (23)附录C (24)附录D (27)附录E (31)附录F (32)附录G (33)附录H (39)前言1范围本标准规定了射频电路板设计应遵守的基本工艺要求。

本标准适用于射频电路板的PCB设计。

2规范性引用文件IPC-SM-782 Surface Mount Design and Land Pattern StandardIPC 2252-2002 Design Guide for RF-Microwave Circuit Boards3术语和定义下列术语和定义适用于本标准。

3.1微波 Microwaves微波是电磁波按频谱划分的定义,是指波长从1m至0.1mm范围内的电磁波, 其相应的频率从0.3GHz至3000GHz。

这段电磁频谱包括分米波(频率从0.3GHz至3GHz)\厘米波(频率从3GHz至30GHz)\毫米波(频率从30GHz至300GHz)和亚毫米波(频率从300GHz至3000GHz,有些文献中微波定义不含此段)四个波段(含上限,不含下限)。

具有似光性、似声性、穿透性、非电离性、信息性五大特点。

3.2射频 RF(Radio Frequency)射频是电磁波按应用划分的定义,专指具有一定波长可用于无线电通信的电磁波。

频率范围定义比较混乱,资料中有30MHz至3GHz, 也有300MHz至40GHz,与微波有重叠;另有一种按频谱划分的定义, 是指波长从1兆m至1m范围内的电磁波, 其相应的频率从30Hz至300MHz;射频(RF)与微波的频率界限比较模糊,并且随着器件技术和设计方法的进步还有所变化。

射频电路PCB设计(板材,设计流程,布局,布线

为保证电路性能,在进行射频电路PCB设计时应考虑电磁兼容性,因而重点讨论元器件的布线原则来达到电磁兼容的目的。

关键词:射频电路PCB 电磁兼容布局随着通信技术的发展,手持无线射频电路技术运用越来越广,如:无线寻呼机、手机、无线PDA等,其中的射频电路的性能指标直接影响整个产品的质量。

这些掌上产品的一个最大特点就是小型化,而小型化意味着元器件的密度很大,这使得元器件(包括SMD、SMC、裸片等)的相互干扰十分突出。

电磁干扰信号如果处理不当,可能造成整个电路系统的无法正常工作,因此,如何防止和抑制电磁干扰,提高电磁兼容性,就成为设计射频电路PCB时的一个非常重要的课题。

同一电路,不同的PCB设计结构,其性能指标会相差很大。

本讨论采用Protel99 SE软件进行掌上产品的射频电路PCB设计时,如果最大限度地实现电路的性能指标,以达到电磁兼容要求。

1 板材的选择印刷电路板的基材包括有机类与无机类两大类。

基材中最重要的性能是介电常数εr、耗散因子(或称介质损耗)tanδ、热膨胀系数CET和吸湿率。

其中εr影响电路阻抗及信号传输速率。

对于高频电路,介电常数公差是首要考虑的更关键因素,应选择介电常数公差小的基材。

2 PCB设计流程由于Protel99 SE软件的使用与Protel 98等软件不同,因此,首先简要讨论采用Protel99 SE软件进行PCB设计的流程。

①由于Protel99 SE采用的是工程(PROJECT)数据库模式管理,在Windows 99下是隐含的,所以应先键立1个数据库文件用于管理所设计的电路原理图与PCB 版图。

②原理图的设计。

为了可以实现网络连接,在进行原理设计之间,所用到的元器件都必须在元器件库中存在,否则,应在SCHLIB中做出所需的元器件并存入库文件中。

然后,只需从元器件库中调用所需的元器件,并根据所设计的电路图进行连接即可。

③原理图设计完成后,可形成一个网络表以备进行PCB设计时使用。

PCB-射频PCB设计要求

、印制电路板设计规范——射频PCB 设计要求2005-XX-XX 发布 2005-XX-XX 实施xxx** xxx x x xx 有限公司企业标准(设计技术标准)xxxxxxxxxx 发次目 次前言 (IV)使用说明 (VIII)1范围 (5)2规范性引用文件 (5)3定义、符号和缩略语 (5)3.1微波Microwaves (5)3.2射频Radio Frequency RF (缩写为:RF) (5)3.3印制电路板Printed Circuit Board (缩写为:PCB) (6)3.4阻抗impedance (6)3.5微带线Microstrip (6)3.6趋肤效应 (6)3.7耗散因数(介质损耗角) Dissipation factor (缩写为:Df) (6)3.8介电常数Permittivity (缩写为:Dk) (6)3.9“Q”品质因素Quality Factor (简称为Q-Factor) (6)3.10电磁干扰electromagnetic interference (缩写为:EMI) (6)3.11电磁兼容性electromagnetic compatibility (缩写为:EMC) (6)3.12PCB寄生参数 (7)3.13噪声Noise (7)3.14接地Grounding (7)3.15屏蔽 Shielding (7)3.16屏蔽罩EMI shielding (7)3.17耦合 (7)3.18静电放电electrostatic discharge(缩写为:ESD) (7)3.19波长wavelength (缩写为:λ) (7)4标准维护办法 (8)5射频印制板加工信息 (8)5.1射频电路对基材的要求 (8)5.2常用射频板材的特性和选用 (8)5.3PCB厚度 (8)5.4铜箔厚度 (9)5.5RF丝印字符的设计要求 (9)5.6射频板阻焊层设计 (9)5.7RF PCB其他设计工艺要求 (10)6射频板布局设计 (10)6.1射频板的布局原则 (10)6.1.1布局方案确定 (10)6.1.2物理分区和电气分区 (10)6.1.3物理分区原则 (10)6.1.4电气分区原则 (10)6.2射频板的通用布局要求 (11)6.2.1RF链路一字布局 (11)6.2.2RF链路L形布局 (11)6.2.3元器件布局通用要求 (11)6.2.4金属屏蔽腔对PCB布局的工艺要求 (12)6.2.5不同频率单元混排 (13)6.3常用射频模块电路推荐布局方案 (13)6.3.1频综布局 (13)6.3.2混频器(MIXER)电路布局 (15)6.3.3声表滤波器电路布局 (15)6.3.4放大器单元电路的布局 (16)6.3.5功放管单元电路的布局 (18)7射频板布线设计 (19)7.1射频板叠层结构 (19)7.2射频板布线原则 (19)7.3传输微带线的阻抗控制 (20)7.4射频板布线要求 (21)7.4.1转角 (21)7.4.2微带线布线 (21)7.4.3带状线布线 (22)7.4.4微带线耦合器 (22)7.4.5微带线功分器 (23)7.4.6λ/4微带线 (23)7.4.7渐变线 (23)8过孔与接地 (23)8.1射频信号走线过孔 (23)8.2接地过孔 (24)8.2.1射频器件焊盘与过孔的设计要求 (24)8.2.2单板边缘的接地过孔 (25)8.2.3屏蔽腔的接地过孔 (25)8.3接地 (25)8.3.1大面积接地 (25)8.3.2分组就近接地 (26)8.3.3射频器件的接地 (26)8.3.4微带电路的接地 (26)8.3.5接地时应注意的问题 (26)8.3.6接地工艺性要求 (26)8.3.7焊盘隔热路径设计 (27)9屏蔽 (27)10射频板ESD工艺 (28)11附录一 射频板材厂家部分型号产品的性能参数介绍 (29)12附录二 常用射频器件手册要求过孔设计方法 (30)前 言言为了规范印制电路板射频PCB的设计要求,提高射频印制电路板的设计质量,特编制本标准。

MTK平台射频方案简介

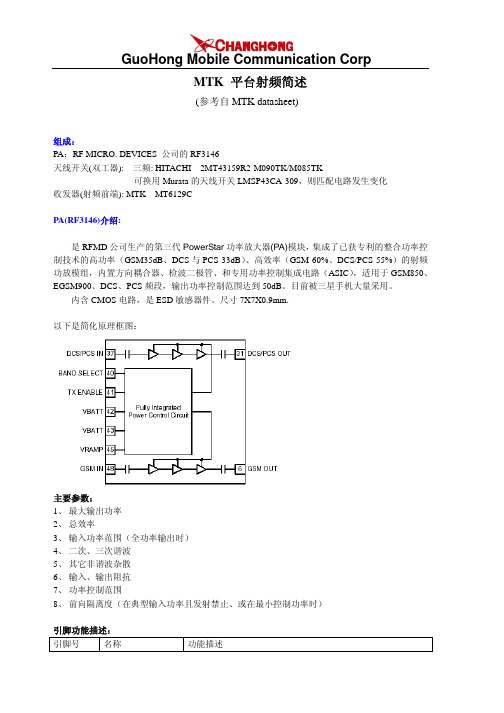

MTK 平台射频简述(参考自MTK datasheet)组成:PA:RF MICRO. DEVICES 公司的RF3146天线开关(双工器): 三频: HITACHI 2MT43159R2-M090TK/M085TK可换用Murata的天线开关LMSP43CA-309,则匹配电路发生变化收发器(射频前端): MTK MT6129CPA(RF3146)介绍:是RFMD公司生产的第三代PowerStar功率放大器(PA)模块,集成了已获专利的整合功率控制技术的高功率(GSM35dB、DCS与PCS 33dB)、高效率(GSM 60%、DCS/PCS 55%)的射频功放模组,内置方向耦合器、检波二极管、和专用功率控制集成电路(ASIC),适用于GSM850、EGSM900、DCS、PCS频段,输出功率控制范围达到50dB。

目前被三星手机大量采用。

内含CMOS电路,是ESD敏感器件。

尺寸7X7X0.9mm.以下是简化原理框图:主要参数:1、最大输出功率2、总效率3、输入功率范围(全功率输出时)4、二次、三次谐波5、其它非谐波杂散6、输入、输出阻抗7、功率控制范围8、前向隔离度(在典型输入功率且发射禁止、或在最小控制功率时)引脚功能描述:引脚号名称功能描述2 VCC2GSM GSM驱动级的控制电压输入,需连接VCCOUT并去耦,分配给功率控制部分GSM频段射频输出脚,匹配与隔直电路内置,输出阻抗50欧6 GSM850/900OUT18 VCC3GSM GSM输出级的控制电压输入,需连接VCCOUT并去耦,分配给功率控制部分OUT 流入VCC2、VCC3的控制电压输出,分配给功率控制部分,19、20 VCC不能接其它引脚DCS/PCS输出级的控制电压输入,需连接VCCOUT并去耦,DCS/PCS21 VCC3分配给功率控制部分DCS/PCS频段射频输出脚,匹配与隔直电路内置,输出阻抗50 31 DCS/PCSOUT欧35 VCC2DCS/PCS驱动级的控制电压输入,需连接VCCOUT并去耦,DCS/PCS分配给功率控制部分IN DCS/PCS频段的射频输入脚,输入阻抗50欧37 DCS/PCSGSM、DCS/PCS预放大级的控制电压,内部提供,需加去耦DCS/PCS39 VCC1SEL 允许外部控制选择频段,“0”为GSM,“1”为DCS/PCS40 BANDENABLE 允许PA模组工作,“1”允许。

(完整版)射频PCB设计(1)

模组射频PCB 设计随着物联网技术的兴起,现在的电子产品搭载无线通讯功能是越来越普遍了,而无线通讯技术是依赖于PCB上的射频电路来实现的,并且需要专业的设计和仿真分析工具。

现将模组射频电路PCB 设计分享给大家。

走线原则对于自身没有连接器的模块,需通过 RF 走线和天线馈点或者连接器连接,所以 RF 线推荐走微带线,越短越好,差损控制在 0.2dB 以内,并且阻抗控制在50Ω。

在模块和天线连接器(或馈点)之间预留一个π型电路(两个并行器件接地脚要直接接到主地)供天线调试。

在 PCB 走线时,此信号走线控制50Ω。

产品的射频性能与此走线密切相关。

在 PCB 板上影响此走线阻抗的因素如下:●走线的宽度和厚度●介质介电常数和厚度●焊盘的厚度●与地线的距离●附近的走线阻抗设计两个天线接口的 RF 信号线阻抗都需要控制50Ω。

在实际应用中根据 PCB 的其他参数如参考层厚度、层数和叠层等都会影响到 RF 的走线方式,不同的情况参考 GND 层不一样,走线差距也将很大。

3W 原则多层板设计天线 RF 信号在 PCB 上走线时,首先考虑的是满足基本的“3W 原则”。

为了减少线间串扰,应保证线间距足够大,如果线中心距不少 3 倍线宽时,则可保持 70%的线间电场不互相干扰,称为“3W 原则”。

3W 原则示意图射频PCB Layout 部分●射频走线尽量做50欧姆阻抗,如果无关做到,应将射频走线宽度保持在0.5mm~1mm距地安全距离也要保持在0.5mm~1mm,周围打满地孔●射频座子的地建议尽量净空●过孔焊盘建议用泪滴结束射频走线应尽量远离电源,SIM卡,时钟,高速数字信号;保其不对周围器件产生的影响,所以在天线周边建议客户不要放其他元器件,并且 PCB 上的走线尽可能远离 RF 部分。

射频走线应尽量短,遇弯需走蛇形线或圆弧,周围打地孔;两层板阻抗设计因为大部分客户多有用双面板进行设计,所以针对两层板典型的 1.6mm,1.0mm 厚度PCB 设计做实例说明:案例一:PCB 板厚 1.6mm考虑到 PCB 板厚的影响,要完全符合 3W 原则很难实现,既要保证50Ω走线,又要确射频走线过长时,模块测和天线测建议预留匹配电路如果板上空间富裕,优先通过布局实现RF走线的短和直,如果布局空间不允许,需要拐角走线,一定避免直角或45°拐角走线,要走圆弧走线,如果实在要走直角了,可以通过放置元件通过元件的摆位的方式来替代走线来做90°角的转折,这样可以最大化避免阻抗突变造成的信号反射影响。

高频PCB设计-射频电路的布局的走线

高频PCB设计:射频电路的布局的走线1、射频电路的布局和连接尽可能地短由于传输线拐角处的阻抗突变会造成信号反射,高频信号将作为电磁场能量辐射到空间中。

结果,经“拐角”之后的信号电平值可能下降。

因此,在设计高频电路时,必须精心设计RF布局以使得RF走线拐角角度尽可能的小。

设计RF电路时,如果板上有足够的空间,则将RF相关元器件布置成尽可能直线化。

通过直线化布局布线布线,可以避免信号反射,防止信号电平值降低,以满足设计指标。

设计要点:在低频电路的时,信号走线成直角也可以正常工作。

然而,在高频电路中,即使走线铜箔宽度的细微变化也会产生影响,因为走线宽度变化,特征阻抗就会受到影响,发生信号反射,降低信号电平值,达不到设计指标。

2、在RF走线的拐角处通过放置元件或者圆弧走线的方式来降低特性阻抗突变造成的影响还是围绕老wu第一点说的【避免特征阻抗突变】的原则,如果板上空间富裕,优先通过布局实现RF走线的短和直,如果布局空间不允许,需要拐角走线,一定避免直角或45°拐角走线,要走圆弧走线,如果实在要走直角了,可以通过放置元件通过元件的摆位的方式来替代走线来做90°角的转折,这样可以最大化避免阻抗突变造成的信号反射影响。

设计要点:在高频电路的情况下,重要的是改善RF线路的布局,即遵循【避免特征阻抗突变】的原则3、为接地焊盘单独接地,避免共用接地过孔设计高频电路时,必须认真处理RF信号走线和GND之间的连接。

在上图的反例中,RF元件的接地焊盘共用一个接地过孔与GND平面连接。

下图的改进实例中,为每个接地焊盘就近打了接地过孔与GND平面连接,接地环路更小,将噪声降至最低。

设计要点:与常规电路相比,高频电路对于与GND的连接必须严格处理,为每个接地焊盘单独提供一个接地过孔以最短的途径与地平面进行连接。

4、射频巴伦差分走线要保持对称设计高频电路时,必须注意同一电路部分的接线。

比如上面的反例图示是射频巴伦(balun)电路,左右走线不对称。

射频 pcb layout 设计规则-概述说明以及解释

射频pcb layout 设计规则-概述说明以及解释1.引言1.1 概述概述部分主要介绍了射频PCB布局设计规则这篇长文的背景和主要内容。

在现代电子设备中,无线通信技术得到了广泛的应用与发展。

射频电路作为其中的一个重要组成部分,对于无线通信的性能起到关键影响。

而射频PCB布局设计正是为了优化射频电路的性能而提出的一种设计规则。

射频PCB布局设计规则是针对射频电路在PCB板上的布局位置、布线方式以及各器件之间的互连关系等方面制定的一系列规范和原则。

通过合理的布局设计,可以减小射频电路中的信号传输损耗、最大限度地降低噪声干扰和回波等问题,从而提高射频电路的工作效率和可靠性。

本文将重点介绍射频PCB布局设计中的一些重要规则,包括组件布置、信号走线、地平面和分离布局等方面。

具体而言,我们将深入探讨射频器件的布局位置选择、射频信号走线的规则以及如何设计地平面和分离布局来最大程度地减小电磁干扰和回波。

通过详细的说明和实例示范,读者将能够更加深入地理解射频PCB布局设计规则的重要性和应用价值。

同时,本文还将展望未来射频PCB布局设计的发展方向,以期为射频电路设计提供更加详尽和准确的指导。

在本文的后续内容中,我们将逐一介绍这些规则并给出相应的设计建议,希望读者能够从中受益并应用到自己的实际工作中。

1.2 文章结构:本文将分为以下几个部分进行阐述射频PCB布局设计规则。

首先,引言部分将概述本文主要内容,并介绍文章结构。

接着,正文部分将详细探讨射频PCB布局设计的重要性,包括其对系统性能和电磁兼容性的影响。

同时,本节还将介绍射频PCB布局设计的一般原则和技巧,以帮助读者理解和应用这些规则。

最后,在结论部分,我们将对全文进行总结,并展望未来射频PCB布局设计的发展趋势。

通过本文的阐述,读者将能够深入了解射频PCB布局设计的重要性,掌握射频电路布局的基本原则和规则。

这些知识将有助于读者在实际设计中更好地应用射频技术,提高系统的性能和可靠性。

射频PCB设计规范(一)

射频PCB设计规范(⼀)我记得很早以前,我在⽹上发表过多篇有关射频PCB的设计规范。

现在应学员群员⼩强同学的要求,在此总结⼀下最近半年来做射频PCB遇到的⼀些问题,期待⼤家多多砸砖。

1)⼩功率的RF的PCB设计中,主要使⽤标准的FR4材料(绝缘特性好、材质均匀、介电常数ε=4,10%)。

主要使⽤4层~6层板,在成本⾮常敏感的情况下可以使⽤厚度在1mm以下的双⾯板,要保证反⾯是⼀个完整的地层,同时由于双⾯板的厚度在1mm以上,使得地层和信号层之间的FR4介质较厚,为了使得RF信号线阻抗达到50欧,往往信号⾛线的宽度在2mm左右,使得板⼦的空间分布很难控制。

对于四层板,⼀般情况下顶层只⾛RF信号线,第⼆层是完整的地,第三层是电源,底层⼀般⾛控制RF器件状态的数字信号线(⽐如设定ADF4360系列PLL的clk、data、LE信号线。

)第三层的电源最好不要做成⼀个连续的平⾯,⽽是让各个RF器件的电源⾛线呈星型分布,最后接于⼀点。

第三层RF器件的电源⾛线不要和底层的数字线有交叉。

2)对于⼀个混合信号的PCB,RF部分和模拟部分应当远离数字数字部分(这个距离通常在2cm以上,⾄少保证1cm),数字部分的接地应当与RF部分分隔开。

严禁使⽤开关电源直接给RF部分供电。

主要在于开关电源的纹波会将RF部分的信号调制。

这种调制往往会严重破坏射频信号,导致致命的结果。

通常情况下,对于开关电源的输出,可以经过⼤的扼流圈,以及π滤波器,再经过线性稳压的低噪⾳LDO(Micrel的MIC5207、MIC5265系列,对于⾼电压,⼤功率的RF电路,可以考虑使⽤ LM1085、LM1083等)得到供给RF电路的电源。

3)RF的PCB中,各个元件应当紧密地排布,确保各个元件之间的连线最短。

对于ADF4360-7的电路,在pin-9、pin-10引脚上的VCO电感与ADF4360芯⽚间的距离要尽可能的短,保证电感与芯⽚间的连线带来的分布串联电感最⼩。

MTK平台射频问题

图. 低功率等级的 PVT 不平,断成两截 原因分析:按键灯用 MT6318 的电源供电,当按键灯亮的时候,电源被干扰,不稳定导致。 解决办法:改原理图,在按键灯的供电电路加磁珠滤波。

M6025 按键供电原理图改之前

M6025 按键供电原理图改之后

5)低功率等级调制谱 Fail 或偏大的问题(M6036) 现象:

调制谱正常。后分析该电路发现,MT6139 的供点电路的走线有问题:从 MT6223 出来的 VRF 走线直接和 VRF_SENSE 走线在 MT6223 的网络处就连在了一起,正确的走法应该是从 MT6223 出来的 VRF 走线先走 到 MT6139,再从 MT6139 返回走到 MT6223 的 VRF_SENSE PIN 脚。

在按键灯的电源电路部分增加磁珠,减少电源的干扰。 6)电源不稳定引起的调制谱的问题(M7035) 现象:

按照 GSM 规范,调制谱标准规范要求在信道中心频率+-400KHz 位置的发射功率要小于-60dBc,在信 道中心频率+-200KHz 位置的发射功率要小于-30dBc。相位误差指标正常。

原因分析: 相位误差正常,可判断不是 PA 和 TC 之间的匹配电路引起的问题。 M7035 的 MT6139 的供电电源默认使用的是 MT6223 的 VRF 输出。当使用兼容的 LDO 供电的时候,

初次调试的时候 RMS PE 会比较大或者超过 5,Peak PE 会超过 20。同时调制谱指标会大于-60dBc, 有的项目在信道中心频率+-200KHz 位置也会超标。

原因分析: 导致传导的相位误差、调制谱 FAIL 需要对 MT6139 的发射架构进行了解。MT6139 的发射部分采用

的 DCT 的发射架构,VCO 的频率范围分别如下:

硬件设计规范-射频电路设计

硬件设计规范――射频电路设计一. 前言二. 射频电路设计规范2.1射频电路原理图设计2.2射频电路摆件和走线设计2.3射频电路调试2.4天线设计三. 总结一射频电路设计规范说明随着公司项目的增多,设计工作也随着繁重,射频电路设计涉及整个手机项目始终,因此有必要形成一个设计规范,对射频电路设计人员起一个指导作用,了解整个射频电路设计的流程和相应该做的工作,能够让设计工作变得更加规范、简捷、明了,提高设计效率,减少和避免设计失误和错误, 整体提高公司射频电路的设计能力。

二射频电路设计规范2.1 射频电路原理图设计就射频电路而言不同的手机开发平台,射频电路基本类似,现以MTK平台述说射频电路设计,射频电路原理图主要包括Transceiver+PA+FEM+TCXO四个主要器件,外加RLC组成射频电路。

射频前端之前用ASM+SAW filter,由于FEM的出现在价格和调试的简化方面有很大的优势,因此目前FEM的使用趋于替代ASM,目前 MTK的Transceiver主要用MT6129,具有四频收发功能,近期MTK会推出MT6139。

PA目前有RFMD、skyworks、renease,siliconlab,源通等,就功率控制的方式分有:电压控制式(RFMD,RENEASE)、电流控制式(SKYWORKS)、功率控制式(源通)。

就优缺点而言。

就达到功率放大的功能都没有问题,以RFMD为代表的压控式PA,目前使用最广泛,在APC和频谱上以其优良的性能得到广大客户的认可,由于是电压控制式,在功率受电压变化的影响较大。

以skyworks为代表的流控式PA,目前在众多平台上使用,它的优势:工作电流较小,缺点:在MTK平台上APC DAC OFFSET 的一致性不好,APC和频谱调试比较困难,并且耦合开关谱在天线调试频点不合适的时候,出现开关谱fail。

源通的PA采用功率控制,优点:和RFMD兼容,可以做替代,缺点:在高功率等级情况下,APC value 的变化对功率很想很大,对工厂APC的校准良率有一定影响,开关谱调试不是很容易。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图中红色部分就 是模拟电路MIC 部分采用地回流 路环一点接地的 方式处理,注意 音频地回流不和 PA回流交叉

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

无线终端PCB常用HDI工艺介绍

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

根据pcb板形状和固定结构件来进行布局,评估怎样 放走线最好最短。如下图MT8312平板的整过布局图:

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

TOP

BOTTOM

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

差分线

FM差分天线:阻抗90欧姆 MIPI差分100欧母

USB差分线差分阻抗90欧姆

DDR3 EDCLK:差分阻抗100欧姆

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

射频控制线

I/Q线RX和TX两两分开包地

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

CLK走线

CLK1/RTC32K/SRCL KENA/AUD_CLK

摄像头P/M clk

TF卡座 clk

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

LCD CLK

射频PCB与数模混合类PCB布线完成后的收尾 处理

放好有结构位置要求的元器件

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

• 初步处理放好有结构位置要求的元器件,如SIM卡、电池连接器、马 达、耳机、数据接口….等、试着初步确定射频和基带各区域的大概范 围。如图1 • 参照上面的TOP和Bottom图并放置焊接屏蔽罩焊盘的铜皮宽度以作参 考(做在防焊层,宽度一般有1mm、0.8mm、0.6mm)。如图2

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

盲埋孔HDI工艺PCB叠层结构

• 6层盲埋孔PCB叠层结构

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

PCB的叠层结构

• PCB的分层 • PCB分层的原则 • 手机PCB分层考虑

手机电路中需要进行ESD防护的电路

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

• 对于静电我们可以形象地归为:堵、疏、躲得宗旨针对手 机中需要进行ESD防护的电路进行增强ESD防护主要由硬 件工程师来设计合适的ESD防护电路,其实这部分电路很 简单。原理就是让可能的ESD尽快卸放到地。(从传导即 接触放电来讲)根据这一原理,PCB的布局和布线很重要 ESD防护器件一定要紧靠输入端放置,布线一定要是先经 过ESD防护器件

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

PCB的布线规则和技巧

• • • • • • • • • • • • • • • 熟悉主要的一些脚pin含义 射频布线 布线技巧 天线ANT处理 时钟电路的布线技巧 自动增益控制处理 滤波器处理 电源处理 去藕电容的布线要点 过孔模型与寄生参数 接地和过孔设计 PLL电路处理 地线影响阻抗 电流分布图 数模混合类PCB布线

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

PCB的叠层

• PCB分层在PCB设计中也是很有讲究,好的分层会让设计避免出现许 多让人困扰的问题发生,特别是目前高速PCB设计中,这个问题就越 显的分层的好坏对PCB设计成功地的优劣。

• • • • • ■表面地铺铜的处理(图2) ■配合阻抗需求挖空地平面(如下图1) ■地孔VIA的处理(如下图1) ■模拟与数字电源平面 DRC CHECK

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

图1

图2

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

• 和结构工程师充分沟通,新的结构还有商量余地,基本上 也就定了各模块的区域,要结构给的是透视图,标明限高 区,

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

TOP

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

PCB分层的原则

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

• 与元件面相邻的层为地平面,提供器件屏蔽层以及为顶层 布线提供回流平面,另外对射频来讲可以防止射频泄露到 内层。 • 所有信号层尽可能与地平面相邻 • 主电源尽可能与其对应地相邻 • 尽量避免两信号层直接相邻 • 兼顾层压结构对称

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

电源层要与地层相邻

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

• 电源层要临近地层:提供很好的藕合,有利于藕合电容增 大,去藕效果好,电源回路小,电源系统阻抗低,有利于 改善地弹噪声,有利于控制EMI,其实有很多EMI的原因 就是电源系统处理得不好造成的,目前也越来关注电源完 整性的设计,还出现了很多这方面的分析软件。两层中间 的厚度h 的值越小越好。

图1

图 2

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

价值观:客户第一 PCB | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长 初步规划整个 的分区

• 要把各个部分模块化,如下图

CPU与DDR部分

电源部分布 局

射频部分的布局

差分匹配网络的布局

四合一 (WIFI/GPS/BT/FM)布局 行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真 ·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

目录

原理方块图 PCB布局 无线终端PCB常用HDI工艺介绍 PCB的叠层结构 特性阻抗的控制 PCB的布线规则和技巧 PCB板级的ESD处理方法和技巧

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长 PCB设计中特性阻抗所涉及的方面

• • • •

考虑设计中可能要用到的传输线类型 根据用到的传输线类型进行合理叠层分配 根据特性阻抗要求调整合适的参数组合,以确定设计参数 与厂商沟通设计参数进行确定由于PCB厂家在实际的制作中有很多因素制约从而 与我们事先自己计算的参数会有出入

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

MTK平台射频高速PCB设计

阿龙电子 MID研发部 • 整机工程部 原晓霞 刘刚 • 2009-12-04

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

电源去耦电容的摆放

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长 优先按照优先射频路径摆放器件,

• RF输出要远离RF输入。 • 敏感的模拟信号应该尽可能远离高速数字信号和RF信号。 • 优化布局,使RF路径最短并最好,使RF信号尽量不使用过 孔 • 右图是MT8312射频部分的布局

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

• HDI简介 • 盲埋孔HDI工艺PCB叠层结构

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

HDI简介

• HDI板,是指High Density Interconnect,即高密度互连板 ,HDI板的钻孔孔径一般为3-6mil(0.076-0.152mm),采用激光 钻孔技术(有时也称为镭射孔技术)。从而使PCB的空间 使用率得到很大的改善,主要用来解决像手机这类高密度 互连扳的设计困难,传统的机械钻孔技术已无法满足和实 现高密度互连这一要求,目前这一工艺技术得到了广泛的 利用,工艺技术也已很成熟。

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任

MT8312平板六PCB分层考虑

TOP GND(Signal) GND

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

Signal GND(Signal) BOTTOM

•

这样的叠层有点不符合前面提到的分层原则,由于成本的元素,是个 折衷处理的叠层,由于板子面积很小板子变形已不是主要考虑的对象, 第6层上尽可能的不走线,第二层尽量少走线,走短线(Top也是)第4 层是最好的走线层,尽量走主要关键线,没有独立电源层。

价值观:客户第一 | 阳光沟通 | 团队协作 | 拥抱变化 | 学习成长

射频布线

• 射频布线一定要满足50欧母阻抗线要求,前后左右上下要 包好地,接收与发射要分开。

行为准则:尊重·简单·重用·检查·并行·勇气·反馈·改善·认真·责任