FPGA与ADC0809接口电路详解

ADC0809应用电路资料

adc0809应用电路资料1、模拟信号输入IN0~IN7:IN0-IN7 为八路模拟电压输入线,加在模拟开关上,工作时采用时分割的方式,轮流进行A/D 转换。

2、地址输入和控制线:地址输入和控制线共 4 条,其中ADDA、ADDB 和ADDC 为地址输入线,用于选择IN0-IN7 上哪一路模拟电压送给比较器进行A/D 转换。

ALE 为地址锁存允许输入线,高电平有效。

当ALE 线为高电平时,ADDA、ADDB和ADDC 三条地址线上地址信号得以锁存,经译码器控制八路模拟开关通路工作。

3、数字量输出及控制线(11 条):START 为“启动脉冲”输入线,上升沿清零,下降沿启动ADC0809 工作。

EOC 为转换结束输出线,该线高电平表示AD 转换已结束,数字量已锁入“三态输出锁存器”。

D0-D7 为数字量输出线,D7 为最高位。

ENABLE 为“输出允许”线,高电平时能使D0-D7 引脚上输出转换后的数字量。

4、电源线及其他(5 条):CLOCK 为时钟输入线,用于为ADC0809 提供逐次比较所需,一般为640kHz 时钟脉冲。

Vcc 为+5V 电源输入线,GND 为地线。

+VREF 和-VREF 为参考电压输入线,用于给电阻网络供给标准电压。

+VREF 常和VDD 相连,-VREF 常接地。

ADC0809 芯片性能特点: 是一个逐次逼近型的A/D 转换器,外部供给基准电压;单通道转换时间116us;分辨率为8 位,带有三态输出锁存器,转换结束时,可由CPU 打开三态门, 读出8 位的转换结果;有8 个模拟量的输入端,可引入8 路待转换的模拟量。

ADC0809 的数据输出结构是内部有可控的三态缓冲器,所以它的数字量输出信号线可以与系统的数据总线直接相连。

内部的三态缓冲器由OE 控制,当OE 为高电平时,三态缓冲器打开,将转换结果送出;当OE 为低电平时,三态缓冲器处于阻断状态,内部数据对外部的数据总线没有影响。

第五章 5.7节 模拟电路接口技术ADC0809

2、主要性能指标 (1)、分辨率

分辨率反映A/D 转换器对输入微小变化响应的能力,通常用数字输

出最低位(LSB)所对应的模拟输入的电平值表示。n 位A/D 能反应 1/2^n 满量程的模拟输入电平。

由于分辨率直接与转换器的位数有关,所以一般也可简单地用数字

量的位数来表示分辨率,即n 位二进制数,最低位所具有的权值,就 是它的分辨率。

值得注意的是,分辨率与精度是两个不同的概念,不要把两者相混

淆。即使分辨率很高,也可能由于温度漂移、线性度等原因,而使其 精度不够高。

例如,ADC输出为八位二进制数, 输入信号最大值为 5V,其分辨率为: U m 19 .61mV 8

2 1

(2)、转换时间

转换时间是指完成一次A/D 转换所需的时间,即由发出启动转换

/**********(C) ADC0809.C**************/ #include <reg51.h> #include "1602.h" #define uchar unsigned char #define uint unsigned int sbit ADC_START=P2^0; //四个控制引脚的定义 sbit ADC_ALE =P2^1; sbit ADC_EOC =P2^2; sbit ADC_OE =P2^3; sbit D0=P0^0; //八盏灯的定义 sbit D1=P0^1; sbit D2=P0^2; sbit D3=P0^3; sbit D4=P0^4; sbit D5=P0^5; sbit D6=P0^6; sbit D7=P0^7;

AD转换速度: 500K频率:130us 640K频率:100us 分辨率:8位

4、ADC0809接口电路

ADC0809与单片机的接口电路

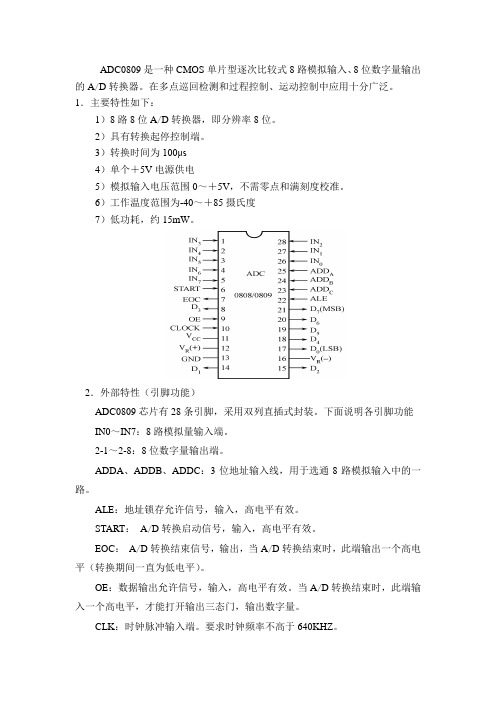

ADC0809是一种CMOS单片型逐次比较式8路模拟输入、8位数字量输出的A/D转换器。

在多点巡回检测和过程控制、运动控制中应用十分广泛。

1.主要特性如下:1)8路8位A/D转换器,即分辨率8位。

2)具有转换起停控制端。

3)转换时间为100μs4)单个+5V电源供电5)模拟输入电压范围0~+5V,不需零点和满刻度校准。

6)工作温度范围为-40~+85摄氏度7)低功耗,约15mW。

2.外部特性(引脚功能)ADC0809芯片有28条引脚,采用双列直插式封装。

下面说明各引脚功能IN0~IN7:8路模拟量输入端。

2-1~2-8:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路。

ALE:地址锁存允许信号,输入,高电平有效。

START:A/D转换启动信号,输入,高电平有效。

EOC:A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):基准电压。

VCC:电源,单一+5V。

GND:地。

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。

此地址经译码选通8路模拟输入之一到比较器。

START上升沿将逐次逼近寄存器复位。

下降沿启动A/D转换,之后EOC输出信号变低,指示转换正在进行。

直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。

当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。

单片机与ADC0809的接口电路图。

FPGA与ADC0809接口电路详解

FPGA与ADC0809接口电路详解注:(1)本程序基于FPGA和vhdl编写有详尽的程序解释和原理分析以及原理图,状态图(2)对于adc0809具体资料可上网查在此不累述一.FPGA与ADC0809的接口电路图原理二.关于ADC0809的说明(重点)(1)ale信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)oe信号(引脚)en使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上(3)eoc信号(引脚):eoc为高电平时完成转换,为低电平时正在转换。

(4)start信号(引脚):要给start线送一个100ns宽的启动正脉冲,start下跳沿时,开始进行A/D转换,在转换期间start以保持低电平。

三.转换状态图对于状态图的真值表未列出 注意对应的注释为vhdl 语句ale<='1';start<='0';en<='0';----eoc='1' ale<='0';start<='0';en<='0';--再次检测数据是否转换完 if eoc='0' then next_state<=st4;else next_state<=st5;器,将数据送入数据总线存器四.ADC0809采样接口电路程序--*********ADC0809采样控制*************--******因为FPGA 的时钟频率为50MHz ,则256分频后,即ADC0809输入时钟为195KHz****** --******对ADC0809进行简单的采样控制,得到的数据进FPGA 送到8个并排的数码管显示***** library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity PL_AD isport ( d : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据输入FPGA clk,eoc: in std_logic; --clk 为系统时钟,eoc 为ADC0809转换结束信号输入FPGA lock1,start, ale,en: out std_logic; --ADC0809控制信号FPGA 输出信号 abc_in :in std_logic_vector(2 downto 0); --模拟选通信号abc_out :std_logic_vector(2 downto 0);--ADC0809模拟信号选通信号q : out std_logic_vector(7 downto 0));送至8个并排数码管信号FPGA 输出数字信号 end pl_AD;architecture behav of PL_AD istype states is ( st0,st1, st2, st3, st4,st5,st6);--定义状态类型枚举类型signal current_state, next_state:states:=st0;--定义总体两个状态现态和次态并且初值为st0态signal regl :std_logic_vector(7 downto 0);--定义中间寄存器signal lock : std_logic;signal qq:std_logic_vector(7 downto 0);--定义计数器用于分频begincom:process(current_state,eoc) –此进程主要是驱动ADC0809工作即数据转换过程begincase current_state iswhen st0=>next_state<=st1;ale<='0';start<='0';en<='0';--准备when st1=>next_state<=st2;ale<='1';start<='0';en<='0';--三个地址信号送入地址锁存器when st2=>next_state<=st3;ale<='0';start<='1';en<='0';--开始数据转换when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;when st5=>next_state<=st6;ale<='0';start<='0';en<='1'; --打开输出数据锁存器,将数据送入数据总线when st6=>next_state<=st0;ale<='0';start<='0';en<='1';regl<=d;--打开输出数据锁存器,将数据送入寄存器regl when others=> next_state<=st0;ale<='0';start<='0';en<='0';end case;end process;clock:process(clk) --对系统时钟进行分频,得到驱动ADC0809的时钟信号beginif clk'event and clk='1' then qq<=qq+1;if QQ="01111111" THEN lock<='1';--实现分频current_state <=next_state;--在lock上升沿,转换至下一状态elsif qq<="01111111" then lock<='0';end if;end if;end process;q<=regl;--寄存器数据输出即FPGA输出lock1<=lock;abc_out<=abc_in;--模拟选通信号送往ADC0809end behav;注:有错when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;不过我这里的注释好像错了,这两个when合起来才是检测数据是否转换完的。

FPGA设计-ADC0809

目录摘要 (2)1设计任务 (4)2系统设计原理 (4)2.1 硬件设计原理 (4)2.1.1 ADC0809的主要特性 (4)2.1.2 ADC0809的外部特性 (4)2.1.3工作过程 (5)2.2 软件设计思路 (6)2.3 程序流程图 (7)3功能与时序仿真 (8)3.1 功能仿真得出的RTL图 (8)3.2 功能仿真得出的状态图 (8)3.3 时序仿真 (9)4总结 (9)5参考文献 (10)附录一程序 (11)摘要实现时必须严格遵守ADC0809的工作时序,对选定的通道输入一个模拟量,调节电位器改变输入的模拟量。

利用quartus2进行文本编辑输入和试仿;给出仿真波形。

最后进行引脚锁定并进行测试,硬件验证ADC0809 的控制功能。

具体过程为:编写ADC0809时序的VHDL代码。

对其进行编译仿真主要控制信号为:Start为转换启动信号,高电平有效;ale为通道选择地址信号的锁存信号。

当启动转换后,程序开始执行,查询状态,状态为0.1.时等待,状态2时,查询EOC信号的状态,判断是否转换结束,当EOC=1时表示转换结束,否则继续等待;转换结束后继续查询状态,若OE信号为高电平则控制打开三态缓冲器,当LOCK信号为高电平时,将转换后的数据进行锁存,至此一次转换结束。

关键词:工作时序、AD0809 、VHDL、quartus2、编译仿真、Start 、EOC、OE、三态缓冲器AbstractImplementation must strictly abide by the work timing of ADC0809, an analogue for the selected channel input, adjust the potentiometer change the analog input. Using quartus2 to input text editing and try copy; The simulation waveform is given. Finally pin lock and test, the control function of the hardware validation ADC0809. Concrete process is: the timing of ADC0809 VHDL code.To compile the simulation main control signal is: Start for conversion Start signal, high efficient;Ale for channel selection address signal is latched signals. , when start the conversion, program starts executing the query status, the status of 0.1. While waiting, state 2, track the status of EOC signal, judge whether the conversion is over, when the EOC = 1 said switch over, or continue to wait for; Transformation after the end of continue to query the state, if the OE signal for high level control to open the tri-state buffer, when the LOCK signal for high electricity at ordinary times, the converted data latches, ended a transformation.Keywords:Work timing、AD0809 、VHDL、quartus2、Compile thesimulation、Start 、EOC、OE、Tri-state buffer1设计任务基于VHDL语言,实现对ADC0809简单控制。

FPGA直接控制ADC0809对模拟信号进行采样.

第二章总体方案设计2.1 系统方案设计在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。

单片机的速度极大的限制了A/D高速性能的利用,而FPGA的时钟频率可高达100MHz以上。

本设计以高集成度的芯片为核心,进行时序控制、码制变换。

具有开发周期短,灵活性强,通用能力好,易于开发、扩展等优点。

既降低了设计难度,又加快了产品的开发周期。

基于FPGA的信号采集系统主要有:A/D转换器,FPGA,RS232通信,PC 机组成。

A/D 转换器对信号进行会采集,A/D 内部集成了采样、保持电路,可有效的降低误差,减少外围电路的设计,降低系统的功耗。

A/D在接受到指令后进行采集,FPGA采集控制模块首先将采集到的通过A/D 转换城的数字信号引入FPGA,而后对数字信号送往算法实现单元进行处理,并存于FPGA内部RAM 中,再将数据由RS232传送到PC上做FFT,实现对采集信号的时域和频域的显示。

图2.1.1系统的总体框图:FPGA的设计结构如图2.1.2所示。

数字倍频器的倍频输出提供ADC控制器的采样触发脉冲。

根据ADC0809操作时序,ADC控制器来实现ADC0809的数据采集操作,采样的时机由倍频器来控制。

控制器每控制完成一次采样操作,则停止等待下一个触发脉冲的到来。

倍频器每输出一个低电平脉冲,ADC采样控制器的状态机进行一次采样操作。

在倍频器的触发控制下,完成被测信号一个基波周期N个点的等间隔采样,同时数字倍频器跟踪输入信号的频率的变化,尽可能地保持N个点的采样宽度正好为被测信号一个周波的宽度。

-时钟分配及各模块的控制:在协调模块工作时,起到很重要的作用。

引进晶振产的时钟信号,根据实际需要对起进行倍频或分频,使A/D的采样频率,RAM的读写频率,信号处理实现的核心模块的工作频率一致。

图2.1.2系统具体流程框图2.2 各功能模块的设计方案2.2.1 FPGA最小系统板方案设计FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物[4]。

模数转换器ADC0809应用原理

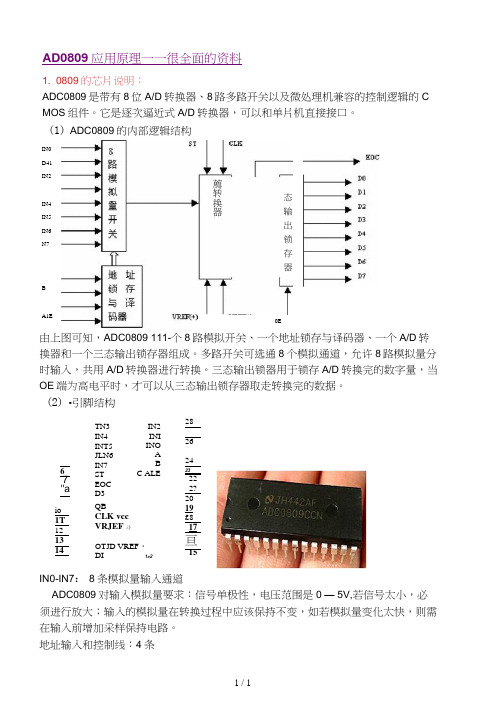

精品文档AD0809应用原理--很全面的资料1.0809 的芯片说明:ADC0809是带有 8 位 A/D 转换器、 8 路多路开关以及微处理机兼容的控制逻辑的 CMOS 组件。

它是逐次逼近式 A/D 转换器,可以和单片机直接接口。

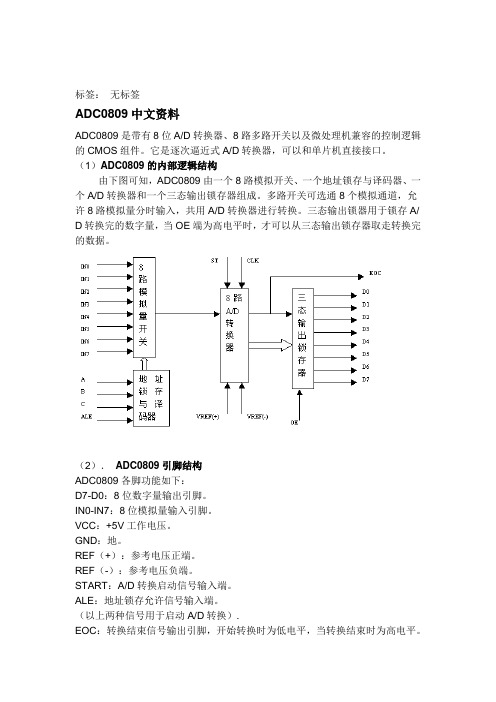

(1) ADC0809的内部逻辑结构由上图可知, ADC0809由一个 8 路模拟开关、一个地址锁存与译码器、一个A/D 转换器和一个三态输出锁存器组成。

多路开关可选通8 个模拟通道,允许8 路模拟量分时输入,共用 A/D 转换器进行转换。

三态输出锁器用于锁存A/D 转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

( 2).引脚结构IN0- IN7:8 条模拟量输入通道ADC0809对输入模拟量要求:信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线: 4 条ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将 A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B 和 C 为地址输入线,用于选通 IN0-IN7 上的一路模拟量输入。

通道选择表如下表所示。

C B A 选择的通道000IN0001IN1010IN2011IN3100IN4101IN5110IN6111IN7数字量输出及控制线: 11 条ST 为转换启动信号。

当 ST 上跳沿时,所有内部寄存器清零;下跳沿时,开始进行 A/ D 转换;在转换期间, ST应保持低电平。

EOC为转换结束信号。

当 EOC为高电平时,表明转换结束;否则,表明正在进行 A/D 转换。

OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。

OE= 1,输出转换得到的数据; OE=0,输出数据线呈高阻状态。

D7- D0为数字量输出线。

模数转换器ADC0809应用原理

AD0809应用原理一一很全面的资料1. 0809的芯片说明:ADC0809是带有8位A/D 转换器、8路多路开关以及微处理机兼容的控制逻辑的C MOS 组件。

它是逐次逼近式A/D 转换器,可以和单片机直接接口。

(1) ADC0809的内部逻辑结构由上图可知,ADC0809 111-个8路模拟开关、一个地址锁存与译码器、一个A/D 转 换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分 时输入,共用A/D 转换器进行转换。

三态输出锁器用于锁存A/D 转换完的数字量,当OE 端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2) •引脚结构IN0-IN7: 8条模拟量输入通道ADC0809对输入模拟量要求:信号单极性,电压范围是0 — 5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需 在输入前增加采样保持电路。

地址输入和控制线:4条67 "aio1T1213 14TN3 IN4 INT5 JLN6 IN7 ST EOC D3 QBCLK vcc VRJEF 斗IN2 INI INO A B C ALEOTJD VREF ・ DI 1>228 26 2423222? 20 19 £8 17亘15BA1EIN0 D41 IN2IN4 IN5 IN6 N70E薦转换器态 输 出 锁 存 器ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A, B, C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A, B和C为地址输入线,用于选通IN0-IN7±的一路模拟量数字量输出及控制线:11条ST为转换启动信号。

当ST±跳沿时,所有内部寄存器清零;下跳沿时,开始进行A /D转换;在转换期间,ST应保持低电平。

EOC为转换结束信号。

当EOC为高电平时,表明转换结束;否则,表明正在进行A/D转换。

ADC0809逻辑结构图

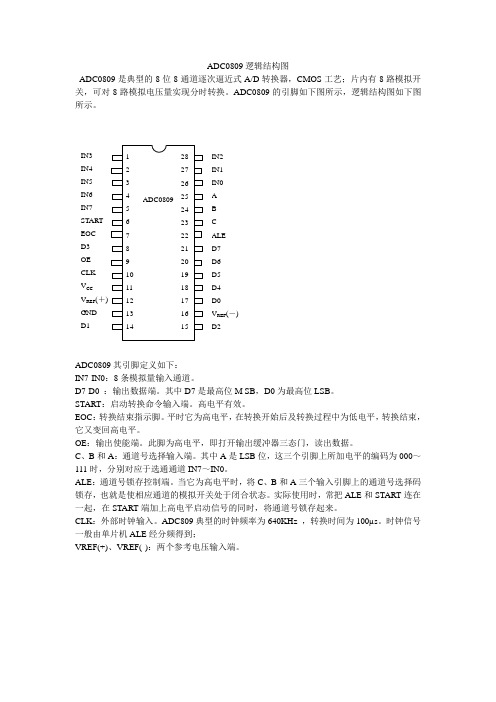

ADC0809逻辑结构图ADC0809是典型的8位8通道逐次逼近式A/D转换器,CMOS工艺;片内有8路模拟开关,可对8路模拟电压量实现分时转换。

ADC0809的引脚如下图所示,逻辑结构图如下图所示。

1 2 3 4 5 6 7 8 910111213142827262524232221201918171615ADC0809IN2IN1IN0ABCALED7D6D5D4D0V REF(-)D2IN3IN4IN5IN6IN7STARTEOCD3OECLKV CCV REF(+)GNDD1ADC0809其引脚定义如下:IN7-IN0:8条模拟量输入通道。

D7-D0 :输出数据端。

其中D7是最高位M SB,D0为最高位LSB。

START:启动转换命令输入端。

高电平有效。

EOC:转换结束指示脚。

平时它为高电平,在转换开始后及转换过程中为低电平,转换结束,它又变回高电平。

OE:输出使能端。

此脚为高电平,即打开输出缓冲器三态门,读出数据。

C、B和A:通道号选择输入端。

其中A是LSB位,这三个引脚上所加电平的编码为000~111时,分别对应于选通通道IN7~IN0。

ALE:通道号锁存控制端。

当它为高电平时,将C、B和A三个输入引脚上的通道号选择码锁存,也就是使相应通道的模拟开关处于闭合状态。

实际使用时,常把ALE和START连在一起,在START端加上高电平启动信号的同时,将通道号锁存起来。

CLK:外部时钟输入。

ADC809典型的时钟频率为640KHz ,转换时间为100µs。

时钟信号一般由单片机ALE经分频得到;VREF(+)、VREF(-):两个参考电压输入端。

ADC0809逻辑结构图。

ADC0809

标签:无标签ADC0809中文资料ADC0809是带有8位A/D转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

(1)ADC0809的内部逻辑结构由下图可知,ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/ D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2).ADC0809引脚结构ADC0809各脚功能如下:D7-D0:8位数字量输出引脚。

IN0-IN7:8位模拟量输入引脚。

VCC:+5V工作电压。

GND:地。

REF(+):参考电压正端。

REF(-):参考电压负端。

START:A/D转换启动信号输入端。

ALE:地址锁存允许信号输入端。

(以上两种信号用于启动A/D转换).EOC:转换结束信号输出引脚,开始转换时为低电平,当转换结束时为高电平。

OE:输出允许控制端,用以打开三态数据输出锁存器。

CLK:时钟信号输入端(一般为500KHz)。

A、B、C:地址输入线。

ADC0809对输入模拟量要求:信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线:4条ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B和C为地址输入线,用于选通IN0-IN7上数字量输出及控制线:11条ST为转换启动信号。

当ST上跳沿时,所有内部寄存器清零;下跳沿时,开始进行A/D转换;在转换期间,ST应保持低电平。

EOC为转换结束信号。

当E OC为高电平时,表明转换结束;否则,表明正在进行A/D转换。

单片机与ADC0809接口电路

单片机与ADC0809接口电路一、ADC0809主要信号引脚的功能说明1.IN7~IN0——模拟量输入通道2. ALE——地址锁存允许信号。

对应ALE上跳沿,A、B、C地址状态送入地址锁存器中。

3. START——转换启动信号。

START上升沿时,复位ADC0809;START下降沿时启动芯片,开始进行A/D转换;在A/D转换期间,START应保持低电平。

本信号有时简写为ST.4. A、B、C——地址线。

通道端口选择线,A为低地址,C为高地址5. CLK——时钟信号。

ADC0809的内部没有时钟电路,所需时钟信号由外界提供,因此有时钟信号引脚。

使用频率为10KHz~1280KHz的时钟信号6. EOC——转换结束信号。

EOC=0,正在进行转换;EOC=1,转换结束。

使用中该状态信号即可作为查询的状态标志,又可作为中断请求信号使用。

7. D7~D0——数据输出线。

为三态缓冲输出形式,可以和单片机的数据线直接相连。

D0为最低位,D7为最高8.OE——输出允许信号。

用于控制三态输出锁存器向单片机输出转换得到的数据。

OE=0,输出数据线呈高阻;OE=1,输出转换得到的数据。

9.Vcc—— +5V电源。

Vref——参考电源参考电压用来与输入的模拟信号进行比较,作为逐次逼近的基准。

其典型值为+5V(Vref(+)=+5V, Vref(-)=0V).二、原理图三、电路连接说明及工作过程AT89c51单片机的P1口用作数据复用总线与ADC0809的数据输出端相连(原理图未画出)。

单片机的低3位(P0.0~P0.2)数据线(选通abc)用于选择8路模拟量输入。

ADC0809的时钟信号CLK由单片机的ALE信号提供,由于单片机内部晶振频率为11.0592MHz,即单片机的ALE输出为1/6f osc=1.8432MHz,经四分频器得到输入到0809CLKk端的信号频率为460.8KHz,满足工作要求。

转换的启动信号START和8路模拟输入开关的地址锁存允许信号ALE由单片机的写信号WR(P3.6)及地址译码输出信号逻辑提供。

ADC0809引脚图和接口电路图

ADC0809引脚图与接口电路 2008-06-28 19:04ADC0809引脚图与接口电路作者:佚名 来源:本站原创 点击数: 859 更新时间:2007年07月29日A/D 转换器芯片ADC0809简介 8路模拟信号的分时采集,片内有8路模拟选通开关,以及相应的通道抵制锁存用译码电路,其转换时间为100μs 左右。

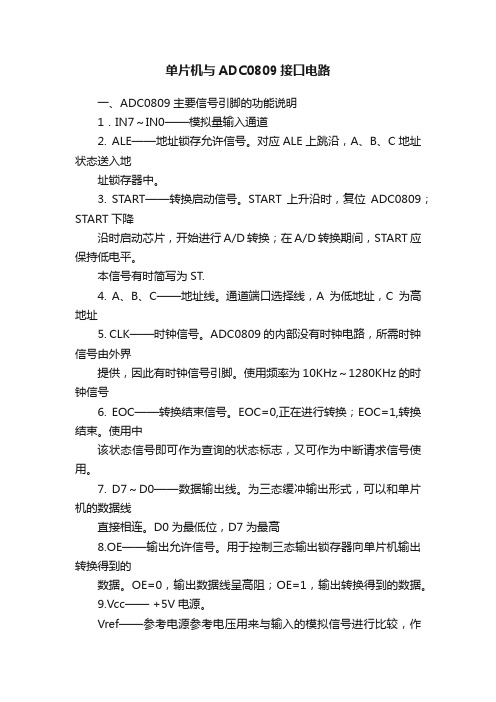

图9.8 《ADC0809引脚图》1. ADC0809的内部结构ADC0809的内部逻辑结构图如图9-7所示。

图9.7 《ADC0809内部逻辑结构》图中多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用一个A/D转换器进行转换,这是一种经济的多路数据采集方法。

地址锁存与译码电路完成对A、B、C 3个地址位进行锁存和译码,其译码输出用于通道选择,其转换结果通过三态输出锁存器存放、输出,因此可以直接与系统数据总线相连,表9-1为通道选择表。

表9-1 通道选择表2.信号引脚ADC0809芯片为28引脚为双列直插式封装,其引脚排列见图9.8。

对ADC0809主要信号引脚的功能说明如下:IN7~IN——模拟量输入通道ALE——地址锁存允许信号。

对应ALE上跳沿,A、B、C地址状态送入地址锁存器中。

START——转换启动信号。

START上升沿时,复位ADC0809;START下降沿时启动芯片,开始进行A/D转换;在A/D转换期间,START应保持低电平。

本信号有时简写为ST.A、B、C——地址线。

通道端口选择线,A为低地址,C为高地址,引脚图中为ADDA,ADDB和ADDC。

其地址状态与通道对应关系见表9-1。

CLK——时钟信号。

ADC0809的内部没有时钟电路,所需时钟信号由外界提供,因此有时钟信号引脚。

通常使用频率为500KHz的时钟信号EOC——转换结束信号。

EOC=0,正在进行转换;EOC=1,转换结束。

使用中该状态信号即可作为查询的状态标志,又可作为中断请求信号使用。

D 7~D——数据输出线。

模数转换器ADC0809引脚及内部框图

模数转换器ADC0809引脚及内部框图

模数转换器ADC0809引脚及内部框图

ADC0809 8通道8位a/d转换器,ADC0809是带有8位A/D转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

ADC0809芯片为28引脚为双列直插式封装,其引脚排列见图9.8。

对ADC0809主要信号引脚的功能说明如下:

- ALE地址锁存允许信号。

对应ALE上跳沿,A、B、C地址状态送入地址锁存器中。

- START转换启动信号。

START上升沿时,复位ADC0809;START下降沿时启动芯片,开始进行A/D转换;在A/D转换期间,START应保持低电平。

本信号有时简写为ST.

- A、B、C地址线。

通道端口选择线,A为低地址,C为高地址,引脚图。

ADC0809接口电路

8位A/D转换器芯片ADC0809ADC0809是CMOS单片型逐次逼近式A/D转换器,ADC0809的主要特性:● 它是具有8路模拟量输入、8位数字量输出功能的A/D转换器。

● 转换时间为100μs。

● 模拟输入电压范围为0V~+5V,不需零点和满刻度校准。

● 低功耗,约15mW。

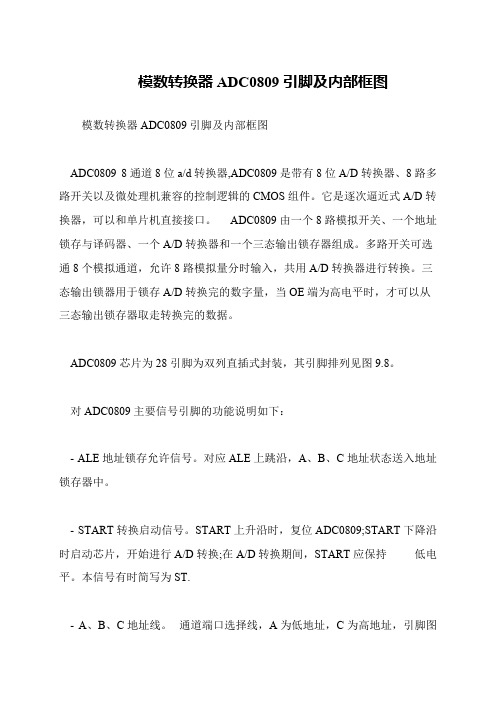

(1)ADC0809结构框图及引脚说明图4.24 ADC0809的结构框图和引脚通道选择开关通道地址锁存和译码逐次逼近A/D转换器8位锁存器和三态门(2)ADC0809的工作过程对ADC0809的控制过程是:① 首先确定ADDA、ADDB、ADDC三位地址,决定选择哪一路模拟信号;② 使ALE端接受一正脉冲信号,使该路模拟信号经选择开关到达比较器的输入端;③ 使START端接受一正脉冲信号,START的上升沿将逐次逼近寄存器复位,下降沿启动A/D转换;④ EOC输出信号变低,指示转换正在进行。

⑤ A/D转换结束,EOC变为高电平,指示A/D转换结束。

此时,数据已保存到8位三态输出锁存器中。

此时CPU就可以通过使OE信号为高电平,打开ADC0809三态输出,由ADC0809输出的数字量传送到CPU。

(3)CPU读取A/D转换器数据的方法① 查询法优点:接口电路设计简单。

缺点:A/D转换期间独占CPU,致使CPU运行效率降低。

② 定时法:优点:接口电路设计比查询法简单,不必读取EOC的状态。

缺点:A/D转换期间独占CPU,致使CPU运行效率降低;另外还必须知道A/D转换器的转换时间。

CPU读取A/D转换器数据的方法③ 中断法优点:A/D转换期间CPU可以处理其它的程序,提高CPU的运行效率。

图4.25 ADC0809接口电路缺点:接口电路复杂。

(4)ADC0809接口电路图 4. 25 ADC0809接口电路[例4.1]利用图4.25,采用无条件传送方式,编写一段轮流从IN0~IN7采集8路模拟信号,并把采集到的数字量存入0100H开始的8个单元内的程序。

FPGA控制AD转换原理及程序

基于FPGA的AD控制模块(2010-07-23 18:00:42)转载▼分类:技术标签:杂谈这是夏天小学期做的第一个课程设计。

题目是《模拟信号处理》,实质上就是做一个对ADC0809的控制器,控制AD转换并读取出转换结果,将结果显示为10进制数。

ADC0809是单通道输入,8位输出的模/数转换器。

参考电压为2.560V时最小分辨率为0.020V。

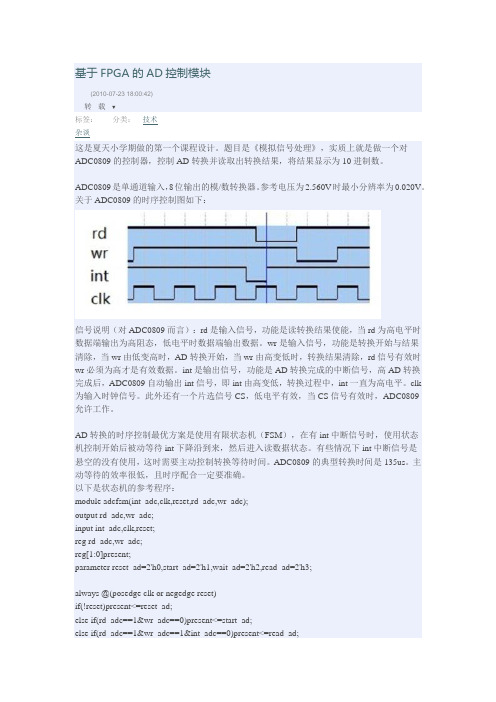

关于ADC0809的时序控制图如下:信号说明(对ADC0809而言):rd是输入信号,功能是读转换结果使能,当rd为高电平时数据端输出为高阻态,低电平时数据端输出数据。

wr是输入信号,功能是转换开始与结果清除,当wr由低变高时,AD转换开始,当wr由高变低时,转换结果清除,rd信号有效时wr必须为高才是有效数据。

int是输出信号,功能是AD转换完成的中断信号,高AD转换完成后,ADC0809自动输出int信号,即int由高变低,转换过程中,int一直为高电平。

clk 为输入时钟信号。

此外还有一个片选信号CS,低电平有效,当CS信号有效时,ADC0809允许工作。

AD转换的时序控制最优方案是使用有限状态机(FSM),在有int中断信号时,使用状态机控制开始后被动等待int下降沿到来,然后进入读数据状态。

有些情况下int中断信号是悬空的没有使用,这时需要主动控制转换等待时间。

ADC0809的典型转换时间是135us。

主动等待的效率很低,且时序配合一定要准确。

以下是状态机的参考程序:moduleadcfsm(int_adc,clk,reset,rd_adc,wr_adc);outputrd_adc,wr_adc;inputint_adc,clk,reset;regrd_adc,wr_adc;reg[1:0]present;parameterreset_ad=2'h0,start_ad=2'h1,wait_ad=2'h2,read_ad=2'h3;always @(posedgeclk or negedge reset)if(!reset)present<=reset_ad;else if(rd_adc==1&wr_adc==0)present<=start_ad;else if(rd_adc==1&wr_adc==1&int_adc==0)present<=read_ad;else if(rd_adc==1&wr_adc==1)present<=wait_ad;else present<=reset_ad;always @(present)begincase(present)reset_ad:beginrd_adc<=1;wr_adc<=0;endstart_ad:beginrd_adc<=1;wr_adc<=1;endwait_ad:beginrd_adc<=1;wr_adc<=1;endread_ad:beginrd_adc<=0;wr_adc<=1;endendcaseendendmoduleAD转换后的结果为8位二进制数据,即00H~FFH,要输出到数码管上显示,需要将二进制码转换为8421BCD码。

VHDL实验:用状态机实现ADC0809的采样控制电路

VHDL实验二用状态机实现ADC0809的采样控制电路一、实验目的1.学习用状态机对A/D转换器ADC0809的采样控制电路的实现。

二、实验仪器1.PC机一台2.KHF-5 CPLD/FPGA实验开发系统一套。

三、实验要求1.查阅ADC0809芯片资料。

2.预习实验内容。

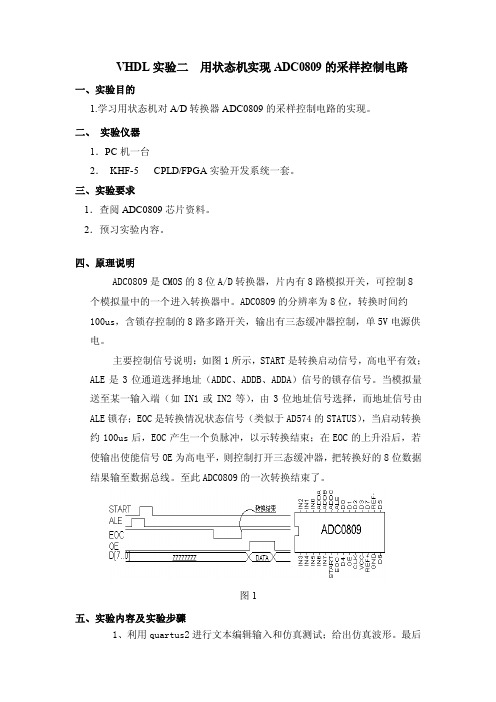

四、原理说明ADC0809是CMOS的8位A/D转换器,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中。

ADC0809的分辨率为8位,转换时间约100us,含锁存控制的8路多路开关,输出有三态缓冲器控制,单5V电源供电。

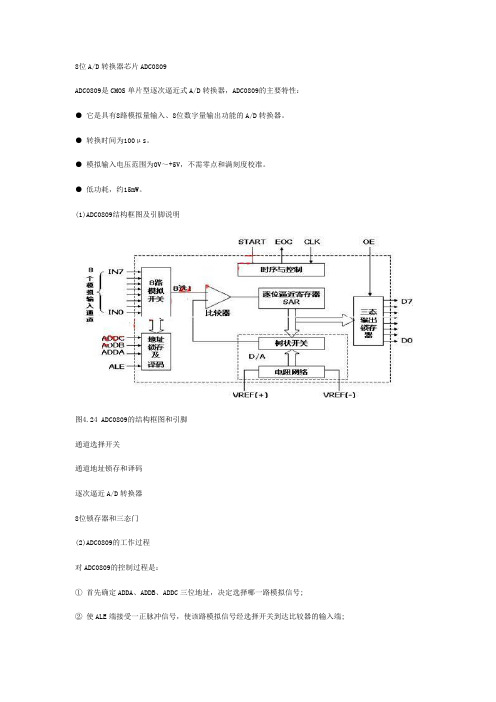

主要控制信号说明:如图1所示,START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;EOC是转换情况状态信号(类似于AD574的STATUS),当启动转换约100us后,EOC产生一个负脉冲,以示转换结束;在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

至此ADC0809的一次转换结束了。

图1五、实验内容及实验步骤1、利用quartus2进行文本编辑输入和仿真测试;给出仿真波形。

最后进行引脚锁定并进行测试,硬件验证对ADC0809的控制功能。

实验代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY adc0809 ISPORT ( ina : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --0809的8位转换数据输出CLK ,EOC : IN STD_LOGIC; --CLK xitong工作时钟ALE, ck, OE : OUT STD_LOGIC; --ck是0809de 工作时钟adda,addb,addc:out std_logic;outa : OUT STD_LOGIC_VECTOR(13 DOWNTO 0) );END adc0809 ;ARCHITECTURE behav OF adc0809 IS--signal sa:std_logic_vector(7 downto 0);signal fp:std_logic_vector(9 downto 0);signal f:std_logic;TYPE states IS (st0, st2, st3,st4,st5,st6) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号BEGINADDA <= '1';addb<='0';addc<='0';--sa<=ina;process( CLK)beginif( CLK'event and CLK='1')thenif fp=15 thenfp<="0000000000";f<=not f;elsefp<=fp+1;end if;end if;end process;ck<=f;PRO: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式CASE current_state ISWHEN st0 => ALE<='0';START<='0';OE<='0';LOCK<='0' ;next_state <= st2;-- WHEN st1 => ALE<='1';START<='1';OE<='0';LOCK<='0' ;next_state <= st2;WHEN st2 => ALE<='1';START<='1';OE<='0';LOCK<='0' ;next_state <= st3;WHEN st3 => ALE<='0';START<='0';OE<='0';LOCK<='0';IF (EOC='1') THEN next_state <= st3; --测试EOC的下降沿ELSE next_state <= st4;END IF ;WHEN st4=> ALE<='0';START<='0';OE<='0';LOCK<='0';IF (EOC='0') THEN next_state <= st4; --测试EOC的上升沿,=1表明转换结束ELSE next_state <= st5; --继续等待END IF ;WHEN st5=> ALE<='0';START<='0';OE<='1';LOCK<='0';next_state <= st6;WHEN st6=> ALE<='0';START<='0';OE<='1';LOCK<='1';next_state <= st0;WHEN OTHERS => ALE<='0';START<='0';OE<='0';LOCK<='0';next_state <= st0;END CASE ;END PROCESS PRO ;PROCESS (f)BEGINIF ( f'EVENT AND f='1') THENcurrent_state <= next_state; -- 在时钟上升沿,转换至下一状态END IF;END PROCESS; -- 由信号current_state将当前状态值带出此进程,进入进程PROPROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= ina ;END IF;END PROCESS ;with REGL(3 downto 0) selectouta(6 downto 0) <="0110000"when"0001",--1"1101101"when"0010",--2"1111001"when"0011",--3"0110011"when"0100",--4"1011011"when"0101",--5"1011111"when"0110",--6"1110000"when"0111",--7"1111111"when"1000",--8"1111011"when"1001",--9"1110111"when"1010",--A"0011111"when"1011",--b"1001110"when"1100",--c"0111101"when"1101",--d"1001111"when"1110",--e"1000111"when"1111",--f"1111110"when others;--0with REGL(7 downto 4) selectouta(13 downto 7) <="0110000"when"0001",--1"1101101"when"0010",--2"1111001"when"0011",--3"0110011"when"0100",--4"1011011"when"0101",--5"1011111"when"0110",--6"1110000"when"0111",--7"1111111"when"1000",--8"1111011"when"1001",--9"1110111"when"1010",--A"0011111"when"1011",--b"1001110"when"1100",--c"0111101"when"1101",--d"1001111"when"1110",--e"1000111"when"1111",--f"1111110"when others;--0END behav;2、建议引脚锁定为:oe为p18。

计算机接口与微机原理-第9周-模拟数字转换器ADC0809

计算机接⼝与微机原理-第9周-模拟数字转换器ADC0809模拟数字转换器ADC0809n模/数转换器n模/数转换器的性能参数n模/数转换原理n ADC 0809的内部结构图n ADC 0809的⼯作⽅式n ADC 0809芯⽚的接⼝电路中⼭⼤学信息科学与技术学院陈任数/模和模/数转换v当⽤计算机来构成数据采集或过程控制等系统时,所要采集的外部信号或被控制对象的参数,往往是温度、压⼒、流量、声⾳和位移等连续变化的模拟量。

v计算机只能处理不连续的数字量,即离散的有限值。

v因此,必须⽤模数转换器即A/D转换器,将模拟信号变成数字量后,才能送⼊计算机进⾏处理。

v计算机处理后的结果,也要经过数模转换器即D/A转换器,转换成模拟量后,在⽰波器上显⽰结果波形和在记录仪上描记下来,或驱动执⾏部件,达到控制的⽬的。

模/数转换器v我们时常需要把模拟信号转化为数字信号, 以便进⾏数据的存储,处理和传输,如:把电压,电流,光,声⾳等模拟信号转化为数字信号。

v模/数转换器可以把模拟信号转换为数字信号,也称为ADC(Analog-to-Digital Converter)。

模数转换器ADC模拟信号数字信号模拟信号8位模数转换器ADC8位⼆进制数X 参考电压: V refv输⼊模拟信号(如,电压值0~+5V) ,启动模数转换,产⽣8位⼆进制数输出。

start模/数转换器原理v实现A/D转换的基本⽅法有⼗⼏种,常⽤的有计数法,逐次逼近法,双斜积分法和并⾏转换法。

v逐次逼近式A/D转换具有速度快,分辨率⾼等优点,且采⽤这种⽅法的ADC芯⽚成本较低,因此在计算机数据采集系统中获得了⼴泛的应⽤。

v逐次逼近式A/D转换器的转换原理是建⽴在逐次逼近的基础上,把输⼊电压V i和⼀组从参考电压分层得到的量化电压进⾏⽐较,⽐较从最⼤的量化电压开始,由粗到细逐次进⾏,由每次⽐较的结果来确定相应的位是1还是0。

不断⽐较和逼近到两者差别⼩于某⼀误差范围时即完成了⼀次转换。

数字电路实验三:数字电压表(设计报告)

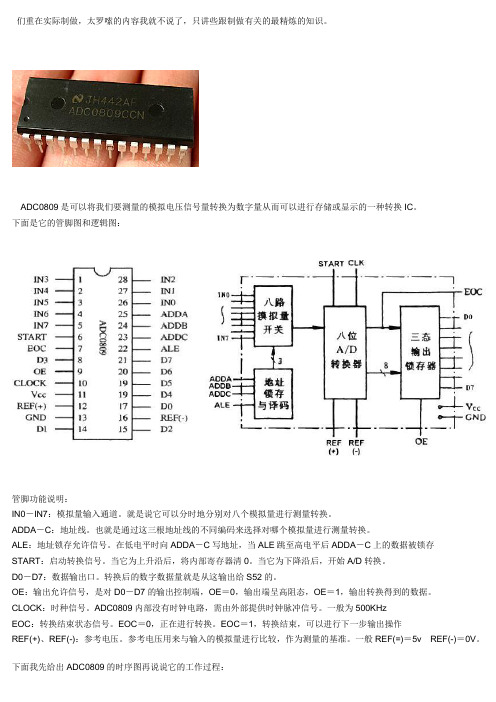

数字电路实验三:数字电压表(设计报告)数电实验3设计报告实验名称:数字电表实验目的:1.掌握组合逻辑与时序逻辑电路的设计方法及调试方法2.熟练掌握常用MSI逻辑芯片的功能及使用方法3.初步掌握Verilog HDL数字系统设计方法4.熟悉PLD实验箱的结构和使用及Quartus II软件的基本操作5.掌握采用Quartus II软件和实验箱设计实现逻辑电路的基本过程设计任务及要求:1、利用FPGA 与ADC0809 设计一个数字电压表,能够测量0-5V 之间的直流电压值,四位数码显示。

2、在实验电路板上焊接插座,将ADC0809 安装在插座上。

3、选择一路模拟量输入通道(如:IN0),经可调电位器送入0-5V 的直流电压。

4、ADC0809 时序由FPGA 控制,ADC 转换输出的数字量(D7-D0)送回FPGA,转换结果由实验箱上的LED 数码管以十进制形式显示。

5、ADC0809 的VREF 接+5V 电压。

6、FPGA 与ADC0809 之间接口利用实验箱上的“彩色液晶”接口。

程序设计过程:1、定义程序名、输入输出量和初始化Moduleadc_cc(clkin,rst,clkout,sel,data,start,eoc,ale,oe,seg_com,seg_data); input clkin; //时钟输入50MHZ inputrst;inputeoc; //ADC0809input [7:0] data; //输入八位数据output clkout; //时钟输出output start; //ADC0809起始信号 output [2:0] sel;//转换通道 output ale; //ADC0809 outputoe;//ADC0809 output [7:0] seg_com; //位选 output [7:0] seg_data;//段选parameter CLK_FREQ = 'D50_000_000;//系统时钟50MHZ parameter CLK_out_FREQ ='D500_000;//输出时钟parameter state_pre = 0; //sel 状态1parameter state_pre2 = 1; //ale 状态2 parameter state_start =2; //start 状态3 parameter state_conv = 3; //conv 状态4parameter state_wait = 4; // 状态5 parameter state_readpre = 5;// 状态6 parameter state_read = 6;//over // 状态7reg [2:0] sel; //定义寄存器 reg ale;//定义寄存器 reg start; //定义寄存器 regoe; //定义寄存器reg [7:0] data_led; //LED显示数据 reg[31:0] DCLK_DIV; //32位计数器regclkout; //提供ADC0809时钟500KHZ reg [3:0]state = state_pre;2、按照PDF所给出的时序图进行编程对照时序图,使ADC0809按上图方式工作进行编程always @ (negedgeclkout) case (state) state_pre : begin sel[2:0] <='b000; //ABC 000 通道0 state <= state_pre2;//转到状态2 oe<= 0; //OE拉低 end state_pre2 :begin ale <= 1; state <= state_start; endstate_start : begin start <= 1; ale<= 0; state <=state_conv; end state_conv : begin ale <= 0;start <= 0; state <= state_wait; end state_wait :begin if(eoc) begin state <= state_readpre; endend state_readpre : begin oe<= 1; state <= state_read; end state_read : begin data_led = data; state <= state_pre; end endcase//ALE拉高 //转到状态3 //START拉高 //转到状态4//ALE拉低锁定 //START拉低 AD启动 //转到状态5 //查询EOC是否被拉高 //转到状态6 //输出使能拉高 //转到状态7//开始读数据 //重新回到状态1 进行下一次AD转换 3、将AD转换结果用数码管显示。

AD0809详解

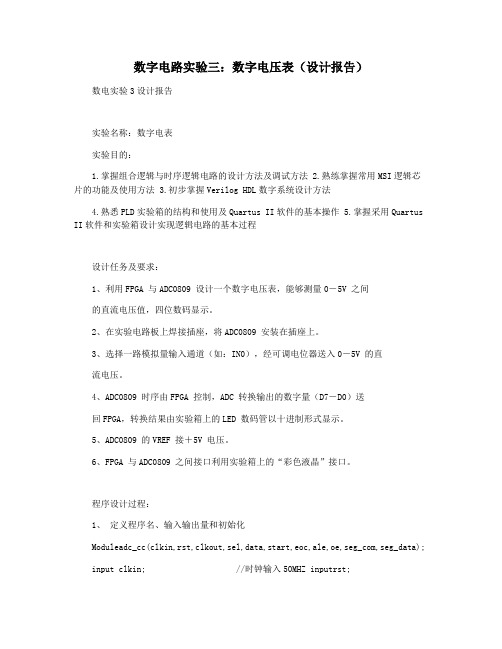

们重在实际制做,太罗嗦的内容我就不说了,只讲些跟制做有关的最精炼的知识。

ADC0809是可以将我们要测量的模拟电压信号量转换为数字量从而可以进行存储或显示的一种转换IC。

下面是它的管脚图和逻辑图:管脚功能说明:IN0-IN7:模拟量输入通道。

就是说它可以分时地分别对八个模拟量进行测量转换。

ADDA-C:地址线。

也就是通过这三根地址线的不同编码来选择对哪个模拟量进行测量转换。

ALE:地址锁存允许信号。

在低电平时向ADDA-C写地址,当ALE跳至高电平后ADDA-C上的数据被锁存START:启动转换信号。

当它为上升沿后,将内部寄存器清0。

当它为下降沿后,开始A/D转换。

D0-D7:数据输出口。

转换后的数字数据量就是从这输出给S52的。

OE:输出允许信号,是对D0-D7的输出控制端,OE=0,输出端呈高阻态,OE=1,输出转换得到的数据。

CLOCK:时种信号。

ADC0809内部没有时钟电路,需由外部提供时钟脉冲信号。

一般为500KHzEOC:转换结束状态信号。

EOC=0,正在进行转换。

EOC=1,转换结束,可以进行下一步输出操作REF(+)、REF(-):参考电压。

参考电压用来与输入的模拟量进行比较,作为测量的基准。

一般REF(=)=5v REF(-)=0V。

下面我先给出ADC0809的时序图再说说它的工作过程:它的工作过程是这样的,①在IN0-IN7上可分别接上要测量转换的8路模拟量信号。

有人问了,可不可以只接一路?我就只想测一个模拟信号。

当然可了②将ADDA-ADDC端给上代表选择测量通道的代码。

如000(B)则代表通道0;001(B)代表通道1;111则代表通道7。

③将ALE由低电平置为高电平,从而将ADDA-ADDC送进的通道代码锁存,经译码后被选中的通道的模拟量送给内部转换单元。

④给START一个正脉冲。

当上升沿时,所有内部寄存器清零。

下降沿时,开始进行A/D转换;在转换期间,START保持低电平。

基于FPGA和adc0809的数字电压表的设计

基于FPGA的数字电压表的设计0 引言传统的数字电压表设汁通常以大规模ASIC(专用集成电路)为核心器件,并辅以少量中规模集成电路及显示器件构成。

ASIC完成从模拟量的输入到数字量的输出,是数字电压表的心脏。

这种电压表的设计简单、精确度高,但是这种设计方法由于采用了ASIC器件使得它欠缺灵活性,其系统功能固定,难以更新扩展。

后来发展起来的用微处理器(单片机)控制通用A/D转换器件的数字电压表的设计的灵活性明显提高,系统功能的扩展变得简单,但是由于微处理器的引脚数量有限,其控制转换速度和灵活性还是不能满足日益发展的电子工业的需求。

而应用EDA(电子设汁自动化)技术及FPGA(现场可编程门阵列),其集成度高、速度快、性能十分可靠、用户可自由编程且编程语言通俗易懂、系统功能扩展非常方便[1]。

采用FPGA芯片控制通用A/D转换器可使速度、灵活性大大优于由微处理器和通用A/D转换器构成的数字电压表。

1 系统设计原理本设计利用ADC0809作为电压采样端口,FPGA作为系统的核心器件,用LED(发光二极管)进行数码显示。

采用Alterla公司FLEX10K系列EPF10K20TC144-4芯片FPGA作为系统的核心器件,负责ADC0809的A/D转换的启动、地址锁存、输入通道选择、数据读取。

同时,把读取的8位二进制数据转换成便于输出的3位十进制BCD码送给数码管,以显示当前测量电压值。

这些工作由ADC0809转换控制模块、数据转换模块、译码模块完成。

2 FPGA软件设计及模块仿真2.1 A/D转换控制模块的软件设计本模块完成ADC0809的初始化、A/D转换的启动、地址锁存、通道选择、状态读取及数据读取、数据锁存等功能。

此模块的软件设计主要采用VHDL的多进程状态机完成[4]。

工作时序如下:上电瞬问,FPGA初始化,ADD置成"01",状态机处于第1个状态,此时ALE、START、OE、LOCK(数据锁存信号)均置0,初始化ADC0809。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA与ADC0809接口电路详解

注:(1)本程序基于FPGA和vhdl编写

有详尽的程序解释和原理分析

以及原理图,状态图

(2)对于adc0809具体资料可上网查在此不累述

一.FPGA与ADC0809的接口电路图原理

二.关于ADC0809的说明(重点)

(1)ale信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)oe信号(引脚)en使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上

(3)eoc信号(引脚):eoc为高电平时完成转换,为低电平时正在转换。

(4)start信号(引脚):要给start线送一个100ns宽的启动正脉冲,start下跳沿时,开始进行A/D转换,在转换期间start以保持低电平。

三.转换状态图

对于状态图的真值表未列出 注意对应的注释为vhdl 语句

ale<='1';start<='0';en<='0';

----eoc='1' ale<='0';start<='0';en<='0';--再次检测数据是否转换完 if eoc='0' then next_state<=st4;

else next_state<=st5;

器,将数据送入数据总线

存器

四.ADC0809采样接口电路程序

--*********ADC0809采样控制*************

--******因为FPGA 的时钟频率为50MHz ,则256分频后,即ADC0809输入时钟为195KHz****** --******对ADC0809进行简单的采样控制,得到的数据进FPGA 送到8个并排的数码管显示***** library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity PL_AD is

port ( d : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据输入FPGA clk,eoc: in std_logic; --clk 为系统时钟,eoc 为ADC0809转换结束信号输入FPGA lock1,start, ale,en: out std_logic; --ADC0809控制信号FPGA 输出信号 abc_in :in std_logic_vector(2 downto 0); --模拟选通信号

abc_out :std_logic_vector(2 downto 0);--ADC0809模拟信号选通信号

q : out std_logic_vector(7 downto 0));送至8个并排数码管信号FPGA 输出数字信号 end pl_AD;

architecture behav of PL_AD is

type states is ( st0,st1, st2, st3, st4,st5,st6);--定义状态类型枚举类型

signal current_state, next_state:states:=st0;--定义总体两个状态现态和次态并且初值为st0态

signal regl :std_logic_vector(7 downto 0);--定义中间寄存器

signal lock : std_logic;

signal qq:std_logic_vector(7 downto 0);--定义计数器用于分频

begin

com:process(current_state,eoc) –此进程主要是驱动ADC0809工作即数据转换过程

begin

case current_state is

when st0=>next_state<=st1;ale<='0';start<='0';en<='0';--准备

when st1=>next_state<=st2;ale<='1';start<='0';en<='0';--三个地址信号送入地址锁存器

when st2=>next_state<=st3;ale<='0';start<='1';en<='0';--开始数据转换

when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完

if eoc='1' then next_state<=st3;

else next_state<=st4;

end if;

when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完

if eoc='0' then next_state<=st4;

else next_state<=st5;

end if;

when st5=>next_state<=st6;ale<='0';start<='0';en<='1'; --打开输出数据锁存器,将数据送入数据总线

when st6=>next_state<=st0;ale<='0';start<='0';en<='1';regl<=d;--打开输出数据锁存器,将数据送入寄存器regl when others=> next_state<=st0;ale<='0';start<='0';en<='0';

end case;

end process;

clock:process(clk) --对系统时钟进行分频,得到驱动ADC0809的时钟信号

begin

if clk'event and clk='1' then qq<=qq+1;

if QQ="01111111" THEN lock<='1';--实现分频

current_state <=next_state;--在lock上升沿,转换至下一状态

elsif qq<="01111111" then lock<='0';

end if;

end if;

end process;

q<=regl;--寄存器数据输出即FPGA输出

lock1<=lock;

abc_out<=abc_in;--模拟选通信号送往ADC0809

end behav;

注:有错

when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完

if eoc='1' then next_state<=st3;

else next_state<=st4;

end if;

when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完

if eoc='0' then next_state<=st4;

else next_state<=st5;

end if;

不过我这里的注释好像错了,这两个when合起来才是检测数据是否转换完的。

正确的注释是:

when st3=> ale<='0';start<='0';en<='0';--检测EOC的下降沿

if eoc='1' then next_state<=st3;--如果eoc=1则保持在st3

else next_state<=st4;--否则进入下一状态

end if;

when st4=> ale<='0';start<='0';en<='0';--检测eoc的上升沿

if eoc='0' then next_state<=st4;--如果eoc=0则保持在st4

else next_state<=st5;--否则进入下一状态

end if;

看了ADC0809的工作时序图就知道了:

start是转换启动信号,一个正脉冲后A/D开始转换;ale是3位通道选择地址信号锁存信号。

当模拟量送至某一输入端时,有3位地址信号选择,而地址信号由ALE锁存。

EOC是转换情况状态信号,当启动装换约100us后,eoc将产生一个负脉冲,以示转换完成,在eoc的上升沿后,且输出使能信号enanle为高电时,则打开三态缓冲器,把转换好的8位数据送入数据总线,这样便完成了一次转换。