数字电子技术模拟试题1

《数字电子技术》模拟试题及答案6页word

《数字电子技术》模拟试题一、填空题(每题2分,共20分)1、十六进制数97,对应的十进制数为 151。

2、“至少有一个输入为0时,输出为 0 ”描述的是与运算的规则。

3、 4 变量逻辑函数有16个最小项。

4、基本逻辑运算有: 与 、 或 和 非 运算。

5、两二进制数相加时,不考虑低位的进位信号是 半 加器。

6、TTL 器件输入脚悬空相当于输入 高 电平。

7、RAM 的三组信号线包括: 数据 线、地址线和控制线。

8、采用四位比较器对两个四位数比较时,先比较 最高 位。

二、单项选择题(每个3分,共15分) 1、图1的国标逻辑符号中 B 是异或门。

图12、下列逻辑函数表达式中可能存在竞争冒险的是 C 。

A ))((C B B A F ++= B ))((C B B A F ++= C ))((C B B A F ++= D ))((C B B A F ++=3、下面逻辑式中,不正确的是_ A___。

A.C B A ABC ⋅⋅=B. A AB A +=C. ()A A B A +=D. AB BA =4、时序逻辑电路中必须有___B___。

A. 输入逻辑变量 B. 时钟信号C. 计数器D. 编码器5、有S1,S2两个状态,条件 B 可以确定S1和S2不等价。

A. 输出相同B. 输出不同C. 次态相同D. 次态不同三、简答题(共10分)1、证明:B A B A A +=+(4分)解:B A B A B A A A +=+⋅=+⋅+)()()左边=(1 2、某逻辑函数的真值表如表1所示,画出卡诺图。

(6分) 表1 某逻辑函数的真值表A B C F 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 X 1 0 0 X 1 0 1 0 1 1 0 1 111X四、分析题(20分)图2分析图2所示电路的逻辑功能。

1)列出其时钟方程:(2分) CP1=CP ↑;CP0=CP ↑。

2)列出其驱动方程:(4分)ZJ1=Q0;K1= 1 ;J0=1Q ;K0=11Q X Q X +⋅或。

数字电子技术模拟试题及答案

《数字电子技术》模拟试题 20分)一、填空题(每题2分,共 1511、十六进制数97 。

,对应的十进制数为 0 时,输出为2”描述的是与运算的规则。

、“至少有一个输入为 0 变量逻辑函数有16个最小项。

、 4 3 运算。

非和 4、基本逻辑运算有: 与、或加器。

半 5、两二进制数相加时,不考虑低位的进位信号是电平。

高 6、TTL器件输入脚悬空相当于输入线、地址线和控制线。

数据 7、RAM的三组信号线包括:位。

最高8、采用四位比较器对两个四位数比较时,先比较15分)二、单项选择题(每个3分,共的国标逻辑符号中是异或门。

B 1、图1图1C 。

2、下列逻辑函数表达式中可能存在竞争冒险的是B)(B?(A?C)F? B A )B?C)(?(A?BFF?(A?B)(B?C)F?(A?B)(B?C) D C3、下面逻辑式中,不正确的是_ A___。

ABC?A?B?C B. A. A??ABA D. C. AA??B)A(BAAB?4、时序逻辑电路中必须有___B___。

A. 输入逻辑变量B. 时钟信号C. 计数器D. 编码器5、有S1,S2两个状态,条件 B 可以确定S1和S2不等价。

A. 输出相同次态不同D. 次态相同C. 输出不同B.10分)三、简答题(共A??B左边=(A?)(A?B)(?1A?A?B)?解:分) 1、(证明:4B?BA?A?A12、某逻辑函数的真值表如表所示,画出卡诺图。

(6分)某逻辑函数的真值表 1 表F B A C0 0 0 01 1 0 01 0 1 0X 1 1 0X 0 0 10 0 1 11 1 0 1X1 11分)四、分析题(20Z图2分析图2所示电路的逻辑功能。

1)列出其时钟方程:(2分) CP1=CP↑;CP0=CP↑。

2)列出其驱动方程:(4分)Q1;K0==1 ;J0。

Q0J1=;K1=1?Q?Q1或XX3)列出其输出方程:(1分)Z=XQ1Q0n?1n?1?QQ1Q0Q?Q1?Q0?XQ1或Q1?Q0?XQ1Q04)求次态方程:4(分);10分)9)作状态表及状态图(5.五、波形题(10分)出图如3所示,试画的,入已知输信号XY,Z波形的波形。

数字电子技术基础习题及答案

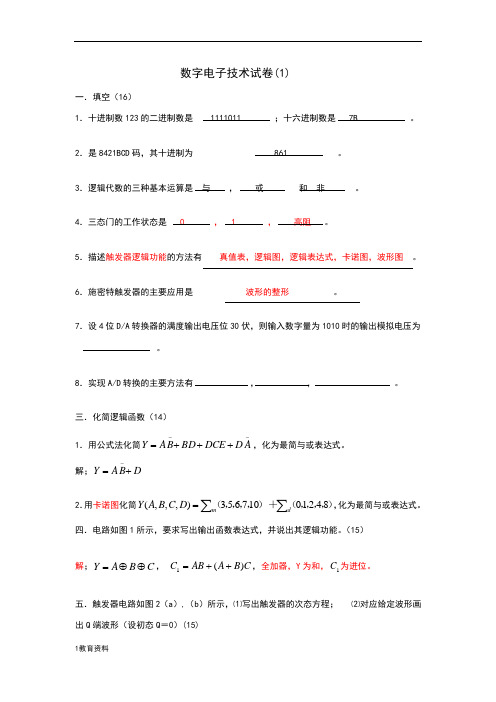

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。

8.实现A/D 转换的主要方法有 , , 。

三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=mdD C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

(15)数字电子技术试卷(2)二.填空(16)1.十进制数的二进制数是;十六进制数是。

2.逻辑代数中逻辑变量得取值为 0、1 。

3.组合逻辑电路的输出状态只与当前输入有关而与电路原状态无关。

4.三态门的输出有0、1、高阻,三种状态,当多个三态门的输出端连在一根总线上使用时,应注意只能有1个三态门被选通。

5.触发器的基本性质有有两个稳态,在触发信号作用下状态可相互转变,有记忆功能6.单稳态触发器的主要应用是延时。

数字电子技术试卷及答案(1)

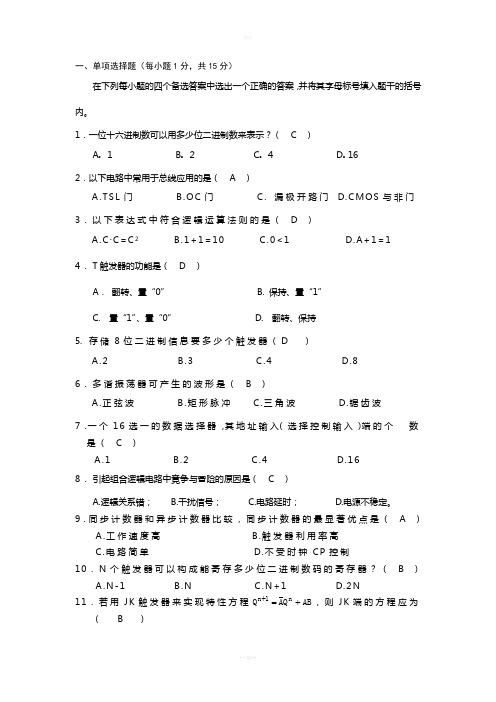

一、单项选择题(每小题1分,共15分)在下列每小题的四个备选答案中选出一个正确的答案,并将其字母标号填入题干的括号内。

1.一位十六进制数可以用多少位二进制数来表示?( C )A . 1B . 2C . 4D . 16 2.以下电路中常用于总线应用的是( A )A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D )A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是( D )A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D )A.2B.3C.4D.8 6.多谐振荡器可产生的波形是( B )A.正弦波B.矩形脉冲C.三角波D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C )A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C )A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为( B )A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的DA C ,其输出电平的级数是( C )A.4B.10C.1024D.10013.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D )A.2B.4C.8D.3214.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C )A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B )A.0.7RC ;B.1.1RC ;C.1.4RC ;D.1.8RC ;二、多项选择题(每小题1分,共5分)在下列每小题的四个备选答案中有二至四个正确答案,请将正确答案全部选出并将其字母标号填入题干的括号内;少选错选都不得分。

数电期末模拟题及答案.doc

WORD格式《数字电子技术》模拟一题一、单项选题择(2× 10 分)1.下列等式成立的是()A、A⊕1=AB、 A⊙0=AC、 A+AB=AD、 A+AB=B2.函数 F=(A+B+C+D)(A+B+C+D)(A+C+D)的标准与或表达式是()A、 F=∑ m(1,3,4,7,12)B、F=∑m(0,4,7,12)C、 F=∑ m(0,4,7,5,6,8,9,10,12,13,14,15)D、 F=∑ m(1,2,3,5,6,8,9,10,11,13,14,15)3.属于时序逻辑电路的是()。

A、寄存器B、 ROMC、加法器D、编码器4.同步时序电路和异步时序电路比较,其差异在于后者()A、没有触发器B、没有统一的时钟脉冲控制C、没有稳定状态D、输出只与内部状态有关,与输入无关5.将容量为256× 4 的 RAM扩展成1K× 8 的 RAM,需()片 256× 4 的 RAM。

A、 16B、 2C、 4D、 8n16.在下图所示电路中,能完成 Q0 逻辑功能的电路有()。

A、 B、 C、D、7.函数 F=AC+AB+BC,无冒险的组合为()。

A、 B=C=1B、 A=0, B=0C、 A=1, C=0D、 B=C=O8.存储器RAM在运行时具有()。

A、读功能B、写功能C、读 / 写功能D、无读 / 写功能9 .触发器的状态转换图如下,则它是:A=1()01 A=0 A、 T 触发器A=0 B、 RS触发器C、 JK 触发器A=1D、 D 触发器10.将三角波变换为矩形波,需选用()A、多谐振荡器B、施密特触发器C、双稳态触发器D、单稳态触发器二、判断题( 1× 10 分)() 1、在二进制与十六进制的转换中,有下列关系:( 1001110111110001)B=( 9DF1)H() 2、8421 码和 8421BCD码都是四位二进制代码。

() 3、二进制数 1001 和二进制代码 1001 都表示十进制数 9。

数字电子技术试题(1-5章)

第1章 数制和码制一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数(10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数(1001010.011001)2 =( )8 =( )16。

一、填空题答案:1.26、32、1A ;2.100011、43、 23;3.10101001、A9、169;4.1001011、113、75;5.1000101、45、105;6.2331、4D9;7.112.31、4A.64。

第2章 逻辑代数基础一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=;3. ()()()()Y AB BC AC ''''=; 4. Y A '=;5.1Y =; 6.1Y =; 7.Y A B =+。

数字电子技术测试试卷与答案精选全文完整版

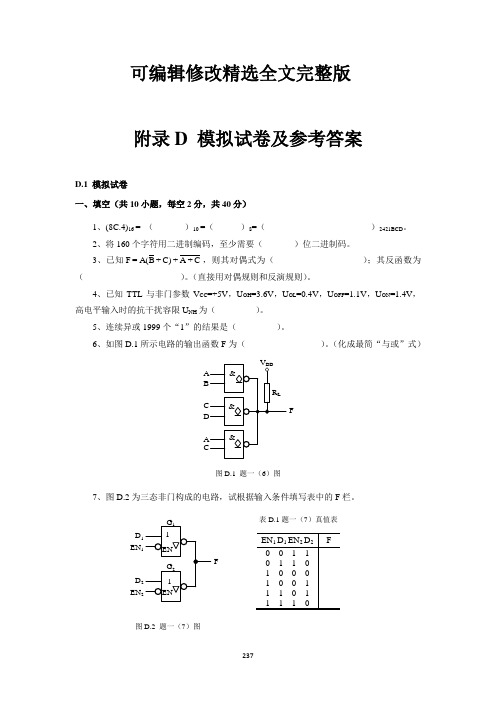

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

数字电子技术期末模拟卷1答案

数字电子技术期末模拟卷1答案(总4页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--系、班 姓 名 座 号…………………密……………封……………线……………密……………封……………线…………………《数字电子技术》课程考试题(1答卷)( 年 月 日) 题 号一 二 三 四 五 总分 复核人得 分评卷人一、单项选择题(在每小题的备选答案中选出一个正确的答案,并将答案的号码填在括号内。

每小题2分,共20分) 1、指出下列各种触发器中,哪些可以用来构成移位寄存器和计数器( 2 )。

(1) 基本RS 触发器(2)边沿JK 触发器(3)同步RS 触发器(4)同步D 锁存器 2、构成一个9进制加法计数器共需( 4 )个触发器。

(1)3 (2)10 (3)2 (4)4 3、基本RS-FF 由二个与非门或者由二个或非门交叉构成,由二个与非门构成的基本RS-FF 输入端触发信号是( 1 )。

(1) 低电平 (2)高电平 (3)脉冲前边沿 (4)脉冲后边沿 4、用CMOS 门电路组成的单稳态电路,脉冲宽度Tw 由(1 )决定。

(1)R 、C (2)触发信号 (3)电源电压 (4)以上都是 5、用若干RAM 实现位扩展而组成多位的RAM 时,其方法是将下列选项中的( 2 )以外的部件相应地并联在一起。

(1)地址线 (2)数据线(输出线) (3)片选信号线 (4)读/写线 6、在一个N 位计数器中,时钟信号到达时,各触发器的翻转有先有后,这种触发器称为( 2 )。

(1)同步计数器 (2)异步计数器 (3)时空计数器 (4)移位寄存计数器7.下列函数式中,是最小项之和形式的为( B )8.和TTL 电路相比,CMOS 电路最突出的优势在于( D ) A .可靠性高; B .抗干扰能力强; C .速度快; D .功耗低。

9.可以将输出端直接并联实现“线与”逻辑的门电路是(D ) A .三态输出的门电路; B .推拉式输出结构的TTL 门电路; C .互补输出结构的CMOS 门电路; D .集电极开路输出的TTL 门电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西南交通大学数字电子技术学期考试试题一

一. 简答填空题(共20分,第6小题每空2分,其它每空1分)

1.某数字信号的逻辑值为0111010,设高电平电压为5V,低电平电压为0V。

试绘出该信号的数字波形。

波形:

2.已知某时序电路的状态转换表如下,如果初态为S0,输入序列为X=110101101时,则输出序列为。

输入原态

X

01

S0S3/1S1/0

S1S3/1S2/0

S2S3/1S0/0

S3S1/1S2/0

3.写出下图所示各门电路的输出状态(0或1)。

已知V IH=3.6V,V IL=0.4V,图(a)、(b)是TTL门,图(c)、(d)是CMOS门。

4.一个存储容量为256K×8的存储器,地址线有条,数据线有条。

5.如要将一个最大幅度为5.1V的模拟信号转换为数字信号,要求输入每变化20mv,输出信号的最低位(LSB)发生变化,应选用位A/D

次态/输出

转换器,其分辨率为 %。

6. 四个电路输入V I 、输出V O 的波形如图所示,试简答分别实现下列功能的最简电路类型(不必画出电路)。

7. 写出下图所示PLD 的输出F 1、F 2逻辑表达式。

二. 逻辑代数和组合逻辑

1. 公式法化简下列函数为最简与或式。

(4分)

(a )

(b )

(c )

(d )

F 1= F 2=

&

&

&

&

=1

=1

≥1

≥1

1

BD

C

D

A

B

A

C

B

A

D

C

B

A

F+

+

+

+

=

)

,

,

,

(

2. 分析以下组合电路的功能,要求写出图示电路的逻辑表达式(3分),列出其真值表(2分),并说明电路的逻辑功能(2分)。

三. 用或非门设计一个组合电路。

其输入为8421BCD码,输出L当输入数能被4整除时为1,其他情况为0。

(0可以被任何整数整除,要求有设计过程,给出电路图)

(1)建立真值表(3分)

(2)写出函数的最小项表达式(3分)

(3)化简函数表达式(4分)

(4)用或非门实现。

(4分)

四. 已知时序电路如图所示。

1.请写出各触发器的驱动方程和次态方程。

(5分)

2.画出电路的状态(Q1Q0)转换图。

(5分)

J0Q0 CP J1Q1 CP

CP Q0Q1 1

五. 下图为一个电路的状态转换图。

现准备用D 触发器实现该电路,请写出触发器的驱动方程和输出方程。

(S 0、S 1、S 2的编码分别为00、01、11)(15分)

六. 电路见下图。

请问:

1. 74161接成了几进制的计数器?(3分) 2. 画出输出CP 、Q 0、Q 1、Q 2、L 的波形。

(7分)

(器件功能表见最后一页)

七. 一种能产生7位编码信息的编码电路如图所示。

试分析:(10分)

S 0

S 1 S 2

1/0

1/0

1/1

0/0

0/0

0/0

X/Z 输入/

输出

S 1 Q 0 Q 1 Q 2 Q S 2 74161 LD

E Y

Y D 7 D 6 D 5 D 4

L

S 0 S 1 S 2

&

1

1 CP

1

1.接通电源但未按下按键P时各IC的工作状态;

2.说明按下图示位置按键P时,编码值是如何存入8D寄存器IC5中的;

3.写出按键P时,b7b6b5b4b3b2b1的编码值。

注:IC3的功能描述:

G1G2:使能信号,低电平有效;

A0A1A2A3:地址输入;

Y0Y1······Y15:译码输出,低电平有效;

使能信号有效时,各译码输出的表达式见表:

八.用555定时器构成的一种触发定时电路如图所示。

(10分)

试回答:

1.电路的稳态Q=?

2.v i为何种边沿触发?触发信号幅值应为多大?

3.画出v c及v o从触发翻转到定时结束的波形;

4.导出输出信号脉宽t w的计算公式。

(注:触发信号的脉冲宽度小于输出信号的脉冲宽度)

附:芯片功能表

同步4位二进制计数器74161的符号和功能表如下:

功能表:符号:

CP R d S1S2LD功能

X0X X X清零

S2Q0Q1Q2Q

X1011保持

S174161LD

X1X01保持

↑1110置数

↑1111计数

其中输出Q3是最高位,输入D3是最高位,C是进位信号,74161只当Q3Q2Q1Q0 =1111时,C=1。

8选1选择器74151的符号和功能表如下:

功能表:符号:

8D寄存器内部电路:。