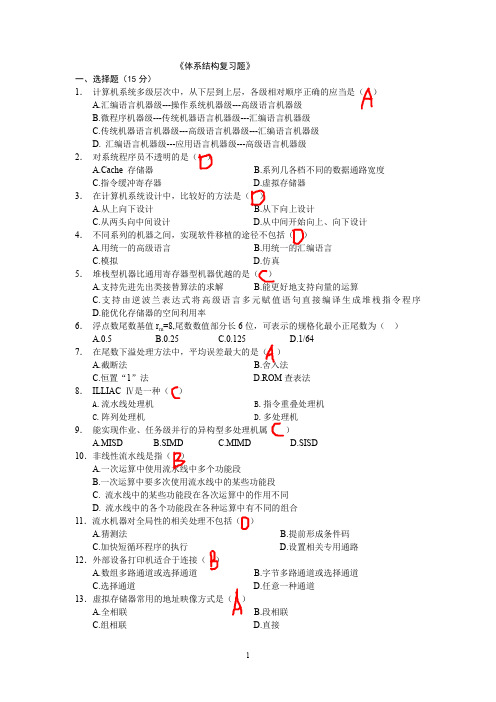

体系结构复习题

计算机系统结构复习试题及答案(非计算)

计算机系统结构复习试题及答案(⾮计算)⼀.名词解释计算机系统结构:传统机器程序员所看到的计算机属性,即概念性结构与功能特性。

在计算机技术中,把这种本来存在的事物或属性,但从某种⾓度看⼜好像不存在的概念称为透明性。

系列机:由同⼀⼚家⽣产的具有相同系统结构、但具有不同组成和实现的⼀系列不同型号的计算机。

同构型多处理机系统:由多个同类型或⾄少担负同等功能的处理机组成,它们同时处理同⼀作业中能并⾏执⾏的多个任务。

堆栈型机器:CPU 中存储操作数的单元是堆栈的机器。

累加器型机器:CPU 中存储操作数的单元是累加器的机器。

通⽤寄存器型机器:CPU 中存储操作数的单元是通⽤寄存器的机器。

数据相关:考虑两条指令i 和j,i 在j 的前⾯,如果下述条件之⼀成⽴,则称指令j 与指令 i 数据相关:(1)指令j 使⽤指令i 产⽣的结果;(2)指令j 与指令k 数据相关,⽽指令k ⼜与指令i 数据相关。

定向:⽤来解决写后读冲突的。

在发⽣写后读相关的情况下,在计算结果尚未出来之前,后⾯等待使⽤该结果的指令并不见得是马上就要⽤该结果。

如果能够将该计算结果从其产⽣的地⽅直接送到其它指令需要它的地⽅,那么就可以避免停顿。

向量处理机:指令级并⾏:简称ILP。

是指指令之间存在的⼀种并⾏性,利⽤它,计算机可以并⾏执⾏两条或两条以上的指令。

指令的动态调度:是指在保持数据流和异常⾏为的情况下,通过硬件对指令执⾏顺序进⾏重新安排,以提⾼流⽔线的利⽤率且减少停顿现象。

是由硬件在程序实际运⾏时实施的。

指令的静态调度:是指依靠编译器对代码进⾏静态调度,以减少相关和冲突。

它不是在程序执⾏的过程中、⽽是在编译期间进⾏代码调度和优化的。

失效率:CPU 访存时,在⼀级存储器中找不到所需信息的概率。

失效开销:CPU 向⼆级存储器发出访问请求到把这个数据调⼊⼀级存储器所需的时间。

强制性失效:当第⼀次访问⼀个块时,该块不在Cache 中,需要从下⼀级存储器中调⼊Cache,这就是强制性失效。

软件体系结构与设计模式期末复习

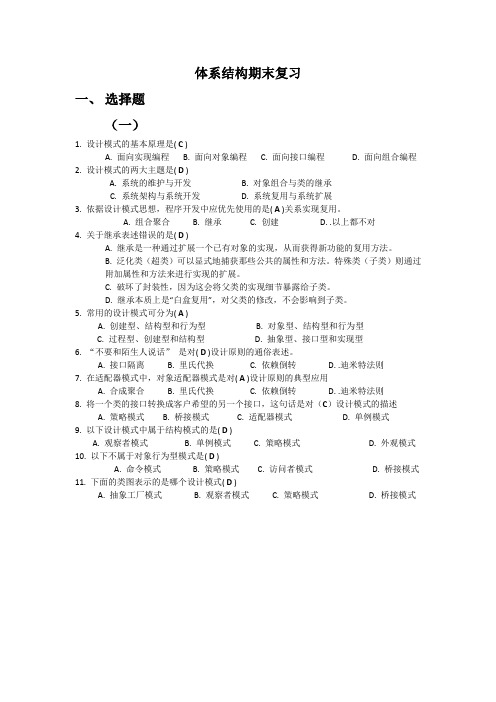

体系结构期末复习一、选择题(一)1. 设计模式的基本原理是( C )A. 面向实现编程B. 面向对象编程C. 面向接口编程D. 面向组合编程2. 设计模式的两大主题是( D )A. 系统的维护与开发B. 对象组合与类的继承C. 系统架构与系统开发D. 系统复用与系统扩展3. 依据设计模式思想,程序开发中应优先使用的是( A )关系实现复用。

A. 组合聚合B. 继承C. 创建D. .以上都不对4. 关于继承表述错误的是( D )A. 继承是一种通过扩展一个已有对象的实现,从而获得新功能的复用方法。

B. 泛化类(超类)可以显式地捕获那些公共的属性和方法。

特殊类(子类)则通过附加属性和方法来进行实现的扩展。

C. 破坏了封装性,因为这会将父类的实现细节暴露给子类。

D. 继承本质上是“白盒复用”,对父类的修改,不会影响到子类。

5. 常用的设计模式可分为( A )A. 创建型、结构型和行为型B. 对象型、结构型和行为型C. 过程型、创建型和结构型D. 抽象型、接口型和实现型6. “不要和陌生人说话”是对( D )设计原则的通俗表述。

A. 接口隔离B. 里氏代换C. 依赖倒转D. .迪米特法则7. 在适配器模式中,对象适配器模式是对( A )设计原则的典型应用A. 合成聚合B. 里氏代换C. 依赖倒转D. .迪米特法则8. 将一个类的接口转换成客户希望的另一个接口,这句话是对(C)设计模式的描述A. 策略模式B. 桥接模式C. 适配器模式D. 单例模式9. 以下设计模式中属于结构模式的是( D )A. 观察者模式B. 单例模式C. 策略模式D. 外观模式10. 以下不属于对象行为型模式是( D )A. 命令模式B. 策略模式C. 访问者模式D. 桥接模式11. 下面的类图表示的是哪个设计模式( D )A. 抽象工厂模式B. 观察者模式C. 策略模式D. 桥接模式12. Open-Close开闭原则的含义是一个软件实体( A )A. 应当对扩展开放,对修改关闭。

系统结构复习

中国地质大学(武汉)计算机学院吴湘宁计算机体系结构习题及答案第一章基础知识1.名词解释翻译解释模拟仿真透明性程序访问局部性[答案]略2. 一个经解释实现的计算机可以按功能划分为四级. 每一级为了执行一条指令需要下一级的N条指令. 若执行第一级的一条指令需要的时间为K ns, 那么执行第二、三、四级的一条指令各需要多少时间?3. 计算机系统按功能划分层次结构的好处主要体现在哪些方面?[答案] (1) 有利于理解软件, 硬件和固件在系统中的地位和作用;(2) 有利于理解各种语言的实质和实现途径;(3) 有利于推动计算机系统结构的发展;(4) 有利于理解计算机系统结构的定义.4. 什么是透明性? 对计算机系统结构, 下列哪些是透明的? 哪些是不透明的?1) 存储器的模m交叉存取; 2) 浮点数据表示; 3) I/O系统是采用通道方式还是I/O处理机方式; 4) 阵列运算部件; 5) 数据总线宽度; 6) 通道是采用结合型的还是独立型的; 7) 访问方式保护; 8) 程序性中断; 9) 串行、重叠还是流水控制方式; 10) 堆栈指令; 11) 存储器的最小编址单位; 12) Cache存储器.[答案] 一种本来是存在的事务或属性, 但从某种角度看却好像不存在, 称为透明性.对计算机系统结构来说透明的是: 1), 4), 5), 6), 9), 12)对计算机系统结构来说不透明的是:2), 3), 7), 8), 10), 11)5. 什么是计算机体系结构? 什么是计算机组成? 什么是计算机实现? 并说明三者的关系和相互影响?[答案] 计算机系统结构是计算机系统的软, 硬件分界面, 是机器语言程序员或是编译程序员所需了解的计算机属性;计算机组成是计算机系统结构的逻辑事项;计算机实现是计算机组成的物理实现.三者的关系和互相影响为:(1) 具有相同系统结构的计算机可以采用不同的组成;(2)(2) 一种计算机组成可以采用多种不同的计算机实现;(3) 计算机组成、计算机实现对计算机系统结构有着很大的影响;(4) 计算机系统结构的设计不应限制计算机组成和实现技术,应能用于高档机,也可用于低挡机;(5) 在不同时期, 计算机系统结构,、组成和实现所包含的内容会有所变化,三者之间的界线常常很模糊.6. 从机器(汇编)语言程序员角度看, 以下哪些是透明的?1) 指令地址存储器; 2) 指令缓冲器; 3) 时标发生器; 4) 条件码寄存器; 5) 乘法器; 6) 主存地址寄存器; 7) 磁盘外设; 8) 先行进位链; 10) 通用寄存器; 11) 中断字寄存器.[答案] 对机器(汇编)语言程序员来说透明的有: 2), 3), 5), 6), 8), 9)对机器(汇编)语言程序员来说不透明的有: 1), 4), 7), 10), 11)7. 假设在一台40 MHz处理机上运行200 000条指令的目标代码, 程序主要由四种类型的指令所组成. 根据程序跟踪实验结果, 各类指令的混合比和每类指令的CPI值如表1.9所示.(1) 试计算在单处理机上执行上述该程序时的平均CPI;(2) 根据(1)所得到的CPI, 计算相应的MIPS速率及程序的执行时间.[答案] (1) 2.24 CPI (2) 17.86 MPIS; 0.0112 s8. 某工作站采用时钟频率为15 MHz、处理速率为10 MIPS的处理机来执行一个程序,假定每次存储器存取为1周期延迟, 试问:(1) 此计算机的有效CPI是多少?(2) 假定将处理机的时钟频率提高到30 MHz, 但存储器子系统速率不变, 这样, 每次存储器存取需要两个时钟周期. 如果30%的指令每条只需要一次存储存取, 而另外5%的指令每条需要两次存储存取, 还假定已知混合程序的指令数不变, 并与原工作站兼容, 试求改进后的处理机性能.[答案] (1) 1.5 CPI; (2) 15.8 MPIS9.什么是并行性?它分为哪两种类型?开发计算机系统并行性的主要技术途径有哪三个?沿这些途径分别发展出什么类型的计算机?[答案]略10.实现软件移植的途径有哪些?[答案]略11.什么是Flynn分类法,按照Flynn分类法可将计算机系统分为哪几类?[答案]略第二章指令系统1. 名词解释数据类型、数据表示、规格化浮点数、Huffman编码、扩展编码、RISC[答案]略2. 某模型机有8条指令I1~I8, 它们的使用频度分别为0.3, 0.3, 0.2, 0.1, 0.05, 0.02, 0.02, 0.01.(1) 试分别用Huffman编码和平均码长最短的等长扩展码(限定为两种码长)对其操作码进行编码.(2) 分别计算Huffman编码和等长扩展码编码的平均长度.[答案] (1) 操作码的Huffman编码和2-4等长扩展码编码如下表1所示.(2) Huffman编码的平均长度为2.38位; 等长扩展码编码的平均码长为2.8位.3. 某模型机有10条指令I1~I10, 它们的使用频度分别为0.3, 0.24, 0.16, 0.12, 0.07, 0.04, 0.03,0.02, 0.01, 0.01.(1) 计算机采用等长操作码表示时的信息冗余量.(2) 要求操作码平均码长最短, 试设计操作码的编码, 并计算所设计操作码的平均长度. (3) 设计2-5扩展操作码编码,并计算平均码长.(4) 设计2-4(2/8)等长扩展码编码,并计算平均码长. [答案] (1) 采用等长操作码表示时的信息冗余量为33.5%. (2) 操作码的Huffman编码如表2所示, 此种编码的平均长度为2.7位.(3) 操作码的2-5扩展码编码如表2所示, 此种编码的平均长度为2.9位.(4) 操作码的2-4(2/4)等长扩展码编码如表2所示, 此种编码的平均长度为2.92位.4. 何谓指令格式的优化? 操作码和地址码的优化一般采用哪些方法?[答案] 指令格式的优化是指通过采用多种不同的寻址方式, 地址制, 地址形式和地址码长度以及多种指令字长, 并将它们与可变长操作码的优化表示相结合, 就可以构成冗余度尽可能少的指令字. 操作码的优化采用扩展操作码编码法. 地址码优化有以下四种方法:(1) 在指令中采用不同的寻址方式;(2)(2) 在指令中采用多地址制;(3) 同一种地址制还可以采用多种地址形式和长度, 也可以考虑利用空白处来存放直接操作数或常数等;(4) 在以上措施的基础上, 还可以进一步考虑采用多种指令字长度的指令.5. 若某机设计有如下指令格式的指令:三地址指令12种, 一地址指令254种, 设计指令的长度为16位, 每个地址码字段的位数均为4位. 若操作码的编码采用扩展操作码, 问二地址指令最多可以设计多少种? [答案] 二地址指令最多可以设计48种.6. 一台模型机共有九条指令I1~I9, 各指令的使用频度分别为0.3,0.2,0.2,0.1,0.08,0.6,0.03, 0.02, 0.01. 该模型机有8位和16位两种指令字长. 8位字长指令为寄存器----寄存器(R--R)二地址类型, 16位字长指令为寄存器----存储器(R--M)二地址变址寻址类型.(1) 试设计有两种码长的扩展操作码, 使其平均码长最短, 并计算此种编码的平均码长. (2) 在(1)的基础上, 该机允许使用多少个可编址的通用寄存器?(3) 若采用通用寄存器作为变址寄存器, 试设计该机的两种指令格式, 并标出各字段的位数.(4) 计算变址寻址的偏移地址范围.[答案] (1) 操作码的2-5扩展码编码如表3所示, 此种编码的平均长度位2.9位.2) 在(1)的基础上, 该机允许使用8个可编址的通用寄存器.(3) 该机的两种指令格式及各字段的位数如下:R-R型: 操作码OP (2位) | 源寄存器RS (3位) | 目的寄存器Rd (3位)R-M型: 操作码OP (5位) | 源寄存器RS (3位) | 变址寄存器RX (3位) | 偏移地址 (5位)(4) 变址寻址的偏移地址范围为-16~+15.7. 简述CISC的特点.[答案] CISC的特点如下:(1) 庞大的指令系统;(2) 采用了可变长度的指令格式;(3) 指令使用的寻址方式繁多;(4) CISC指令系统中包括一些用于特殊用途的指令, 各种指令的使用频度相当悬殊.8. 从指令格式, 寻址方式以及平均CPI三个方面, 比较经典CISC和纯RISC体系结构.[答案] 略9.简述RISC设计的一般原则。

网络安全体系结构复习题

1.被动攻击主要是收集信息而不是进行访问,数据的合法用户对这种活动一点也不会觉察到。

被动攻击包括嗅探、信息收集等攻击方法在建立信息安全管理体系时,首先应该建立信息安全方针和目标2.OSI安全体系结构中定义了五大类安全服务,其中,数据机密性服务主要针对的安全威胁是窃听攻击3.建立和实施信息安全管理体系的重要原则是领导重视,全员参与,持续改进4.为保证计算机网络系统的正常运行,对机房内的三度有明确的要求,其三度是指温度,湿度和洁净度5.公钥基础设施(PKI)的核心组成部分是认证机构CA6.包过滤技术防火墙在过滤数据包时,一般不关心数据包的内容7.不属于CIDF体系结构的组件是自我防护单元8.计算机网络安全体系结构是指网络安全基本问题应对措施的集合9.密码学的目的是研究信息安全10.采用模拟攻击漏洞探测技术的好处是探测结果准确率高11.由于系统软件和应用软件的配置有误而产生的安全漏洞,属于配置错误12.根据美国联邦调查局的评估,80%的攻击和入侵来自企业内部网13.计算机病毒是一个程序14.P2DR(PPDR)模型是一种常用的计算机网络安全模型,包含4个主要组成部分,分别是:安全策略,防护,检测和响应15.对计算机网络安全构成威胁的因素可以概括为:偶发因素,自然因素和人为因素三个方面16.防火墙的体系结构一般可分为:双重宿主主机系统机构,屏蔽主机体系结构和屏蔽子网体系结构。

17.按照计算机网络安全漏洞的可利用方式来划分,漏洞探测技术可以划分为信息型漏洞探测和攻击型漏洞探测18.从系统构成上看,入侵检测系统应包括数据提取,入侵分析,相应处理和远程管理四大部分。

19.物理安全技术主要是指对计算机及网络系统的环境,场地,设备和人员等采取的安全技术措施。

20.密码体制从原理上可分为两大类,即单钥密码体制和双钥密码体制。

21.简述计算机网络安全的定义?计算机网络安全是指利用管理控制和技术措施,保证在一个网络环境里,信息数据的机密性,完整性及可使用性受到保护。

计算机体系结构复习题

4

(1) 选择适合于流水线工作的算法应先计算A1+B1、

A2+B2、A3+B3和A4+B4; 再计算(A1+B1) ×(A2×B2) (A3+B3) ×(A4+B4);

然后求总的结果。

(2) 画出时空图 (3) 计算性能

A 段 5

B

C

D

C× D A× B

A× B× C× D

A = A 1+ B 1 4 3 2 1 输 入 0 1 2 3 4 5 6 7 A B 8 C D 9 10 11 1 2 A× B C× D 13 14 时间 B = A 2+ B 2 C = A 3+ B 3 D = A 4+ B 4

计算机组成是计算机系统结构的逻辑实现。 计算机实现是计算机组成的物理实现。一种 体系结构可以有多种组成。一种组成可以有 多种实现。

4、计算机系统设计的量化设计原则有哪些?说 出它们的含义? 答:加速经常性事件的原则:对经常发生的情 况采用优化方法的原则进行选择,以得到更多 的总体上的改进。 Amdahl定律:加快某部件执行速度所能获得的 系统性能加速比,受限于该部件的执行时间占 系统中总执行时间的百分比。 CPU性能公式:执行一个程序所需的CPU时间, CPU时间 = 执行程序所需的时钟周期数×时钟 周期时间 程序的局部性原理:程序执行时所访问的80%是 程序代码的20%的部分。

6

7

8

9 A B

1 0 11 1 2 1 3 1 4 1 5 1 6 1 7 1 8 C D A× B C× D

时间

输 入

A1 A2 A3 A4 B1 B2 B3 B4

最新系统结构总复习题(附答案)

《计算机系统结构》期末考试复习题一、选择题:1、我们称由(B )实现的机器为虚拟机器。

A、硬件B、软件C、微程序D、固件2、计算机系统结构设计者所关心的是(C )所看到的的计算机结构。

A、硬件设计人员B、逻辑设计人员C、机器语言或汇编语言程序员D、高级语言程序员3、计算机组成是计算机系统结构的(B )。

A、硬件实现B、逻辑实现C、软件实现D、以上三种4、在计算机系统设计时,为了提高系统性能,应当注意(A )。

A、加快经常性使用指令的执行速度B、要特别精心设计少量功能强大的指令B、要减少在数量上占很小比例的指令的条数D、要加快少量指令的速度5、SIMD计算机可以处理(D )。

A、多指令流、单数据流B、单指令流单数据流C、多指令流多数据流D、单指令流多数据流6、在提高CPU性能的问题上,从系统结构角度,可以(C )。

A、提高时钟频率B、减少程序指令条数C、减少每条指令的时钟周期数D、减少程序指令条数和减少每条指令的时钟周期数7、冯.诺依曼计算机是(B )。

A、以存储器为中心B、以CPU为中心C、以处理输入/输出危重点D、以存储器与计算器为中心8、解决软件移植最好的办法就是(C )。

A、采用模拟方法B、采用仿真的方法C、采用统一高级语言D、采用统一标准设计计算机结构9、对计算机系统结构,下列透明的是(A )。

A、数据总线宽度B、浮点数表示C、CPU寄存器个数D、存储器的编址方法10、以下对系统程序员不透明的是(B )。

A、系列机各档不同的数据通路宽度B、虚拟存储器C、指令缓冲寄存器D、存储器读写缓冲寄存器11、在浮点数表示中,尾数的位数多少主要影响( B )。

A、表数范围B、表数精度C、表数效率D、运算实现容易程度12、当浮点数的尾数基值为(A )时,其表数效率最高(假如不考虑隐藏位)。

A、16B、8C、4D、213、当浮点数的尾数基值为( D )时,其表数精度最高,表数范围最大。

A、2B、8C、16D、2或414、当浮点数的尾数用原码表示,基值为2,阶码用移码表示,基值为2时,若尾数部分占23位(不含符号位),阶码占8位(含符号位),则表示的最大负数和最大正数分别为( C )。

计算机网络复习题

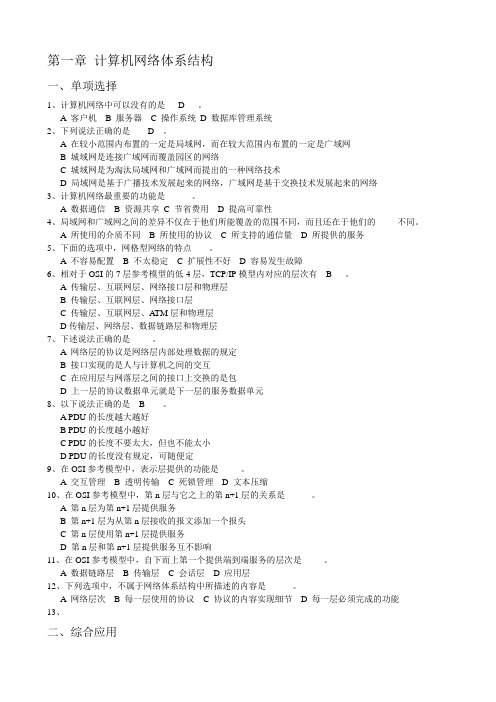

第一章计算机网络体系结构一、单项选择1、计算机网络中可以没有的是___D___。

A 客户机B 服务器C 操作系统D 数据库管理系统2、下列说法正确的是____D__。

A 在较小范围内布置的一定是局域网,而在较大范围内布置的一定是广域网B 城域网是连接广域网而覆盖园区的网络C 城域网是为淘汰局域网和广域网而提出的一种网络技术D 局域网是基于广播技术发展起来的网络,广域网是基于交换技术发展起来的网络3、计算机网络最重要的功能是______。

A 数据通信B 资源共享C 节省费用D 提高可靠性4、局域网和广域网之间的差异不仅在于他们所能覆盖的范围不同,而且还在于他们的_____不同。

A 所使用的介质不同B 所使用的协议C 所支持的通信量D 所提供的服务5、下面的选项中,网格型网络的特点____。

A 不容易配置B 不太稳定C 扩展性不好D 容易发生故障6、相对于OSI的7层参考模型的低4层,TCP/IP模型内对应的层次有__B___。

A 传输层、互联网层、网络接口层和物理层B 传输层、互联网层、网络接口层C 传输层、互联网层、ATM层和物理层D传输层、网络层、数据链路层和物理层7、下述说法正确的是_____。

A 网络层的协议是网络层内部处理数据的规定B 接口实现的是人与计算机之间的交互C 在应用层与网落层之间的接口上交换的是包D 上一层的协议数据单元就是下一层的服务数据单元8、以下说法正确的是__B____。

A PDU的长度越大越好B PDU的长度越小越好C PDU的长度不要太大,但也不能太小D PDU的长度没有规定,可随便定9、在OSI参考模型中,表示层提供的功能是_____。

A 交互管理B 透明传输C 死锁管理D 文本压缩10、在OSI参考模型中,第n层与它之上的第n+1层的关系是______。

A 第n层为第n+1层提供服务B 第n+1层为从第n层接收的报文添加一个报头C 第n层使用第n+1层提供服务D 第n层和第n+1层提供服务互不影响11、在OSI参考模型中,自下而上第一个提供端到端服务的层次是_____。

软件体系结构-复习题

《软件体系结构》习题一、单选题第一章概述1、软件开发模型大体上可以分为3种类型。

第1种是以软件需求完全确定为前提的;第2种是在软件开发初期阶段只能提供基本需求时采用的;第3种是以形式化为基础的变换模型。

A.协同模型B.瀑布模型C.变换模型D.迭代式模型2、根据《信息技术软件生存周期过程》标准,企业为实现ERP系统而准备招标书的活动属于生存周期基本过程中的过程,与该活动属于同一过程的活动还有。

A.总体规划B.系统实现C.获取D.供应A.启动B.准备投标C.系统需求分析D.项目管理3、螺旋模型是一种演进式的软件过程模型,结合了原型开发方法的系统性和瀑布模型可控性特点。

它有两个显著特点,一是采用的方式,逐步加深系统定义和实现的深度,降低风险;二是确定一系列,确保项目开发过程中的相关利益者都支持可行的和令人满意的系统解决方案。

A.逐步交付B.顺序C.循环D.增量A.实现方案B.设计方案C.关键点D.里程碑4、极限编程是一种重要的敏捷开发方法,包括策划、设计、编码和测试4个框架活动的规则和实践。

下面关于极限编程的叙述,错误的是。

A.极限编程中使用的重要技术是重构,既包括设计技术的重构,也包括构建技术的重构B.极限编程提倡在基本设计完成后立即进行编码实现,并进行测试C.极限编程活动中的关键概念之一是“结对编程”,推荐两个人面对同一台计算机共同开发代码D.极限编程过程中建立的单元测试应当使用一个可以自动实施的框架,支持代码修改后即时的回归测试策略5、把整个软件开发流程分成多个阶段,每一个阶段都由目标设定、风险分析、开发和有效性验证以及评审构成。

A.原型模型B.瀑布模型C.螺旋模型D.V模型6、某企业使用了某厂商的软件产品,随后该厂商又推出了这种产品的新版本。

该企业信息中心正在考虑是否需要升级该软件。

信息中心未做出立即更新软件版本的决定,最可能的原因是。

A.需要等待用户部门做出支付软件版本升级费用的预算B.用户部门还没有要求软件版本升级C.虽然新版软件在社会上已普遍使用,但信息中心还是担心存在潜在问题D.新版软件与其他用户部门正在使用的软件不兼容7、某小型软件公司欲开发一个基于Web的考勤管理系统,客户对系统的基本功能、表现形式等要求并不明确。

计算机系统结构复习题

1【简答题】传统的存储程序计算机的主要特征是什么?存在的主要问题是什么?目前计算机系统是如何改进的?正确答案:解:主要特征:(1)机器以运算器为中心;(2)采用存储程序原理;(3)存储器是按地址访问的、线性编址的空间;(4)控制流由指令流产生;(5)指令由操作码和地址码组成;(6)数据以二进制编码表示,采用二进制运算。

主要问题和改进:(1)问题:以运算器为中心,所有部件的操作都由控制器集中控制,导致慢速输入输出操作占用快速运算器矛盾,影响运算器效率发挥。

改进:各种分布式的I/O处理或输入输出方式如程序控制、DMA(直接存储器访问)方式、 I/O 处理机等。

(2)问题:数据和指令存放在同一存储器中,自我修改程序是难以编制、调试和使用的,不利于指令执行的重叠和流水。

改进:通过存储管理硬件的支持,由操作系统控制在程序执行过程中不准修改程序.(3)问题:访问存储器次数较多影响计算机系统性能。

改进:按内容访问的相联存储器CAM,大量使用通用寄存器,在CPU和主存之间设置高速缓冲存储器cache。

(4)问题:受程序计数器控制,程序执行只能串行、顺序执行.改进:改进CPU的组成,如采用重叠方式、先行控制、多操作部件甚至流水方式把若干条指令的操作重叠起来;采用向量处理技术、多机并行处理,总之通过并行处理技术进一步提升计算机系统速度。

(5)问题:需要指令功能更加丰富,但实现困难;计算机存储器容量大增,采用直接寻址方式指令中地址码位数不够.改进:出现了CISC和RISC指令系统,CISC用硬件实现大量丰富功能,RISC只包含使用频率高的少量指令;采用多种灵活的寻址方式,如间接寻址、相对寻址、变址寻址、基址寻址、页式寻址等。

2【简答题】通用寄存器型指令系统结构在灵活性和提高性能方面的优势主要体现在哪几个方面?正确答案:(1)寄存器的访问速度比存储器快很多;(2)对编译器而言,能更加容易、有效地分配和使用寄存器。

在表达式求值方面,通用寄存器型结构具有更大的灵活性和更高的效率。

计算机体系结构-复习题(附答案)-vip专享

《计算机体系结构》复习题一、填空题1. 推动计算机系统结构发展的主要动力是( 计算机应用 )。

2. ( 器件 )的发展是促使计算机系统结构不断发展的最活跃因素。

3. 衡量计算机系统性能可采用各种尺度,但最为可靠的衡量尺度是( 时间 )。

4. CPI表示执行每条指令所需的( 平均时钟周期数 )。

5. 计算机系统中的数据表示是指可由硬件直接辨认的( 数据类型 )。

6. 在向量处理中经常会遇到稀疏向量,为了节省存储空间和处理时间( 压缩向量 )的表示方法。

7. 在当今的RISC机的指令系统中,全都是( 定字长 )指令格式。

8. 增强向量流水处理性能的方法主要有:多功能部件并行操作和采用( 链接 )技术。

9. 数组多路通道与设备之间的数据传送的基本单位是( 数据块 )。

10. 数据流系统结构是基于数据驱动和( 消息传送 )的计算模型。

11. 现代计算机系统是由(硬件/固件)和(软件)组成的十分复杂的系统。

12. 计算机系统应能支持软件可移植,实现可移植性的常用方法有3种,即(采用系列机),(仿真和模拟),统一高级语言。

13. 可以将当前大多数通用寄存器型指令集结构进一步细分为3种类型,即( RM结构)、( RR结构)和存储器-存储器型指令集结构。

14.MIPS指令DADDIU R14,R5,#6属于( I )类型的指令格式;MIPS指令SD R4,300(R5)属于( I )类型的指令格式。

15.描述流水线的工作,常采用时空图的方法。

在时空图中,横坐标表示(时间),纵坐标代表(空间或流水线各段)。

16.在MIPS指令实现的简单数据通路中,在WB周期中,有两大类指令执行操作:( Load )和( ALU )指令。

17.存储器的层次结构中,“Cache-主存”层次是为了弥补主存(速度)的不足,“主存-辅存”层次是为了弥补主存(容量)的不足。

18.Cache实现的映像规则有全相联映像、(直接)和(组相联)三种。

(完整版)软件体系结构复习题及答案

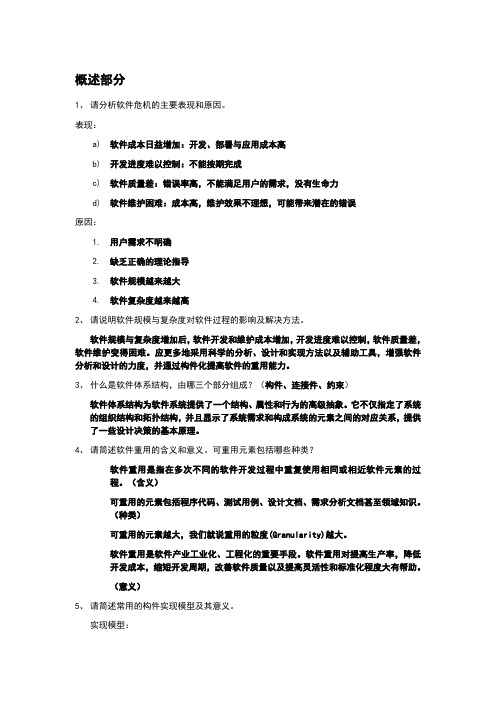

概述部分1、请分析软件危机的主要表现和原因。

表现:a)软件成本日益增加:开发、部署与应用成本高b)开发进度难以控制:不能按期完成c)软件质量差:错误率高,不能满足用户的需求,没有生命力d)软件维护困难:成本高,维护效果不理想,可能带来潜在的错误原因:1.用户需求不明确2.缺乏正确的理论指导3.软件规模越来越大4.软件复杂度越来越高2、请说明软件规模与复杂度对软件过程的影响及解决方法。

软件规模与复杂度增加后,软件开发和维护成本增加,开发进度难以控制,软件质量差,软件维护变得困难。

应更多地采用科学的分析、设计和实现方法以及辅助工具,增强软件分析和设计的力度,并通过构件化提高软件的重用能力。

3、什么是软件体系结构,由哪三个部分组成?(构件、连接件、约束)软件体系结构为软件系统提供了一个结构、属性和行为的高级抽象。

它不仅指定了系统的组织结构和拓扑结构,并且显示了系统需求和构成系统的元素之间的对应关系,提供了一些设计决策的基本原理。

4、请简述软件重用的含义和意义。

可重用元素包括哪些种类?软件重用是指在多次不同的软件开发过程中重复使用相同或相近软件元素的过程。

(含义)可重用的元素包括程序代码、测试用例、设计文档、需求分析文档甚至领域知识。

(种类)可重用的元素越大,我们就说重用的粒度(Granularity)越大。

软件重用是软件产业工业化、工程化的重要手段。

软件重用对提高生产率,降低开发成本,缩短开发周期,改善软件质量以及提高灵活性和标准化程度大有帮助。

(意义)5、请简述常用的构件实现模型及其意义。

实现模型:1.CORBA2.EJB / DCOM / COM+意义:这些模型通常都定义了构件的实现方式、接口定义、访问方法等。

符合这些标准的任何构件都有很高的重用能力。

描述部分6、请用图示法说明4+1模型的5种视图之间的关系及关注点和涉众用户。

数据视图风格部分7、什么是软件体系结构的风格?它在软件开发过程中具有何种意义?软件体系结构风格是指设计、组织和实现软件体系结构的各种惯用模式和习惯用法,是对一系列体系结构设计的抽象。

计算机体系结构复习计算题

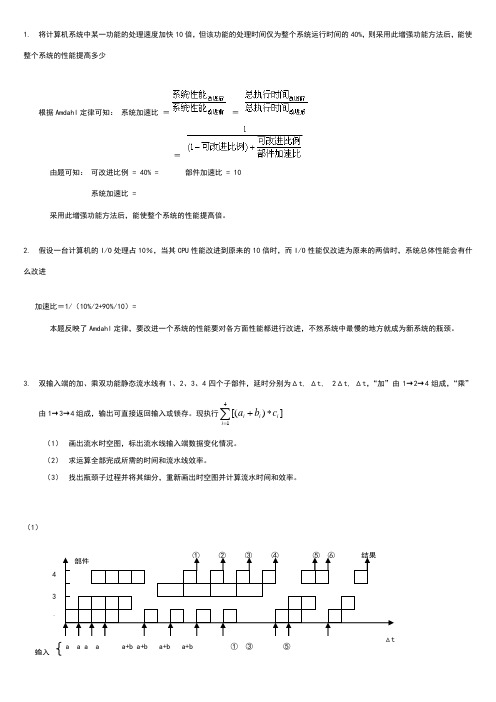

1. 将计算机系统中某一功能的处理速度加快10倍,但该功能的处理时间仅为整个系统运行时间的40%,则采用此增强功能方法后,能使整个系统的性能提高多少根据Amdahl定律可知:系统加速比===由题可知:可改进比例 = 40% = 部件加速比 = 10系统加速比 =采用此增强功能方法后,能使整个系统的性能提高倍。

2. 假设一台计算机的I/O处理占10%,当其CPU性能改进到原来的10倍时,而I/O性能仅改进为原来的两倍时,系统总体性能会有什么改进加速比=1/(10%/2+90%/10)=本题反映了Amdahl定律,要改进一个系统的性能要对各方面性能都进行改进,不然系统中最慢的地方就成为新系统的瓶颈。

3.双输入端的加、乘双功能静态流水线有1、2、3、4四个子部件,延时分别为Δt, Δt, 2Δt, Δt,“加”由1→2→4组成,“乘”由1→3→4组成,输出可直接返回输入或锁存。

现执行∑=* +41]) [(iiiicba(1)画出流水时空图,标出流水线输入端数据变化情况。

(2)求运算全部完成所需的时间和流水线效率。

(3)找出瓶颈子过程并将其细分,重新画出时空图并计算流水时间和效率。

(1)部件①②③④⑤⑥结果输入a a a a a+b a+b a+b a+b ①③⑤Δt 432(2)由上图可知,全部运算完的时间是23Δt 。

923723437=∆⨯∆=t t η(3)由上图可知,流水时间为20Δt 。

1003720537=∆⨯∆=t t η4. 有一条流水线如下所示。

50ns 50ns 100ns 200ns(1) 求连续输入5指令,该流水线的实际吞吐率和效率;(2) 该流水线的瓶颈在哪一段请采取两种不同的措施消除此“瓶颈”。

对于你所给出的新流水线,计算连续输入5条指令时,其实际吞吐率和效率。

5. 假设我们考虑条件分支指令的两种不同设计方法如下:(a)CPUA :通过比较指令设置条件码,然后测试条件码进行分支;(b)CPUB :在分支指令中包括比较过程。

计算机体系结构复习题(有答案)

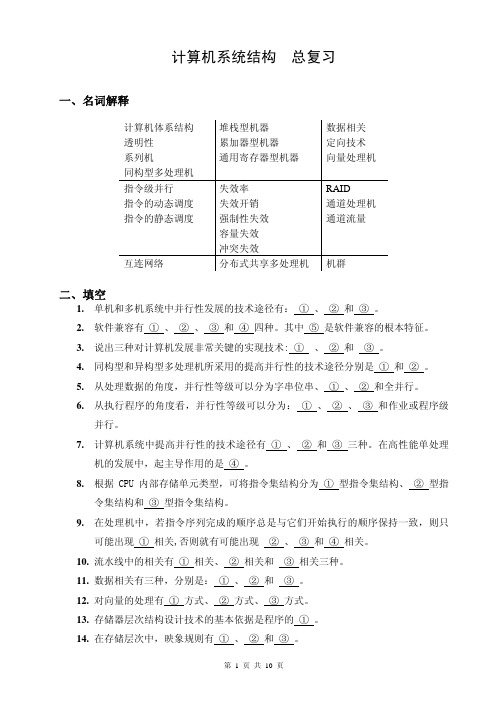

计算机系统结构 总复习

∑ 而且设置有足够地缓冲寄存器,若以最快的方式用该流水计算: AiBi i =1

① 画出时空图;(9 分) ② 计算实际的吞吐率、加速比和效率。(6 分) 15. 静态多功能流水线由 6 个功能段组成,如图 E_3 所示。其中,s1、s4、s5、s6 组

成乘法流水线,s1、s2、s3、s6 组成加法流水线,各个功能段时间均为△t,假设 该流水线的输出结果可以直接返回输入端,而且设置有足够地缓冲寄存器,若以 最快的方式用该流水计算:∏(Ai+Bi)(其中 i=1..4,∏为连乘符号) ① 画出时空图;(9 分) ② 计算实际的吞吐率、加速比和效率。(6 分) 16. (20 分)设指令流水线由取指令、分析指令和执行指令 3 个部件构成,每个部件 经过的时间为△t,连续流入 12 条指令。分别画出标量流水处理机以及 ILP 均为 4 的超标量处理机、超长指令字处理机、超流水处理机的时空图,并分别计算它们 相对于标量流水处理机的加速比。 17. (15 分)给定以下的假设,试计算直接映象 Cache 和两路组相联 Cache 的平均访 问时间以及 CPU 时间。 ① 理想 Cache(命中率为 100%)情况下的 CPI 为 2.0,时钟周期为 2ns,平均每条指 令访存 1.2 次。 ② 两种 Cache 容量均为 64KB,块大小都是 32 字节。 ③ 组相联 Cache 中的多路选择器使 CPU 的时钟周期增加了 10%。 ④ 这两种 Cache 的失效开销都是 80 ns。 ⑤ 命中时间为 1 个时钟周期。 ⑥ 64 KB 直接映象 Cache 的失效率为 1.4%,64 KB 两路组相联 Cache 的失效率为 1.0%。

① 画出处理过程的时空图。(9 分) ② 计算其吞吐率、加速比和效率。(6 分) 12. 有一条动态多功能流水线由 5 段组成(如图 E_2 所示),加法用 1、3、4、5 段,

第2章 计算机体系结构 习题与答案

第二章习题(P69-70)一、复习题1.简述冯∙诺依曼原理,冯∙诺依曼结构计算机包含哪几部分部件,其结构以何部件为中心?答:冯∙诺依曼理论的要点包括:指令像数据那样存放在存储器中,并可以像数据那样进行处理;指令格式使用二进制机器码表示;用程序存储控制方式工作。

这3条合称冯∙诺依曼原理OgtiojD。

冯∙诺依曼计算机由五大部分组成:运算器、控制器、存储器、输入设备、输出设备,整个结构一般以运算器为中心,也可以以控制器为中心。

(P51-P54)r1fI4bu。

2.简述计算机体系结构与组成、实现之间的关系。

答:计算机体系结构通常是指程序设计人员所见到的计算机系统的属性,是硬件子系统的结构概念及其功能特性。

计算机组成(computer organization)是依据计算机体系结构确定并且分配了硬件系统的概念结构和功能特性的基础上,设计计算机各部件的具体组成,它们之间的连接关系,实现机器指令级的各种功能和特性。

同时,为实现指令的控制功能,还需要设计相应的软件系统来构成一个完整的运算系统。

计算机实现,是计算机组成的物理实现,就是把完成逻辑设计的计算机组成方案转换为真实的计算机。

计算机体系结构、计算机组成和计算机实现是三个不同的概念,各自有不同的含义,但是又有着密切的联系,而且随着时间和技术的进步,这些含意也会有所改变。

在某些情况下,有时也无须特意地去区分计算机体系结构和计算机组成的不同含义。

(P47-P48)28BoSAn。

3.根据指令系统结构划分,现代计算机包含哪两种主要的体系结构?答:根据指令系统结构划分,现代计算机主要包含:CISC和RISC两种结构。

(P55)4.简述RISC技术的特点?答:从指令系统结构上看,RISC体系结构一般具有如下特点:(1)精简指令系统。

可以通过对过去大量的机器语言程序进行指令使用频度的统计,来选取其中常用的基本指令,并根据对操作系统、高级语言和应用环境等的支持增设一些最常用的指令;hJslBtf。

计算机体系结构复习题

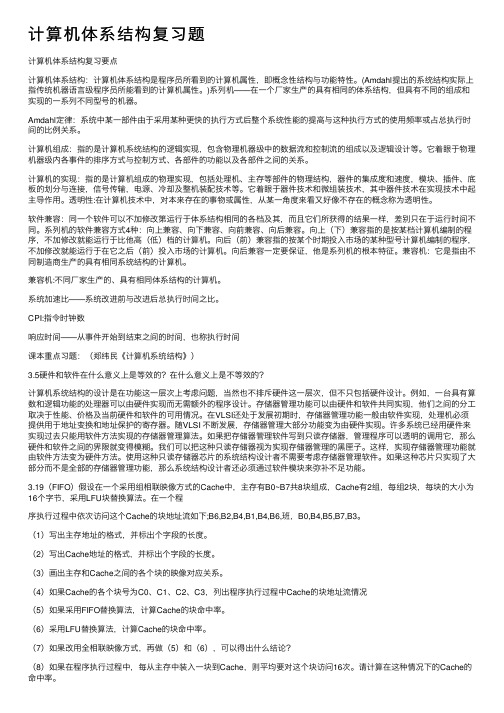

计算机体系结构复习题计算机体系结构复习要点计算机体系结构:计算机体系结构是程序员所看到的计算机属性,即概念性结构与功能特性。

(Amdahl提出的系统结构实际上指传统机器语⾔级程序员所能看到的计算机属性。

)系列机——在⼀个⼚家⽣产的具有相同的体系结构,但具有不同的组成和实现的⼀系列不同型号的机器。

Amdahl定律:系统中某⼀部件由于采⽤某种更快的执⾏⽅式后整个系统性能的提⾼与这种执⾏⽅式的使⽤频率或占总执⾏时间的⽐例关系。

计算机组成:指的是计算机系统结构的逻辑实现,包含物理机器级中的数据流和控制流的组成以及逻辑设计等。

它着眼于物理机器级内各事件的排序⽅式与控制⽅式、各部件的功能以及各部件之间的关系。

计算机的实现:指的是计算机组成的物理实现,包括处理机、主存等部件的物理结构,器件的集成度和速度,模块、插件、底板的划分与连接,信号传输,电源、冷却及整机装配技术等。

它着眼于器件技术和微组装技术,其中器件技术在实现技术中起主导作⽤。

透明性:在计算机技术中,对本来存在的事物或属性,从某⼀⾓度来看⼜好像不存在的概念称为透明性。

软件兼容:同⼀个软件可以不加修改第运⾏于体系结构相同的各档及其,⽽且它们所获得的结果⼀样,差别只在于运⾏时间不同。

系列机的软件兼容⽅式4种:向上兼容、向下兼容、向前兼容、向后兼容。

向上(下)兼容指的是按某档计算机编制的程序,不加修改就能运⾏于⽐他⾼(低)档的计算机。

向后(前)兼容指的按某个时期投⼊市场的某种型号计算机编制的程序,不加修改就能运⾏于在它之后(前)投⼊市场的计算机。

向后兼容⼀定要保证,他是系列机的根本特征。

兼容机:它是指由不同制造商⽣产的具有相同系统结构的计算机。

兼容机:不同⼚家⽣产的、具有相同体系结构的计算机。

系统加速⽐——系统改进前与改进后总执⾏时间之⽐。

CPI:指令时钟数响应时间——从事件开始到结束之间的时间,也称执⾏时间课本重点习题:(郑纬民《计算机系统结构》)3.5硬件和软件在什么意义上是等效的?在什么意义上是不等效的?计算机系统结构的设计是在功能这⼀层次上考虑问题,当然也不排斥硬件这⼀层次,但不只包括硬件设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

名词解释:1.计算机系统结构:传统机器程序员所看到的计算机属性,即概论性机构与功能特性。

2.CISC:复杂指令集计算机。

3.定向技术:流水线中将计算结果从其产生的地方直接送到真正需要它的地方,而不是从寄存器文件读出使用,他是一种解决数据相关,避免流水线暂停的技术。

4.指令级并行:并行执行两条或两条以上的指令。

5.多级存储层次:采用不同技术实现的存储器,处在离CPU不同距离的层次上,各存储器之间一般满足包容关系,即任何一层存储器中的内容都是其下一层(离CPU更远的一层)存储器中内容的子集。

6.系统加速比7.RISC8.动态流水线9.指令的动态调度10.全相联映象11.Amdahl定律12.寻址方式13.静态流水线14.前瞻执行15.替换算法16.紧密耦合系统17.通用寄存器型机器18.数据相关19.写后读冲突20.分支目标缓冲21.存储程序计算机22.松散耦合系统23.处理机间流水线24.分段开采25.全相联映象判断题26.(√)执行时间不是唯一的性能指标,但它是最普遍的性能表示形式。

27.()MIPS和MFLOPS是计算机性能衡量的两个可靠指标。

28.()程序的空间局部性指程序即将用到的信息很可能就是目前正在使用的信息。

29.(√)响应时间必须通过运行“真实程序”获得。

30.()基准程序能够完全预测一个程序在计算机上的运行性能。

31.()DLX流水线中,所有数据相关都可以通过定向技术解决。

32.()强制性失效和容量失效也受相联度的影响。

33.(√)伪相联cache具有快速命中与慢速命中两种命中时间。

34.(√)Cache命中时间往往会直接影响到处理器的时钟频率。

35.(√)Cache失效中必定包含强制性失效。

36.(×)根据Moore定律,DRAM的周期时间是每三年降低四倍。

37.(×)RISC结构的机器性能一定要比CISC结构的机器性能高。

38.(√)Amdahl定律揭示的性能递减规则说明如果仅仅对计算机中的一部分做性能改进,则改进越多,系统获得的效果越小。

39.(×)程序在向量计算机上运行,不会出现数据相关和结构相关。

40.(√)随着时间的推移,计算机系统的成本会逐渐降低。

41.(√)在DLX流水线中,可以在ID段检测所有数据相关。

42.(×)容量失效却随着容量的增加而增加。

43.(×)预取必须和正常访存操作并行才有意义。

44.(√)采用容量小、结构简单的Cache会减小cache的命中时间。

45.(×)Cache失效中必定包含容量失效。

46.(×)MIPS是测量计算机性能的一致性指标。

47.(×)平均每条指令的执行周期数(CPI)与程序无关。

48.(×)Amdahl定律中“可改进比例”指可改进部分在改进系统计算时间中所占的比例。

49.(×)通过操作系统的多进程技术可以完全回避I/O处理时间的问题。

因为当一个进程在等待I/O处理的时候,另外的一些进程可以在CPU上运行。

50.()MIPS和MFLOPS都可以用来准确地评价计算机系统的性能。

51.(√)编译器可以通过重新排列代码的顺序来消除相关引起的暂停。

52.(√)2:1的Cache经验规则说明容量为N 的直接映象Cache的失效率约等于大小为N/2 的两路组相联Cache的失效率。

53.(√)预取必须和正常指令的执行并行才有意义。

54.(×)Cache失效中必定包含冲突失效。

55.(√)写操作流水化会减小cache的命中时间。

56.(√)在计算机性能测量中,调和平均的含义是单位时间机器能够执行的程序数。

57.(√)CPU性能公式中指令条数(IC)与指令集格式和编译器有关。

58.(√)Amdahl定律中“部件加速比”指可改进部分改进以后性能的提高。

59.(×)在Cache中,只要增加块容量,一定可以减小失效率。

60.(√)现代CPU中已经没有堆栈型和累加器型的指令集结构。

61.(√)向量处理机用每秒取得多少浮点运算结果来衡量机器速度,以MFLOPS作为测量单位。

62.(√)一些降低失效率的方法会增加命中时间或失效开销。

63.(√)数据对存储位置的限制比指令的少,因此更便于编译器优化。

64.(√)组相联或直接映象Cache中才可能存在冲突失效。

65.(√)素数模法是避免存储体冲突的一种方法。

66.(×)根据Moore定律,DRAM的周期时间是每三年降低四倍。

67.(×)RISC结构的机器性能一定要比CISC结构的机器性能高。

68.(√)Amdahl定律揭示的性能递减规则说明如果仅仅对计算机中的一部分做性能改进,则改进越多,系统获得的效果越小。

69.(×)程序在向量计算机上运行,不会出现数据相关和结构相关。

70.(√)随着时间的推移,计算机系统的成本会逐渐降低。

71.(√)在DLX流水线中,可以在ID段检测所有数据相关。

72.(×)容量失效却随着容量的增加而增加。

73.(×)预取必须和正常访存操作并行才有意义。

74.(√)采用容量小、结构简单的Cache会减小cache的命中时间。

75.(×)Cache失效中必定包含容量失效。

简答题76.计算机系统结构的Flynn分类法是按什么来分类的?共分为哪几类?77.区别不同指令集结构的主要因素是什么?根据这个主要因素可将指令集结构分为哪3类?78.简述流水线技术的特点。

79.地址映象方法有哪几种?它们各有什么优缺点?80.同步总线和异步总线各有什么优缺点?81.计算机系统设计中经常使用的4个定量原理是什么?并说出它们的含义。

82.指令集应满足哪几个基本要求?83.简述先行控制的基本思想。

84.简述减小Cache失效开销的几种方法。

85.简述通道完成一次数据传输的主要过程。

86.试说明计算机系统结构、计算机组成与计算机实现之间的相互关系。

87.简述CISC指令集结构功能设计的主要目标。

从当前的计算机技术观点来看,CISC指令集结构的计算机有什么缺点?88.减少流水线分支延迟的静态方法有哪些?89.简述Tomasulo算法的基本思想。

90.通过编译器对程序优化来改进Cache性能的方法有哪几种?简述其基本思想。

分析说明题91.指令的执行可采用顺序执行、重叠执行和流水线三种方式,是分析说明它们的主要区别及优缺点。

92.分别从执行程序的角度和处理数据的角度来说明计算机系统中并行性等级从低到高可分为哪几级?93.试说明存储层次设计要解决的四个问题。

计算题94.某台主频为400MHz的计算机执行标准测试程序,程序中指令类型、执95.计算机系统中有三个部件可以改进,这三个部件的部件加速比为:部件加速比1=30;部件加速比2=20;部件加速比3=10(1)如果部件1和部件2的可改进比例均为30%,那么当部件3的可改进比例为多少时,系统加速比才可以达到10?(2)如果三个部件的可改进比例分别为30%、30%和20%,三个部件同时改进,那么系统中不可加速部分的执行时间在总执行时间中占的比例是多少?96.动态多功能流水线由6个功能段组成,如下图:其中,S1、S4、S5、S6组成乘法流水线,S1、S2、S3、S6组成加法流水线,各个功能段时间均为50ns,假设该流水线的输出结果可以直接返回输入端,而且设置有足够的缓冲寄存器,若以最快的方式用该流水计算:(1)画出时空图;(2)计算实际的吞吐率、加速比和效率。

97.假设某应用程序中有4类操作,通过改进,各操作获得不同的性能(1)改进后,各类操作的加速比分别是多少?(2)各类操作单独改进后,程序获得的加速比分别是多少?(3)4类操作均改进后,整个程序的加速比是多少?出师表两汉:诸葛亮先帝创业未半而中道崩殂,今天下三分,益州疲弊,此诚危急存亡之秋也。

然侍卫之臣不懈于内,忠志之士忘身于外者,盖追先帝之殊遇,欲报之于陛下也。

诚宜开张圣听,以光先帝遗德,恢弘志士之气,不宜妄自菲薄,引喻失义,以塞忠谏之路也。

宫中府中,俱为一体;陟罚臧否,不宜异同。

若有作奸犯科及为忠善者,宜付有司论其刑赏,以昭陛下平明之理;不宜偏私,使内外异法也。

侍中、侍郎郭攸之、费祎、董允等,此皆良实,志虑忠纯,是以先帝简拔以遗陛下:愚以为宫中之事,事无大小,悉以咨之,然后施行,必能裨补阙漏,有所广益。

将军向宠,性行淑均,晓畅军事,试用于昔日,先帝称之曰“能”,是以众议举宠为督:愚以为营中之事,悉以咨之,必能使行阵和睦,优劣得所。

亲贤臣,远小人,此先汉所以兴隆也;亲小人,远贤臣,此后汉所以倾颓也。

先帝在时,每与臣论此事,未尝不叹息痛恨于桓、灵也。

侍中、尚书、长史、参军,此悉贞良死节之臣,愿陛下亲之、信之,则汉室之隆,可计日而待也。

臣本布衣,躬耕于南阳,苟全性命于乱世,不求闻达于诸侯。

先帝不以臣卑鄙,猥自枉屈,三顾臣于草庐之中,咨臣以当世之事,由是感激,遂许先帝以驱驰。

后值倾覆,受任于败军之际,奉命于危难之间,尔来二十有一年矣。

先帝知臣谨慎,故临崩寄臣以大事也。

受命以来,夙夜忧叹,恐托付不效,以伤先帝之明;故五月渡泸,深入不毛。

今南方已定,兵甲已足,当奖率三军,北定中原,庶竭驽钝,攘除奸凶,兴复汉室,还于旧都。

此臣所以报先帝而忠陛下之职分也。

至于斟酌损益,进尽忠言,则攸之、祎、允之任也。

愿陛下托臣以讨贼兴复之效,不效,则治臣之罪,以告先帝之灵。

若无兴德之言,则责攸之、祎、允等之慢,以彰其咎;陛下亦宜自谋,以咨诹善道,察纳雅言,深追先帝遗诏。

臣不胜受恩感激。

今当远离,临表涕零,不知所言。