考研计算机组成原理笔记

《计算机组成原理》唐朔飞第二版_笔记

《计算机组成原理》唐朔飞第⼆版_笔记第1章概论1,计算机系统的软硬件概念1)硬件:计算机的实体部分,它由看得见摸得着的各种电⼦元器件,各类光、电、机设备的实物组成,如主机、外部设备等。

2)软件:由⼈们事先编制的具有各类特殊功能的程序组成,分为系统软件和应⽤软件。

①系统软件⼜称为系统程序,主要⽤来管理整个计算机系统,监视服务,使系统资源得到合理的调度,⾼效运⾏。

它包括:标准程序库、语⾔处理程序(编译程序)、操作系统、、服务程序(如诊断、调试、连接程序)、数据库管理系统、⽹络软件等。

②应⽤软件⼜称应⽤程序,它是⽤户根据任务需要所编制的各种程序,如科学计算程序、数据处理程序、过程控制程序、实物管理程序。

2、计算机系统的层次结构:1)硬联逻辑级:第零级是硬联逻辑级,这是计算机的内核,由门,触发器等逻辑电路组成。

2)微程序级:第⼀级是微程序级。

这级的机器语⾔是微指令集,程序员⽤微指令编写的微程序,⼀般是直接由硬件执⾏的。

3)传统机器级:第⼆级是传统机器级,这级的机器语⾔是该机的指令集,程序员⽤机器指令编写的程序可以由微程序进⾏解释。

操作4)系统级:第三级是操作系统级,从操作系统的基本功能来看,⼀⽅⾯它要直接管理传统机器中的软硬件资源,另⼀⽅⾯它⼜是传统机器的延伸。

5)汇编语⾔级:第四级是汇编语⾔级,这级的机器语⾔是汇编语⾔,完成汇编语⾔翻译的程序叫做汇编程序。

6)⾼级语⾔级:第五级是⾼级语⾔级,这级的机器语⾔就是各种⾼级语⾔,通常⽤编译程序来完成⾼级语⾔翻译的⼯作。

7)应⽤语⾔级:第六级是应⽤语⾔级,这⼀级是为了使计算机满⾜某种⽤途⽽专门设计的,因此这⼀级语⾔就是各种⾯向问题的应⽤语⾔。

把计算机系统按功能分为多级层次结构,就是有利于正确理解计算机系统的⼯作过程,明确软件,硬件在计算机系统中的地位和作⽤。

3、计算机组成和计算机体系结构1)计算机体系结构:是指那些能够被程序员所见到的计算机系统的属性,即概念性的结构与功能特性。

408考试笔记

408考试笔记一、计算机组成原理1. 冯诺依曼体系结构可不能忘呀。

计算机的五大部件:运算器、控制器、存储器、输入设备、输出设备。

就像一个小团队一样,各自有着明确的分工呢。

运算器负责计算数据,控制器就像个小指挥家,指挥着整个计算机系统的运行。

存储器用来存储数据和程序,输入设备把外部信息送进计算机,输出设备把计算机处理的结果输出出去。

2. 数据的表示和运算也很重要哦。

原码、反码、补码的概念得清楚。

原码就是符号位加上真值的绝对值,反码是原码除符号位外按位取反,补码是反码加1。

在做加减法运算的时候,补码可是很方便的呢。

3. 存储系统也有很多要记的。

主存的组成结构,什么存储单元、存储字、存储字长之类的。

还有高速缓冲存储器(Cache),它就像一个小助手,能够提高CPU访问数据的速度,原理是基于程序的局部性原理哦。

二、操作系统1. 操作系统的功能可多啦。

处理机管理,进程和线程是重点。

进程是资源分配的基本单位,线程是独立调度的基本单位。

进程有它的生命周期,创建、就绪、运行、阻塞、终止这些状态得牢记。

2. 内存管理也不简单。

分区存储管理、分页存储管理、分段存储管理都各有特点。

分页存储管理是把主存分成大小相等的块,程序也分成大小相等的页,通过页表来实现地址映射。

分段存储管理则是按照程序的逻辑段来划分内存,有段表来进行地址转换。

3. 文件系统方面,文件的逻辑结构和物理结构要分清。

逻辑结构有有结构文件(如顺序文件、索引文件等)和无结构文件(流式文件)。

物理结构有连续分配、链接分配(包括隐式链接和显式链接)、索引分配等。

三、计算机网络1. 网络体系结构的分层可不能搞混哦。

OSI七层模型(物理层、数据链路层、网络层、传输层、会话层、表示层、应用层)和TCP/IP四层模型(网络接口层、网络层、传输层、应用层)。

每一层都有自己的功能和协议。

2. IP地址相关知识很关键。

IPv4地址是32位的,有A、B、C、D、E五类地址。

子网掩码的作用是用来划分网络号和主机号的。

终于有人把'计算机组成原理学习笔记'整理出来了

终于有人把'计算机组成原理学习笔记'整理出来了1. 计算机组成原理概论计算机:数字电子计算机组成:计算机硬件系统的逻辑实现原理:不以具体机型为依托的,基本实现原理。

计算机组成原理:掌握如何实现的具体细节。

1.1 计算机系统简介计算机系统由两大部分组成:硬件和软件。

软件又包括系统软件和应用软件。

系统软件可以管理整个计算机系统:•语言处理程序(将高级语言转换为机器可以懂得指令)•操作系统•服务性程序(比如数学库、MPI服务程序进行并行之间的通信)•数据库管理系统•网络软件应用软件是按照任务需要编制成的程序。

可以简单将软件看作一个层次结构,硬件为软件提供接口,系统软件又为应用软件形成接口,来完成不同的程序。

对于计算机的物理结构层次,我们这门课主要研究逻辑层和微电路层的具体实现方式。

计算机系统的指令层次如下图所示操作系统可以管理软硬件的资源。

计算机系统结构定义了系统软硬件的交界面,定义了哪些功能由软件实现,哪些功能由硬件实现,定义为==程序员所见到的计算机系统的属性概念性的结构与功能特性==。

(指令系统,数据类型,寻址技术,I/O机理),即程序员需要理解的东西。

计算机组成:实现计算机体系结构所体现的属性,即具体指令的实现。

1.2 计算机的基本组成1.2.1 冯诺依曼结构上图实线表示数据流动,虚线表示控制反馈。

•计算机结构由五大部件组成:存储器、运算器、控制器、输入设备、输出设备。

•以运算器为中心,==程序存储在存储器中==。

•指令和数据以同等地位保存在存储器中,可以按照地址寻找。

•指令和数据由二进制表示,指令由操作码和地址码组成,操作码指明指令要干什么,地址码指明操作数的地址。

冯诺依曼结构以运算器为中心,容易形成瓶颈。

我们可以使用存储器作为中心来进行优化,但是还不够。

1.2.2 现代计算机硬件框图指令和数据都是保存在存储器中的。

1.2.3 存储器的基本组成MAR是存储器地址寄存器,保存了存储单元的地址和编号,长度反映存储单元的个数。

计算机组成原理笔记

计算机组成原理笔记

1. 计算机组成原理是研究计算机硬件和软件组成及其相互关系的学科领域。

2. 计算机由中央处理器(CPU)、存储器和输入输出设备组成,其中CPU是计算机的控制中心。

3. CPU由控制单元和算术逻辑单元组成,控制单元负责指令

的解析和执行,算术逻辑单元负责数据的运算。

4. 存储器用于存储计算机运行时所需的数据和指令,其中包括主存储器和辅助存储器。

5. 输入输出设备用于与外部世界进行信息交互,例如键盘、鼠标、显示器和打印机等。

6. 计算机执行程序时,先从辅助存储器中将程序加载到主存储器,然后由CPU依次执行指令。

7. 指令由操作码和操作数组成,操作码表示指令的类型,操作数表示指令所操作的数据。

8. 指令在执行过程中通过执行周期来完成,包括取指令、分析指令、执行指令和写回数据等阶段。

9. 计算机的性能可以通过时钟频率、指令执行速度和吞吐量等指标进行衡量。

10. 计算机的内部结构可以采用冯·诺依曼结构或哈佛结构,冯·诺依曼结构中指令和数据存储在同一存储器中,而哈佛结

构中指令和数据存储在不同的存储器中。

11. 计算机的指令集架构可以分为精简指令集(RISC)和复杂

指令集(CISC)两种类型。

12. 硬件和软件之间通过接口进行通信,例如操作系统作为硬

件和应用软件之间的接口。

13. 并行计算可以提高计算机的性能,包括并行指令和并行处理等技术。

14. 计算机组成原理还涉及到虚拟内存、缓存和流水线等重要概念和技术。

15. 计算机组成原理的研究对于理解计算机的工作原理和优化计算机性能具有重要意义。

计算机组成原理(考研期末)知识点总结

计算机组成原理(考研期末)知识点总结(一)存储系统1.存储器的基本概念●分类●作用(层次):CACHE 主存辅存●存储介质:磁半导体光●存取方式●随机存取:RAM ROM●串行访问●顺序存取:磁带●直接存取:磁盘●信息可保存性--易失性破坏性读出非●性能指标●存储容量字●单位成本每位成本●存储速度(数据传输率主存带宽)●层次化结构●Cache-主存层次:硬件实现,解决速度不匹配问题●主存-辅存层次:硬件+操作系统实现,解决容量问题,逐渐形成虚拟存储系统2.半导体存储器●存储器芯片的基本结构●译码驱动电路(译码器:扩充容量)●存储矩阵●读写电路●地址线,数据线,片选线,读写控制线●半导体存储器RAM(易失性存储器)●SRAM:触发器存储信息,速度快成本高集成度低,用于高速缓存●DRAM:电容存储信息,需要刷新,速度慢成本低,集成度高,用于主存SDRAM●DRAM的刷新:集中刷新,分散刷新,●异步刷新●不需要CPU控制●行为单位,仅需要行地址●存储器中所有芯片同时刷新●RAM的读写周期●ROM(非易失性存储器)●特点:结构简单,位密度比RAM高,非易失性,可靠性高●类型:MROM,PROM,EPPROM,FLASH MEMORY,SSD3.存储器与CPU的协同工作(提高存储系统的工作速度)●主存与CPU的连接●字扩展●位扩展●线选法●译码片选法●译码器的使用●分析地址空间●字位同时扩展●选择存储器芯片●与CPU进行连接●双口RAM和多模块存储器●多模块存储器●单体多字●多体并行●低位交叉编址●高位交叉编址●双端口RAM●高速缓冲存储器●CACHE局部性原理和性能分析●局部性原理●空间局部性●时间局部性●性能分析●命中率和失效率●CACHE----主存体系的平均访问时间●CACHE工作原理●地址映射方式●全相联●直接相联●组相联●替换算法●RAND随机●FIFO先入先出●LRU最近最少使用●LFU最不经常使用●写策略●命中●全写法●写回法●不命中●写分配法●非写分配法●虚拟存储器(主存和辅存共同构成)(增加存储系统的容量)●基本概念:虚地址(逻辑地址)映射到实地址(物理地址)●解决问题:进程并发问题和内存不够用问题●类型●页式●段式●段页式●虚实地址转换(提高速度)●快表TLB●慢表Page(二)指令系统1.指令格式●操作码和地址码组成一条指令●操作码●定长操作码和扩展操作码●操作码类型2.指令寻址方式●指令寻址(通过PC)●顺序寻址●跳跃寻址●数据寻址●隐含寻址●立即寻址:给寄存器赋初值●直接寻址●间接寻址:扩大寻址范围,便于编制程序●寄存器寻址:指令执行速度更快●寄存器间接寻址●偏移寻址(各寄存器内容+形式地址):基址寻址,变址寻址(处理数组,编制循环程序),相对寻址●堆栈寻址3.CISC和RISC●CISC复杂指令系统计算机(用微程序控制器)●更多更复杂,一般为微程序控制,用于计算机系统●RISC精简指令系统计算机(用硬布线控制器)●指令数目少,字长固定,寻址方式少,寄存器数量多,一般为组合逻辑控制,用于手机(三)中央处理器1.CPU的功能和基本结构●CPU的功能:指令控制,操作控制,时间控制,数据加工,中断处理●运算器●功能:对数据进行加工●基本结构:●算术逻辑单元ALU●暂存寄存器●通用寄存器组●累加寄存器ACC●程序状态字寄存器PSW●移位器,计数器●控制器●功能:取指令,分析指令,执行指令●控制器的基本结构●程序计数器PC●指令寄存器IR●指令译码器,时序系统,微操作信号发生器●存储器地址寄存器MAR●存储器数据寄存器MDR●数据通路的基本结构●专用通路●内部总线2.指令执行过程●指令周期●构成:机器周期、CPU周期——CPU时钟周期、节拍●类型:取指周期,间址周期,执行周期,中短周期●标志触发器FE,IND,EX,INT:区别工作周期●数据流●取指周期:根据PC取出指令代码存放在IR●间址周期:根据IR中指令地址码取出操作数的有效地址●执行周期:根据指令字的操作码和操作数进行相应操作●中断周期:保存断点,送中断向量,处理中断请求●执行方案●单指令周期:串行,指令相同执行时间●多指令周期:串行,指令不同执行时间●流水线方案:隔一段时间启动一条指令,多条指令处于不同阶段,同事并行处理3.数据通路的功能和基本结构(连接路径)●CPU内部总线●单总线●多总线●专用数据通路:多路选择器和三态门●了解各阶段微操作序列和控制信号4.控制器的功能和工作原理●控制器的结构和功能●计算机硬件系统连接关系●控制器的功能:取指令,分析指令,执行指令●控制器的输入和输出●硬布线控制器●硬布线控制单元图:组合逻辑电路+触发器●设计步骤(了解)●分析每个阶段的微操作序列●选择CPU的控制方式●安排微操作序列●电路设计●微程序控制器●基本结构●微地址形成部件●微地址寄存器CMAR●控制存储器CM●微指令寄存器CMDR●微指令的格式●水平型:并行操作●字段直接编码方式●直接编码方式●字段间接编码方式●垂直型:类似机器指令●微指令的地址形成方式●下地址字段指出:断定方式●根据机器指令的操作码形成●基本概念●微命令和微操作●微指令和微周期●主存储器和控制存储器●程序和微程序●寄存器:MAR和CMAR,IR和CMDR●硬布线和微程序的比较(微操作控制信号的实现形式)5.指令流水线●指令流水线的概念●指令执行过程划分为不同阶段,占用不同的资源,就能使多条指令同时执行●表示方法●指令流程图:分析影响流水线的因素●时空图:分析性能●性能指标●吞吐率TP●加速比S●效率E●影响流水线的因素●结构相关(资源冲突)●数据相关(数据冲突)●控制相关(控制冲突)●流水线的分类●按使用级别:部件功能级,处理机级,处理机间●按完成功能:单功能,多功能●按连接方式:动态,静态●按有无反馈信号:线性,非线性●多发技术●超标量流水线技术●超流水线技术●超长指令字技术(四)总线1.总线概念和分类●定义:一组能为多个部件分时共享的公共信息传送线路●分类●按数据传输格式●串行,并行●按功能●片内总线●系统总线●数据总线,地址总线,控制总线●通信总线●按时序控制方式●同步,异步●总线结构●单总线结构——系统总线●双总线结构(通道)●主存总线●IO总线●三总线结构●主存总线●IO总线●DMA总线2.总线的性能指标●总线传输周期(总线周期)●总线带宽●总线宽度(位宽)●总线复用:一种信号线传输不同信息3.总线仲裁●集中仲裁方式●链式查询方式●计数器定时查询方式●独立请求方式●分布仲裁方式4.总线操作和定时●总线传输的四个阶段●申请分配阶段●传输请求●总线仲裁●寻址阶段●传输阶段●结束阶段●定时●同步定时方式(同步通信)●异步定时方式(异步通信)●不互锁●半互锁●全互锁●半同步通信●分离式通信5.总线标准(五)IO系统1.IO系统基本概念●演变过程●早期:分散连接,CUP与IO串行,程序查询方式●接口模块和DMA阶段:总线连接,cpu与io并行,中断方式及DMA方式●具有IO通信结构的阶段●具有IO处理机的阶段●IO系统的基本组成●IO软件——IO指令和通道指令●IO硬件——外设,设备控制器和接口,IO总线等●IO方式简介●程序查询方式:IO与CPU串行,CPU有“踏步等待”现象(由程序控制)●程序中断方式:IO准备数据时CPU继续工作,在指令执行结束时响应中断(由程序控制)●DMA方式:主存与IO交换信息时由DMA控制器控制,在存取周期结束时响应DMA请求(由硬件控制)●通道方式:通过IO指令启动通道,通道程序放在主存中(由硬件控制)2.外部设备●输入设备——键盘,鼠标●输出设备●显示器●分类●阴极射线管(CRT)●液晶(LCD)●发光二极管(LED)●参数●屏幕大小,分辨率,灰度级,刷新频率●显示存储器(VRAM)●容量=分辨率*灰度级位数●带宽=容量*帧频●打印机●外存储器●磁盘存储器●组成●存储区域:磁头,柱面,扇区●硬盘存储器:磁盘驱动器,磁盘控制器,盘片●工作过程:寻址,读盘,写盘对应的控制字,串行读写●性能指标●容量●记录密度●平均存取时间●数据传输率●磁盘阵列RAID——利用磁盘廉价的特点提高存储性能,可靠性和安全性●光盘存储器●固态硬盘SSD——采用FLASH Memory记录数据3.IO接口●主要功能●设备选址功能:地址译码和设备选择●传送命令●传送数据:实现数据缓冲和格式转换●反应IO设备的工作状态●基本结构●设备选择电路,命令寄存器和命令译码器,数据缓冲寄存器DBR,设备状态标记,控制逻辑电路●内部接口和外部接口●编址●统一编址——与存储器共用地址,用访存命令访问IO设备●独立编址:单独使用一套地址,有专门的IO指令●分类●数据传送方式:并行接口,串行接口●主机访问IO设备的控制方式●程序查询接口●中断接口●DMA接口●功能选择的灵活性●可编程接口●不可编程接口4.IO方式●程序查询方式:CPU与IO串行工作,鼠标,键盘●程序中断方式●中断系统●中断的基本概念●工作流程●中断请求●分类●中断请求标记触发器INTR●中断响应●中断响应的条件●中断判优●软件:查询程序●硬件:排队器●优先级的设置●中断处理●中断隐指令●关中断●保存断点PC●引出中断服务程序●中断服务程序●单重中断与多重中断●中断服务程序的具体步骤●中断屏蔽技术●屏蔽字●程序执行轨迹●程序中断方式●工作流程●CPU占用情况●中断响应(隐指令)●中断服务程序●DMA方式●DMA控制器●组成●主存地址计数器:存放要交换数据的主存地址●传送长度计数器:记录传送数据的长度●数据缓冲寄存器:暂存每次传送的数据●DMA请求触发器:设备准备好数据后将其置位●控制/状态逻辑:由控制和时序电路及状态标志组成●中断机构:数据传送完毕后触发中断机构,提出中断请求●主要功能●传送前:接受外设的DMA请求,向CPU发出总线请求,接管总线控制权●传送时:管理总线,控制数据传送,确定主存单元地址及长度,能自动修改对应参数●传送后: 向CPU报告DMA操作的结束●传送过程●预处理:CPU完成寄存器初值设置等准备工作●数据传送:CPU继续执行主程序,DMA控制器完成数据传送●后处理:CPU执行中断服务程序做DMA结束处理。

计算机组成原理知识点笔记

计算机组成原理知识点笔记第一课时1、指令分为操作码和地址码,操作码指明了操作类型,地址码指明了对哪两个数进行操作。

2、CPU的时钟频率也即是CPU的主频。

3计算机系统结构:概念性结构和功能特性。

是指硬件子系统的概念性结构和功能特性。

由指令系统所规定的所有属性,所以也称指令集体系结构。

主要研究计算机系统软件和硬件的功能分配,以及如何最佳地实现分配给硬件的功能。

例如:指令系统中是否包括乘法指令?4、计算机组织:也称计算机组成:计算机主要部件的类型、数量、组成方式、控制方式和信息流动方式以及相互连接而构成的而系统。

主要研究数据和指令的组织,数据的存取、传送和加工处理。

数据流和指令流的控制方式基本运算的算法例如:如何实现乘法指令?5计算机实现:计算机功能的物理实现。

6、加法指令执行速度因为加法指令能反映乘除等运算,而其他指令的执行时间也大体与加法指令相当。

7、CPI,执行一条指令所需时钟周期数,是主频的倒数。

8、等效指令速度法9存储器不仅能存放数据,而且也能存放指令,两者在形式上没有区别,但计算机应能区分数据还是指令。

10 有时我们说某个特定的功能是由硬件实现的,但并不是说不要编写程序,如乘法功能可由乘法器这个硬件实现,但要启动这个硬件(乘法器)工作,必须先执行程序中的乘法指令。

11 指令译码器是译指令的操作码。

而是在读出之前就知道将要读的信息是数据还是指令了12 在计算机领域中,站在某一类用户的角度,如果感觉不到某个事物或属性的存在,即“看”不到某个事物或属性,则称为“对xxxx用户而言,某个事物或属性是透明的”。

13程序控制器:(PC)是执行指令的机器。

14 机器字长定义为CPU中在同一时间内一次能够处理的二进制数的位数,实际上就是CPU中数据通路的位数15 浮点运算器的数据通路要宽得多。

16所以一般把定点运算器的数据通路宽度定为机器字长。

因为机器字长与内存单元的地址位数有关,而地址计算是在定点运算器中进行的。

江科大-计算机组成原理考研复习笔记

考查目标计算机学科专业基础综合考试涵盖数据机构、计算机组成原理、操作系统和计算机网络等学科专业基础课程。

要求考生比较系统地掌握上述专业基础课程的概念、基本原理和方法,能够运用所学的基本原理和基本方法分析、判断和解决有关理论问题和实际问题。

考试形式和试卷结构一、 试卷满分及考试时间本试卷满分为150分,考试时间为180分钟二、 答题方式答题方式为闭卷、笔试三、 试卷内容结构数据结构 45分计算机组成原理 45分操作系统 35分计算机网络 25分四、 试卷题型结构单项选择题 80分(40小题,每小题2分)综合应用题 70分计算机组成原理【考查目标】1. 理解单处理器计算机系统中各部件的内部工作原理、组成结构以及相互连接方式,具有完整的计算机系统的整机概念。

2. 理解计算机系统层次化结构概念,熟悉硬件与软件之间的界面,掌握指令集体系结构的基本知识和基本实现方法。

3. 能够运用计算机组成的基本原理和基本方法,对有关计算机硬件系统中的理论和实际问题进行计算、分析,并能对一些基本部件进行简单设计。

一、 计算机系统概述(一) 计算机发展历程第一台电子计算机ENIAC(Electronic Numerical Integrator And Computer)诞生于1946年的美国宾夕法尼亚大学。

ENIAC用了18000电子管、1500继电器、重30吨、占地170m3、耗电140kw、每秒计算5000次加法。

冯•诺依曼(VanNeumann)首次提出存储程序的概念,将数据和程序一起放在存储器中,使得编程更加方便。

50多年来,虽然对冯•诺依曼机进行了很多改革,但结构变化不大,仍然称为冯•诺依曼机。

一般把计算机的发展分为四个阶段:第一代(1946-50‘s后期):电子管计算机时代;第二代(50‘s中期-60’s后期):晶体管计算机时代;第三代(60‘s中期-70’s前期):集成电路计算机时代;第四代(70‘s初-):大规模集成电路计算机时代。

考研:计算机组成原理考点总结

考研:计算机组成原理考点总结●1 计算机系统和概述●历程●硬件●电子管●晶体管●集成电路●大规模集成电路●摩尔定律●软件●系列机体系结构相同●兼容机器语言兼容●可移植性●固件●结构●硬件●冯诺依曼计算机●同时存储数据和程序●五大部件●输入●输出●存储器●寄存器●通用●专用●mar●mdr●pc●ir●psw●cache●主存●辅存●运算器●算术逻辑单元●寄存器●acc●mq乘商●x操作数●ix变址寄存器●br基址寄存器●控制器●ir●pc●cu●信息存储相同解释不同●指令组成●软件●软件功能●系统软件●os●dbms●应用软件●语言●机器语言(可以被硬件直接执行)●汇编语言●汇编器●高级语言●编译器●解释器●软硬件逻辑功能一致性●层次结构●高级语言虚拟机●汇编语言虚拟机●操作系统虚拟机●机器语言●微程序机器●性能指标●名词●字长●数据通路带宽●空间●时间●吞吐量●处理请求数量ps●响应时间●总时间●主频和CPU时钟周期 T=1/f●CPI●执行一条指令所需的时钟周期数●CPU执行时间●时间=(指令条数xCPI)/主频●MIPS=指令条数/(执行时间x10⁶)=主频/CPI●MFLOPS每秒执行多少百万次浮点运算●基准程序●2 数据的表示和运算●数制与编码●进位及转换●计算机中一切数据都用二进制表示●表示简单●逻辑真假对应●规则简单●数制●二进制●十进制●八进制●十六进制●数制转换●B2O3位转●B2H4位转●X2D权相加●D2X整数:除基取余法小数:乘积取整法●值的编码●各种码制及其关系●原码:用机器数的最高位表示数的符号,其余各位表示数的绝对值。

(计算麻烦)●反码:正数正常表示,负数各位取反●补码:反码末位加1●优势●0的补码唯一●多表示一个数●运算简单●模4补码(双符号位小数)●与真值转换●大于等于0,相等●小于0,逐位取反,末位加一●移码:真值加偏置值●Bias的值●Bias = 2^{k-1}-1,IN IEEE 754●Bias = 2^{k-1}时,移码等于补码的符号位取反●全0最小,全1最大●BCD码:2->10的快速转换●8421●余3●2421●码制的关系●补码、移码在数轴不对称●原码,反码在数轴对称(有2个0)●负数的反码补码越靠近0真值越大●值的表示●整数:定点数●U整数:原码●S整数:补码●小数:IEEE 754 浮点数●阶码:移码●尾数:原码●不考虑字长整数可以精确表示,浮点数不可以精确表示●数的运算●加减运算●运算部件●一位全加器●输出●进位:C_{out} = A_iB_i+ (A_i\oplus B_i)C_i●值:S_n=C_{i}\oplus A_i\oplus B_i(奇数校验)●图●串行进位加法器●把n个全加器相连可得到n位加法器●逻辑图●信号逐级形成,速度慢●并行进位加法器●原理:每个C_i形成条件在最初均已经获得->先行进位●空间换时间●一般采用四位并行●并行加法器的串联与并联●标志位●ZF=\neg(S_{n-1}+...+S_0)0标志,判断结果是否为0●OF=C_{out}\oplus C_{n-1}溢出标志,判断有符号数的结果是否溢出●CF=C_{out}\oplus C_{in}进位标志,判断无符号数是否溢出●SF=S_{n-1}符号标志●补码的加减运算●公式●[A+B]_补=([A]_补+[B]_补)mod\space 2^{n}●[A-B]_补=([A]_补+[-B]_补)mod\space 2^{n}●规则●符号位参与运算●高位截断●电路●减法时作用于取反器与加法器的C0达到求B的补码的效果(减法->加法)●溢出判别●正数相加小于0,负数相加大于0●单符号位:(A_sB_s)\oplus S_s●双符号位:S_{s1}\oplus S_{s2}●标志位:OF●原码的加减运算●加法直接相加●减法取反相加●高位截断●溢出看CF●乘法运算●原码一位乘法●过程●绝对值参与运算,符号位结果为A_{s}\oplus B_{s}●乘数MQ,ACC置空,Cn置为字长值●为1累加,为0不操作●逻辑右移●LOOP●电路●C寄存进位(采用带进位的右移)●Cn存储字长为处置●MQ最低位送至控制器,判断是否加●补码一位乘法(Booth算法)●原理●[x\times y]_补=[x]_补\times (-b_{w-1}\times 2^{w-1}+\sum\limits^{n-2}\limits_{i=0}b_i\times 2^i)●=[x]补\times[2^{n-1}\times(b_{n-2}-b_{n-1})+2^{n-2}\times(b_{n-3}-b_{n-2})+...+2^{0}\times(b_{-1}-b_{0})+b_{-1}]●=[x]补\times[\sum\limits^{n-1}\limits_{i=0}2^{i}\times(b_{i-1}-b_{i})+b_{-1}]●=[x]补\times\sum\limits^{n-1}\limits_{i=0}2^{i}\times(b_{i-1}-b_{i})\space\space (let\space b_{-1}=0)●规则●双符号位,符号参与运算●末位加一位初值为0●根据b_{i-1}-b_i判断●-1加[-x]_补●1加[x]_补●0不变●算数右移●n次移位,最后移位完成再运算一遍●电路●无需C进行右移(符号位参与运算)●除法运算●原码除法●符号Q_s=x_s\oplus y_s●商的值|Q|=|X|/|Y|●恢复余数●步骤●默认商1,小于0则加回来●左移●LOOP●不恢复余数●原理●商多加A,左移,减A\Rightarrow (+A)\times 2-A=+A●商完与除数为负,商0,左移加除数●步骤●余数正商1,左移,减除数●余数负商0,左移,加除数●n次后商0,恢复余数●补码除法●规则●符号参与运算,除数、被除数、商、余数均用补码●除数被除数同号则减,异号则加●余数除数同号上1,左移减除数●余数除数异号上0,右移加除数●LOOP●末尾置1●电路●移位运算●算术移位(针对有符号数)●逻辑移位(无符号数)●循环移位●带进位位●不带进位位●浮点数表示和运算●浮点数表示●V = (−1)^s × M × r^E(r是基数,E是阶码,M称为尾数)●规格化●有效位越多,精度越高●尾数最高位为有效值●IEEE 754●V = (−1)^s × M × 2^E●类型●单精度●1+8+23●双精度●1+11+52●Bias=2^{k-1}-1●E=2^{exp}-Bias●三种类型●Case 1 Normalized Values●Exp is neither all zeros (numeric value 0) nor all ones●E = e − Bias, Bias = 2^{k-1}-1●The significand is defined to be M = 1+ f●M is in the range 1≤M<2● An implied leading 1 representation, getting an additional bit of precision for free●Case 2 Denormalized Values●exponent field is all zeros●E = 1− Bias●M = f●WHY?●Provide a way to represent numeric value 0●+0.0 has a bit pattern of all zeros●when the sign bit is 1, but the other fields are all zeros, we get the value −0.0●Represent numbers that are very close to 0.0●gradual underflow in which possible numeric values are spaced evenly near 0.0.●Case 3: Special Values●the exponent field is all ones●∞ : When the fraction field is all zeros●Overflow●NaN : When the fraction field is nonzero●Result cannot be given as a real number or as infinity● Representing uninitialized data●运算●加减●向大数对阶(损失精度更小)●尾数加减●规格化●舍入●Round-to-even(default mode)●The least significant digit of the result is even●Attempts to find a closest match●It will round upward about 50% of the time and round downward about 50% of thetime.●Round-toward-zero●Positive numbers downward and negative numbers upward●Round-down(截断)●Round-up●溢出判断●右规,exp全1●左规,exp全0●数据存储与转换●数据存储●按“边界对齐”方式存储●一次访存取出●空白填充●空间换时间●数据排列IEEE 754已规范,不影响●Little endian●least significant byte to most●Big endian●from most to least●0x01234567 in Machine●数据转换●C中转换情况●most numbers are signed by default●情况●标明转换●隐含转换●U和S运算均转换到U●同样字长整数转换--- Based on a bit-level perspective●The numeric values might change, But the bit patterns do not●T2U●Conversion from two’s complement to unsigned●Conversion from two’s complement to unsigned.●U2T●Unsigned to two’s-complement conversion●Conv ersion from unsigned to two’s complement●整数向大整数数转换●To convert an unsigned number to a larger data type ------ simply add leading zeros to therepresentation●To convert two’s-complement number to a larger data type------ perform a sign extension●Examples of sign extension●The proof of Expansion of a two’s-complement number by sign extension (by 1 bit)●When converting from short to unsigned, the program first changes the size and then the type.●整数向小整数转换●bit位截断●Truncation of an unsigned number●Truncation of a two’s-complement number●整数与浮点数的转换● int to float●the number cannot overflow●but it may be rounded●int or float to double● exact numeric value can be preserved (because double has both greater range)●greater precision can be preserved● double to float●the value can overflow to +∞ or −∞, since the range is smaller.●Otherwise, it may be rounded, because the precision is smaller.●float or double to int●value may be rounded toward zero●the value may overflow●Intel-compatible microprocessors designate the bit pattern [10 ... 00] (TMin_w forword size w)as an integer indefinite value.●3 存储系统●存储技术●SRAM●双稳态触发器●速度最快●易失性(断电后)●集成度低●Cache、Register File●DRAM●电容●速度快●易失性(2ms)●刷新●分类●集中刷新●固定时间一起刷新,有死区●分散刷新●读完刷新,没有死区,但降低了速度●异步刷新●缩短了死区,提高了效率,可在无请求时刷新●特点●透明●行刷新●破坏性读出●结构●存储体●二维阵列(引脚复用---时间换空间)●控制信号●译码器●片选控制●访存控制●读写控制●Memory●ROM●MROM●直接写入●PROM●一次可编程●EPROM●可擦除可编程●Flash闪存存储器●固态硬盘#ssd●页为单位读写●重写需要擦除整块 ------ 读比写快●随机访问●磁盘驱动器(磁盘)#disk●直接存取存储器●组成●磁盘●扇面●磁道●扇区●柱面●(不同盘面同一磁道)●性能指标●记录密度●磁盘容量●平均存取时间●寻道时间●平均旋转延迟(1/2TMAX)●传输时间●数据传输率●单位时间传输字节数●阵列●RAID0●无校验●无冗余●RAID1●镜像●海明纠错码●RAID2●RAID3●位交叉奇偶校验●RAID4●块交叉奇偶校验●RAID5●无独立校验阵列●光盘●串行读写●性能指标●容量●成本●速度●存取时间●启动存储器至完成操作时间●存取周期●存取时间+恢复时间●带宽●单位时间传输信息量●层次结构●原理●良好的程序符合局部性原理●高层充当下一层的高速缓存●层次●主存●存储技术:DRAM●编址方式●字节编址●容量及速度扩展●容量扩展●位扩展●无需片选●地址线相同●数据线不同●字节扩展●低位地址线相同●高位地址线做片选信号●字位扩展●多模块存储体●单体多字●一个存储单元放多字,速度提高●顺序存取●多体并行●高位交叉编址●顺序存取●地址空间增加,速度不变●低位交叉编址●交叉存放,并行读写●地址空间增加,速度提高●片选信号●线选●译码片选●主存选择与连接●与CPU有直连通道●数据总线●地址总线●决定访存空间●控制总线●读写●片选●选择芯片●ROM存放系统程序、标准子程序●RAM存放用户数据、代码●芯片尽量简化连线●地址线选择低位相连,高位译码●数据线连接●位扩展相连●片选线连接●访存●读写●高位地址线●Cache●存储技术:SRAM●组成●块(传送单元)●组●组中行●映射方式●直接映射●每个组一行●过程●组选择●标志位匹配及有效位检查●字选择●特点●简单●冲突大●组相联●每个组若干行●过程●组选择●每一行同时匹配及有效位检查●字选择●特点●增加硬件成本●冲突降低●全相联●只有一个组●过程●每一行的标志位匹配及有效位检查●字选择●特点●冲突最低●速度最快●硬件价格最高●适用●TLB●数据查找●分类●Miss->Memory●同步,Hit后取消访存●基本过程●组选择●行匹配●字选择●缓存不命中●分类●冷缓存●冲突不命中(放置策略)●容量不命中(容量大小)●替换算法●随机●FIFO●LRU(多维护位1位)●命中:低的加一●不命中有空闲,全体加一●不命中无空闲,最大出,全体加一●抖动●不断加载驱逐相同组●填充解决●写策略●写命中●写直达●写回(多修改位一位)●维护修改位●适用传送时间长●写不命中●非写分配●写分配●分配Cache空间,进Cache写,一般与写回搭配●系统中的Cache●分级Cache●数据、指令Cache●辅存●磁盘存储器#disk●固态硬盘 #ssd●映射关系●Cache—主存(速度)●虚拟存储器------主存—磁盘(容量、进程管理、空间保护)●段式虚拟存储器●页式虚拟存储器●段页式虚拟存储器●用户程序->虚拟地址(段)●用户●过程●段基址(USER)●段首址(SEGMENT)->段虚拟地址●段虚拟地址首地址+段内偏移->虚拟地址●虚拟地址->物理地址(页)●操作系统及硬件●页表●页命中(硬件)●地址翻译●缺页(OS+硬件)●磁盘调页●地址翻译●TLB(快表)●全相联●多级页表●思想●一级空表项无需创建二级页表●主存只需保存一级页表,二级页表随进程调入调出●前表项是后表基址,各个表比较标志位,直至找到物理页号●步骤●接收虚拟地址●MMU生成PTE请求●查询TLB●查询主存中多级页表●页面已加载?●已加载●读取PTE地址●MMU生成PA●未加载●触发异常●寻找牺牲页,若已修改则写回●调入新页面,更新内存●返回原先进程,重新执行指令●4 指令系统●指令系统●所有指令的集合●位于软硬件交界面●指令格式●组成●操作码●操作、功能●识别指令,了解指令功能与组成●地址码●被操作信息●分类●零地址指令●一地址指令●二地址指令●三地址指令●四地址指令●长度●与操作码与地址码长度有关,与机器字长无直接联系●分类●定长操作码●速度快●简化硬件,控制简单●变长操作码●有限字长,丰富功能●扩展操作码●操作码的位数随地址减少而增加●一,二,三地址可以组合●指令种类●数据传送●数据运算●转移●输入输出●寻址方式●指令寻址●顺序●跳跃●PC relative●They encode the difference between the address of the target instruction and the address ofthe instruction immediately following the jump●Give an “absolute” address●数据寻址●类型●隐含寻址●缩短字长●增加硬件●立即数寻址●位数限制●直接寻址●位数限制●间接寻址●扩大寻址范围●多次访存●寄存器寻址●寄存器直接寻址●快●寄存器数目少●寄存器间接寻址●快●访存●相对寻址(PC)●They encode the difference between the address of the target instruction and theaddress of the instruction immediately following the jump●基址寻址●面向操作系统●R中值不可修改●有利于多道程序设计,可用于编制浮动程序●变址寻址●面向用户●R中值可修改●主要用于处理数组问题●基址变址寻址●[BP]+[DI]+disp●比较●汇编指令●寄存器●格式●AT&T●movl $2, 8(%edx, %eax, 3)●Intel●mov long ptr [ebx+eax*3+8], 2●常用指令●数据传输●mov●lea●push●pop●数据运算●add/sub●cmp●inc/dec●mul/imul●div/idiv●被除数隐含在edx:eax●余数edx●and/or/Xor●text●not●neg●shl/shr●转移●jmp●jxx●call/ret●调用过程●存寄存器,存参数●call●存寄存器●。

计算机组成原理 考研知识点

计算机组成原理考研知识点一、知识概述《计算机组成原理- 指令系统》①基本定义:指令系统就是一台计算机能执行的所有指令的集合。

就好比一个厨师能做的所有菜的菜谱,计算机就按照这个“菜谱”来干活儿。

②重要程度:在计算机组成原理中超级重要。

它相当于计算机的智慧源泉,如果没有指令系统,计算机就不知道该干啥了。

③前置知识:得先了解二进制,因为计算机里都是用二进制来表示这些指令的。

还得稍微知道点计算机硬件的基本结构,比如有运算器、控制器这些东西。

④应用价值:比如说编写操作系统的时候就必须按照指令系统的规则来搞,开发各种软件也离不开它。

要是开发一款游戏,那游戏里的各种操作,像人物走动、攻击等,最后都要转化成指令系统里的指令。

二、知识体系①知识图谱:指令系统处于计算机硬件和软件的中间地带,连接着计算机的物理结构和软件系统。

②关联知识:和计算机硬件中的运算器、控制器、存储系统等关系很密切。

比如指令要在运算器里进行运算操作,控制器来取指令指挥计算机各个部分的协同工作。

③重难点分析:- 掌握难度:指令格式的理解有点难,不同类型的指令格式可能有各种不同的字段。

- 关键点:理解每条指令的功能、指令的编码方式以及指令在计算机中的执行过程。

④考点分析:- 在考试中的重要性:非常重要。

经常在考研里出现。

- 考查方式:可能是直接考指令格式的意义,也可能给出一段程序描述,让你判断需要用到哪些指令或者写出指令序列。

三、详细讲解【理论概念类】①概念辨析:- 指令:是计算机执行某种操作的命令,例如让计算机把两个数相加,“相加”这个操作对应的命令就是指令。

- 指令系统:前面说过啦,所有能执行的指令的集合。

它有一定的指令格式,就像写信有一定的格式一样,比如说有操作码字段,表示要进行什么操作,还有地址码字段,可能表示操作数在哪里。

②特征分析:- 格式固定性:就类似菜谱的格式固定一样,指令系统有它固定的格式,不过不同计算机可能格式不同。

- 功能明确性:每条指令的功能都很明确,不会模棱两可。

计算机组成原理考研知识点总结

计算机组成原理考研知识点总结计算机组成原理是计算机科学与技术专业的一门重要课程,作为计算机考研的知识点之一,它涉及到计算机的硬件结构、指令系统、运算器、控制器、存储器、输入输出设备等方面的内容。

本文将对计算机组成原理的知识点进行总结。

一、计算机系统结构计算机系统由硬件和软件两部分组成。

硬件包括中央处理器(CPU)、内存、输入输出设备等,而软件则包括操作系统、应用程序等。

计算机硬件可以分为运算器、控制器和存储器三部分,它们共同协作完成计算机的各种任务。

二、指令系统指令系统是计算机中的指令集合,用于规定计算机能够执行的操作。

指令系统包括机器指令的格式和指令的编码方式。

机器指令格式包括操作码、操作数、寻址方式等内容。

指令的编码方式有定长编码和变长编码两种方式。

三、运算器运算器是计算机的主要执行部件,负责进行各种算术和逻辑运算。

运算器包括算术逻辑单元(ALU)和寄存器。

ALU是进行算术和逻辑运算的核心部件,寄存器用于存储运算中的数据和结果。

四、控制器控制器是计算机的指挥部,负责协调指令的执行和各个部件的工作。

控制器包括指令寄存器、程序计数器、指令译码器等。

指令寄存器用于存储当前执行的指令,程序计数器用于存储下一条将要执行的指令的地址,指令译码器用于解析指令的操作码和操作数。

五、存储器存储器用于存储计算机运行时的指令和数据。

存储器包括主存储器和辅助存储器。

主存储器是计算机中运行速度最快的存储器,用于存储当前运行的程序和数据。

辅助存储器包括硬盘、光盘等,用于长期存储数据。

六、输入输出设备输入输出设备用于与外部环境进行信息交互。

输入设备将外界的信息输入到计算机中,包括键盘、鼠标、扫描仪等;输出设备将计算机处理的结果输出到外界,包括显示器、打印机、音响等。

七、总线总线是计算机中各个部件之间传输数据和信号的通路。

总线可以分为数据总线、地址总线和控制总线。

数据总线用于传输数据,地址总线用于传输数据的地址,控制总线用于传输控制信号。

计算机组成原理复习笔记

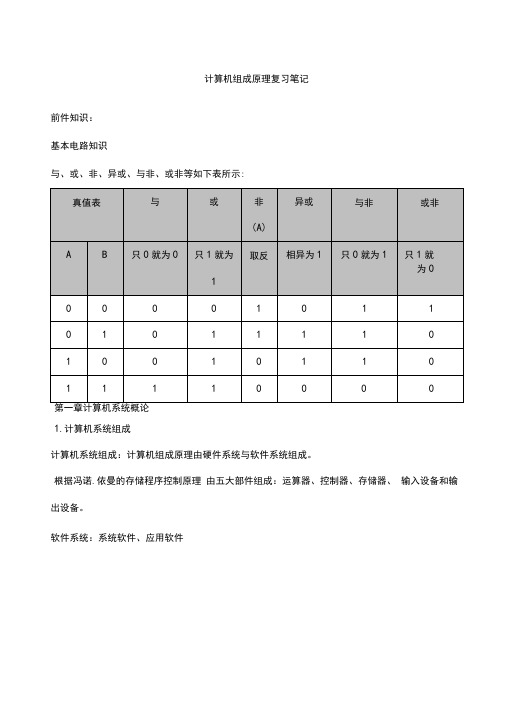

计算机组成原理复习笔记前件知识:基本电路知识与、或、非、异或、与非、或非等如下表所示:第一章计算机系统概论1.计算机系统组成计算机系统组成:计算机组成原理由硬件系统与软件系统组成。

根据冯诺.依曼的存储程序控制原理由五大部件组成:运算器、控制器、存储器、输入设备和输出设备。

软件系统:系统软件、应用软件外设:输入、输出设备、外存储器等应用软件特制软件摩尔定律:记住价格与时间成反比。

2 .计算机系统性能指标字长(处理机字长)是指计算机处理器一次能够完成的二进制位数(MIPS 是指计算机处理器每秒执行百万条指令。

3 .计算机系统的层次结构 计算机系统的层次结构分为五级以下图所示:中央处理器(CPU运算器 控制器 寄存器内存储器:DDR2 DDR3计算机系统操作系统数据库管理系统程序编译工具软件系统通用软件16, 32, 64)。

第二章运算方法和运算器1.原码、反码、补码、移码的计算方法性质原码反码补码正数原码反码补码一样负数连同符号位一起使用二进制表不除符号位以外其余位取反(0变1,1变0)除符号位外其余位取反加1(性质等于在反码基础之上加1)零[+0]原=0。

-00 [-0]原=10 (00)[+0]反=00-- 00[-0]反=11 (11)[+0]补=[-0]补=00--00移码主要用于表示浮点数中补码的真值公式:将所有位上的数按基数移码的阶码2n-1 (n为数所在的位置)相乘后求出和,这个和的结果就是补码的真值。

计算某个数大于或小于某个值得条件。

例:[X]补=(01101) 2,[Y]补=(11101) 2。

则X与Y的十进制数是多少。

X=-0 X 24+1 X 23+1 X 22 +0 X 21+1 X 20 =8+4+1=(+13) 10Y=-1 X 24+1 X 23+1 X 22 +0 X 21+1 X2°=-8+4+1= (-1)102.原码、反码、补码、移码的表示范围(n位二进制位数)浮点数的表示范围就省略了。

上海市考研计算机组成原理重点知识梳理

上海市考研计算机组成原理重点知识梳理计算机组成原理是计算机科学与技术专业考研中的一门重要课程,它主要涉及计算机硬件系统的基本组成和工作原理。

在考研复习阶段,掌握计算机组成原理的重点知识是非常关键的。

本文将对上海市考研计算机组成原理的重点知识进行梳理。

一、计算机硬件的基本组成计算机硬件主要由中央处理器(CPU)、存储器和输入输出设备组成。

1. 中央处理器(CPU)中央处理器是计算机系统中的“大脑”,它主要负责执行指令和控制操作。

CPU由控制器和运算器组成,控制器负责指令的解码和控制操作,运算器负责数据的运算和处理。

2. 存储器存储器用于存储计算机程序和数据,它分为主存和辅助存储器。

主存储器是计算机中的主要存储器,它能够直接被CPU访问,常见的主存储器有内存条和高速缓存。

辅助存储器主要用于长期存储数据,如硬盘、光盘等。

3. 输入输出设备输入输出设备用于与计算机系统进行信息交互,常见的输入设备有键盘、鼠标等,常见的输出设备有显示器、打印机等。

二、计算机指令与指令系统计算机指令是计算机硬件执行的基本单位,指令系统是计算机中所有指令的集合。

1. 指令的格式计算机指令通常由操作码和操作数两部分组成。

操作码用来表示指令的功能,操作数用来表示指令的操作对象。

2. 指令的分类根据指令的功能和操作对象不同,指令可以分为数据传输指令、算术逻辑指令、控制指令等。

3. 指令的执行过程指令的执行过程主要包括指令寻址、指令获取、指令解码和指令执行等几个阶段。

三、计算机的运算方法计算机通过运算方法来实现各种复杂的计算和运算,其中包括定点数的运算和浮点数的运算。

1. 定点数的运算定点数的运算是指对固定范围的数进行运算,常见的定点数运算包括加法、减法、乘法和除法等。

2. 浮点数的运算浮点数的运算是指对任意范围的数进行运算,浮点数运算一般包括加法、减法、乘法和除法等。

四、计算机的存储器结构计算机的存储器结构包括层次结构和地址映射。

1. 存储器的层次结构计算机的存储器按照速度和容量的不同,可以分为多层次的结构,包括高速缓存、主存和辅助存储器等。

组成原理最终笔记

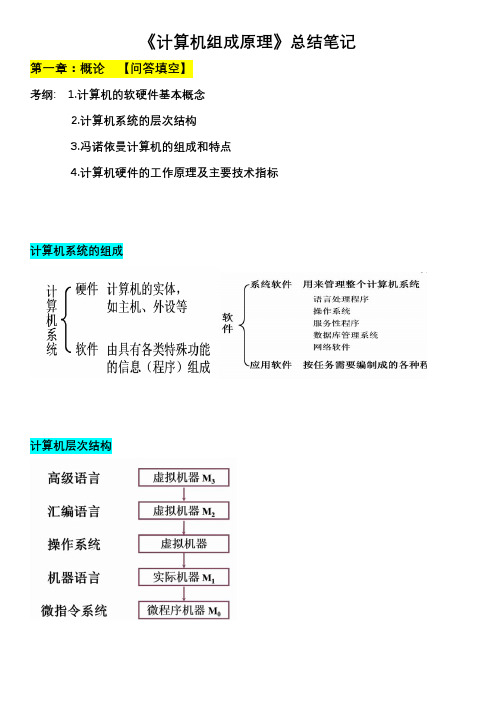

《计算机组成原理》总结笔记第一章:概论【问答填空】考纲: 1.计算机的软硬件基本概念2.计算机系统的层次结构3.冯诺依曼计算机的组成和特点4.计算机硬件的工作原理及主要技术指标计算机系统的组成计算机层次结构冯诺依曼计算机的组成和特点组成:由运算器、存储器、控制器、输入设备和输出设备五大部件组成特点:1、指令和数据以同等地位存于存储器,可按地址寻访2、指令和数据均用二进制表示3、指令由操作码和地址码组成,操作码表示操作性质,地址码用来表示操作数在存储器中的位置4、指令在存储器内按顺序存放5、机器以运算器为中心(现在机器以存储器为中心)注:冯诺依曼计算机工作方式的基本特点是按地址访问并顺序地址执行计算机五大部件的功能运算器:完成算术运算和逻辑运算,并将运算的中间结果暂存在运算器内存储器:用来存放数据和程序控制器:控制、指挥程序和数据的输入、运行以及处理运算结果(自动识别数据和指令) 输入设备:将人们熟悉的信息形式转换为机器能识别的信息形式输出设备:将机器运算结果转为人们熟悉的信息形式注:现代计算机由三部分组成:CPU、I/O、主存储器算术逻辑单元(Arithmetic Logic Unit ALU):完成逻辑运算控制单元(Control Unit CU):用来解释存储器中的指令,并发出各种操作命令和执行命令。

ALU和CU为CPU的核心部件计算机硬件的工作原理及主要技术指标MIPS (million instructions per second):百万条指令每秒CPI (Cycle Per Instruction):执行一条指令所需的时钟周期(机器主频的倒数)FLOPS (floating-point operations per second):浮点运算次数每秒扩展与练习机器字长:指CPU一次能处理数据的位数(简称字)指令字长:机器指令中含二进制代码的总位数存储字长:在存储单元中二进制代码的个数存储容量= 存储单元个数×存储字长程序计数器(Program counter PC):存放下一条指令地址指令寄存器(Instruction register IR):用于存放当前从主存读出的正在执行的指令数据寄存器(Data Register DR):用于存储操作数、结果、信息存储器地址寄存器(Memory Address Register MAR):存放欲访问的存储单元的地址存储器数据寄存器(MDR):用来存放从存储单元取出的代码或准备存入存储单元的代码1秒=103 毫秒=106 微秒=109 纳秒1s =103 ms=106 μs=109 ns问:指令和数据都存于存储器中,计算机如何区分它们?1、通过不同的时间段来区分指令和数据,在取指令阶段取出的是指令,在执行指令阶段取出的是数据2、通过地址来源区分,由PC提供存储单元地址取出的是指令,由指令地址码部分提问:什么是指令?什么是程序指令:由操作码和地址码,分别表示何种操作和存储地址程序:程序是可以连续执行,并能够完成一定任务的一条条指令的集合程序由指令组成第二章:计算机发展及应用【问答填空】考纲:1.Moore定律2.计算机发展的五个阶段Moore定律摩尔定律:微芯片上集成的晶体管数目每3年翻两番(现在不适用改为每3年翻1番)计算机发展的五个阶段第一代电子管计算机(1946年-1957) 主要元器件是电子管第二代晶体管计算机(1958年-1964) 用晶体管代替了电子管第三代中小规模集成电路计算机(1965-1970) 主要以中、小规模集成电路取代了晶体管第四代大规模集成电路计算机(1971至今) 采用大规模集成电路和超大规模集成电路第五代计算机智能计算机扩展与练习问:什么是摩尔定律,该定律是否永久生效?为什么?摩尔定律指出,微芯片上集成的晶体管数目以每三年翻两番的规律递增,但由于物理极限的闲置,摩尔定律不能永久生效第三章:系统总线【问答计算】重点考纲: 1.系统总线的概念及类型2.总线仲裁方式3.总线特征及性能指标:总线宽度、总线时钟频率、总线带宽4.总线结构及控制方式5.流行的总线标准系统总线的概念及类型总线分成三大类:片内总线(芯片内部的总线)、系统总线(计算机各部件之间的信息传输线)、通信总线(计算机系统之间或计算机)系统总线分为三大类:数据总线、地址总线、控制总线数据总线:传输各功能部件之间的数据信息,总线宽度特指数据总线的根数,是衡量系统性能的一个重要参数(双向传输,其位数与机器字长,存储字长有关)地址总线:用来指出数据总线上的数据源或目的数据在主存单元的地址或I/0设备的地址,(单向传输,只能读或写,地址线的位数与存储单元个数有关,如地址线有20根,则对应的存储单元个数为220)控制总线:用来发出各种控制信号的传输线(可进可出,可以认为是双向)总线特征及性能指标:总线宽度、总线时钟频率、总线带宽总线特性:机械特性(尺寸、形状、管脚数、排列顺序)、电器特性(传输方向和有效电平范围)、功能特性(每根传输线的功能(传地址、传数据和发出控制命令) )、时间特性(信号的时序关系)总线的性能指标:总线宽度:数据线的根数标准传输率:每秒传输的最大字节数(MBps)时钟同步/异步:同步、不同步总线复用:地址线与数据线复用信号线数:地址线、数据线和控制线的综合总线控制方式:突发、自动、仲裁、逻辑、计数其它指标:负载能力总线结构及控制方式以及总线总裁(总线判优)DMA总线:用于高速I/O设备与主存之间直接交换信息总线总裁方式:分为集中式(链式查询、计数器定时查询、独立请求方式) 和分布式链式查询方式:对电路故障很敏感,优先级别低的设备很难获得请求计数器定时查询方式:相比链式查询多了一组设备地址线,少了一根总线同意线(BG),能改变计数器的初值从而优先次序可以改变,但增加了控制线(设备地址)数,控制也变得复杂独立请求方式:响应速度快,优先次序控制灵活(通过程序改变),但控制线数量多,总线控制更复杂(硬件成本最高)总线通讯控制:同步通信、异步通信(不互锁、半互锁、全互锁)、半同步通信流行的总线标准PCI总线:外设使用AGP总线:显卡使用RS-232C总线:串行总线USB总线:热拔插扩展与练习1.一个总线传输周期包括申请分配阶段、寻址阶段、传输阶段和结束阶段四个阶段2.总线同步影响总线效率的原因是:必须按照最慢速度来设计公共周期问:总线时钟频率为33MHz,总线宽度为32位,则总线带宽为多少?33MHz ×32bit = 33MHz ×4B = 132MBps注:总线带宽=总线频率(每秒传输次数)×总线宽度(每秒传输多少位数据)。

计算机组成原理笔记

计算机组成原理笔记1.计算机系统简介(硬件部分)计算机系统组成硬件计算机的主体,如主机、外设软件系统软件:⽤来管理整个计算机系统语⾔处理程序操作系统服务性程序数据库管理系统⽹络软件应⽤软件:按任务需求编写的各种软件计算机系统层次结构从程序员⾓度硬件微指令系统(微程序机器M0):由硬件直接执⾏微指令机器语⾔(实际机器M1):⽤微指令解释机器指令软件操作系统(虚拟机器M2):⽤机器语⾔解释操作系统汇编语⾔(虚拟机器M3):⽤汇编程序翻译成机器语⾔程序⾼级语⾔(虚拟机器M4:⽤编译程序翻译成汇编语⾔程序计算机体系结构和计算机组成的区别计算机系统程序员所见到的计算机系统的属性的概念性的结构和功能特性指令系统、数据类型、寻址技术、I/O机理等计算机组成实现计算机体系结构所体现的属性具体指令的实现2.计算机的基本组成冯·诺伊曼计算机的特点1.计算机由五⼤部件组成2.指令和数据以同等地位存于存储器,可按地址寻访3.指令和数据⽤⼆进制表⽰4.指令由操作码和地址码组成有加减乘除指令,取地址指令5.存储程序(重要特征)6.以运算器为中⼼我们现在普遍使⽤的计算机⼴义上都属于冯·诺伊曼计算机冯·诺伊曼计算机硬件框图缺点:以运算器为中⼼的计算机,使得运算器的运算速度成了计算机性能的瓶颈以存储器为中⼼的现代硬件框图主机CPU运算器ALU控制器CU存储器主存辅存I/O设备输⼊设备输出设备存储器的基本组成存储器-存储体-存储单元-存储元件(0/1)存储体主存储器MAR:存储器地址寄存器,反映存储单元的个数MDR:存储器数据寄存器,反映存储字长存储单元:存放⼀串⼆进制代码,每个存储单元赋予⼀个地址,按地址寻访存储单元存储字:存储单元中⼆进制代码的组合存储字长:存储单元中的⼆进制代码位数运算器的基本结构和⼯作过程X、ACC、MQ、MQ均为寄存器控制器的基本结构控制器的功能解释指令:取址-分析-取操作数-执⾏指令-保存结果保证指令按次序执⾏完成⼀条指令取指令 PC:程序计数器分析指令 IR:指令寄存器执⾏指令 CU:控制单元控制器的基本组成PC:存放当前欲执⾏指令的地址,具有计数功能IR:存放当前欲执⾏的指令CU:执⾏指令运算器 + 控制器 + 存储器 = 主机主机完成⼀条指令的过程以取数指令为例- 1、2、3、4:取指令 - 5、6、7、8、9:取数以存数指令为例- 1、2、3、4:取指令 - 5、6、7、8、9:存数⼀元⼆次⽅程程序的运⾏过程将程序通过输⼊设备送⾄计算机程序⾸地址 >> PC启动程序运⾏取指令:PC >> MAR >> M(存储体) >>MDR >> IR,PC + 1 >> PC分析指令:OP操作码(IR) >> CU执⾏指令:Ad地址码(IR) >> MAR >> M >> MDR >> ACC.....打印结果停机计算机硬件的主要技术指标机器字长CPU⼀次能处理数据的位数与CPU的寄存器的位数有关运算速度主频核数:每个核⽀持的线程数CPI:执⾏⼀条指令所需要的时钟周期数MIPS:⼀秒执⾏百万条指令、FLOPS:每秒浮点运算次数存储容量主存容量存储单元个数*存储字长:如2^MAR (K) * MDR字节数:如2^13(b) = 1KB辅存容量字节数:如80GB3.总线总线的基本概念什么是总线总线是连接各个部件的信息传输线吗,是各个部件共享的传输介质总线上信息的传送串⾏:远距离使⽤并⾏:单板内或板间使⽤总线分类⽚内总线:芯⽚内部的总线系统总线:计算机各部件之间的信息传输线数据总线:双向,与机器字长、存储字长有关地址总线:单向,与存储地址、I/O地址有关控制总线:存储器读写、总线允许、中断确认通信总线:⽤于计算机系统之间或计算机系统与其他系统(如控制仪表、移动通信)等之间的通信传输⽅式串⾏通信总线并⾏通信总线总线控制总线优判控制基本概念主设备(模块)对总线有控制权从设备(模块)响应从主设备发来的总线命令总线的优判控制集中式链式查询:连接⽅式决定了优先级,其结构简单计数器定时查询:可通过软件⽅式改变优先级,较灵活独⽴请求⽅式:速度更快,总数较多分布式总线的通信控制⽬的:解决通信双⽅协调配合问题总线传输周期申请分配周期:主模块申请,总线仲裁决定(即上述的总线优判控制)寻址阶段:主模块向从模块给出地址和命令传数阶段:主模块和从模块交换数据结束阶段:主模块撤销有关消息总线通信的四种⽅式同步通信:由统⼀时标控制数据传送异步通信:采⽤应答⽅式,没有公共时钟标准半同步通信:同步、异步结合分离式通信:充分挖掘系统总线的⼀个瞬间的潜⼒4.存储器概述按存取⽅式分类存取时间与物理地址⽆关(随机访问)随机存储器只读存储器存取时间与物理地址有关(串⾏访问)顺序存取存储器:如磁带直接存取存储器:如磁盘按作⽤分类主存储器RAM静态RAM动态RAMROM:只读可擦写不可擦写辅助存储器磁盘、磁带、光盘闪存(Flash Memory)U盘、SSD⾼速缓冲存储器(Cache)存储器的层次结构- CPU运⾏相对与主存过快,导致不平衡,受限于主存,缓存-主存这⼀结合解决了速度问题 - 虚地址即我们写代码调试时所看见的的地址,程序访问存储器所使⽤的逻辑地址称为虚拟地址主存储器主存基本组成主存和CPU的联系主存中存储单元地址⼤端模式:数据的⾼字节保存在内存的低地址中,⽽数据的低字节保存在内存的⾼地址⼩端模式:数据的⾼字节保存在内存的⾼地址中,⽽数据的低字节保存在内存的低地址⼀根地址线只能表⽰0和1,cpu在内存或硬盘⾥⾯寻找⼀个数据时,先通过地址线找到地址,然后再通过数据线将数据取出来。

计算机组成原理笔记总结

计算机组成原理笔记总结

计算机组成原理是指计算机硬件的组成结构、工作原理、性能指标以及指令系统等方面的基础知识。

以下是计算机组成原理的一些重要内容和笔记总结:

1. 计算机的五大基本组成部分:中央处理器(CPU)、主存储器、输入设备、输出设备和外部设备。

2. 中央处理器(CPU)是计算机的核心,由算术逻辑单元(ALU)、控制单元(CU)、寄存器等组成。

3. 主存储器用于存储程序和数据,分为随机存取存储器(RAM)和只读存储器(ROM)。

4. 输入设备用于将外部数据或命令输入到计算机,包括键盘、鼠标、扫描仪等。

5. 输出设备用于将计算机处理结果输出给用户或其他设备,包括显示器、打印机、音响等。

6. 外部设备是连接计算机系统的外部设备,例如硬盘、光驱、USB设备等。

7. 指令系统是计算机硬件与软件之间的桥梁,是计算机程序的基础。

8. 计算机的工作原理是指计算机如何通过处理器执行指令、存

取数据等,包括取指令、译码指令、执行指令等步骤。

9. 性能指标是衡量计算机性能的指标,包括时钟频率、存储器容量、带宽、吞吐量等。

10. 计算机的发展历程经历了多个阶段,从第一代计算机的大

型机到现代个人计算机的微型机。

通过学习计算机组成原理,可以深入了解计算机的硬件组成、工作原理及其与软件之间的关系,为深入学习计算机体系结构、操作系统、编译原理等相关知识打下坚实的基础。

计算机组成原理(考研+期末)重点知识点总结

计算机组成原理(考研+期末)重点知识点总结一、Ch01&02: 概论与数据表示●计算机系统组成1.硬件系统●冯·诺依曼思想●提出使用二进制作为计算机数制基础|●二进制运算规则简单●0/1状态更容易用物理状态实现●适合采用布尔代数方法实现运算电路●存储程序将程序存放在计算机的存储器中●程序控制计算机中控制器逐条取出存储器中的指令并按顺序执行●五大部件●运算器运算器完成算术运算,逻辑运算●控制器控制器控制指令的执行,根据指令功能给出实现指令功能所需的控制信号●存储器主存储器存放程序及数据●输入设备●输出设备●系统互联总线(Bus)是连接两个或多个设备的公共通信线路2.软件系统●应用软件●系统软件●操作系统●固件(Firmware)固化的软件,兼具硬件和软件的特性,如BIOS3.层次结构●高层是底层功能的扩展,低层是高层的基础●计算机性能指标与评价1.非时间指标●字长CPU一次操作能处理的最大数据位宽,一般与寄存器、运算器、数据总线的位宽相等●主存容量主存能存储的最大信息量,一般用MxN表示(M表示存储单元数,又称子容量;N表示每个存储单元存储的二进制位数,也称位容量)2.与时间有关的性能指标●时钟周期时钟周期是计算机中最小最基本的时间单元,在一个时钟周期内CPU完成一个最基本的动作时钟周期是时钟频率的倒数,也称节拍周期或T周期,随着主频的提高时钟周期将变短●CPI(Clock Cycles Per Instruction)执行每条指令所需要的平均时钟周期数●计算机数据表示1.进制转换●十进制转二进制真值●整数部分除2取余,倒着取,直到商为0为止●小数部分乘2取整,正着取,直到满足位数或小数部分为0为止2.数值编码●真值用正负号+/-表示正负的二进制数值●机器码将符号和数值一起编码表示的二进制数●原码符号位0正1负,数值位不变●表示区间●定点小数●定点整数●反码符号位与原码相同,数值位上正数与原码相同,负数为原码取反●表示区间与原码一致●补码●模的概念a ≡b (mod m) 模为m●时钟原理:表示负数时可以使用模的性质转换成正数,即把减法变成加法●负数的补码可以用模数加上该负数获得●有字长限制的二进制运算为有模运算,模数为最高位进位的权值●计算机中补码的定义●设定点小数x0.x1x2...xn 其中x0为符号位,该数模数为最高位进位2●根据补码定义可知●扩展至n位定点整数而言●求补码的简便方法●反码法(适合机器运算)当X为负数时,补码等于反码末位加1当x为正数时,补码与原码一致●扫描法(适合手工计算)当X为负数时,对真值部分从右到左扫描,右起第一个1及其右边的0保持不变,左边的真值位全部取反●移码●只能用于定点正数的表示,通常用于表示浮点数的阶码●移码与补码只有符号位相反,其余全相同3.浮点数表示●二进制浮点数采用了类似十进制科学计数法的表示方法●阶码E(Exponent)是定点整数,用移码表示●尾数M(Mantisa)是定点小数,用补码表示●浮点数表示范围●IEEE754标准4.汉字区位码●GB2312编码●双字节编码,16位,其中两个字节的最高位都是1,实际有14位编码空间●实际没有填满,使用94x94的矩阵表示所有汉字字符,矩阵的每一行称为“区”,每一列称为“位”●转换公式:区位码 + A0A0H = GB2312编码●汉字机内码计算机内部存储的汉字编码,如GB系列编码●汉字输入码(外码)使用英文键盘输入汉字的编码,即输入方案●流水码●音码(拼音)●形码(五笔)●音形码●汉字字形码(输出码)输出汉字的图形点阵数据,字形码按区位码排列的二进制文件称为汉字库●数据校验1.码距与校验●校验码在原始数据中引入部分冗余信息用于校验●码距/海明距离一个编码集内两个不同编码对应二进制位不同的个数●校验码的目的在于提高编码集中最小码距●码距越大,抗干扰能力越大,纠错能力越强,数据冗余越大,编码效率越低2.奇偶校验●冗余位:1位校验位P●检验串中1的个数●检错位G=1一定出错●只能提供奇数位错误的检错3.二维奇偶校验/交叉奇偶校验●将一个串分成很多等长的子串,按行分布在二维矩阵里,同时进行行和列的奇偶校验●一个数据位参加多个检验组,发生错误可在多个检测码中反馈4.海明校验5.CRC循环冗余校验●模2运算不考虑进位和借位的运算●生成步骤●1. 将原数值M左移r位得到R●2. 找一个r+1位的二进制串G●3. 用模2除法求R除以G得到的余数填在右边的空白r位上就是冗余码部分●解码将校验码除以生成多项式(约定的二进制串G)后余数为0表示数据正常二、Ch03: 运算器●定点加减法运算1.运算定义●补码加法●补码减法2.溢出检测●监测符号位:正正得负 & 负负得正 -> 溢出●监测进位:符号位进位与数值位进位不同为溢出●双符号位:将符号位扩展成两位进行运算●若相加后两个符号位不同为溢出●符号位最高位永远是正确符号位3.逻辑实现●全加器(FA)带进位的一位加法器●逻辑表达式●逻辑电路●半加器(HA)没有进位输入●多位串行加法器●先行进位加法器●定点乘法运算1.原码一位乘法●符号位:异或●真值部分:普通竖式运算●部分积使用累加寄存器存储2.补码一位乘法●符号位参与运算,可以采用单符号位,双符号位用于溢出检验●运算步骤●先写出[X]补,[-X]补,[Y]补备用,画出运算表格,注意[Y]补要在最右边扩充一个0●判断乘数[Y]补最后两位,决定部分积加哪个数●01:[X]补●00/11:0●10:[-X]补●将部分积和乘数都右移一位,注意左边移出的位接在右边●部分积是算术右移,即符号位扩展右移,且右边没有限制●乘数右边是位宽墙,不需要扩展●重复上述步骤直到乘数不足一位,将最终结果与移出位拼起来形成答案●浮点运算1.浮点加减法运算●阶码和尾数均采用补码表示●对阶:使两浮点数阶数相等,尾数就可以直接相加●规则:小阶向大阶看齐小阶放大,尾数减小,右移损失的是影响较小的低位●步骤●求阶差:减法运算●尾数移位●保留附加位移除的低位部分(的最高位),作为附加位参与中间运算提高精度●通常保留三个保留附加位,从右到左排序(高位到低位)●保护位●舍入位●粘位舍入位右侧还有数则粘位为1,否则为0●尾数运算●结果规格化目的是保证浮点数编码唯一性,真值格式是数据位的最高位一定是1●规格化方法●左移规格化(左规放大)●绝对值小于0.5需要放大●移动(逻辑左移,补0)多少位阶码减多少●注意符号位一起移●右移规格化(右规减小)●绝对值超过1,发生上溢●只需要算术右移(保留符号位)一位,阶码+1●舍入●末位恒置1法只要移位丢失的位中有一位是1,结果末位就是1●0舍1入法丢失位最高位若是1则将尾数末位+1●舍入可能破坏规格化结果,因此需要再次规格化●溢出判断●只有阶码移除才算溢出●当阶码符号位为01或10时结果溢出●IEE754浮点数●阶码用移码表示,尾数用原码表示,且尾数的最高位隐藏●对阶和规格化采用移码的计算规则●尾数隐藏位参与运算,采用原码运算规则2.浮点乘法运算●第一步:阶码相加●第二步:尾数相乘●第三步:规格化舍入三、Ch04: 存储系统●存储系统概述1.存储器的分类●按存储介质●磁存储器包含机械装置,体积大,速度慢,成本低●半导体存储器了解其是什么,不必掌握原理●双极型存储器●MOS存储器●静态MOS存储器(SRAM)●动态MOS存储器(DRAM)●光存储器(光盘)●按存储方式●随机存储器(RAM,Random Access Memory)根据地址随机读写数据单元,访问时间与访问位置顺序无关半导体存储器是随机存储器●顺序存储器(SAM,Sequential Access Memory比如磁带存储器●直接存储器(DAM,Direct Access Memory)不需要顺序搜索就能直接存取信息,兼具RAM和SAM的特性(根据地址读写,但时间和位置并非完全没有关系)磁盘是DAM,由于机械结构的延迟导致其时间和磁头与目标扇区的距离有关●按可写性●读写存储器●只读存储器(ROM,Read-Only Memory)●按可保存性●易失性存储器●非易失性存储器●按功能和速度●寄存器存储器●高速缓冲存储器(高速缓存Cache)隐藏在寄存器和主存之间的高速小容量存储器,用于存放CPU常用或即将使用的指令和数据,一般由SRAM构成,用于缓冲CPU寄存器和主存之间的性能差异●主存储器(主存)CPU除寄存器外唯一能直接访问的存储器,用于存放指令和数据,通过地址直接、随机地读写主存主存一般是半导体存储器,但还包括BIOS和硬件端口等●外存储器(外存/辅助存储器)容量大,但速度块,如磁盘、磁带、光盘、网络存储阵列等2.存储器性能指标●存储容量●位表示法用存储器中存储单元总数与存储字长(每个单元的位数)的乘积表示,如1K*4位(K=1024)●字节表示法带B表示法,1B=8位●存取速度●存取时间(访问时间)启动一次存储器操作到操作完成的时间,注意读写时间可能不同(DRAM读慢写快,闪存读快写慢)●存取周期连续启动两次操作之间最短的间隔时间,略大于存取时间对于主存而言,周期除了包括存取时间还包括状态恢复时间●存储器带宽单位时间内存储器能传输的信息量,与存储时间的长短和一次传输的数据位多少有关一般来说,存取时间越短,数据位宽越大,存储带宽越高3.存储系统层次结构4.DRAM刷新●刷新的概念定期补充电荷以避免电荷泄露(泄露电流)引起的信息丢失●刷新周期●刷新周期是存储器实际完成两次完整刷新的时间间隔●最大刷新周期:信息存储到数据丢失之前的时间间隔●按行刷新动态存储器的刷新按行进行●减少存储矩阵的行数,增加列数,可以减少刷新周期●刷新地址由刷新地址计数器产生,而不是CPU发出,位数与存储芯片的行数有关●每个刷新周期内,刷新地址计数器从0到最大值循环遍历一次●刷新时DRAM不能响应CPU访问,称为死时间●刷新方式由于CPU和内存刷新控制器存在内存争用问题,由不同的解决方案决定了不同的刷新方式●集中刷新●最大刷新周期:2ms●在数据丢失之前集中刷新所有行,即一个最大刷新周期的时间的最后部分全部用于刷新,其余时间用于读写●存在死区(集中刷新的区段CPU长时间无法访问),用于实时要求不高的场合●分散刷新●最大刷新周期:2ms●一次读写操作后紧跟着一个刷新操作,一个读写+刷新操作被称作一个存储周期●刷新次数过多,浪费了时间,用于低速系统●异步刷新(最常用)●最大刷新周期:2ms●各刷新周期分散地安排在一个最大刷新周期中●假设存储矩阵有有128行,每隔2ms/128=15.5微秒刷新一行,将128次刷新分散●主存系统1.主存特征●基本结构●空间逻辑上可以看作一个一维数组,每个数组元素存储一个m位的数据单元,主存地址就是数组的下标索引●硬件结构由存储体(DRAM)和外围电路(包括译码器、数据寄存器和读写控制电路构成)●存储体有2^n个m位的存储单元●地址译码器接受来自CPU的n位地址信号,转换成2^n根地址译码信号,其中每根译码信号都连接一个存储单元,2^n个译码信号中有且只有一个信号有效●数据暂存器暂存CPU送来写入的数据或主存读出的数据●读写控制电路接受CPU的读写控制信号,决定存储器的读写模式●数据存放●存储字长主存中每个存储单元存储的位数●数据字长(字长)计算机一次能处理的二进制位数,存储字长和数据字长不一定相同●地址访问模式存储字长都是字节(8-bit)的整倍数,通常按字节编址●字节地址(8位)●半字地址(16位)●字地址(32位)●小端(Little-Endian)存储数字中低位先存(在地位内存),大端存储与之相反●边界对齐●跨n个字节地址的变量访问需要消耗n个存取周期●对齐后访问速度高,不对齐节约主存空间2.主存的组织与CPU连接●存储器扩展左侧是4片2K x 2位的字长扩展右侧是4片8K x 8位的字数扩展●位扩展(DBUS,字长扩展/数据总线扩展)适用于存储芯片的数据总线位宽小于CPU数据总线位宽●各芯片同时并行工作●字扩展(ABUS,字数扩展/容量扩展/地址总线扩展)适用于存储芯片的单元字长小于要求的存储单元字长●CPU给出地址后,经译码器片选后,同一时刻只有一个芯片在工作●综合扩展●考察重点●根据要求对存储器的组合●不同存储器之间的关系(串联OR并联/多合一OR一分多)3.并行主存系统●SDRAM(同步DRAM,Sync Dynamic Random Access Memory)●普通DRAM的访问过程是CPU给出地址和控制信号 -> 经过存取时间后完成操作,存取时间内CPU只能等待●同步DRAM与CPU的数据交换时钟信号同步,不需要等待●DDR(Double Data Rate)SDRAM●在时钟周期的上/下沿各进行两次数据传输●DDRn代表2^n路总线,提升总带宽●双端口存储器双端口存储器有两组相互独立的端口,分别可独立地进行读写操作●两个端口地址不同时,不会发生冲突,可以并行读写●两个端口地址相同时,发生冲突●每个端口有一个阻塞标志BUSY,置0时表示阻塞,置1表示复位●冲突发生时由逻辑判断哪个端口优先操作,并将另一个端口置0,优先端口操作完成后再复位另一个端口,继续操作●多通道内存技术组织方式与存储扩展中的字长扩展方式一致(并联)●单体多字存储器(联动模式)多个存储模块共享地址总线,因此读取一个地址时可以并行读取到多个模块中同一地址的单元,从而实现在一个周期内访问多个存储字,m个存储模块可以提升m倍带宽●所有存储模块同步并发,共用同一个地址寄存器●单存储周期访问多个存储字,数据线为合并结果●性能线性增长,总线位宽变换●要求内存的容量、频率、时许完全一致●多体多字存储器(非联动模式)两个模块之间通过独立的片选信号、地址总线和读写控制线,数据总线也彼此独立,因此两根内存不需要同步,但仍是并发工作●多体单字存储器(多体交叉存储器/编址方式)由多个容量、存取速度相同的存储模块构成,但彼此之间不是并发运行,根据其编址方式的不同进行分类(把地址中哪一部分交给选片器)●高位多体交叉(顺序编址)●多模块串行,相邻地址在同一存储体内先顺着编完一个模块,再编下一个模块●可以扩充容量,但由于程序具有局部性和连续性的特点,往往会导致一个存储体访问频繁而其他存储器空闲●方便故障隔离,无性能提升●低位多体交叉(交叉编址)●多模块流水并行,相邻地址在不同存储体中●可以扩充容量并提升性能(减少恢复时间的影响)●适合突发的顺序访问,是带cache的主存(SDRAM和多通道内存)编址模式●考察重点:不同编址方式下的带宽计算(时间)●存储周期公式:T=nt●T=存储模块的存储周期●n=交叉模块数(通常为2的幂次方)●t=总线的反应时间/存储体切换时间●顺序编址读写时间:t总=nT●T=存储周期●n=读写的存储字个数●交叉编址读写:t总=T+(n-1)t●T=存储周期●n=读写的存储字个数●t=最短反应时间●带宽:W=B*n/t总●B=总线位宽度●n=读写的存储字个数●t总=读写总时间4.高速缓冲存储器(cache)SRAM相比DRAM速度更快,但容量小、功耗大、价格高,可用于缓冲(cache),缓解主存与CPU之间的性能差异,推而广之,一切有性能差异的地方都可以有cache●cache 工作原理●根据SRAM中cache块的大小,将主存进行分块(块大小与cache块大小相同),并对主存块进行编号●使用cache的理论依据:程序局部性在一段时间内,整个程序的执行仅限于程序中的某一部分,而执行程序所需的指令也仅限于某个存储区域●时间局部性(反复调用)当程序访问一个存储位置时,该程序在未来可能被多次访问(如循环体)●空间局部性(连续存放)一旦程序访问了某个存储单元,其临近的存储单元大概率也即将被访问(代码、数组等数据在主存中均按顺序存放)●cache 读操作流程●CPU接受要读取的地址,解码并在cache中查找地址●如果命中,则根据地址读出cache中数据并返回CPU●如果缺失,则为缺失的数据分配cache块(可能发生块替换),载入内容并更新cache,然后再读取数据返回CPU●cache 写操作流程●CPU接受地址,解码并在cache中寻找对应地址●若查找命中,则直接进行数据写入;若查找缺失,则根据是否采用写分配法进行下一步操作●写分配法(Write-Allocate)需要先将数据块载入cache,重新进行写命中流程●非写分配法则直接将数据写入主存●在写命中后,将数据写入到cache中●若采用写回(Write-Back, WB)策略,则将该cache行的修改位(脏位,Dirty Bit)置为1,并在该cache块被替换时才会将修改写入主存●若采用写穿(Write-Through, WT)策略(又称直写法),当写命中时,同时修改cache和主存中的同一数据块多CPU/多核系统下,各CPU都有自己的cache,因此这种情况下写穿法无法保证其他CPU中cache的同步更新●cache 相关术语●数据命中(Hit)CPU访问的数据在cache中找到●命中访问时间 tc命中时数据访问所需的时间,包括查找时间和cache访问时间●数据缺失(Miss)CPU访问的数据不能在cache中找到●缺失补偿(Miss Penalty)数据缺失时访问所需时间,包括查找时间、主存访问时间和cache访问时间,其中主存访问时间占大头,通常用tm表示●数据块(Block)cache和主存都被分为若干固定大小的数据块(cache和主存中块大小相同),每个块包含若干字(节),以块为单位交换数据,这也是一种预读策略●进行分块后,主存和cache地址都可以用块地址(序号):块内偏移地址(偏移字节数)的二维地址空间进行描述●命中率(Hit Ratio)h=Nc/(Nc+Nm)某程序运行期间,命中cache的次数比上访问主存的总次数●缺失率(Miss Ratio)1-命中率●平均访问时间 ta = htc + (1-h)tm●访问效率 e = tc/ta●各种因素间的关系●cache 命中率与容量的关系●块容量与命中率的关系空间局部性越好,时间局部性越差●地址映射方式与命中率的关系●cache 行/槽(Line/Slot)将一个cache数据块和相关的标记标志信息合称一个cache行●cache 关键技术●数据查找(Data Identification)如何快速判断数据是否在cache中●全相联映射中使用相联存储器(Content Addressable Memory, CAM)实现快速查找●CAM是一种直接按内容进行访问(输入的不是地址而是要查询的key)的存储器,用于存放查找表,其基本存储数据单元是键值对●硬件成本高(比较器多),通常用于存放查找表/全相联cache●存储容量=查找表容量=表项数*表项大小cache中用于存放块表,虚拟存储器中用于存放段/页表●CPU片内缓存●查找表与缓存副本一体●存放cache行(有效位+主存块序号+数据块副本)●片外缓存/片内查找表●查找表与缓存副本分离●只存放查找信息(有效位+主存块序号+cache块地址)●读逻辑实现●Valid位用于判定当前键值对是否有效(若无效直接不输出)●所有存储单元中的Key要与输入的关键字进行并发比较,有n个存储单元就有n个比较器●所有比较器的输出结果取或,输出为Hit结果●将每个比较器的输出结果输入三态门控制端,若Hit成功则输出对应Value●地址映射(Address Mapping)如何将主存数据放入cache行中●全相联(Full Associative Mapping)映射全相联模式下,主存中每一个数据块都可以放入cache中的任意数据块(任意行)中●新的主存数据块可以载入cache中的任意一个空行,只有cache满时才会进行替换,因此利用率最高,但需要CAM提供的快速查找功能,查找成本较高●优点:映射灵活,cache利用率高,冲突率低,命中率高●缺点:淘汰算法复杂,查找成本高●主存地址分为主存块地址/序号(tag,长度为s)和块内偏移量(offset,长度为w)两部分●cache块(数据块副本)应与主存中数据块大小相同,即容纳偏移量最大值数量的字节数,因此cache块大小为2^w字节●主存容量对应为2^(s+w)字节●所有cache行的实际容量为 n*(1+s+8*2^w)位●n:cache行数●1:每行有效位●s:每行tag部分(主存块序号)●8*2^w:数据块容量从字节转换成位●逻辑硬件实现假设cache块大小为4W(=4*16Bit),共8行主存按字访问,地址长度为9位,采用全相联映射●块大小为4W,且读取单位是字(W),则偏移地址为0~4,则w=2●tag部分由于地址总长度为9位,则s=9-2=7●其后过程与CAM类似,只是需要使用偏移地址选择最后的输出●查找表和数据块副本分开存放,用相联存储器连接●直接相联(Direct Mapping)直接相联模式下,每一个(类)主存块地址(序号)只能映射到cache中固定的行●映射规则:cache块号 i = 主存块号 j mod (cache行数 n)上述规则等价于将主存按cache总大小进行分区,每个分区中包含的数据块数量与cache行数相同,每个分区中的数据块只能填入对应序号的cache行中●主存地址可以细分为区地址(tag)、区内行索引(index)和偏移地址(offset)三部分●tag字段表示主存中分区的序号(查找标记)●index字段表示当前分区下cache行的序号●offset与全关联相同●cache的实际容量为n*(1+s-r+8*2^w)位●s是块地址总长度,r是行索引长度,s-r是区地址长度(直接相连cache只用存储区地址用于查询)●硬件逻辑实现●由于主存块只能放置在index对应的cache行中,因此不需要全相联查找,也不需要将查找表放在CAM中,直接通过index就可以访问对应数据●结构中没有相联存储器,所有cache行共用一个比较器●查找表和数据副本一起存放,无需相联存储器●优点是映射速度快,查找成本低,替换算法简单;缺点是命中率低,易冲突导致cache利用率低●组相联(Set Associative Mapping)组相联映射是将直接相联映射和全相联映射两种方式的折中,既能提高命中率,又能降低查找硬件的开销●k-路组相联将cache分成固定大小的组,每组有k行●主存数据块首先采用直接相联映射的方式定位到cache中固定的组,映射规则为cache组号 = 主存块号 mod (cache组数)等价于把k组cache块看成一个数据块进行映射,其中具体某一块的映射则由完全映射决定●然后采用全相联映射到组内任何一个cache行●主存地址可以分为标记字段(tag),组索引(index)和块内偏移(offset)三部分●tag字段与直接相联中分区序号类似●index字段是cache组的索引,即映射规则中得到的余数●cache的实际容量为 kn*(1+s-d+8*2^w)位●k为k路中的每组行数●n为cache组数●s-d是标记位长度●逻辑硬件实现●直接相联映射让数据查找的范围快速缩小到一个cache组,大大减少了查找范围,降低了硬件开销;组内采取全相联映射规则,避免了高冲突率,提高了cache的命中率●k路组相联只需要k个并发比较器●大容量cache可采用直接映射方式(cache够大可以提升命中率),小容量cache一般采用全相联映射或组相联映射●替换策略(Placement Policy)cache满后如何处理●先进先出法(FIFO)●最近不经常使用方法(LFU,Least Frequent Used)每行设置一个计数器,统计自处理器启动以来每个cache行的调用次数,当需要替换时替换掉调用次数最少的行。

考研复试计算机组成原理重点笔记

指令系统指令其实就是一组有特殊意义的二进制数,指示计算机执行某种操作的命令,也叫机器字或指令字,是计算机运行的最小功能单位。

一台计算机的所有指令的集合构成该机的指令系统,也称为指令集。

指令系统是计算机的主要属性,位于硬件和软件的交界面上。

机器指令机器指令是CPU能直接识别并执行的指令。

相联存储器相联存储器是一种按内容访问的存储器。

工作原理:把数据和数据的某一部分作为关键字,按顺序写入信息,读出时并行地将该关键字与存储器中的每一个单元进行比较,找出存储器中所有与关键字相同的数据字,特别适合信息的检索和更新。

Cache由于CPU的速度比内存和硬盘的速度要快得多,所以在存取数据时会使CPU等待,影响计算机的速度。

SRAM的存取速度比其它内存和硬盘都要快,所以它被用作电脑的高速缓存(Cache)RAM随机存储器(Random Access Memory)表示既可以从中读取数据,也可以写入数据。

当机器电源关闭时,存于其中的数据就会丢失。

我们通常购买或升级的内存条就是用作电脑的内存,内存条(SIMM)就是将RAM集成块集中在一起的一小块电路板,它插在计算机中的内存插槽上,以减少RAM集成块占用的空间。

高级调度先来先服务和短作业(进程)优先调度算法;高优先权调度算法和高响应比优先调度算法简述冯诺依曼体系结构计算机的工作原理1.存储器用来存放数据和程序2.运算器主要运行算数运算和逻辑运算,并将中间结果暂存到运算器中3.控制器主要用来控制和指挥程序和数据的输入运行,以及处理运算结果4.输入设备用来将人们熟悉的信息形式转换为机器能够识别的信息形式,常见的有键盘,鼠标等5.输出设备可以将机器运算结果转换为人们熟悉的信息形式,如打印机输出,显示器输出等计算机采用流水线目的是什么?它的作用和cache的作用一样,都是为了充分利用计算资源,即充分利用cpu,防止其闲置。

简述中断和DMA 的区别1、中断方式是在数据缓冲寄存区满后,发中断请求,CPU进行中断处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微机原理用书<微型计算机原理及接口技术>第二版裘雪红李伯成西电出版社专题一一微机的组成P15 图1.21 cpu的特点: 8086 (重点)1> cpu内有6直接指令预取队列BIU (总线接口单元)读内存存入预取队列EU (指令执行单元)读预取队列执行2> 内部有四个段寄存器(20位---1M)3> 多种模式(最大,最小) 8086可接入另外的cpu二8086的引线最小模式P19 图2.1 (重点这个必须熟悉每个引脚什么作用必须知道)三内部寄存器(重点必须记住其中一些指令才能读懂程序)P26 图2.4四内存组织安字节编址没一地址存放1字节程序地址=ES*16+IP堆栈地址=SS*16+SP数据地址=DS/ES*16+EA五时序P31 图2.8六总线形成(知道最小模式)P33 图2.11专题二寻址方式和指令系统一寻址方式1 决定操作数地址(知道)1> 立即MOV AL, 05H2> 直接MOV AL, [2000H]MOV [2000H],AL3> 寄存器MOV AX,BXMOV DS,DX4> 寄存器间接(稍注意)MOV BX,1000HMOV DS,BXMOV SI,2000HMOV AL,[SI]5> 寄存器相对MOV AL,[SI+3]6> 基址,变址偏移地址=基址地址(BX,BP)+变址地址(SI,OI) MOV AL,[SI+BX]7> 基址,变址,相对MOV AX,-1[SI+BX]MOV [BX],BX8> 隐含寻址二指令系统(重点编程序读程序)1 传送MOV AL,RXYTMOV AX,SEG RXYT(把RXYT所在段地址给AX)MOV SI,OFFSET RXYT(偏移地址给SI)MOV DS,AXMOV AL,[SI]堆栈地址POSH AX MOV AX,1000HPOSH BX MOV SS,AXMOV SP,2000HPOSH AX 1> SP-1→SP2> AH→MSP3> SP-1→SP4> AL→SPPOP BX2 算术要背的: ADD ADC SUB SBB MUL DIV知道的: CMP INC DEC DAA DAS BCD3 逻辑移位循环指令(以下写出来的必须会用!)1> AND OR XOR NOT TEST NEGMOV BL,45HMOV AL,0FHAND BL,AC2> SAL SHL(逻辑左移相当于乘2)MOV DX,0400HSHL DX,1 (0800)SHL DX,1 (1600)若定义MOV CL,4 (移位次数一定放在CL)则SHL DX,CL (移位4次)SHR(逻辑右移)MOV DL,40HSHR DL,1 (20)SHR DL,1 (10H)SHR DL,1 (08H)SAR(算术右移)MOV DL,0C0H (11000000 -64)SAR DL, 1 (11100000 -32)3> 循环(大概知道)ROL ROR RCL RCR4 串操作指令(不考!)5 程序控制指令(重点)JMP(无条件转移不必深究只要知道转移到哪就行)无符号数JC JNC JP/JPE JNP/JPO JA.JNBE JAE.TMB JB.TNAE JBE.JNA(不知道问题不大)有符号数JS JNS JO JNO JG.JNLE JGE.JNL JL.JNGE JLE.JNG(不知道问题不大)常用的有JX/TE JNZ重点LOOP CALL(子程序调用) RET(子程序返回)6 cpu控制指令(不太重要)CLC STC SLI STI大概知道HLT WAIT NOP就行了7 I/O(重要) 只有两条IN AL,75H (直接寻址接口只有一个字节就是8位从00H到FFH 一用256个)OUT 3EH,AL (把AL输出到3E接口)常用寄存器间接寻址OUT DX,AL注意读入和把一个写出都要走AL指令到此位置汇编不做要求统计里面从80000H以下100个地址里有多少个负数START: MOV DX,80000HMOV DS,DXMOV SI,0000HMOV BX,0(计数器)GOON: MOV AL,[SI]AND AL,80H(用”与”操作看最高位)JZ NEXTADD BL,1NEXT: INC SIINC BHCNP BH,100JNZ GOONHLT(停机指令)从48000H开始有150个ASCII码分别取出ASCII码加入偶校验再放回第一位为检验位START: MOV BX,40000HMOV DS,BXMOV SI,8000HMOV CL,150GOON: MOV AL,[SI]AND AL,AL(或AND AL.0FFH)JP NEXTADD AL,80HNEXT: MOV [SI].AL(放回)INC SI(地址加一)DEC CLTNZ GOON写出程序要你读START: MOV AL.DA TABMOV CL,4MOV AH,0(AH消0)MOV CH,10DIV CH,(AH除以10,余1)MOV BL,AH(个位数AH放入BL)MOV AH,0DIV CHMOV BH,ALSHL AH,CL(逻辑左移)OR BL,AHMOV RSUT.BXHLT放入RSUT和他的下一个地址里专题三存储器一SRAM1 8088 CPU是八位机2 8086 CPU是十六位机8088系统总线(重点)这里是重中之重大家可以去看看往年的题目几乎都有这样的题但是这里的图我实在是不懂画大家见谅大家要掌握的就是给出地址和作出连接图之间怎么转化大家把树上这部分连接的图好好看看还有就是要能解决不是顺序存储的情况比如32k不顺序(84000H~8BFFH) 注意下38译码器其他的译码器不要求二动态存储器不看只要知道”动态”是什么含义就行三只读存储器(大概了解)EPROM连接大多同SRAM 只有一个线不同编程: 用紫外光擦干净每个单元都是F 或每一位都是高电平即干净编程方: 按标准编程(50正负5ms)EEPROM 引线和SRAM没有区别:在线编程系统运行重即可编程)分为按字节编程(几百到几十毫秒)和页编程(300毫秒)(一定要知道这2个用的时间)专题四I/0技术(没说道的不考)一无条件传送方式大家看看P255 图6.14二查询逐个外设查询CPU效率低P260 图6.18三中断1 P261 图6.202 分类内部中断外部中断3 一般过程1> 请求INTR NMI优先级从高到低: 复位HOLD 内部中断NMI INTA 单步中断STI IRET执行完后步响应中断必须再执行一条指令2> 承认3> 保护4> 中断类型码(向量码)5> 服务6> 返回4 8086P267 图6.245 中断优先级控制6 PIO 8259(可编程中断控制器1> 可工作再8位机和16位机上2> 8259中断优先级控制包括I 一般全嵌套苦丁优先级IR0 IR1 …IR1II 自动循环(刚服务结束的最低)III 一次制定某一个最低屏蔽不考3> 结束: 自动结束命令结束一般命令结束: 结束优先级最高的程序制定命令结束: 用在特殊屏蔽里不考8259级联: 最多可级联8个从属控制器所以最大有64个中断请求输入端四DMA(重中之重)1 引线P285 图6.422 特点1> M→I/O I/0→M (这里4通道均可)M→M(这里只能是CH0,CH1)2> 优先级固定0,1,2,3自动循环:刚结束最低下一个最高3> 级联4> DMA传送一字节需要4个体压缩的只要2个体2T 系统时钟5M →200ns 400ns→2.5MB/s3 描述传送过程(重重重)注意这么一个细节: DMAC是16位的如果而总线是20位的所以需要一个锁存器锁存4位地址.专题五芯片及应用一简单应用二可编程并行接口PPI 82551 引线P3002 工作方式(知道方式0就足够)输出有锁存输入(如外设输入)不能锁存所以外设的信号要一直加在输入端A B口没有单根定义功能C口可以四根四根定义方式1 2 不要求P309 图7.15START: MOV DX,8001HMOV AL,00HOUT DX,ALCALL TIMEISMOV AL,71HOUT DX,ALCALL TIMEISTMP START这个程序是一个八字LED灯显示F 亮一秒暗一秒无限循环三8253 可编程定时器1 引线P313 图7.192 工作方式P315开始所以方式0,1,2,3,4,5 记住工作方式特点方式2 ,3 OUT能源源不断出现周期性波形四串行接口(只要知道收发是怎么作的)在课的最后老李非常突兀的说了下面3个点意思是什么不言而喻了吧1 采样定理采样频率位信号最高频率两倍以上熵没有损失(就是说可以无损还原回来)比如一幸好是10KHz的那么AD 转换器速度转换一个要sμ100≤2 光电隔离器件隔离的目的:消除打功率外设和微机共地的影响(消除地的干扰)3 DMA三种传送类型M→I/O 内存到接口I/O→M 接口到内存M→M 内存到内存Made by 一砣煤里面没有画图但是重点的地方给大家说出来了可以说是老李课上的板书除了图都有了这样大家也不用拿着四百多页的书没有头绪的下手了有很多不考的地方老李第一节课就说了"我说到的不一定考到但是我没说道的一定不考" 这是原话。