FPGA与单片机实现数据RS232串口通信的设计

基于fpga的串口设计及实现

基于fpga的串口设计及实现

基于FPGA的串口设计及实现是一个涉及数字电路设计和通信协

议的复杂课题。

首先,让我们从串口通信的基本原理开始。

串口通信是一种通过串行传输数据的通信方式,它使用一个或

多个数据线(通常是一对)来逐位地传输数据。

常见的串口通信标

准包括RS-232、RS-485、UART等。

在FPGA中实现串口通信,需要

考虑以下几个方面:

1. 串口通信协议选择,根据具体的应用场景和需求,选择合适

的串口通信协议。

例如,UART是一种常见的串口通信协议,它使用

起始位、数据位、校验位和停止位来传输数据。

2. 串口通信接口设计,在FPGA中设计串口通信接口,需要考

虑数据的发送和接收,时钟信号的同步等问题。

通常需要使用FPGA

的IO资源来实现串口通信接口。

3. 串口通信协议的实现,在FPGA中实现选择的串口通信协议,包括数据的发送和接收、时序控制、校验等功能。

这通常需要使用Verilog或VHDL等硬件描述语言进行开发。

4. 硬件调试和验证,设计完成后,需要进行硬件调试和验证,包括时序分析、波形仿真等工作,确保串口通信的稳定和可靠。

在实际的FPGA串口设计中,还需要考虑时钟频率、数据传输速率、数据格式、数据校验、中断处理等问题。

此外,还需要考虑FPGA与外部设备的接口,如与传感器、显示器、存储器等设备的接口设计。

总之,基于FPGA的串口设计及实现涉及到硬件设计、数字电路设计、通信协议等多个方面的知识,需要综合考虑各种因素,进行全面的设计和实现。

最新fpga实现串行接口 rs232资料讲解

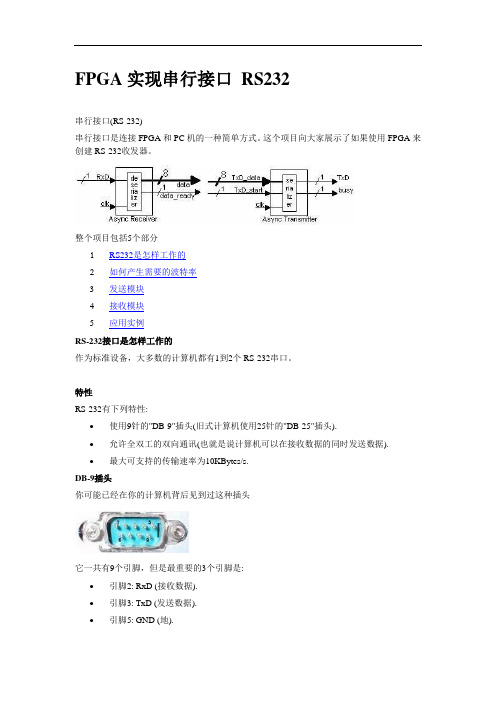

FPGA实现串行接口RS232串行接口(RS-232)串行接口是连接FPGA和PC机的一种简单方式。

这个项目向大家展示了如果使用FPGA来创建RS-232收发器。

整个项目包括5个部分1RS232是怎样工作的2如何产生需要的波特率3发送模块4接收模块5应用实例RS-232接口是怎样工作的作为标准设备,大多数的计算机都有1到2个RS-232串口。

特性RS-232有下列特性:•使用9针的"DB-9"插头(旧式计算机使用25针的"DB-25"插头).•允许全双工的双向通讯(也就是说计算机可以在接收数据的同时发送数据).•最大可支持的传输速率为10KBytes/s.DB-9插头你可能已经在你的计算机背后见到过这种插头它一共有9个引脚,但是最重要的3个引脚是:•引脚2: RxD (接收数据).•引脚3: TxD (发送数据).•引脚5: GND (地).仅使用3跟电缆,你就可以发送和接收数据.串行通讯数据以每次一位的方式传输;每条线用来传输一个方向的数据。

由于计算机通常至少需要若干位数据,因此数据在发送之前先“串行化”。

通常是以8位数据为1组的。

先发送最低有效位,最后发送最高有效位。

异步通讯RS-232使用异步通讯协议。

也就是说数据的传输没有时钟信号。

接收端必须有某种方式,使之与接收数据同步。

对于RS-232来说,是这样处理的:6串行线缆的两端事先约定好串行传输的参数(传输速度、传输格式等)7当没有数据传输的时候,发送端向数据线上发送"1"8每传输一个字节之前,发送端先发送一个"0"来表示传输已经开始。

这样接收端便可以知道有数据到来了。

9开始传输后,数据以约定的速度和格式传输,所以接收端可以与之同步10每次传输完成一个字节之后,都在其后发送一个停止位("1")让我们来看看0x55是如何传输的:0x55的二进制表示为:01010101。

基于单片机RS232串行通讯的设计

^ , 一

为电可擦除闪速存储器(no h) , 可多次修改程序, 甚至可以在线编程。 I 1 8 P C 6F 7X 片内数据存储器除 RAM外,还有 6 字节的EEP OM, 4 R 可 以当 作一般的或非易失性的数据存储器使用, 简单方便。它还具有片 内上电复位 , 延时电路、 看门狗电路等。另外, C 6 系列单片机功耗 I P1 极低, 而是 一 因 种非常 适合在各种便携式设备中 使用的高 性价比 的单 片机, 并已经得到 r 越来越广泛的应用。

其次分析脉冲整流滤波电路。 一般开关变压器都有二个以上的次

级绕阴, 分别输出不同的直流电 不可能每一个脉冲整流滤波电路 压,

都损坏。 用行频检波器或万用表交流档测一下开关变压器次级翰出

分析启动电路。 启动电路是否正常工作可以这样来判别:开机前. 用万用表接在启动电路电压输出端, 然后开机, 监测开机瞬间电压。 如 果表针能摆动.说明 启动电 作正常。 路工 启动电 路一般来 较简单。 说比 通常只有三个元件:两个电阻和一个电容构成。一般来说电阻不易变 质, 电容易变质。电容变质后, 对开关管基极提供的偏流会变化, 太大 或太小都不能使开关管振荡, 故启动电路故障一般在于电容变质。另 外, 有的彩电为了减少开机时电流对开关管的冲击, 设置了软启动电

端, 如有电压, 再断开负载, 接上假负载, 测一下脉冲整流电路输出端 有尤直流电压, 使可判断该电路有无故障。 这部分电路十分简单, 可对 所有元件逐一检查。

1 2 启动 电路

端对地短路, 烧毁保险丝。 特别注意的是, 其中 往往开关管的 管壳与散 热处之间绝缘不良, 这也是造成烧保险丝故障的原因之一。

绷写

力 习 C

(2)半双工 通信:也称双向交替通信, 通 即 信的双方都可以发送信 息, 但不能同时发送或同时接收, 这种通信往往是一方发送另一方接

基于FPGA串口通信的电路和程序设计

中北大学毕业设计中期总结学生姓名:袁财源学号:1206044145 学院:仪器科学与技术专业:电子科学与技术设计题目:基于FPGA串口通信的电路和程序设计指导教师: 郭涛2015 年1月5日毕业设计中期总结MAX232芯片结构第一部分是电荷泵电路。

由1、2、3、4、5、6脚和4只电容构成。

功能是产生+12v 和-12v两个电源,提供给RS-232串口电平的需要。

第二部分是数据转换通道。

由7、8、9、10、11、12、13、14脚构成两个数据通道。

其中13脚(R1IN)、12脚(R1OUT)、11脚(T1IN)、14脚(T1OUT)为第一数据通道。

8脚(R2IN)、9脚(R2OUT)、10脚(T2IN)、7脚(T2OUT)为第二数据通道。

TTL/CMOS数据从11引脚(T1IN)、10引脚(T2IN)输入转换成RS-232数据从14脚(T1OUT)、7脚(T2OUT)送到电脑DB9插头;DB9插头的RS-232数据从13引脚(R1IN)、8引脚(R2IN)输入转换成TTL/CMOS数据后从12引脚(R1OUT)、9引脚(R2OUT)输出。

第三部分是供电。

15脚GND、16脚VCC(+5v)。

RS232 (DB9)引脚定义1 :DCD :载波检测。

主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音,处于在线状态。

2 :RXD:此引脚用于接收外部设备送来的数据;在你使用Modem时,你会发现RXD指示灯在闪烁,说明RXD引脚上有数据进入。

3 :TXD:此引脚将计算机的数据发送给外部设备;在你使用Modem时,你会发现TXD指示灯在闪烁,说明计算机正在通过TXD引脚发送数据。

4 :DTR:数据终端就绪;当此引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好。

5 :GND:信号地;此位不做过多解释。

6 :DSR:数据设备就绪;此引脚高电平时,通知计算机Modem已经准备好,可以进行数据通讯了。

基于FPGA的RS232设计

FPGA 串口RS232的设计,该模块RS232的波特率为9600,其模块结构框图如下图示:

设计模块功能描述:

Testbench(测试模块):模拟PC机串口信号发送和接受设备,首先向RS232接收端发送串口数据信息,然后通过RS232接收端来接收RS232发送端的数据信息。

RS232_rx(串口接收模块):通过接受来自testbench的串行数据信息,并存入到FIFO中。

RS232_tx(串口发送模块):通过读取FIFO的有效数据标志位wrusedw,来判断FIFO中是否还有数据需要发送。

如有,则继续读取FIFO中的数据信息,并发送出去。

RS232_clk(串口时钟):提供RS232需要时钟,规定RS232通信波特率。

FIFO(ip核模块):调用的为ALTERA的ip核模块,主要用于RS232接收,发送数据的存储和缓冲作用。

以下为模块设计代码:

Testbench(测试模块) 1

TOP顶层设计模块1

RS232_clk(时钟模块) 1

RS232_rx(接收模块) 1

RS232_tx(发送模块) 1。

FPGA和单片机串行通信接口的实现

FPGA和单片机串行通信接口的实现FPGA(Field-Programmable Gate Array)和单片机(Microcontroller)是两种常用的数字电子设备,它们在串行通信接口方面有不同的实现方式。

首先,我们需要了解串行通信是一种将数据以位的形式逐个传输的通信方式。

常见的串行通信协议包括UART(Universal Asynchronous Receiver/Transmitter)、SPI(Serial Peripheral Interface)和I2C (Inter-Integrated Circuit)等。

对于FPGA和单片机之间的串行通信,我们可以基于以下几种方式进行实现:1. UART:UART是一种常见的串行通信协议,可以实现全双工的通信。

在FPGA和单片机之间建立UART通信,需要在FPGA中实现UART模块,并将其与单片机的UART接口连接。

在FPGA中,我们可以使用硬件语言(如Verilog或VHDL)来实现UART模块,该模块负责将FPGA内部的数据通过UART协议进行封装和解封装。

单片机与FPGA之间通过TX(发送)和RX (接收)引脚建立连接。

单片机可以通过串口发送数据给FPGA,FPGA接收到数据后进行处理,然后再通过串口将处理后的数据发送给单片机。

2.SPI:SPI是一种用于片上外设之间通信的串行通信协议,常用于FPGA与外部设备(例如传感器、显示器等)之间的通信。

在FPGA和单片机之间建立SPI通信,需要在FPGA中实现SPI控制器,并将其与单片机的SPI接口连接。

FPGA通过把数据写入SPI发送缓冲区或从SPI接收缓冲区读取数据来实现与单片机的通信。

单片机通过控制SPI接口的时钟、数据和使能信号来与FPGA进行数据传输。

3.I2C:I2C是一种双线制串行总线,常用于连接多个设备的系统,例如FPGA、单片机和其他外部设备之间的通信。

在FPGA和单片机之间建立I2C通信,需要在FPGA中实现I2C控制器,并将其与单片机的I2C接口连接。

基于FPGA的RS232通信电路设计

课题概述

课题研究的主要内容 相关技术及软件及软件平台

UART设计原理

UART各模块

波特率发生模块 接收模块 发送模块

波特率发生模块仿真

为仿真方便,把分频系数设置为10

接收模块仿真

接收数据为10000101 无校验位 接收正确

接收模块仿真

发送数据为10000101 接收错误

偶校验

发送模块仿真

发送数据为10110010 发送正确

无校验位

下载验证

实验板上的收发指示灯均闪烁

结论

仿真和验证结果均表明,该UART控制器 功能符合设计要求。

致谢

谢谢各位老师

请批评指正

一种利用FPGA实现串口通信的设计

• 124•串口通信具有技术成熟、应用简单的特点,在工业控制、工业测量等领域大范围应用,但传统的计算机+专业UART 接口芯片的架构,在多串口的系统设计中存在集成度不高、设计不灵活的缺陷。

本文介绍了一种基于FPGA 实现串口数据接收的设计方案,经测试,运行稳定,具备推广应用价值。

工业控制、工业测量等系统经常需要接入数量众多的各种外设数据,数据率不高的外设一般都采用异步串口对外输出数据,具有技术成熟、应用简单的特点,且该技术形成标准较早,应用市场存在大量的配置异步串口的设备型号,采用异步串口,便于外设的选型。

但传统的计算机+专业UART 接口芯片的架构,在接入外设数量较多的情况下,系统设计就变得复杂,调试工作量增大。

随着可编程逻辑器件的发展,嵌入式电子系统越来越多地采用FPGA 进行数字逻辑电路设计,具有设计灵活、易于维护、研制周期短、集成度高的优点。

本文介绍了一种利用FPGA 实现异步串口的设计,利用FPGA 器件I/O 口资源丰富的特点,可集成众多具备异步串口通信接口的外设进入同一系统。

多路串口数据在FPGA 内部分别提取、恢复出以字节为单位的数据,在FPGA 内部进行后续处理或进行数据打包,通过计算机总线(PCI 总线或Local Bus总线等)送给主控或处理计算机。

图1 多串口系统示意图下文以图1中的一路异步串口为例,介绍利用FPGA 接收处理串口数据的设计。

1 硬件设计如图1所示,硬件电路设计涉及电平转换电路和FPGA 电路。

串口的信号电平有RS232和RS422两种,其中RS232又分9V 电平和12V 电平。

鉴于RS422电平信号在抗干扰能力上的优势,在工业领域,异步串口多采用RS422电平。

考虑到接口两端电路的安全性,电平转换电路采用带隔离的设计,工程中采用AD 公司的ADM2582E 芯片实现RS422电平到TTL 电平的转换,该芯片内部集成有收、发电路各1个通道,特点是RS422端的电源、信号、地与TTL 端的电源、信号、地是隔离的,芯片采用单电源供电,内部集成隔离式DC-DC 电源。

基于FPGA的串口通讯电路设计毕业论文

本科学生毕业论文论文题目:学院: 年级:专业:姓名: 学号: 指导教师:基于FPGA勺串口通信电路设计集成电路设计与集成系统i串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持RS-232接口(又称EIA RS-232-C)的通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART),本文设计了一个串口数据采集和处理程序,详细介绍了用Verilog HDL硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用Quartus II软件进行仿真并给出结果,分别验证各个模块的正确性。

本设计还使用基于ALTERA 公司的Cyclone II EP2C5T144芯片的FPGA开发板,在FPGA开发板上实现和PC 通过串口调试软件完成双向通信,不仅要求将开发板的数据显示在PC的串口调试助手软件上,还要求用PC发送数据的ASCII码来驱动电路的8个LED 灯,验证用FPGA实现串行通信的可行性。

关键词串行通信;RS-232; UART ;Verilog HDL ;FPGAAbstractSerial com muni cati on in terface is a widely used com muni cati on in terface. At prese nt, most of processor in tegrated RS-232(EIA RS-232-C) in terface to support UART (Uni versal Asynchronous Receiver/Tra nsmitter) com muni cati on, This thesis desig n a data acquisiti on and treatme nt program. Besides that, the thesis in troduced Baud Rate Generator module、Receiver module、Send module based on Ianguage Verilog HDL and give the results by simulate in Quartus II software. This desig n also uses EP2C5T144 FPGA chip to achieve the two-way com muni cati on by simulate with Quartus II and PC through the serial port debuggi ng software. Not only requires the developme nt board's data displayed in the PC's serial port debugg ing software, also ask ASCII data sent by PC Code to drive eight LED lights, mean while verified the serial com muni cati on with FPGA.Key wordsSerial commu ni catio n; RS-232; UART; Verilog HDL; FPGA摘要 (I)Abstract (II)第1章语言和工具 (2)1.1 Verilog HDL 语言概述 (2)1.2 FPGA 概述 (4)1.3 Quartus II 软件介绍 (8)1.4 FPGA开发板介绍 (9)1.5本章小结 (12)第2章串口通信协议简介 (13)2.1串口通信接口 (13)2.2 RS232通信协议 (13)2.3串口通信时序分析 (15)2.4本章小结 (16)第3章串口通信的VerilogHDL实现 (17)3.1设计功能说明 (17)3.2波特率发生器模块的VerilogHDL实现 (17)3.3发送模块的Verilog HDL实现 (19)3.4接收模块的Verilog HDL 实现 (25)3.5本章小结 (31)第4章串口通信的硬件调试 (32)4.1板级调试说明 (32)4.2下载配置FPGA (33)4.3配置串口调试软件 (35)4.4调试结果 (35)4.5本章小结 (38)结论 (39)参考文献.......................................................... 错误!未定义书签。

基于FPGA的RS-232通信协议接口设计

0 引言RS-232接口是1970年由美国电子工业协会(EIA)联合贝尔系统、调制解调器厂家及计算机终端生产厂家共同制定的用于串行通信的标准[1]。

常见的RS-232串口有DB25和DB9 2种,接口定义如图1所示。

RS-232通信协议因其低成本和高可靠性而被广泛应用,加上其占用的I/O 口数量少,许多以嵌入式微处理器为核心的控制系统中常常采用该技术[2]。

工业控制的RS-232口一般只使用RXD、TXD、GND 3条线,使用简单方便。

FPGA 即现场可编程门阵列,是在PAL、GAL、CPLD 等可编程器件的基础上发展而来,作为专用集成电路领域中的一种半定制电路,它既解决了定制电路生成周期长且内部电路不能更改的不足,又克服了原有的可编程器件门电路有限的缺点[3]。

该文的逻辑设计是基于Altera 公司的Cyclone V 系列FPGA,型号为DE10-Nano,开发板上同时集成了Cortex-A9 ARM 处理器,提高了设计的灵活性。

1 RS-232协议介绍RS-232电平是负逻辑,即逻辑‘1’是-15V~ -5V,逻辑‘0’是+5 V~+15 V,与TTL 电平相反,使用时需要注意。

RS-232为串行异步通信,每一数据帧由起始位、数据位、奇偶校验位(可省略)、停止位和线路空闲位组成[4],如图2所示。

一般情况下,起始位为1位,数据位为5、6、7或8位,奇偶校验位为1位,停止位为1、1.5或2位。

在无数据传送时,传送线为逻辑‘1’,处于空闲状态,当检测到低电平后,为数据传输的“起始位”,之后开始传送数据位,低位在前,高位在后,发完数据位后,根据所发数据发送奇校验位或偶校验位,最后以一位高电平作为停止位结束该次数据传送[5]。

传送的速率一般为9 600 bps 或115 200 bps 等。

该文在RS-232串口通信协议的基础上,利用FPGA 对该协议进行模拟仿真,进行数据的接收与发送,并利用串口调试助手进行在线测试。

基于FPGA的RS-232串口通信控制器设计毕业设计

基于FPGA的RS-232串口通信控制器设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日指导教师评阅书评阅教师评阅书教研室(或答辩小组)及教学系意见摘要串口是可以在使用一根线发送数据的同时用另一根线接收数据。

串口通信协议也可以用于获取远程采集设备的数据。

通过RS-232以实现计算机之间、计算机与设备之间相互通信,目前仍是通讯领域广泛使用的方法之一。

基于FPGA的串口通讯设计

基于FPGA的串口通讯设计随着科技的不断发展,现场可编程门阵列(FPGA)因其高度的灵活性和强大的数据处理能力,日益成为通讯系统设计的重要选择。

串口通讯作为一种常见的通讯方式,广泛应用于各种设备之间的数据传输。

本文将探讨如何将FPGA应用于串口通讯设计,以期提高通讯效率和稳定性。

在本文中,我们将首先确定合适的主控芯片,然后设计基于FPGA的串口通讯电路,并对FPGA资源进行合理配置。

接下来,我们将介绍如何实现串口通讯算法,以提高通讯效率和稳定性。

在基于FPGA的串口通讯设计中,我们需要考虑以下电路元件的选择和设计:电阻分压器:用于降低输入信号的电压,以适应FPGA的输入范围。

晶体振荡器:为FPGA提供时钟信号,确保设备的同步运行。

电源转换器:将外部电源转换为FPGA所需的电压和电流范围。

我们还需要根据实际需求,设计串口通讯电路的功能模块,如数据发送、数据接收等。

在基于FPGA的串口通讯设计中,我们需要根据实际需求,合理分配FPGA内部资源。

具体来说,我们需要:锁相环(PLL):用于倍频和分频时钟信号,实现高速数据传输。

信号输出:驱动外部设备,如LED、LCD等。

在实现串口通讯算法时,我们首先需要定义通讯协议,包括数据格式、波特率、校验位等。

然后,我们可以使用流程图等方式,明确算法实现步骤。

例如:实验验证为了验证基于FPGA的串口通讯设计的可行性和可靠性,我们搭建了实验环境,并进行了以下测试:功能测试:检测电路各功能模块是否正常工作,如数据发送、数据接收等。

性能测试:测试通讯速率、稳定性、抗干扰能力等指标。

协议兼容性测试:检测算法是否兼容不同串口通讯协议。

长时间运行测试:检测系统在长时间运行下的稳定性和可靠性。

通过以上实验测试,我们发现基于FPGA的串口通讯设计在通讯速率、稳定性、抗干扰能力等方面均具有显著优势,能满足多种应用场景的需求。

同时,该设计具有较好的协议兼容性和可扩展性,能根据不同需求进行定制化扩展。

单片机与FPGA的串口通信

你应该是想实现单片机与FPGA的串口通信。

以下内容可能会对你有所帮助:根据RS232 异步串行通信来的帧格式,在FPGA发送模块中采用的每一帧格式为:1位开始位+8位数据位+1位奇校验位+1位停止位,波特率为2400。

本系统设计的是将一个16位的数据封装成高位帧和低位帧两个帧进行发送,先发送低位帧,再发送高位帧,在传输数据时,加上文件头和数据长度,文件头用555555来表示,只有单片机收到555555时,才将下面传输的数据长度和数据位进行接收,并进行奇校验位的检验,正确就对收到的数据进行存储处理功能,数据长度可以根据需要任意改变。

由设置的波特率可以算出分频系数,具体算法为分频系数X=CLK/(BOUND*2)。

可由此式算出所需的任意波特率。

下面是实现上述功能的VHDL源程序。

Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity atel2_bin isport( txclk: in std_logic; --2400Hz的波特率时钟reset: in std_logic; --复位信号din: in std_logic_vector(15 downto 0); --发送的数据start: in std_logic; --允许传输信号sout: out std_logic --串行输出端口);end atel2_bin;architecture behav of atel2_bin issignal thr,len: std_logic_vector(15 downto 0);signal txcnt_r: std_logic_vector(2 downto 0);signal sout1: std_logic;signal cou: integer:=0;signal oddb:std_logic;type s is(start1,start2,shift1,shift2,odd1,odd2,stop1,stop2);signal state:s:=start1;beginprocess(txclk)beginif rising_edge(txclk) thenif cou<3 then thr<=0000000001010101; --发送的文件头elsif cou=3 thenthr<=0000000000000010; --发送的文件长度elsif (cou>3 and state=stop2) then thr<=din;--发送的数据end if;end if;end process;process(reset,txclk)variable tsr,tsr1,oddb1,oddb2: std_logic_vector(7 downto 0);beginif reset=1 thentxcnt_r<=(others=>0);sout1<=1;state<=start1;cou<=0;elsif txclkevent and txclk=1 thencase state iswhen start1=>if start=1 thenif cou=3 thenlen<=thr;end if;tsr:=thr(7 downto 0);oddb1:=thr(7 downto 0);sout1<=0; --起始位txcnt_r<=(others=>0);state<=shift1;elsestate<=start1;end if;when shift1=>oddb<=oddb1(7) xor oddb1(6) xor oddb1(5) xor oddb1(4) xor oddb1(3) xor oddb1(2) xor oddb1(1) xor oddb1(0);sout1<=tsr(0); --数据位tsr(6 downto 0):=tsr(7 downto 1);tsr(7):=0;txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd1;cou<=cou+1;end if;when odd1=> --奇校验位if oddb=1 thensout1<=0;state<=stop1;elsesout1<=1;state<=stop1;end if;when stop1=>sout1<=1; --停止位if cou<4 thenstate<=start1;elsestate<=start2;end if;when start2=>tsr1:=thr(15 downto 8);oddb2:=thr(15 downto 8);sout1<=0; --起始位txcnt_r<=(others=>0);state<=shift2;when shift2=>oddb<=oddb2(7) xor oddb2(6) xor oddb2(5) xor oddb2(4) xor oddb2(3) xor oddb2(2) xor oddb2(1) xor oddb2(0);sout1<=tsr1(0);--数据位tsr1(6 downto 0):=tsr1(7 downto 1);tsr1(7):=0;txcnt_r<=txcnt_r+1;if (txcnt_r=7) thenstate<=odd2;end if;when odd2=> --奇校验位if oddb=1 thensout1<=0;state<=stop2;elsesout1<=1;state<=stop2;end if;when stop2=>sout1<=1; --停止位if len=0000000000000000 thenstate<=stop2;elsestate<=start1;len<=len-1;end if;end case;end if;end process;sout<=sout1;end behav;剩下的波形仿真就自己搞定。

RS232接口与单片机串行通信程序设计

RS232接口与单片机串行通信程序设计/zhaojun_xf/blog/static/3005058020087 27457988/2008单片机的串行口是非常有用的,通过他我们可以把单片机系统的数据传回电脑处理或者接受电脑传过来的数据而进行相应的动作,下面我就给大家介绍上一下电脑的RS-232接口与单片机串行通信程序设计方法,上还有很多这样的文章大家去搜索下。

RS-232简介:在串行通讯时,要求通讯双方都采用一个标准接口,使不同的设备可以方便地连接起来进行通讯.RS-232-C接口(又称EIA RS-232-C)是目前最常用的一种串行通讯接口. ("RS-232-C"中的"-C"只不过表示RS-232的版本,所以与"RS-232"简称是一样的)它是在1970年由美国电子工业协会(EIA)联合贝尔系统,调制解调器厂家及计算机终端生产厂家共同制定的用于串行通讯的标准.它的全名是"数据终端设备(DTE)和数据通讯设备(DCE)之间串行二进制数据交换接口技术标准"该标准规定采用一个25个脚的DB-25连接器,对连接器的每个引脚的信号内容加以规定,还对各种信号的电平加以规定.后来IBM的PC机将RS232简化成了DB-9连接器,从而成为事实标准.而工业控制的RS-232口一般只使用RXD,TXD,GND三条线. 下面,让我们使用S51增强型单片机实验板来开发一个简单的串口通信实验程序,这是一个串口通信综合实验,需要全套餐客户的相关配件配合才能完成。

通过该实验程序,我们可以检测实验板串口的状态,接收计算机发送来的数据,然后再发送回计算机,如果程序中发送和接收窗中显示的字符相同,则说明实验板的串口是良好的,能够正常收发数据,另外单片机接收计算机的控制指令,根据控制指令来控制实验板上的继电器动作。

首先让我们来看看我们做的通讯软件的实际效果。

FPGA与单片机实现串行通信

题目名称:FPGA与单片机实现串行通信目录1设计任务及内容 (1)2设计方案 (1)3系统硬件设计 (1)3.1单片机串行通信设计 (2)3.2 FPGA串行通信 (3)4系统软件设计 (5)4.1 FPGA单元设计 (5)4.2串行通信MAX3232 (6)5.系统调试 (10)6课程设计总结 (10)附录: (11)1设计任务及内容要求实现FPGA与单片的串行通信,熟悉单片机和VHDL语言的编写,在设计过程中对单片机与FPGA有进一步理解,能够实现串行通信。

2设计方案整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA 波特率发生控制模块,FPGA总体接口模块以及单片机数据接收模块。

在通信过程中完全遵守RS232协议,并利用VHDL语言实现 FPGA与单片机的串口异步通信电路。

本设计采用ll位帧格式异步通信方式,一位起始位、一位停止位、一位奇偶校验位、8位数据位,基于有限状态机原理进行FPGA设计。

设计方案框图如下:3系统硬件设计3.1单片机串行通信设计单片机与FPGA串行通信可采用单片机的SPI(串行外设接口)方式。

相对于UART,SPI更简单,速度更快。

SPI共四条线。

MOSI(Master Out Slave In).MISO,SCK(Serial Clock),SS(Slave Select)。

图1为SPI T作时序。

当单片机向FPGA 传输命令或数据时,应用SPI的四种模式中的SPIO模式。

当片选SS拉低。

然后在每个时钟(SCK)上升沿送出数据。

将片选信号SS与移位寄存器使能端(En)相接,MOSI与移位寄存器数据输入端(SI)相接,SCK同时为移位寄存器提供时钟信号。

在SS信号为低电平时,移位寄存器开始工作,在每个时钟上升沿将接收到的数据左移一位,等全部接受完毕,将SS置一l”,移位寄存器工作完毕,同时为触发器提供时钟,使移位寄存器接收到的数据并行输出。

当单片机从FPGA读取数据时,向FPGA发送读使能信号RE(可用任意空闲I/0口)。

基于FPGA的RS232接口时序逻辑电路设计与实现

基于FPGA的RS232接口时序逻辑电路设计与实现

电子发烧友网核心提示:RS 232接口是现在最常用的一种通信接口。

随着FPGA技术的高速发展,一些常见的接口电路的时序电路可以通过FPGA实现,通过这种设计可减少电路系统元件的数量,提高系统集成度和可靠性。

详细阐述了如何通过FPGA实现RS 232接口的时序逻辑设计。

RS 232接口是1970年由美国电子工业协会(EIA)联合贝尔系统、调制解调器厂家及计算机终端生产厂家共同制定的用于串行通信的标准。

它的全名是数据终端设备(DTE)和数据通信设备(DCE)之间串行二进制数据交换接口技术标准。

该标准规定采用一个25个脚的DB25连接器,对连接器的每个引脚的信号内容加以规定,还对各种信号的电平加以规定。

随着设备的不断改进,出现了代替DB25的DB9接口,现在都把RS 232接口叫做DB9。

RS 232接口是最常见的一种串行通信接口,普通PC机一般都具有此类接口,其最高通信速率(波特率)为115.2 Kb/s。

采用9 600b/s进行数据传输交换的应用较多。

通过FPGA实现其时序电路,主要完成发送和接收两部分逻辑电路的设计。

1 发送逻辑电路的设计。

RS-232串口通信设计课程设计

《CPLD/FPGA 》课程设计报告题目: RS-232串口通信设计院(系):信息科学与工程学院专业班级:通信工程11 学生姓名:学号:指导教师:2014年06 月 09 日至2014年 6 月 20 日RS-232串口通信设计课程设计任务书目录1. 课程设计的目的 (4)2. 课程设计题目描述和要求 (4)3. 课程设计报告内容 (4)3.1 课题设计方案及基本原理 (4)3.2 软件设计 (7)3.3 问题 (14)4.总结 (15)5.参考资料 (16)附录程序清单 (17)1.课程设计的目的:(1)学习RS-232串口通信数据结构,并编程完成串行数据的接收和显示。

(2)掌握RS-232的工作机制与原理。

(3)熟练掌握Quartus2软件的使用。

(4)了解CPLD/FPGA实验箱。

2.课程设计题目描述和要求:(1)课程设计题目:基于FPGA的串口通信程序设计。

(2)课程设计要求:下述设计内容需由学生个人独立完成:1.理解电路原理图与工作过程;2.掌握RS-232电气特性;3.掌握RS-232通信原理及串口通信数据格式,并编程完成串行数据的接收和显示;4.能正确处理编程与调试过程中所遇到的问题;5. 在FPGA中构造一个异步串行通信控制模块,完成PC机发送的接收,并设计显示模块,完成接收数据的显示(3)要求的设计成果:1.程序结构合理,语言简洁,格式规范,注释详细;2. 掌握RS-232的工作机制与原理;3. 格式为:1位起始位,8位数据位,1位停止位,无奇偶校验位,波特率设定为300Baud。

能与计算机正常通信;4. 按要求完成课程设计报告,格式符合学校规范标准,字数不少于2000字。

3.课程设计报告内容:3.1课程设计方案及基本原理:设计方案:利用实验箱上的MAX232芯片控制通过适当分频(分频的目的是为了达到要求的波特率,控制数据传输速率)的串行输入信号,并将其转换为并行信号并通过实验箱上的数码管的后两位显示从计算机中传输出来的16进制数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA与单片机实现数据RS232串口通信的设计发布时间:2010-9-2 发布人:21世纪电子网摘要:本文针对由FPGA构成的高速数据采集系统数据处理能力弱的问题,提出FPGA与单片机实现数据串行通信的解决方案。

在通信过程中完全遵守RS232协议,具有较强的通用性和推广价值。

1 前言现场可编程逻辑器件(FPGA)在高速采集系统中的应用越来越广,由于FPGA对采集到的数据的处理能力比较差,故需要将其采集到的数据送到其他CPU系统来实现数据的处理功能,这就使FPGA系统与其他CPU系统之间的数据通信提到日程上,得到人们的急切关注。

本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。

整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA 波特率发生控制模块,FPGA总体接口模块以及单片机数据接收模块。

本文着重对FPGA数据发送模块实现进行说明。

2 FPGA数据发送模块的设计根据RS232 异步串行通信来的帧格式,在FPGA发送模块中采用的每一帧格式为:1位开始位 8位数据位 1位奇校验位 1位停止位,波特率为2400。

本系统设计的是将一个16位的数据封装成高位帧和低位帧两个帧进行发送,先发送低位帧,再发送高位帧,在传输数据时,加上文件头和数据长度,文件头用555555来表示,只有单片机收到555555时,才将下面传输的数据长度和数据位进行接收,并进行奇校验位的检验,正确就对收到的数据进行存储处理功能,数据长度可以根据需要任意改变。

由设置的波特率可以算出分频系数,具体算法为分频系数X=CLK/(BOUND*2)。

可由此式算出所需的任意波特率。

下面是实现上述功能的VHDL源程序。

Library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity atel2_bin isport( txclk: in std_logic; --2400Hz的波特率时钟reset: in std_logic; --复位信号din: in std_logic_vector(15 downto 0); --发送的数据start: in std_logic; --允许传输信号sout: out std_logic --串行输出端口);end atel2_bin;architecture behav of atel2_bin issignal thr,len: std_logic_vector(15 downto 0);signal txcnt_r: std_logic_vector(2 downto 0);signal sout1: std_logic;signal cou: integer:=0;signal oddb:std_logic;type s is(start1,start2,shift1,shift2,odd1,odd2,stop1,stop2);signal state:s:=start1;beginprocess(txclk)beginif rising_edge(txclk) thenif cou<3 then thr<="0000000001010101"; --发送的文件头elsif cou=3 thenthr<="0000000000000010"; --发送的文件长度elsif (cou>3 and state=stop2) then thr<=din;--发送的数据end if;end if;end process;process(reset,txclk)variable tsr,tsr1,oddb1,oddb2: std_logic_vector(7 downto 0);beginif reset='1' thentxcnt_r<=(others=>'0');sout1<='1';state<=start1;cou<=0;elsif txclk'event and txclk='1' thencase state iswhen start1=>if start='1' thenif cou=3 thenlen<=thr;end if;tsr:=thr(7 downto 0);oddb1:=thr(7 downto 0);sout1<='0'; --起始位txcnt_r<=(others=>'0');state<=shift1;elsestate<=start1;end if;when shift1=>oddb<=oddb1(7) xor oddb1(6) xor oddb1(5) xor oddb1(4) xor oddb1(3) xor oddb1(2) xor oddb1(1) xor oddb1(0);sout1<=tsr(0); --数据位tsr(6 downto 0):=tsr(7 downto 1);tsr(7):='0';txcnt_r<=txcnt_r 1;if (txcnt_r=7) thenstate<=odd1;cou<=cou 1;end if;when odd1=> --奇校验位if oddb='1' thensout1<='0';state<=stop1;elsesout1<='1';state<=stop1;end if;when stop1=>sout1<='1'; --停止位if cou<4 thenstate<=start1;elsestate<=start2;end if;when start2=>tsr1:=thr(15 downto 8);oddb2:=thr(15 downto 8);sout1<='0'; --起始位txcnt_r<=(others=>'0');state<=shift2;when shift2=>oddb<=oddb2(7) xor oddb2(6) xor oddb2(5) xor oddb2(4) xor oddb2(3) xor oddb2(2) xor oddb2(1) xor oddb2(0);sout1<=tsr1(0);--数据位tsr1(6 downto 0):=tsr1(7 downto 1);tsr1(7):='0';txcnt_r<=txcnt_r 1;if (txcnt_r=7) thenstate<=odd2;end if;when odd2=> --奇校验位if oddb='1' thensout1<='0';state<=stop2;elsesout1<='1';state<=stop2;end if;when stop2=>sout1<='1'; --停止位if len="0000000000000000" thenstate<=stop2;elsestate<=start1;len<=len-1;end if;end case;end if;end process;sout<=sout1;end behav;其中各信号的说明已在程序中标明了。

波形仿真图如图2所示。

图2 FPGA数据发送时序仿真图图中Din写入值为3355H,波特率为2400Hz,Start信号始终置逻辑1,即随时都能发送数据。

Reset信号逻辑1时复位,逻辑0时电路开始工作。

THR是数据寄存器,文件头、数据长度以及数据位都先寄存到THR中,Len是数据长度,TSR是低8位数据帧寄存器,TSR1是高8位数据帧寄存器。

数据长度Len定为02H,发送时先发送低8位55H,后发送高8位33H,一共发送两遍。

发送的数据格式说明:当发送55H时,其二进制为01010101,则发送的数据的二进制数为00101010111(1位开始位 8位数据位 1位奇校验位 1位停止位)。

单片机部分先对FPGA发送过来的文件头进行确认,正确就接收文件,否则放弃接收的数据。

根据FPGA发送模块的协议,对串口控制寄存器SCON和波特率控制寄存器PCON的设置即可实现。

3 总结目前电子产品的开发中经常要综合运用EDA技术、计算机控制技术、数字信号处理技术,那么电路各部分经常需要数据交换。

本文也是基于此给出这方面应用的实例,供开发者交流。