基于FPGA的软核处理器在嵌入式中的运用

基于FPGA的嵌入式系统开发

基于FPGA的嵌入式系统开发的实验报告应福军徐飞Linux操作系统近年来在嵌入式领域中发展很快,由于其强大的性能和开源免费的特点,越来越受到嵌入式系统开发商的青睐,信息家电、网络设备、手持终端等都是嵌入式Linux应用的广大市场。

FPGA生产商Xilinx公司提供了全面的嵌入式处理器解决方案,包括PowerPC、MicroBlaze和PicoBlaze三款RISC结构的处理器核。

其中,MicroBlaze 是32位嵌入式软核处理器解决方案,支持CoreConnect总线的标准外设集合,具有兼容性、可配置性以及重复利用性,能够根据成本和性能要求提供高性价比的处理性能。

支持MicroBlaze处理器的嵌入式操作系统很多,比如μC/OS-II、BuleCat ME Linux、RTA MB、ThreadX、PetaL-inux等等。

本次项目实验是在xilinx 公司的spartan_3E开发板上移植petalinux内核一、实验目的通过成功做一个嵌入式项目,把前期课堂学习转化成实践能力,真正具备基础的嵌入式开发能力,为今后的更大的项目实践打下基础二、实验步骤1.在EDK中建立基本硬件系统新建工程,添加DCE,LED,FLASH,DDRAM,MAC,以及定时器等IP核2. 在EDK中创建BSPBSP是在EDK中创建BSP板级支持包(Board Support Package),是介于主板硬件和操作系统之间的一层,应该说是属于操作系统的一部分,主要目的是为了支持操作系统,使之能够更好的运行于硬件主板。

BSP是相对于操作系统而言的,不同的操作系统对应于不同定义形式的BSP,例如VxWorks的BSP和Linux的BSP相对于某一CPU来说尽管实现的功能一样,可是写法和接口定义是完全不同的,所以写BSP一定要按照该系统BSP的定义形式来写(BSP的编程过程大多数是在某一个成型的BSP模板上进行修改),这样才能与上层OS保持正确的接口,良好的支持上层OS。

FPGA平台架构在嵌入式系统中的使用

FPGA平台架构在嵌入式系统中的使用设计嵌入系统的主要挑战来自于需要同时优化众多设计因素。

这些需要优化的设计因素包括单位成本、NRE(不可回收工程)成本、功率、尺寸、性能、灵活性、原型制造时间、产品上市时间、产品在市场生存时间、可维护性、可重配置能力、工程资源、开发和设计周期、工具、硬件/软件划分,以及其他许多因素。

Virtex-II ProTM平台FPGA产品基于高性能的Virtex-IITM结构,为嵌入式系统设计提供了一个极灵活的解决方案。

利用Virtex-II ProTM器件,嵌入式系统设计人员可以在单片器件内集成范围广泛的硬和软IP核心,其中的硬件和固件具有可升级能力,从而可延长产品的在市场生存时间。

Virtex-II 结构的可编程能力降低了系统开发时间并使单个平台FPGA解决方案可适用于多种应用。

Virtex-II ProTM FPGA使系统设计人员可在整个开发周期中对系统进行优化,同时还为硬件和软件设计任务折衷提供了无与伦比的协同设计灵活性。

硬件/软件系统划分允许设计人员可以控制以效率最高的方式实现所需要的功能。

Virtex-II ProTM平台FPGA产品提供了一个可以满足多种应用的处理、DSP和连接功能要求的平台,这些应用包括光学网络系统、千兆位路由器、无线蜂巢式基站、调制解调器阵列、专业视频广播系统、测试和测量设备、生物医疗系统、工业控制器,以及其他许多应用。

下面我们重点列出了Virtex-II ProTM平台FPGA的主要特性和功能。

Rocket I/OTM 收发器Virtex-II ProTM 器件提供了高达16个千兆位并串和串并收发器,可以支持不同的高速串行标准,如Gigabit Ethernet、Fiber Channel、Infiniband、Serial ATA、RapidIO、3GIO、Aurora、和XAUI。

其通道绑定功能可以结合多个通道提供高于3.125Gb/s的数据传输速率。

一种基于FPGA和软核CPU的嵌入式系统设计方法

一种基于FPGA和软核CPU的嵌入式系统设计方法

王赋攀;毕国堂

【期刊名称】《电脑知识与技术》

【年(卷),期】2007(003)014

【摘要】本文对一种基于FPGA和软核CPU的嵌入式系统设计的方法进行了描述,整个系统以FPGA和NIOS为中心进行设计,外围接口包括JTAG、串口、USB口等.系统选用ALTERA公司的Cyclone系列的芯片作为核心处理芯片,配合ALTERA 公司推出的NIOS软核嵌入式处理器构成整个系统的核心.操作系统采用μC/OS嵌入式系统,并移植到FPGA平台上.

【总页数】2页(P492-493)

【作者】王赋攀;毕国堂

【作者单位】西南科技大学,计算机科学与技术学院,四川,绵阳,621010;西南科技大学,计算机科学与技术学院,四川,绵阳,621010

【正文语种】中文

【中图分类】TP311

【相关文献】

1.一种SRAM型FPGA内嵌CPU软核的SEU效应防护设计与验证 [J], 杜新军;周建华;胡剑平

2.基于FPGA片上8位CPU软核Picoblaze的USB接口设计 [J], 张飞;王焕玉

3.基于FPGA MicroBlaze软核实现的以太网设计方法 [J], 王晓鹏

4.采用内置于FPGA中的软核CPU加速嵌入式系统设计 [J], 程光尧

5.一种基于FPGA和软核CPU的嵌入式系统设计方法 [J], 王赋攀;毕国堂

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGA_ASIC-基于FPGA 的嵌入式ASIP 软核设计与实现

基于FPGA的嵌入式ASIP软核设计与实现作者:李庆诚任健刘嘉欣黄宝贞来源:微计算机信息摘要:采用ASIP+FPGA模式设计了一款嵌入式微处理器软核,以该软核为例从体系结构和指令集设计两方面对ASIP+FPGA模式微处理器软核的设计进行了分析和验证,最后通过与传统微处理器对比验证了该设计模式的优势:指令针对性强,执行效率高;易于扩展,适应性强。

关键词:嵌入式系统,处理器软核,ASIP,FPGA,VHDL嵌入式系统往往执行比较单一的任务,针对某种特定应用而专门设计,但目前在嵌入式系统中采用的微处理器绝大部分都是通用嵌入式微处理器,其通用的指令集面对千差万别的嵌入式应用时暴露出专用性差,执行效率低的弱点。

另一个问题是,目前应用的嵌入式微处理器都是硬核,功能模块和指令集都是固定的,当应用发生较大变化时,很难通过对微处理器功能模块和指令集进行扩展来适应变化,往往只能换用一款新的微处理器,甚至重新设计整个嵌入式系统的硬件和软件,浪费了大量的时间和金钱。

因此,如何提高指令集的针对性,提高指令的执行效率以及如何增强嵌入式微处理器的扩展能力成了困扰嵌入式系统开发人员的两个难题。

1.ASIP和FPGAASIP的提出是微处理器设计理念的一项重大创新。

ASIP(Application-Specific Instruction set Processor)即专用指令集处理器,它相对传统微处理器最大的特点就是其指令集针对特定应用专门设计,一条指令就可以完成该种应用常做的一系列运算,例如一些常用算法,这样就极大的提高了指令的执行效率,往往若干条普通指令几十个时钟周期完成的操作用一条专用指令几个时钟周期就完成了。

采用ASIP理念设计微处理器可以在很大程度上解决上一节提到的指令集专用性差,指令执行效率低的问题,但这是要付出代价的,因为这些专用指令一般需要专门硬件电路支持才能实现。

ASIP用传统的集成电路技术实现是不现实的,集成电路设计复杂,开发周期长,定型后无法进行扩充,这样每遇到一种新应用,就得重新设计一款专用芯片,成本是不可接受的,这在一个时期内限制了ASIP的发展,直到FPGA(Field Programmable Gate Array,现场可编程门阵列)的出现,才为ASIP的实现提供了可能。

基于FPGA的嵌入式系统的设计与实现

2、输入模块设计

输入模块主要包括乐曲信息的采集和传输。本系统中,乐曲信息采用MIDI格 式进行存储和传输。用户可以通过MIDI键盘或者其他MIDI设备将乐曲信息输入到 系统中。

3、处理模块设计

处理模块主要由FPGA完成,其主要任务是将输入的乐曲信息转换为硬件可以 识别的控制信号。

具体来说,FPGA首先需要将MIDI格式的乐曲信息解析为数字信号,然后通过 内部算法进行处理,生成控制音频硬件的信号。本系统中,FPGA主要通过VHDL编 程语言来实现上述功能。

基于FPGA的嵌入式系统的设计与实 现

目录

01 基于FPGA的嵌入式系 统设计与实现

02 参考内容

基于FPGA的嵌入式系统设计与 实现

随着科技的不断发展,嵌入式系统在各个领域的应用越来越广泛。FPGA(现 场可编程门阵列)作为一种灵活、高效的硬件设计技术,为嵌入式系统设计提供 了新的解决方案。本次演示将介绍基于FPGA的嵌入式系统的设计与实现。

经过以上步骤,我们可以得出基于FPGA的嵌入式系统的设计与实现具有以下 优点:首先,FPGA的可编程性使得硬件设计更加灵活,可以根据不同需求进行定 制和优化;其次,FPGA的高速并行处理能力可以提高整个嵌入式系统的运算效率 和性能;再次,使用FPGA可以降低系统功耗和成本,同时减小了系统的体积和重 量;最后,FPGA的可重构特性使得系统升级和维护更加简便。

1、硬件设计

系统的硬件部分主要包括DSP、FPGA、RAM、Flash等。其中,DSP用于实现 信号处理算法,接收GPS和惯性导航等传感器数据,计算出位置、速度等信息; FPGA用于实现硬件接口、数据传输和控制逻辑,连接各个硬件模块,保证系统的 正常运行;RAM用于存储运行时的数据和程序;Flash用于存储固件程序和常量数 据。

基于fpga的嵌入式系统设计_修改版

基于fpga的嵌入式系统设计_修改版摘要本文设计完成的是基于FPGA的嵌入式系统开发板,它可以完成FPGA、嵌入式系统和SOPC等的设计和开发。

开发板以Altera公司的Cyclone系列FPGA—EP1C6为核心,在其外围扩展FLASH、SRAM、A/D、D/A、键盘、LED显示、LCD显示、串口通信、VGA接口、PS2接口和USB接口等器件,使其成为一个完整的嵌入式开发系统,系统采用模块化设计,各个模块之间可以自由组合,使得该开发板的灵活性和可扩展性大大提高。

同时开发板所提供的丰富的接口模块,供人机交互和器件间通信使用,方便了开发者的设计和系统的嵌入,可以满足普通高等院校、科研人员等的需求。

开发者可以使用VHDL语言、Verilog HDL语言、原理图输入等多种方式进行逻辑电路和功能模块设计,也可以利用Altera公司提供的IP资源和Nios 16/32位处理器开发嵌入式系统,借助QuartusII和Nios SDK Shell软件进行编译、下载,并通过本嵌入式系统开发板进行调式和结果验证。

关键词:嵌入式系统,Nios嵌入式处理器,SOPC,FPGAIABSTRACTThe thesis completes a design of an embedded system development board based on FPGA.The development board can complete the design of FPGA,embeded system,SOPC and so on.The development board is based on Altera Cyclone device—EP1C6,the board extends several peripheral devices such as,FLASH,SRAM, A/D,D/A,LED,LCD,keyboard,serial port,VGA interface,PS2 interface,USB interface and so on.All the devices constitute an integrated embeded development system. The development board offers us plenty of interfaces to meet the need of the device communication and the intercommunion between human and computer,which makes the design and the embedding of the system more easier.The Nios Development Board can meet the need of scientific researchers and other college researchers.The developers can use VHDL,Verilog HDL,schematic input mode and so on to design logic circuit and function block,they can alse use the IP core and Nios microprocessor which are offered by AlteraIto develop embedded systems. The developers can utilize QuartusⅡ and Nios SDK Shell to compile and download,then they can use this development board to debug and validate the result.KEY WORDS: embeded system, Nios embeded CPU,SOPC,FPGAI目录前言 (1)第1章绪论 (3)1.1嵌入式系统概述 (3)1.1.1嵌入式系统的特点 (3)1.1.2 片上系统和可编程片上系统 (6)1.2 Nios嵌入式处理器 (7)1.2.1 Nios嵌入式处理器特性 (7)1.2.2 Nios嵌入式处理器系统组件 (10)1.2.3 Avalon交换结构总线 (11)第2章 Nios嵌入式系统开发板整体理论分析 (16)2.1 系统设计目标 (16)2.2 系统设计原理 (16)2.3 开发板组件与理论分析 (19)2.4 开发板电路设计原理图与PCB布线图 (24)第3章 Nios嵌入式系统开发板硬件开发环境 (26)3.1 硬件开发环境概述 (26)3.2 FPGA:EP1C6QC240C8的特性和电路设计 (26)I3.2.1 特性和封装 (27)3.2.2 引脚说明 (28)3.2.3 工作条件 (28)3.3 串行配置器件:EPCS1的特性和电路设计 (28)3.3.1 Cyclone FPGA的配置 (28)3.3.2串行配置器件: EPCS1/EPCS4 (31)3.3.3 EPCS1的电路设计 (34)3.4 SRAM:IDT71V016的特性和电路设计 (34)3.4.1 器件特性 (34)3.4.2 IDT71V016工作方式 (35)3.4.3 IDT71V016的电路设计 (37)3.5 FLASH:AM29LV800B的特性和电路设计 (39)3.5.1 器件特性 (39)3.5.2 器件工作方式描述 (40)3.5.3 AM29LV800总线操作 (42)3.5.4 AM29LV800的电路设计 (44)第4章软件开发环境:QuartusⅡ和SOPC Builder (45)4.1 QuartusⅡ及其开发流程 (45)4.2 SOPC Builder (46)4.3 GERMS监控 (49)第5章 Nios嵌入式系统开发板调试 (52)I5.1 片内RAM、ROM调试 (52)5.2 GERMS监控调试 (59)5.3 扩展SRAM调试 (66)5.4 扩展FLASH调试 (69)第6章底板部分 (76)6.1 底板概述 (76)6.2 高速A/D:TLC5540 (77)6.3 高速D/A:DAC908 (79)6.4低速A/D:MCP3202 (82)6.5 低速D/A:DAC7512 (83)6.6 LED数码管及键盘管理器件:ZLG7289A (85)6.7 图形LCD液晶显示屏:HD61202 (88)第7章应用实例:利用Nios嵌入式系统开发板完成DDS的设计 (91)7.1 理论分析 (91)7.2 利用开发板实现的优点 (94)7.3系统设计与实现 (95)7.3.1 参数选取 (95)7.3.2 系统设计 (96)7.3.3 系统实现 (97)第8章总结 (98)8.1 主要工作总结 (98)I8.2 结论 (98)8.3 改进意见 (99)致谢 (100)参考文献 (101)附录 (102)附1 英文原文 (102)附2 中文翻译 (113)附3 Cyclone器件引脚功能、定义和工作条件 (121)附4 测试程序led.c (142)I前言FPGA的特点及其发展趋势:嵌入式系统,是一个面向应用、技术密集、资金密集、不可垄断的产业,随着各个领域应用需求的多样化,嵌入式设计技术和芯片技术也经历着一次又一次的革新。

基于FPGA技术的嵌入式系统设计与开发

基于FPGA技术的嵌入式系统设计与开发嵌入式系统在现代科技中起着至关重要的作用,它们被广泛应用于智能手机、汽车、医疗设备和工业控制等领域。

嵌入式系统的设计与开发过程中,FPGA(Field Programmable Gate Array)技术成为一种常用的解决方案。

本文将探讨基于FPGA技术的嵌入式系统设计与开发的相关内容。

一、嵌入式系统设计与开发的基本概念嵌入式系统是一种特殊的计算机系统,它被嵌入到其他设备或系统中,以实现特定的功能。

嵌入式系统通常具有实时性要求、资源受限、功耗低等特点,因此对其设计与开发的要求较高。

基于FPGA技术的嵌入式系统设计与开发,采用可编程逻辑芯片FPGA作为硬件平台,通过对FPGA内部逻辑电路的编程实现所需功能。

相比于传统的ASIC(Application Specific Integrated Circuit)设计流程,FPGA技术具有可重构性、快速原型开发、灵活性等优势。

二、FPGA技术在嵌入式系统设计与开发中的应用1. 快速原型开发FPGA技术可以提供快速的原型开发平台。

设计人员可以使用HDL (Hardware Description Language,硬件描述语言)如Verilog或VHDL编写嵌入式系统的逻辑电路,并通过FPGA工具链将其综合为FPGA可接受的二进制配置文件。

这样,设计人员可以在相对较短的时间内验证系统的功能和性能。

2. 灵活性与可重构性FPGA技术允许设计人员在硬件平台上灵活地重新编程和更改逻辑电路。

这意味着设计人员可以在嵌入式系统的开发过程中进行迭代和调试,以满足不断变化的需求。

与传统的ASIC设计相比,FPGA技术大大缩短了设计和开发周期。

3. 高性能与低功耗由于可以根据具体功能需求对FPGA进行高度优化,因此基于FPGA技术的嵌入式系统可以实现高性能和低功耗的平衡。

设计人员可以通过优化逻辑电路、使用流水线技术以及利用FPGA内部资源等方法来提升系统性能,并在功耗控制上进行权衡。

一种基于FPGA和软核CPU的嵌入式系统设计方法

电脑知识与技术本栏目责任编辑:谢媛媛开发研究与设计技术1引言嵌入式系统通常包括CPU、存储器和各种外设器件,是计算机技术为基础、面向应用的,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统,其中CPU作为核心而具有重要地位。

嵌入式处理器传统上一般选用ASIC器件,ASIC(专用的集成芯片)器件是一种为具体任务而特殊设计的专用电路,由于ASIC在设计过程中进行了专门优化,其性能、性价比都较高,减少了系统软件和硬件设计的复杂程度,降低系统成本,但还是存在一些缺点,如前期设计费用非常高,一旦设计完就无法升级和扩展等。

“可重构计算”的概念的出现,改变了嵌入式硬件模块的设计方法,它允许在不改变硬件电路板的情况下,实现不同的控制接口和控制功能。

可重构计算是通过现场可编程门阵列(FPGA)实现的,FPGA是20世纪80年代中期以后发展起来的一种可编程的大规模的集成器件。

同ASIC技术相比,基于FPGA的嵌入式具有设计周期短、设计成本和风险低、集成度高、维护和升级方便、可靠性高等特点。

同时,随着系统设计引入"片上可编程系统"(SoPC),FPGA具有了作为嵌入式处理器的能力,在嵌入式系统设计领域已占据越来越重要的地位。

FPGA设计是以软核的设计和使用为主的,因此随着基于FPGA的嵌入式系统的设计技术和市场的成熟,嵌入式CPU软核的大量应用成为可能。

2硬件系统设计2.1系统整体结构整个设计的硬件系统结构如图1,微处理器选用了ALTERA公司的Cyclone系列的EP1C1240Q8;存储设备选用了AM29LV320D;外围接口包括USB接口、以态网接口、JTAG口、以及串口;选用分辨率为128×64液晶显示模块做为输出显示。

以下分别将各个模块进行介绍。

(1)微处理器EP1C12Q240C8是ALTERA公司的Cyclone系列芯片,拥有12060个逻辑单元(LE)、52个M4K存储块、全部RAM位数为239616、两个锁相环,以及249个可用的I/O脚。

用FPGA实现Nios II嵌入式系统配置技术

本文主要根据Altera公司手册及以前的经验,设计和完成了一种新的FPGA配置文件下载更新的方法。其主要原理是在每次启动系统时,由配置控制器从Flash中读出FPGA配置文件,再下载到FPGA中以完成器件的配置功能。当系统需要升级更新FPGA配置文件时,可通过网络或者由主机通过JTAG(Joint Test Action Group)接口(未联网时)将配置文件发送给基于Nios II处理器的嵌入式系统中,由Nios II处理器更新系统中的Flash。当Flash内容更新后,系统就可实现在加电时由配置控制器自动将配置文件下载到FPGA中。而配置控制器是采用复杂可编程逻辑器件(CPLD,Complex Programmable Logic Device),主要功能是实现并串转换。这样在不需要任何硬件动作和专业软件的情况下,只需要进行常规软件操作就可以更新FPGA的配置文件。不仅节约了成本,还有效地缩小了系统体积,有利于以后系统工程的升级更新。

程中很少使用。

边界扫描方式需要连接计算机,无法在现场使用,嵌入式系统中很少采用这种方式。

基于FPGA的嵌入式开发

文献标识码: 八

文章编号: 1672 3791(2007)( 片 上 围设备总线) 、 X P S 中。 夕卜 DCR 总线(设备控制总线)、 OCM总线(片 卜 存 (3 软件开发。软件开发实际 七 ) 就是驱动 储器总线) 、I MI弓 总线( 内部存储器总线) 和 程序的开发, 通用集成电路I 进行印刷电路板 尸 C CH的设计 在创建I 核的时候, ) S 已经提 P Xl 1 喀L总线, 其中Mic 0I aze 系统使用的总线为 r 3 l 供了 一些基本的函数可供使用, 其中包括读/ 和调试, 而是转向以大规模现场可编程逻辑阵 0 尸 总线 、L M B 总线和 F S L 总线 。 B 列 1 PGA} 2](1 ield Prog r amm able Gat c 刃 ’ 了 写寄存器函数等。在软件开发过程中, 是不需 要对硬件部分进行更改的, 因此, 可以反复进 Ar ay , r 现场可编程门阵列)或专用集成电 路 A SI C 为物理载体的系统级的 毖 片设计。使 3 基于F G P A的嵌入式开发流程 行调 这个过程开发周期比较短。 试, ( 4 ) 凋试与验证。在使用 I E 进行设计 S 用AS C为物理载体进行芯片设计的技术称为 I 在设计一个嵌入式系统时 , 首先要创建一 时, 可以使用的仿真工具有Models i, 6. 1(1和 :1 个嵌人 式开发平台, 这个 「 _作主要由Xi in x l 片上系统技术, o c 。 即s n F P GA 具有体系结构完整和逻辑单元灵 platfornl s tudio s . 11 (简称为x Ps )来完成。 Chipsco详 8. 11。使用Mo(lels ir 6. ld 进行 验证主要以书写Te 山ench 为主, s 观察输出波 活、 集成度高以及适用范围 ‘ ) 等特点。 ID J 使用XPS 进行嵌入式开发的主要过程为: 以丁 I }} 言来表达设计意图, ’ 语 以FPGA 作为 硬件载 (1)使用 Baso s yste:n Buil〔 (简称为 ler 形, 可以进行的验证包括功能验证、布局布线 贝 { 体, 以计算机为设计开发工具, 以EDK 软件为 BSB) 「 具创建一个包含基本功能的嵌人式开 后验证等。使用Chips cope s . 11验证,1是 开发环境, 八 C、SOC 和 J 技术等为综合 以 S I , l 发平台。在这个过程 中主要完成的工作是 将设计 下载到FPGA 内, 通过Ch ps ope 观察 i c 设计的方法, 已成为硬件设计工程的主要特 FI〕 开发板的选择, Vir tcx 4 ML402 FPGA 内部实际信号来进行验证。Ch ps co洋 i GA 如 征。 GA 信号的宽度和深 EV altlatiO Platform(用于 ll 嵌人式开发)或 者 占用F尸 内部存储器资源, Vir tex 4 ML403 Eva luati()n 冬 〕 latform (用 度可以任意设置, 但是, 要对资源的利用率有 Z MicroBI。 ze系统 准 的 。 确 估计 使用system Generator 工 创 具 于DSP 开发), 也可以选择其他Xi nx FPGA i l 建模块会自 动产生Tcs b“ h 文件用于 t c I 测试。 就必须要对系统 一个典型的Mic oB aze 系统如图 1所示, 的开发板。如果选择后者, r l 具包括 处于核心地位的是软核处理器Mic oB a e。 进行定义。其中包括 : 处理器的定义 ; 设置处 在 XP S 中可以使用的仿真与验证 工 r l z ChiP co谬 、 门 Mlcr oProces or Debugger S Xi]1 x s 可以在 Xi i x 公司任何系列 F 尸 上创建 理器时钟频率;设置总线时钟;设置调试方式; l n GA SDK。Chips cope 用于 抓取、 Mi r B a e , c o l z 占用一定的内部资源。 处理器通 设置数据存储器和指令存储器的容量; 设置基 (简称为XMD)、 XMD 对 于 察看寄 过LMB 本地存储器总线)总线与数据存储器 本 / 0 设 ( 的1 备等。 蓄 之 一个 含 观察 FPGA 内部真实信号, 设一 豁 完毕 后, 包 存器的依非常有效, 可以察看甲核使用的寄存 和指令存储器进行交互。1 _MB 总线可在单个 基本功能的硬件平台就设计完毕。 ‘ SDK 软件对软件调试非常有效。 (2 硬件设计。为 ) 完成嵌入式设计, PS 器的值, 在x 时钟周期内访问片内存储器 BR AM 。处理器 中提供 了 一此基本功能模块 , 如存储器控制 通过 OPB 总线与 I 核进行交互 , 护 核包 P 这些 器、输入 / 输出设备、中断控制器、存储器、 参考文献 括微处理器调试模块、 文件系统、 存储器控制 P 【 王诚. FPGA/ CPLD 设计I几 ] 1 具 i x linx 器、通用输入 / 输出设备、D D R 控制器、 调试设备、数字时钟管理器等。如果这些 工 核能够满足用户的设计需求, 那么直 接将他们 ISE 使用详解【 . 北京: 人民邮电出版社, M】 UART 、中断控制器以及用户甲 核。通过这 2 00 5 . 并连接到总线 卜 。用户可以使用 即可 些 I 核又可以与 FPGA 片外资源进行交 互。 实例化, P [M]. 在使用 Xi nx 公司FPGA 进行嵌入式开 i l ISE 不 [ISystcr Generator 等软件来设计完成 [2] 王冠.Verilog ll DL 与数字电路设计 n 不同功能的模块, 然后将其作为 I 核引入到 P 发时, 可以使用的总线包括: PLB 总线(处理器 北京: 机械工业出 版社, 2005. 1 刘韬. FPGA 数字电 广 ] 3 系统设计与 开发实 例导航【 北京: 人民邮电出版社, M}. 2005.

一种基于FPGA软核处理器的数字控制系统设计

• 165•采用基于Nios II的可编程片上系统(System on a Programmable Chip,SOPC)在FPGA平台上设计并实现了一种实时性强和精确度高的数字控制系统,这套系统的外设包含串口控制器、电压采集器(ADC)、温度传感器、FLASH及RAM存储器等,能够快速响应上位机的控制指令,实现信号的采集与输出的控制。

本文详细介绍了该系统的设计思路及方案实现,并在实际工程应用中得到了验证。

1.FPGA及其软核处理器概述FPGA(Field Programmable Gate Array)即大规模可编程门阵列是一种基于硬件描述语言进行设计的器件,因其内部逻辑可根据需求自由设计,而且开发成本低,设计周期短。

发展至今,FPGA的有点越来越突出,时钟频率高、内部延时小、运行速度快、借助计算机平台的EDA工具进行自顶向下的设计,在高速数字逻辑应用中大放异彩,得到了众多用户的青睐。

随着硬件功能的提升,基于软核处理器的嵌入式开发模式被迅速推广,已在控制、通信和信号处理领域等复杂应用需求中得到了广泛的应用(孙登强,赵玉龙,李波,等.高精度石英振梁谐振式传感器测试系统设计:仪表技术与传感器,2018;王丽,安永泉,王志斌,等.基于SOPC的弹光调制干涉信号高速数据采集:电子器件,2017)。

Nios II是专为Altera公司开发的系列FPGA的软核处理器(也就是我们说的MCU,但它是一个软核,也就是说,没有添加Nios II软核的FPGA,是一个并没有处理器的逻辑器件,但如果你添加,它会将Nios II处理器合成到FPGA的内部),用于Nios 2软件开发是基于C,C++或汇编语言,软件开发环境是Qartus2支持Nios 2 IDE。

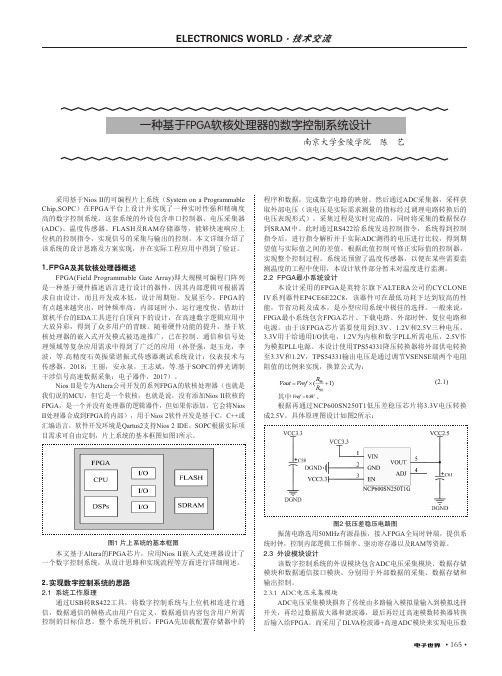

SOPC根据实际项目需求可自由定制,片上系统的基本框图如图1所示。

图1 片上系统的基本框图本文基于Altera的FPGA芯片,应用Nios II嵌入式处理器设计了一个数字控制系统,从设计思路和实现流程等方面进行详细阐述。

FPGA实现嵌入式系统

FPGA实现嵌入式系统北京理工大学雷达技术研究所陈禾主要内容嵌入式系统概念与组成 基于FPGA的嵌入式系统设计 系统集成开发环境嵌入式系统—定义计算系统无处不在,由个人计算机、笔记本 电脑、工作站、大型机和服务器等构成计算 系统并不奇怪,但是,更广泛的是为完全不 同的目的构造的计算系统,它们嵌入在更大 的电子器件内,分别完成特定的功能,而不 被器件的使用者所识别。

对于这样的嵌入计算系统,简称为嵌入式系 统,可以定义为除了计算机或电脑之外的几 乎任何的计算系统。

这个不很精确的定义,可以使我们着手考察 嵌入系统设计者所面临的挑战。

嵌入式系统的一般特性嵌入系统一般功能单一,重复执行一个特定的 程序,除非嵌入系统的程序用新的程序版本更 新,或者因尺寸限制它有几个程序倒进和倒出。

对嵌入系统的约束特别严格,诸如成本、尺寸、 性能和功耗等作为实现的特性,嵌入系统要求 成本是极低的价格,尺寸限制到最小、但达到 实时快速地处理数据,且消耗最少的功率,能 延长电池受命,也不需要冷却等。

其它如NRE成本、灵活性、样机的时间、上市 的时间、可维护性、准确性和安全性。

反应和实时性:许多嵌入系统必须对系统环境 的变化连续地反应,且要无滞后地实时计算确 定的结果。

嵌入式系统应用嵌入式系统组成硬件嵌入式系统实现的基础应用程序实现特定任务和功能操作系统(可选)对应用软件进行管理 使硬件对应用软件透明嵌入式系统硬件部分微处理器或微控制器嵌入式系统的核心存储器用来存储程序和数据外设如定时器、中断控制器、UART、 GPIO等电源部分 其它辅助部分嵌入式系统软件部分应用软件实现所需功能,执行特定任务操作系统(RTOS)提供对应用软件的一组服务 使硬件细节对应用软件透明嵌入式系统的软/硬件设计软件设计重要的是微处理器的内部操作如何进行硬件设计重要的是总线接口,与微处理器的逻辑 连接要遵循总线协议的全部规则,才能 保证硬件设计正确嵌入式系统的软/硬件设计内部操作包括指令集:处理器可以运行的指令的格式 寄存器:通用寄存器、状态寄存器和程序计数器的某种组 合 Cache:专门的高速缓存,储存经常利用的数据和指令等 流水:不同级的指令处理提供增加的性能 存储器管理单元(MMU)提供实现虚拟存储器需要的地 址变换,操作系统利用它来防止程序或任务造成系统崩溃外部接口包括存储器总线接口,对总线仲裁器的规则 协处理器总线接口 中断:一般有多个不同优先级的中断嵌入式系统设计的核心技术|处理器技术z通用处理器z单用途处理器z专用处理器|IC技术z全定制VLSIz半定制ASICz可编程ASIC-FPGA|设计验证技术嵌入式系统—处理器技术|通用处理器或微处理器软件——编程处理器的存储器完成要求的功能控制器:程序存储器数据通道:含寄存器堆或通用ALU|单用途处理器硬件—设计数字电路准确地执行一个程序甚至设计定制数字电路产生单用途处理器控制器:有限状态机,不需要程序存储器数据通道:只包含为执行此程序的基本元件|专用处理器:为特定类应用优化的可编程处理器微控制器(单片机):为嵌入控制应用优化的处理器数字信号处理器(DSP):执行数字信号的常用运算嵌入式系统—IC技术通用处理器专用处理器单片机DSP单用途处理器FPGA CPLD 半定制:标准单元门阵列(结构化ASIC)全定制:ASICASSP嵌入式系统—设计验证技术系统技术条件行为技术条件RTL技术条件逻辑级技术条件门级仿真门电路/单元电路逻辑级综合HDL仿真RTL元件RTL级综合Hw-Sw协同仿真Cores行为综合Model仿真/校验Hw/Sw/OS系统级综合Test/VerificationLibraries/IPCompilation/Synthesis至最终实现可编程系统FPGA内嵌处理器FPGA 嵌入式系统的发展Embedded Software ToolsCPULogic Design ToolsI/O FPGAMemoryLogic Design ToolsFPGA + Memory + IP +High Speed IO (4K & Virtex ™)Embedded Software ToolsCPUI n t e g r a t i o n o f F u n c t i o n sTimeLogic Design ToolsEmbedded Software ToolsLogic + Memory+ IP + Processors + RocketIO (Virtex-II Pro ™)Programmable Systems usher in a new era of systemdesign integration possibilitiesFPGA嵌入式系统的发展嵌入式系统市场|工业分析家普遍预测全球半导体需求市场将是一个稳中带降的趋势。

基于FPGA的嵌入式CPU的VHDL设计

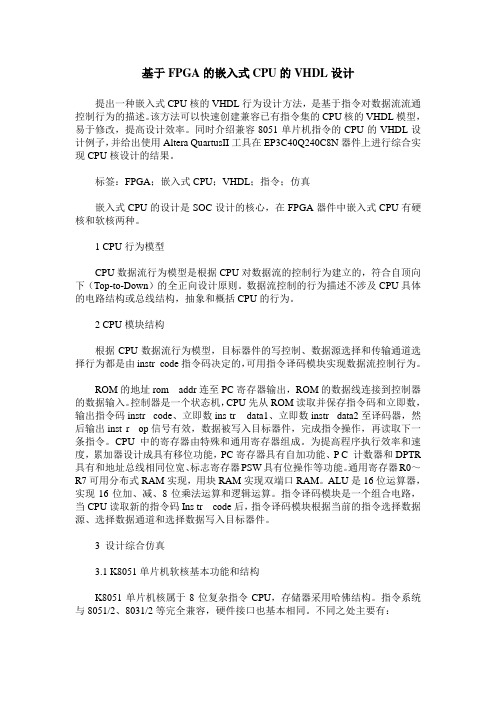

基于FPGA的嵌入式CPU的VHDL设计提出一种嵌入式CPU核的VHDL行为设计方法,是基于指令对数据流流通控制行为的描述。

该方法可以快速创建兼容已有指令集的CPU核的VHDL模型,易于修改,提高设计效率。

同时介绍兼容8051单片机指令的CPU的VHDL设计例子,并给出使用Altera QuartusII工具在EP3C40Q240C8N器件上进行综合实现CPU核设计的结果。

标签:FPGA;嵌入式CPU;VHDL;指令;仿真嵌入式CPU的设计是SOC设计的核心,在FPGA器件中嵌入式CPU有硬核和软核两种。

1 CPU行为模型CPU数据流行为模型是根据CPU对数据流的控制行为建立的,符合自顶向下(Top-to-Down)的全正向设计原则。

数据流控制的行为描述不涉及CPU具体的电路结构或总线结构,抽象和概括CPU的行为。

2 CPU模块结构根据CPU数据流行为模型,目标器件的写控制、数据源选择和传输通道选择行为都是由instr_code指令码决定的,可用指令译码模块实现数据流控制行为。

ROM的地址rom _ addr连至PC寄存器输出,ROM的数据线连接到控制器的数据输入。

控制器是一个状态机,CPU先从ROM读取并保存指令码和立即数,输出指令码instr _code、立即数ins tr _ data1、立即数instr _data2至译码器,然后输出inst r _op信号有效,数据被写入目标器件,完成指令操作,再读取下一条指令。

CPU 中的寄存器由特殊和通用寄存器组成。

为提高程序执行效率和速度,累加器设计成具有移位功能,PC寄存器具有自加功能、P C 计数器和DPTR 具有和地址总线相同位宽、标志寄存器PSW具有位操作等功能。

通用寄存器R0~R7可用分布式RAM实现,用块RAM实现双端口RAM。

ALU是16位运算器,实现16位加、减、8位乘法运算和逻辑运算。

指令译码模块是一个组合电路,当CPU读取新的指令码Ins tr _ code后,指令译码模块根据当前的指令选择数据源、选择数据通道和选择数据写入目标器件。

为什么嵌入式开发人员要使用FPGA

为什么嵌入式开发人员要使用FPGA?

在一个领域中,如果唯一不变的是变化,那么不需要对电子技术和设计方法的发 展变化做多少回顾,您就能见证到创新是如何促使设计工程师创建出下一代的革 新产品的。微处理器得到大规模应用后,可用的新技术为基于软件的革新性电子 产品设计打开大门。简而言之,把设计的主要元素 — 控制“智能” — 转入到软 领域后,设计工程师就可以在更短时间内创建出更好、更智能、更廉价的产品。 变化意味着嵌入式软件开发人员是当今定义电子产品功能和特性的主要推动者, 并且最终将把硬件生产出来。该方法的成功因素在于减少硬件复杂度和把设计的 控制元素转变到可编程领域带来的开放灵活性。 今天,大容量、低成本可编程器件的到来推动了电子产品设计的发展,实现了在 软领域定义系统硬件本身。诸如大容量FPGA这样的大规模器件对满足这一需求十 分理想,一般可用于构建大部分系统外设逻辑功能块,包括总线接口、I/O块、甚 至内存。把大量逻辑引入FPGA对硬件开发具有深远影响,为新时代的‘软’设计 打开了一扇大门,这为设计提供了前所未有的灵活性,同时具有减少板级尺寸和 复杂度的无穷潜力。 虽然这种潜力对电子产品开发过程起到了革命性作用,但多数嵌入式软件开发人 员仍像以前一样工作 — 在设计开始阶段选择分立的硬件处理器、创建物理平台,然后写软件使用该平台。人们在嵌入式 系统开发的‘软’硬件领域缺乏探索,其主要原因在于缺少让C程序员在可编程硬件级使用其技巧的工具。确实,当前多 数FPGA设计流主要都来自芯片设计领域,需要非常专业的技巧。

更多关于Altium Designer支持 Altera Nios II 处理器的信息: /files/corp/media/pdfs/20060403ADIntroSupAlteraNiosIISoftPro.pdf 更多关于Altium Designer支持ARM 技术,AMCC 405 PowerPC处理器,Xilinx MicroBlaze 等处理器的信息: /AboutUs/Media/PressReleases/ 更多Altium Designer嵌入式开发的信息: /Products/AltiumDesigner/ProgrammableDevices/

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的软核处理器在嵌入式中的运用

随着一些ASIC 应用开发日益受到成本的困扰,OEM日渐转向FPGA 来构建自己的系统。

这些系统中绝大多数需要一个处理器为了给设计者提供一个为FPGA 优化的灵活的嵌入式处理器方案,满足16位和32位嵌入式处理器市场的需求,Altera公司公司推出Nios II 系列32位RSIC嵌入式处理器。

这是Altera的第二代软核嵌入式处理器,性能超过200DMIPS,在Altera FPGA 中实现仅需35美分。

因为Nios II处理器是软核,因此开发者能够从无限的系统配置组合中选择满足性能和成本目标的方案,而不必为系统级设计考虑采用ASIC。

与此同时赛灵思公司(Xilinx,Inc.)宣布推出Virtex®-5 FXT 器件。

这些FPGA 器件在业界率先集成了嵌入式PowerPC®440处理器模块、高速RocketIO™GTX收发器和专用XtremeDSP™处理能力。

作为65nm Virtex-5系列的第四款平台,

Virtex-5 FXT提供了极高的性能,还可帮助设计人员降低系统成本、缩小板尺寸并减少元件数量。

在赛灵思公司以及业界领导厂商提供的逻辑、嵌入式和DSP开发工具以及IP内核的支持下,Virtex-5 FXT FPGA为有线和无线通信、音频/视频广播设备、军事、航空航天、工业系统以及其它众多应用提供了一个终极系统集成平台。

从FPGA两大主要生产公司的设计方向上我们可以看出,未来的嵌入式发展将向基于软核处理器的FPGA发展,也就是常称之为的SoPC(可编程片上系统Sysein on a Programmable Chip)设计思想。

基于FPGA 的SoPC 具有设计灵活、可裁减、可配置、可扩充、可升级的特点,并具备软硬件在系统可编程的功能。

我们借助强大得EDA 工具,在设计嵌入式系统时,不仅可以实现软件的可裁减性,同样可以实现硬件的可裁减性,并且可以自主定义处理器的引脚,方便PCB板布线,同样方便更改设计。

Altera 的Nios 处理器和Stratix FPGA 是其Maestro 平台的核心,它具有的核心功能提供了前所未有数据为中心的功能。

能够用于任何需要32位嵌入式处理器的应用。

据介绍,Nios II 系列包括三种软CPU 核,一个是最大系统性能,一个是为最少逻辑使用量优化的,还有一个是二者之间的平衡。

所有核都是100% 代码兼容,让设计者根据系统需求变化改变C P U ,而不会影响现有的软件投入。

Nios II系列是建立在前一代成功的基础之上,以部分的资源提供高得多的性能。

另外,Nios II处理器具有健全的软件开发套件,包括编译器、集成开发环境(IDE ),JTAG 调试器,实时操作系统(RTOS)和TCP/IP 协议栈。

Nios II嵌入式处理器结合Altera的低成本Cyclone 系列和高性能StratixII 系列FPGA 和HardCopy 结构化ASIC系列,在价格、性能和功能上具有很高的灵活性。

Lytle先生认为,Nios II系列增加了Altera 在嵌入式处理器市场上的机会。

当第一代Nios 处理器为Altera 开辟了新的应用和市场之门时,Nios II嵌入式处理器系列有望增加公司在16位和32位嵌入式处理器市场上的机会。

从使用Altera 低成本Cyclone FPGA 系列的探鱼器和引擎测试仪到使用高性能Stratix系列的视频处理和高级通信系统,Altera的软核嵌入式处理器已经成为新应用中使用可编程逻辑的推动力。

在单片器件上集成重要处理性能和SERDES元件,可为那些需要节约板级空间和成本、同时又需要满足高性能要求的设计人员提供巨大的价值。

例如,在无线应用中,Virtex-5

FXT平台技术可以支持的基站类型是受到高度关注的,特别是在支持4G通信系统的LTE(长期演化)基带的应用领域。

创新的Virtex-5 FXT平台是业界首个提供多达两个业界标准的PowerPC 440

处理器模块的FPGA产品。

每个处理器集成了32KB指令和32KB 数据缓存,在550 MHz 时钟频率下可提供高达1,100 DMIPS 的性能。

与PowerPC440模块紧密耦合的是新的集成5x2纵横开关式交换处理器互连架构,支持并发的I/O和存储器访问。

这一高度集成的创新互连架构包括专用的主/从处理器局部总线接口、支持独立发送/接收通道的四个DMA端口,以及一个支持高性能、低延迟点对点连接的专用存储器总线接口。

利用PowerPC 440嵌入式处理器模块,设计人员可快速方便地实现高级可扩展嵌入式处理应用。

先进的PLB架构支持高吞吐量128位接口,可使系统瓶颈最小化,从而将处理器、纵横开关式交换构造以及软IP逻辑之间的数据传输能力最大化。

同时,在视频处理、3D数据处理以及浮点运算等应用中,增强的高性能辅助处理器控制单元(APU)还为专用协处理器引擎或用户专门定义的指令提供额外的连接能力。

在FPGA 中使用软核处理器比硬核的优势在于,硬核实现没有灵活性,通常无法使用最新的技术。

随着系统日益先进,基于标准处理器的方案会被淘汰,而基于Nios II 处理器的方案是基于HDL 源码构建的,能够修改以满足新的系统需求,避免了被淘汰的命运。

将处理器实现为HDL 的IP 核,开发者能够完全定制CPU 和外设,获得恰好满足需求的处理器。

下面我基于Nios II软核处理器介绍一下如何使用软核处理器设计自己的嵌入式系统。

1、使用QuartusⅡ内部集成的系统级开发工具SoPC Builder(如果开发DSP系统则使用DSP Builder),选择合适自己系统得Nios II软核,这里我们可以定义Nios II 处理器的位数,内部RAM的大小,ROM的大小,FLASH的大小,可以定义JTAG仿真的等级。

2、我们完成基本的处理器之后,我们应再加上一些已有或自己开发的IP核,比如一些IO,PWM模块,I2C,UART,SPI等通信模块。

3、接着我们定义中断信息和等级信息,中断地址。

4、全部定义完毕之后,就进行编译,然后定义引脚,下载,这就构成了自己特有的处理器。

5、使用Nios II的C编译器将自己的程序进行编译,之后运行,其中Nios II的C 编译器自带一些操作系统,我们从中进行裁减,实现软件的可裁减性。

从以上步骤我们可以看出,使用软核处理器,我们不仅可以实现软件的可裁减性,还可以实现硬件的可裁减性,所以使用SOPC的设计思想,我们的设计就大大地灵活了。

如有侵权请联系告知删除,感谢你们的配合!。