STM8-SWIM通信协议

深入浅出stm8单片机入门、进阶与应用实例

深入浅出stm8单片机入门、进阶与应用实例STM8单片机是一款性能优越、功能丰富的微控制器,被广泛应用于嵌入式系统中。

本文将从深入浅出的角度,为大家介绍STM8单片机入门、进阶以及实际应用案例。

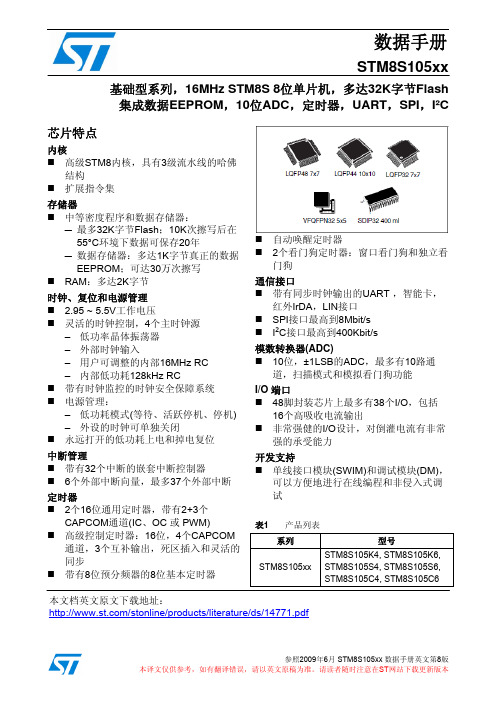

一、STM8单片机入门1. STM8单片机概述STM8单片机是意法半导体公司推出的一款8位微控制器,采用了高性能的STM8内核和丰富的外设资源。

相比其他8位单片机,STM8单片机具有更高的性能、更丰富的功能和更低的功耗。

2. STM8单片机编程语言STM8单片机支持多种编程语言,包括C语言、汇编语言、BASIC语言等。

其中,C语言是最常用的一种编程语言,具有语法简单、易于理解等优点。

3. STM8单片机开发环境STM8单片机开发环境包括开发工具和编程器。

常用的开发工具有IAR Embedded Workbench、ST Visual Develop、Keil uVision等。

编程器可以选择ST-Link/V2、ST-Link/V3、J-Link等。

4. STM8单片机基础知识STM8单片机基础知识包括IO口、定时器、中断等。

掌握这些基础知识是学习STM8单片机的基础。

其中,IO口用于接收或输出数字信号,定时器用于计时、测量时间等,中断用于实现程序的异步处理。

二、STM8单片机进阶与实践1. STM8单片机外设应用STM8单片机具有丰富的外设资源,包括GPIO、I2C、SPI、USART、ADC等。

这些外设可以满足不同应用场景的需求。

例如,GPIO用于控制LED等外围设备,I2C和SPI用于连接外部设备,USART用于串口通信,ADC用于模拟信号的采集。

2. STM8单片机通信协议STM8单片机支持多种通信协议,包括UART、I2C、SPI等。

这些通信协议可以实现与其他设备的通信,例如与传感器、显示器、无线模块等设备的通信。

不同的通信协议有着不同的特点和应用场景,需要根据实际需求选择合适的协议。

3. STM8单片机中断技术中断是STM8单片机中的一项重要技术,可以实现程序的异步处理。

STM8S_汇编

不知是心血来潮,还是其它因素,突然又想起玩汇编语言了。

这几年也没少跟单片机打交道,包括51系列,430系列,ARM系列,但都是用C语言来开发。

不过由于使用C语言,实际上对这些CPU的了解还是不够深刻,当然除了51之外,因为那是我多年前曾经用汇编开发过的芯片。

尽管当今C语言已经在嵌入式产品的开发过程中成为主流,但我个人依然认为,要想真正了解CPU的特点,还得用汇编语言。

不知道这种观点是对还是错,也许是因为自己从硬件做起,写过机器码,用汇编语言做过优化,因此对汇编语音有一种特殊的偏爱。

51系列的芯片用多了,感觉有时写起程序来不太方便,因此总想寻找一些其它的8位单片机玩玩,正好手头有一个ST的三合一开发板,那是09年参加ST研讨会上买的,一直躺在那里,与其躺在那里,不如拿出来玩玩。

这几年,ST在国内推广STM32,力度不小,不过我一直没有用过,只是初步地看看资料。

原因在于在32位单片机方面,我一直在用Luminary公司的LM3S1138,感觉不错,一直都很顺利。

09年ST举办的研讨会上,ST除了介绍STM32外,也介绍了STM8,当时听了以后,觉得还行。

尤其是会上的低功耗演示给我留下了很深刻的印象。

基于这些,我决定好好地玩一下STM8芯片,并将玩的结果拿出来与大家共享。

STM8与汇编语言(2)第一次打开STM8的手册时发现,CPU中的寄存器只有6个,即A、X、Y、SP、PC 和CC。

这几个寄存器,看上去特象早年苹果机使用的微处理器6502。

在眼下都是多寄存器的RISC潮流下,不知ST推出的这种CPU架构有什么意图?这样的芯片能否与Microchip 或者Atmel的RISC结构的MCU竞争呢?在此我无意做评论,我只想了解这颗芯片。

通过仔细研究,我发现由于STM8采用了32位宽度的程序存储器结构,使得大部分的指令都能在一个周期内取出,并且采用了哈佛结构和流水线,相当多的指令也都是单周期完成的。

这样的话,虽然CPU是CISC架构的,但也基本上达到了单周期指令的效果,就像手册上说的,CPU的性能达到了20MISP◎24MHZ。

STM8L中文参考手册-1

简介本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

表一、目录1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

351.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

40 3.4.3介质+密度装置记忆的组织。

..。

41 3.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

STM8L系列超低功耗8位微控制器 说明书

STM8L1xx 典型应用和结构框图

医疗器械 血糖仪 胰岛素泵 糖尿病监护 血压计 胆固醇计 病人监控 心脏监护 仪表 电表/气表/水表/热表 称重 报警系统 中央处理单元 有线/无线传感器 门禁 通用移动设备 手机及配件 3D鼠标及遥控器 游戏机和玩具 GPS手表 体育设施

内部的16MHz RC振荡器 1~16MHz晶体 振荡器 内部的38kHz RC振荡器 32.768kHz晶体 振荡器 运行于16MHz的 STM8核心 嵌套的中断控制器 32个中断向量 多达40个外部中断 SWIM 调试模块 多达41个I/O端口 12位ADC 25个通道

STM8L系列

超低功耗8位微控制器

微控制 超节能

2009年9月

/mcu

STM8L超低功耗MCU系列

意法半导体公司开发出了基于8位STM8内核的超低功耗微控制器.借助一个优秀的面向未来的超低功耗平台,采 用了全新的超低漏电工艺和优化的体系结构,STM8L系列微控制器集合了高性能与超低功耗于一身.STM8L系列 现有三个子系列,可以满足对低功耗有特殊要求的多种应用.

STM8L一览

现在已有26个兼容的产品

Flash容量 (字节) STM8L152C8

64 K 32 K 16 K 8K

STM8L152R8 STM8L152M8 STM8L151R8 STM8L151M8

STM8L151C8 STM8L152K6 STM8L151G6 STM8L151K6 STM8L152K4 STM8L151G4 STM8L151K4 STM8L151F3 STM8L101F3 STM8L151G3 STM8L151K3 STM8L101G3 STM8L101K3 STM8L151G2 STM8L101G2 28引脚 QFN (4x4) 32引脚 LQFP (7x7)/ QFN (5x5) 48引脚 LQFP (7x7)/ QFN (7x7) STM8L152C6 STM8L151C6 STM8L152C4 STM8L151C4

STM8L中文参考手册-1

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx 和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

35 1.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

403.4.3介质+密度装置记忆的组织。

..。

413.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

493.6内存编程493.6.1同时读写(读写网)。

STM8S主控原理图

STM8S主控原理图

1.单片机电源电路:单片机需要一个恒定的供电电压,通常使用稳压

电路来实现,这个电路通常由电源滤波电容、稳压芯片和电位器组成。

2.外部晶振电路:STM8S单片机需要一个外部晶振来提供时钟信号,

这个电路通常包括晶振、两个电容和两个电阻。

3.通信接口电路:STM8S单片机支持UART、SPI和I2C等通信接口,

所以通常还需要一个逻辑电平转换电路和相应的连接器或插座。

4.GPIO电路:STM8S单片机有多个可编程的GPIO引脚,可以用来连

接外部设备,通常需要引脚保护电路和外部设备的驱动电路。

5.ADC电路:STM8S单片机内置了模数转换器(ADC),用于测量模拟

量输入信号,通常需要一个输入电压分压电路和滤波电路。

6.外设驱动电路:除了上述基本电路外,STM8S单片机还可以连接一

些外设,如LCD显示屏、LED指示灯、蜂鸣器等。

这些外设通常需要驱动

电路和相应的连接器。

以上仅是一个简单的例子,实际的STM8S主控原理图还会根据具体的

应用需求而有所差异。

在设计STM8S主控原理图时需要考虑电路的稳定性、可靠性和抗干扰能力,同时还要满足单片机的性能要求和外部设备的需求。

为了提高设计效率,可以借助Eagle、Altium Designer等电路设计软件

来完成。

浅谈STM8(3)——SPI通信

浅谈STM8(3)——SPI通信STM8的SPI还是挺好用的,也挺简单,起码相比于I2C来说是的。

最近因为要调试NRF905,所以就用到了STM8的SPI。

因为调试过程中没有遇到什么大的问题,所以在此只对STM8的SPI作简单的介绍。

博主只使用了STM8作为主设备的双线单向数据模式,并且没有使用CRC。

在使用STM8的SPI时首先需要确认——1.主从关系,并且确认是否使用STM8上的NSS引脚作为主从判据2.SPI时序,四种有差异的时序3.串行数据是MSB在前还是LSB在前以上条件很好地弄清楚后,便可以配置寄存器了。

因为主模式下数据收发全由STM8自身控制,所以不需要使用中断。

另外端口也无需设置,使用默认状态就可以。

需要配置的寄存器只有SPI_CR1和SPI_CR2。

几个要点:1.在配置这两个寄存器时确保SPI_CR1中的SPE复位,禁止SPI。

在配置完成后方可将其打开,使能SPI。

2.SPI_CR2中的SSM和SSI配合使用,若SSM置位使能了软件从设备管理,则原NSS引脚将与SPI没有一丁点的关系,SSI完全代替了NSS引脚。

3.若与STM8通信的器件对通信的频率(波特率)没有要求,SPI_CR1中的BR可随意,可设为000最高速。

4.CPOL和CPHA的选择,查看与STM8通信的器件手册,一般会给出SPI时序图,对比STM8手册上的时序图便可确定。

其余按要求配置便可。

主模式下的读写操作同样很简单。

写:1.复位选中器件的CS,使其进入从模式,准备接受数据2.先查询SPI_SR中的TXE标志(循环查询),直到置位,只有当发送缓冲区空时方可发送数据3.将数据写入SPI_DR,数据将自动发送出去4.循环等待查询SPI_SR中的RXNE标志,等待数据发送完毕并接收回传数据,直到置位5.读出SPI_DR中的数据,复位RXNE6.置位选中器件的CS,结束数据传输若要连续进行数据传输,只需复位一次CS,重复步骤2-5,直到所有数据传输完毕,再置位CS。

STM8 单线接口模块(SWIM)和调试模块(DM)

STM8 单线接口模块(SWIM)和调试模块(DM)介绍STM8 在线调试模式或在应用编程模式由一个单线硬件接口来管理,该接口拥有对存储器超高速编程的特性。

该接口和在线调试模块相配合,可提供一种非侵入性(non-intrusive)的仿真模式,在这种仿真模式下,在线调试器的调试仿真功能非常强大,其性能已经接近于一个全功能仿真器。

主要特性基于一个异步,高注入电流(8mA),漏极开路的双向通讯。

允许读写存储器空间的任意位置。

可读写CPU 寄存器(A,X,Y,CC,CP)。

它们有用于读写的寄存器映射地址。

在运行中可对RAM 和外设寄存器进行非侵入式读写。

器件复位有相应的复位状态指示位,请参考复位状态寄存器(RST_SR)。

时钟速度可选,请参考SWIM 时钟控制寄存器(CLK_SWIMCCR)。

SWIM 引脚可用作普通I/O 口,但如果用户还想使用该引脚做调试,则在使用上有一些限制。

最安全的作法是在PCB 板上提供一个跳线选择。

SWIM 模式在上电复位后,SWIM 模块复位,然后进入OFF 模式。

OFF:在上电复位后的默认状态。

SWIM 不能用作普通I/O 口。

I/O:将全局配置寄存器(CFG_GCR)中的SWD 位置位后进入该模式。

在这种模式下,SWIM 引脚可用作普通I/O 口。

一旦系统复位,SWIM 模块重新回到OFF 模式。

SWIM:当在SWIM 引脚上输入特定的序列时进入该模式。

在这种模式下,调试工具通过SWIM 引脚使用三种命令(SRST 系统复位,ROTF 运行中读,WOTF 运行中写)来控制STM8。

注意:可参考STM8 SWIM 通讯协议和调试模块用户手册来了解SWIM 和调试模块(DM)的更多信息。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

ST推出了STLINK-V3下一代STM8和STM32微控制器代码烧写及调试探针

ST推出了STLINK-V3下一代STM8和STM32微控制器代码烧写及调试

探针

意法半导体推出了STLINK-V3下一代STM8 和STM32微控制器代码烧写及调试探针,进一步改进代码烧写及调试灵活性,提高效率。

STLINK-V3支持大容量存储,具有虚拟COM端口和多路桥接功能,烧写性能是上一代探针的三倍,产品价格具市场竞争力,节省应用开发时间,简化设备现场重新编程流程。

除提供典型的JTAG /串行线调试(SWD)和单线接口模块(SWIM)连接外,STLINK-V3的虚拟COM端口(VCP)和多路桥接器还可以通过UART、I2C、SPI或CAN接口或GPIO 引脚与微控制器通信,方便开发人员使用自定义控制命令自动执行测试,并在PC主机上观察运行时数据,或者使用STLINK-V3配合引导加载程序向设备烧写代码,简化产品维护任务。

现有主要开发工具已支持STLINK-V3,允许用户利用STM32Cube编程器等方便的图形环境和Keil®MDK-ARM、IAR™EWARM和基于GCC的IDE等集成开发环境(IDE)的强大功能。

意法半导体还允许免费访问STLINK-V3底层API,以便与自定义或自动化测试平台集成。

作为一套完整的工具,STLINK-V3SET套件包含探针、调试连接器、电缆和支持SWIM 特定功能的适配板,并可以取用多路桥接信号。

用户可以增加一块附加电路板,例如,电压转换器模块,以较低的成本进一步扩展探针的功能。

STLINK-V3SET现在可从st或通过分销商购买。

STM8L中文参考手册-1,2,3,4(RM0031)

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

351.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

403.4.3介质+密度装置记忆的组织。

..。

413.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

493.6内存编程493.6.1同时读写(读写网)。

STM8L微控制器中文参考手册

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx 微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

35 1.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

40 3.4.3介质+密度装置记忆的组织。

..。

41 3.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

WizPro200ST8 STM8和STM32烧写器(编程器)使用说明书-RV1

有可能为串口选择不对,需要重新选择串口并查找设备;具体操作见第三部分的 PC 应用程序手册。

WizPro200ST8 Flash MCU 编程器使用说明-RV1

2. 请选择“是,仅这一次(Y)”并单击“下一步”,此时电脑屏幕会出现右边的窗口: 3. 请选择“从列表或指定位置安装(高级)(S)”并单击“下一步”,则电脑屏幕将出现如下窗口:

4. 按上图示,按“浏览”按钮,选择正确的驱动程序位置(“USB_Driver\DrvVCP-Win2KXP”),并 单击“下一步”,系统将自动安装相应的驱动程序,点击“完成”完成第一布的安装;

¾ 蓝色红色指示灯交替闪烁,表示编程器正在对目标芯片进行编程器; ¾ 红色灯亮同时蜂鸣器响3次短声:表示对目标芯片编程器失败,需检查相应的连接; ¾ 蓝色灯亮同时蜂鸣器响1次长声:表示对目标芯片编程成功;

5 蜂鸣器:

5.1 上电:响一短声,表示系统内部校验正常,蓝灯亮;响两长声,则表示系统内部出错或内部 数据校验出错,需要重新连接电脑下载数据;若响一长声(约1S),则表示系统内部固件有问题, 需要重新升级或维修;

4.2.2 编程器下载程序后接上电源时: ¾ 红色和蓝色指示灯交替闪烁:表示系统正进行内部数据校验; ¾ 红色灯亮同时蜂鸣器响2次长声:表示系统内部数据校验失败,须连接电脑重新下载程序数据;

WizPro200ST8 Flash MCU 编程器使用说明-RV1

Page 2 of 18

信号说明 引脚

GND

GND

GND

1

3

5

VOUT 7

IND2 LED_NG NIL

9

11

13

引脚

2

4

6

8

10

STlink与STM8S开发板接线及下载程序说明

使用STlink连接STM8S开发板下载程序说明

一、接线说明

STlink支持STM32和STM8单片机的仿真和调试。

STM8S的仿真也同样需要STlink的支持。

连接STM8S开发板你需要进行以下步骤:

♦1.从STlink的盒子中找到一条单排10PIN的线,一头是10P杜邦头,另一头是分开的。

将找到的排线连接到STlin k。

注意你需要插到第二排,也就是空一根针的那一排。

在引出的排线中,找到以下标识的线:

红色的TVCC

橙色的SWIM

黑色的GND

白色的SWIM-RST

♦2.STM8S开发板已经引出了SWIM接口,位于手拧电位器的旁边(左上角)。

那一排4针的排针,从1脚到4脚依次为:

1.VCC

2.SWIM

3.GND

4.RESET

♦3.依次连接这些引脚。

开发板上电,STlink连接到电脑。

二、程序下载说明

1.程序编译成功后,右键单击工程名,选择Options,使用STlink下载。

如下图所示:

2.点击Download and Debug

3.点击“go”,此时程序已经下载到开发板上了。

STM8 FLASH编程手册

June 2011Doc ID 14614 Rev 31/27PM0051Programming manualHow to program STM8S and STM8A Flash program memory and data EEPROMIntroductionThis manual describes how to program Flash program memory and data EEPROM onSTM8 microcontrollers. It applies to access and performance line STM8S and medium and high density STM8A devices. It is intended to provide information to the programming tool manufacturers and to the customers who want to implement programming by themselves on their production line.The in-circuit programming (ICP) method is used to update the content of Flash program memory and data EEPROM while the user software is not running. It uses the Single wire interface module (SWIM) to communicate between the programming tool and the device.In contrast to the ICP method, in-application programming (IAP) can use anycommunication interface supported by the microcontroller (I/Os, SPI, USART , I 2C, USB, CAN...). IAP has been implemented for users who want their application software to update itself by re-programming the Flash program memory during program execution. The main advantage of IAP is its ability to re-program Flash program memory and data EEPROM when the chip has already been soldered on the application board and while the usersoftware is running. Nevertheless, part of the Flash program memory has to be previously programmed using ICP .Some devices also contain a bootloader embedded in a ROM memory. Through this firmware the device memory can be re-programmed using a standard communication interface. This programming method is not described in this document.For details on memory implementation and features, registers or stack top addresses, refer to the product datasheets.Related documents●STM8 SWIM communication protocol and debug module (UM0470)●STM8 bootloader user manual (UM0560)l●STM8S and STM8A microcontroller families reference manual (RM0016)●Basic in-application programming example using the STM8 I 2C and SPI peripherals (AN2737)●STM8 in-application programming example (AN2659)●Performance line datasheet (high density Flash program and data EEPROM)●Access line datasheets (low and medium density Flash program and data EEPROM)●STM8A datasheets (up to 32 Kbytes and up to 128Kbytes of Flash program memory)Contents PM0051Contents1Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1Low density STM8S microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.2Medium density STM8S microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . . 72.3High density STM8S microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92.4Medium density STM8A microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . 102.5High density STM8A microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . . . 123Memory protection strategy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.1Readout protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.2User Boot Code area protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153.3Unwanted memory access protection . . . . . . . . . . . . . . . . . . . . . . . . . . . 154Programming STM8 Flash microcontrollers . . . . . . . . . . . . . . . . . . . . . 164.1Unlocking the Memory Access Security System (MASS) . . . . . . . . . . . . 164.2Block programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164.3Word programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.4Byte programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.5Programming the option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.5.1Summary of memory dedicated option bytes . . . . . . . . . . . . . . . . . . . . 224.5.2How to program the option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.6Memory access versus programming method . . . . . . . . . . . . . . . . . . . . . 234.6.1ICP methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.6.2IAP method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 5Flash program memory and data EEPROM comparison . . . . . . . . . . . 25 6Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262/27Doc ID 14614 Rev 3PM0051List of tables List of tablesTable 1.Low density STM8S memory partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table 2.Medium density STM8S memory partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Table 3.High density STM8S memory partition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Table 4.Medium density STM8A memory partition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 5.High density STM8A memory partition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table 6.Recommended minimum and maximum sizes of the UBC area . . . . . . . . . . . . . . . . . . . . 15 Table 7.MASS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 8.Memory access versus programming method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Table parison between STM8S and STM8A devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 10.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Doc ID 14614 Rev 33/27Glossary PM0051 1 GlossaryThis section gives a brief definition of acronyms and terms used in this document:●BlockA block is a set of bytes that can be programmed or erased in one single programmingoperation. Operations that are available on a block are fast programming, erase only,and standard programming (which includes an erase operation). Refer to Section2:Memory organization for details on block size according to the device.●BootloaderThe bootloader is an IAP application embedded in the system memory of the device. Itis used to erase and program the device using a standard serial communication port.The bootloader is not available on small devices, and is not described in the presentdocument. Refer to STM8 bootloader user manual (UM0500) for more details.●DriverA driver is a control program defined by the application developer. It is used to managethe allocation of system resources to start application programs. In this document twodrivers are described, ICP and IAP drivers.●In-application programming (IAP)IAP is the ability to re-program the Flash program memory and data EEPROM (DAT A)of a microcontroller while the device is already plugged-in to the application and theapplication is running.●In-circuit programming (ICP)ICP is the ability to program the Flash program memory and data EEPROM of amicrocontroller using the SWIM protocol while the device is plugged-in to theapplication.●In-circuit debugging (ICD)ICD is the ability to debug the user software using the SWIM protocol. The user has theability to connect the device to a debugger and insert breakpoints in his firmware.Debugging may be intrusive (application patched to allow debugging) or non intrusive(using a debug module).●Memory access security system (MASS) keysThe Memory access security system (MASS) consists of a memory write protectionlock designed to prevent unwanted memory modifications due to EMS or programcounter loss. To unlock the memory protection, one or more keys must be written in adedicated register and in a specific order. When the operation (write or erase) iscompleted, the MASS must be activated again to provide good memory security.4/27 Doc ID 14614 Rev 3PM0051Glossary●PageA page is a set of blocks. The number of blocks in a page may differ from one device toanother. Refer to Section2: Memory organization for details on page size according tothe device.A dedicated option byte can be used to configure by increments of one page the size ofthe user boot code. Refer to Section5: Flash program memory and data EEPROMcomparison for a description of available areas and option bytes according to thedevices.●Read-while-write (RWW)The RWW feature provides the ability for the software to perform write operation ondata EEPROM while reading and executing the program memory. Execution time istherefore optimized. The opposite operation is not allowed: the software cannot readdata memory while writing program memory.The RWW feature is not available on all STM8 devices. Refer to Table9 for informationon devices with RWW capability.●Single wire interface module (SWIM)The SWIM is a communication protocol managed by hardware in the STM8microcontrollers. The SWIM main purpose is to provide non intrusive debug capability.It can also be used to download programs into RAM and execute them. It can also write(registers or RAM) or read any part of the memory space and jump to any memoryaddress. The SWIM protocol is used for ICP. It is accessed by providing a specificsequence on the SWIM pin either during the reset phase or when the device is running(if allowed by the application).●System memoryThe STM8 system memory is a small ROM accessible when the user software isexecuted. It contains the bootloader. The system ROM and the bootloader are notavailable on all STM8 devices.●User boot code area (UBC)The user boot code area is a write-protected area which contains reset vector, interruptvectors, and IAP routine for the device to be able to recover from interrupted orerroneous IAP programming.●User modeThe user mode is the standard user software running mode in the STM8. It is enteredeither by performing a power-on-reset on the device or by issuing the SWIM SRSTcommand from a development tool.●WordA word is a set of 4 bytes and corresponds to the memory granularity.Doc ID 14614 Rev 35/27Memory organization PM00516/27 Doc ID 14614 Rev 32 Memory organizationThis section describes the memory organization corresponding to:●Access line and performance line STM8S microcontrollers ●Medium and high density STM8A microcontrollersSTM8S microcontrollers offer low density (8Kbytes), medium density (from 16 to32Kbytes) and high density (from 32 to 128Kbytes) Flash program memory, plus data EEPROM.STM8A microcontrollers feature medium density (from 8 to 32Kbytes) and high density (from 32 to 128Kbytes) Flash memory, plus data EEPROM.The memory organization differs from one STM8 family to another. Refer to Section 2.1, Section 2.2, Section 2.3, Section 2.4, and Section 2.3 for a description of the memory organization according to microcontroller family and memory density.A memory accelerator takes advantage of the parallel 4-byte storage, which corresponds to a word. The Flash program memory and data EEPROM can be erased and programmed at byte level, word level or block level. In word programming mode, 4 bytes can beprogrammed/erased during the same cycle, while in block programming mode, a whole block is programmed/erase during the same cycle. Refer to Section 2.1, Section 2.2, Section 2.3, Section 2.4, and Section 2.3 for information on block size according to the devices.2.1 Low density STM8S microcontrollersThe memory array is divided into two areas:●8Kbytes of Flash program memory organized in 128 pages or blocks of 64 bytes each. The Flash program memory is divided into 2 areas, the user boot code area (UBC), which size can be configured by option byte, and the main program memory area. The Flash program memory is mapped in the upper part of the STM8S addressing space and includes the reset and interrupt vectors.●640 bytes of data EEPROM (DATA) organized in 10 pages or blocks of 64bytes each. One block (64bytes) contains the option bytes of which 11 are used to configure the device hardware features. The options bytes can be programmed in user, IAP and ICP/SWIM modes.Refer to T able 1 for a detailed description of the memory partition for low density STM8S microcontrollers.PM0051Memory organizationDoc ID 14614 Rev 37/272.2 Medium density STM8S microcontrollersThe memory is divided into two arrays:●From 16 to 32Kbytes of Flash program memory organized in up to 64 pages of 4blocks of 128 bytes each. The Flash program memory is divided into 2 areas, the user boot code area (UBC), which size can be configured by option byte, and the mainprogram memory area. The Flash program memory is mapped in the upper part of the STM8S addressing space and includes the reset and interrupt vectors.●1Kbytes of data EEPROM (DATA) organized in up to 2 pages of 4 blocks of 128bytes each. One block (128 bytes) contains the option bytes of which 13 are used toconfigure the device hardware features. The options bytes can be programmed in user, IAP and ICP/SWIM modes.Refer to T able 2 for a detailed description of the memory partition for medium density STM8S microcontrollers.Table 1.Low density STM8S memory partitionAreaPage number (1 page=1 block)Block number (1 block=64bytes)Address Data EEPROM000x004000-0x00403F 110x004040-0x00407F 220x004080-0x0040BF (9)90x004240-0x00427F Option bytes -0 (one block only)0x004800-0x00483F Flash program memory000x008000-0x00803F 110x008040-0x00807F 220x008080-0x0080BF (127)1270x009FC0-0x009FFFMemory organization PM00518/27 Doc ID 14614 Rev 3Table 2.Medium density STM8S memory partition (1)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)Address Data EEPROM 000x004000-0x00407F 10x004080-0x0040FF 20x004100-0x00417F 30x004180-0x0041FF 14-70x004200-0x0043FF Option bytes -0 (one block only)0x004800-0x00487F Flash program memory00x008000-0x00807F 10x008080-0x0080FF 20x008100-0x00817F 30x008180-0x0081FF 14-70x008200-0x0083FF... (63)2520x00FE00-0x00FE7F 2530x00FE80-0x00FEFF 2540x00FF00-0x00FF7F 2550x00FF80-0x00FFFF1.The memory mapping is given for the devices featuring 32Kbytes of Flash program memory.PM0051Memory organizationDoc ID 14614 Rev 39/272.3 High density STM8S microcontrollersThe memory is divided into two arrays:●From 32 to 128Kbytes of Flash program memory organized in up to 256 pages of 4 blocks of 128 bytes each. The Flash program memory is divided into 2 areas, the user boot code area (UBC), which size can be configured by option byte, and the mainprogram memory area. The Flash program memory is mapped in the upper part of the STM8S addressing space and includes the reset and interrupt vectors.●From 1 to 2Kbytes of data EEPROM (DATA) organized in up to 4 pages of 4 blocks of 128bytes each. The size of the DATA area is fixed for a given microcontroller. One block (128bytes) contains the option bytes of which 15 are used to configure the device hardware features. The options bytes can be programmed in user, IAP and ICP/SWIM modes.Refer to T able 3 for a detailed description of the memory partition for high density STM8S microcontrollers.Table 3.High density STM8S memory partition (1)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)Address Data EEPROM00x004000-0x00407F 10x004080-0x0040FF 20x004100-0x00417F 30x004180-0x0041FF 1 4 to 70x004200-0x0043FF 28 to 110x004400-0x0045FF 312 to 150x004600-0x0047FF Option bytes-0 (one block only)0x004800-0x00487FMemory organization PM005110/27 Doc ID 14614 Rev 32.4 Medium density STM8A microcontrollersThe memory is divided into two arrays:●From 8 to 32Kbytes of Flash program memory organized in up to 64 pages of 4 blocks of 128 bytes each. The Flash program memory is divided into 2 areas, the user boot code area (UBC), which size can be configured by option byte, and the main program memory area. The Flash program memory is mapped in the upper part of the STM8A addressing space and includes the reset and interrupt vectors.●From 384 bytes to 1Kbytes of data EEPROM (DATA) organized in up to 2 pages of 4 blocks of 128bytes each. One block (128 bytes) contains the option bytes of which 13 are used to configure the device hardware features. The options bytes can be programmed in user, IAP and ICP/SWIM modes.Refer to T able 4 for a detailed description of the memory partition for medium density STM8A microcontrollers.Flash program memory00x008000-0x00807F 10x008080-0x0080FF 20x008100-0x00817F 30x008180-0x0081FF 14 to 70x00 8200-0x00 83FF 28 to 110x00 8400-0x00 85FF... (255)10200x00 27E00-0x00 27E7F 10210x00 27E80-0x00 27EFF 10220x00 27F00-0x00 27F7F 10230x00 27F80-0x00 27FFF1.The memory mapping is given for the devices featuring 128Kbytes of Flash program memory and 2Kbytes of dataEEPROM.Table 3.High density STM8S memory partition (1) (continued)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)AddressPM0051Memory organizationDoc ID 14614 Rev 311/27Table 4.Medium density STM8A memory partition (1)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)Address Data EEPROM 000x004000-0x00407F 10x004080-0x0040FF 20x004100-0x00417F 30x004180-0x0041FF 14-70x004200-0x0043FF Option bytes -0 (one block only)0x004800-0x00487F Flash program memory00x008000-0x00807F 10x008080-0x0080FF 20x008100-0x00817F 30x008180-0x0081FF 14-70x008200-0x0083FF... (63)2520x00FE00-0x00FE7F 2530x00FE80-0x00FEFF 2540x00FF00-0x00FF7F 2550x00FF80-0x00FFFF1.The memory mapping is given for the devices featuring 32Kbytes of Flash program memory.Memory organization PM005112/27 Doc ID 14614 Rev 32.5 High density STM8A microcontrollersThe memory is divided into two arrays:●From 32 to 128Kbytes of Flash program memory organized in up to 256 pages of 4 blocks of 128 bytes each. The Flash program memory is divided into 2 areas, the user boot code area (UBC), which size can be configured by option byte, and the mainprogram memory area. The Flash program memory is mapped in the upper part of the STM8A addressing space and includes the reset and interrupt vectors.●From 1 to 2Kbytes of data EEPROM (DATA) organized in up to 4 pages of 4 blocks of 128bytes each. The size of the DATA area is fixed for a given microcontroller. One block (128bytes) contains the option bytes of which 15 are used to configure the device hardware features. The options bytes can be programmed in user, IAP and ICP/SWIM modes.Refer to T able 5 for a detailed description of the memory partition for high density STM8A microcontrollers.Table 5.High density STM8A memory partition (1)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)Address Data EEPROM00x004000-0x00407F 10x004080-0x0040FF 20x004100-0x00417F 30x004180-0x0041FF 1 4 to 70x004200-0x0043FF 28 to 110x004400-0x0045FF 312 to 150x004600-0x0047FF Option bytes-0 (one block only)0x004800-0x00487FPM0051Memory organizationDoc ID 14614 Rev 313/27Flash program memory00x008000-0x00807F 10x008080-0x0080FF 20x008100-0x00817F 30x008180-0x0081FF 14 to 70x00 8200-0x00 83FF 28 to 110x00 8400-0x00 85FF... (255)10200x00 27E00-0x00 27E7F 10210x00 27E80-0x00 27EFF 10220x00 27F00-0x00 27F7F 10230x00 27F80-0x00 27FFF1.The memory mapping is given for the devices featuring 128Kbytes of Flash program memory and 2Kbytes of dataEEPROM.Table 5.High density STM8A memory partition (1) (continued)AreaPage number (1 page=4 blocks)Block number (1 block=128bytes)Address3 Memory protection strategyThe STM8 devices feature several mechanisms allowing to protect the content of the Flashprogram and data EEPROM areas:●Readout protectionThe software can prevent application code and data stored in the Flash programmemory and data EEPROM from being read and modified in ICP/SWIM mode. Thereadout protection is enabled and disabled by programming an option byte inICP/SWIM mode. Refer to Section3.1 for details.●User boot code area (UBC)In order to guaranty the capability to recover from an interrupted or erroneous IAPprogramming, all STM8 devices provide a write-protected area called user boot code(UBC). This area is a part of the Flash program memory which cannot be modified inuser mode (that is protected against modification by the user software). The content ofthe UBC area can be modified only in ICP/SWIM mode after clearing the UBC optionbyte.The size of the user boot code area can be configured through an option byte byincrements of one page.Refer to Section3.2 for details on user boot code area.●Unwanted memory access protectionAll STM8 devices offer unwanted memory access protection, which purpose is toprevent unintentional modification of program memory and data EEPROM (for exampledue to a firmware bug or EMC disturbance).This protection consists of authorizing write access to the memory only through aspecific software sequence which is unlikely to happen randomly or by mistake. Accessto Flash program and data EEPROM areas is enabled by writing MASS keys into keyregisters.Refer to Section3.3 for details on unwanted memory access protection.protection3.1 ReadoutThe readout protection is enabled by writing 0xAA in the ROP option byte. It is disabled byreprogramming the ROP option byte with any value except for 0xAA and resetting thedevice.The readout protection can only be disabled in ICP/SWIM mode.When the readout protection is selected, reading or modifying the Flash program memory inICP mode (using the SWIM interface) is forbidden. When available, the data EEPROMmemory is also protected against read and write access through ICP.Erasing the ROP option byte to disable the readout protection causes the Flash programmemory, the DATA area and the option bytes to be erased.Even though no protection can be considered as totally unbreakable, the readout protectionfeature provides a very high level of protection for general purpose microcontrollers. Ofcourse, a software that allows the user to dump the Flash program memory content makethis readout protection useless. Table8 describes possible accesses to each memory areasversus the different modes and readout protection settings.14/27 Doc ID 14614 Rev 3Doc ID 14614 Rev 315/273.2 User Boot Code area protectionWhatever the memory content, it is always possible to restart an ICP session after a critical error by applying a reset and restarting the SWIM communication.On the contrary, during IAP sessions, the programming software driver must always be write protected to be able to recover from any critical failure that might happen during programming (such as power failure).The pages where the IAP driver is implemented must be located in the write-protected boot code area (UBC). The application reset and interrupt vectors and the reset routine must also be stored in the UBC. These conditions allow the user software to manage the recovery from potential critical failure by applying a reset and restarting the IAP routine from the protected boot area.The UBC size is defined by the user boot code (UBC) area option byte. This option byte may slightly differ from one product to another. See the following table for the minimum and maximum size of the UBC area. Its maximum size is equal to the full memory size3.3 Unwanted memory access protectionThe unwanted memory access protection consists of writing two 8-bit keys in the right order into dedicated MASS key registers.Writing the correct sequence of keys in the program memory MASS key register(FLASH_PUKR) enables the programming of the program memory area excluding the UBC. If wrong keys are provided, a reset must to be generated to be able to reprogram the right keys.Once the write memory protection has been removed, it is possible to reactivate the protection of the area by resetting the PUL bit in FLASH_IAPSR.To enable write access to the data EEPROM area, another specific MASS key register (FLASH_DUKR) and a different key sequence must be used. Once the dataEEPROM/option byte area is unlocked, it is possible to reactivate the protection of the area by resetting the DUL bit in FLASH_IAPSR.If wrong keys have been provided to the FLASH_PUKR register, the device must be reset before performing a new key program sequence. However, when wrong keys are provided to the FLASH_DUKR register, new keys can be entered without the device being previously reset.In order to be as effective as possible, the application software must lock again theunwanted memory access protection as soon as the programming is completed. Otherwise, the protection level of the MASS is significantly reduced. To activate the MASS protection again, the user must reset the corresponding bits in the FLASH_IAPSR register (DUL bit for data EEPROM or PUL bit for Flash program memory).Table 6.Recommended minimum and maximum sizes of the UBC areaSTM8 microcontroller familyRecommended minimum sizeof the UBC areaMaximum size of the UBC areaLow density STM8S2 pages = 128bytes Full memory size Medium density STM8S and STM8A 2 pages = 1KbyteFull memory sizeHigh density STM8S and STM8A16/27 Doc ID 14614 Rev 3Note:1The mechanism to lock and unlock unwanted memory access protection is identical for option bytes and data EEPROM (see Ta ble 7: MASS ).2Before starting programming program memory or data EEPROM, the software must verify that the area is not write protected by checking that the PUL or DUL bit is effectively set.4 Programming STM8 Flash microcontrollersThis section describes how to program STM8 single-voltage Flash microcontrollers.4.1 Unlocking the Memory Access Security System (MASS)The memory must be unlocked before attempting to perform any erase or write operation. To unlock it, follow the procedure described in Section 3.3: Unwanted memory access protection , and Table 7.The software must poll the PUL and DUL bit, before attempting to write to program memory and data EEPROM, respectively.4.2 Block programmingBlock write operations allow to program an entire block in one shot, thus minimizing theprogramming time.There are three possible block programming modes: erase, write only (also called fast programming) and combined erase/write cycle (also called standard block programming).Table 7.MASSMicrocontrollerfamilyData EEPROM and option bytes Program memoryUnlock Lock Unlock Lock STM8S and STM8AWrite 0xAE then56h in FLASH_DUKR (0x00 5064)(1)(2)1.The OPT and NOPT bits of FLASH_CR2 and FLASH_NCR2 registers must be set/cleared to enableaccess to the option bytes.2.If wrong keys have been entered, another key programming sequence can be issued without resetting thedevice.Reset bit 3 (DUL) in FLASH_IAPSR (0x00 505F)Write 0x56 then0xAE in FLASH_PUKR (0x00 5062)(3)3.If wrong keys have been entered, the device must be reset, and a key program sequence issued.Reset bit 1 (PUL) in FLASH_IAPSR (0x00 505F)。

STM8-SWIM通信协议和调试模块用户手册(部分翻译)

翻译:本人应朋友之邀,翻译了本文的第三章,由于水平有限,且没有用过STM8系列的控制器,如有错误,请见谅。

by踏雪无痕2010-11-11rose_yiyong@December 2009Doc ID 14024 Rev 21/37UM0470User manualSTM8 SWIM communication protocol and debug module IntroductionThis manual has been written for developers who need to build programming, testing or debugging tools for the STM8 microcontroller family. It explains the debug architecture of the STM8 core.The STM8 debug system consists of two modules:●DM: Debug module ●SWIM: Single wire interface moduleRelated documentation:●STM8S Flash programming reference manual (PM0051)●STM8L Flash programming manual (PM0054)STM8 SWIM 通信协议和调试模块用户手册1.介绍:STM8微控制器家族的测试或调试工具.它解释了 stm8 内核调试体系结构STM8 调试系统由两个模块组成:调试模块单线接口模块叙述文档:Contents UM0470Contents1Debug system overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 2Communication layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73Single wire interface module (SWIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . 83.1Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83.2SWIM entry sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93.3Bit format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3.1High speed bit format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.3.2Low speed bit format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.4SWIM communication protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133.5SWIM commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.5.1SRST: system reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.5.2ROTF: read on the fly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.5.3WOTF: write on the fly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153.6SWIM communication reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153.7CPU register access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163.8SWIM communication in Halt mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163.9Physical layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173.10STM8 SWIM registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.10.1SWIM control status register (SWIM_CSR) . . . . . . . . . . . . . . . . . . . . . . 183.10.2SWIM clock control register (CLK_SWIMCCR) . . . . . . . . . . . . . . . . . . . 194Debug module (DM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.2Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204.3Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.3.1Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.3.2Breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.3.3Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.3.4Watchdog control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.3.5Interaction with SWIM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224.4Breakpoint decoding table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 2/37Doc ID 14024 Rev 2UM0470Contents4.5Software breakpoint mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.6Timing description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.7Abort . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244.8Data breakpoint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254.9Instruction breakpoint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254.10Step mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254.11Application notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.11.1Illegal Memory access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.11.2Forbidden stack access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.11.3DM break . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.12DM registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274.12.1DM breakpoint register 1 extended byte (DM_BKR1E) . . . . . . . . . . . . . 274.12.2DM breakpoint register 1 high byte (DM_BKR1H) . . . . . . . . . . . . . . . . . 274.12.3DM breakpoint register 1 low byte (DM_BKR1L) . . . . . . . . . . . . . . . . . . 274.12.4DM breakpoint register 2 extended byte (DM_BKR2E) . . . . . . . . . . . . . 284.12.5DM breakpoint register 2 high byte (DM_BKR2H) . . . . . . . . . . . . . . . . . 284.12.6DM breakpoint register 2 low byte (DM_BKR2L) . . . . . . . . . . . . . . . . . . 284.12.7DM control register 1 (DM_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294.12.8DM control register 2 (DM_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304.12.9DM control/status register 1 (DM_CSR1) . . . . . . . . . . . . . . . . . . . . . . . 314.12.10DM control/status register 2 (DM_CSR2) . . . . . . . . . . . . . . . . . . . . . . . 324.12.11DM enable function register (DM_ENFCTR) . . . . . . . . . . . . . . . . . . . . . 334.12.12Summary of SWIM, DM and core register maps . . . . . . . . . . . . . . . . . . 34 Appendix A Description of the DM_ENFCTR registerfor each STM8 product . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36Doc ID 14024 Rev 23/37List of tables UM0470 List of tablesTable 1.SWIM command summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 2.CPU register memory mapping in STM8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 3.SWIM pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 4.Decoding table for breakpoint interrupt generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Table 5.STM8 registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 6.Peripherals which are frozen by the bits of the DM_ENFCTR registerfor each STM8 product. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 7.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 4/37Doc ID 14024 Rev 2UM0470List of figures List of figuresFigure 1.Debug system block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Figure 2.SWIM pin external connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 3.SWIM activation sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 4.SWIM activation timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 5.SWIM entry sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Figure 6.High speed bit format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 7.Low speed bit format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure mand format (Host -> Target) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 9.Data format (Target -> Host). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 10.Timings on SWIM pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 11.Debug module block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 12.STM8 Instruction Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 13.STM8 Debug Module Stall Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 14.STM8 DM Data Break Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 15.STM8 DM instruction break timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 16.STM8 DM step timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Doc ID 14024 Rev 25/37Debug system overview UM04706/37Doc ID 14024 Rev 21Debug system overview The STM8 debug system interface allows a debugging or programming tool to be connected to the MCU through a single wire bidirectional communication based on open-drain line.It provides non-intrusive read/write access to RAM and peripherals during program executionThe block diagram is shown in Figure 1.Figure 1.Debug system block diagramThe debug module uses the two internal clock sources present in the device, the LSI Low Speed Internal clock (usually in the range 30 kHz-200 kHz, depending on the product) one and the HSI High Speed Internal clock (usually in the range 10 MHz to 25 MHz, depending on the device). The clocks are automatically started when necessary.SWIM EntryLSI oscillator HSI oscillatorComm Layer Command DecodeDebug module (DM)STM8CorePeripherals SWIM pinP e r i p h e r a l B u sCPU BusSWIM RAMFlash/R A M B u sSTM8Data EEPROM调试系统总览UM0470Communication layerDoc ID 14024 Rev 27/372 Communication layerThe SWIM is a single wire interface based on asynchronous, high sink (8 mA), open-drain,bidirectional communication.While the CPU is running, the SWIM allows non-intrusive read/write accesses to be performed on-the-fly to the RAM and peripheral registers, for debug purposes.In addition, while the CPU is stalled, the SWIM allows read/write accesses to be performed to any other part of the MCU’s memory space (Data EEPROM and program memory).CPU registers (A, X, Y , CC, SP) can also be accessed. These registers are mapped in memory and can be accessed in the same way as other memory addresses. ●Register, peripherals and memory can be accessed only when the SWIM_DM bit is set. ●When the system is in HALT , WFI or readout protection mode, the NO_ACCESS flag in the SWIM_CSR register is set. In this case, it is forbidden to perform any accesses because parts of the device may not be clocked and a read access could return garbage or a write access might not succeed.The SWIM can perform a MCU device software reset.The SWIM pin can also be used by the MCU target application as a standard I/O port with some restrictions if you also want to use it for debug. The safest way is to provide a strap option on the application PCB. Figure 2.SWIM pin external connectionsSTM8Application I/OSWIM interface for toolsJumper selection fordebug purposesSWIM pin通信层即使CPU在运行,SWIM 允许不插入读取访问执行空中飞入(on-the-fly)到RAM和外设寄存器达到调试目的另外,当CPU停止时,SWIM允许读写MCU的其它部件的内存空间(DATA EEPROM 和 程序存储器)CPU 寄存器(A,X,Y,CC,SP)同样能读写,这些寄存器映射到内存并且能像访问其它内存地址一样访问它们寄存器,外设和内存只有在SWIM_DM位设置时能读写当系统在HALT,WFI或者读出保护模式时,NO_ACCESS 标志位(SWIM_CSR中)置位。

STM8S105xx 数据手册(中文)

4.1

STM8的中央处理单元 .........................................................................................................7

4.2

单线接口模块(SWIM)和调试模块(DM) ................................................................................7

自动唤醒定时器 2个看门狗定时器:窗口看门狗和独立看

门狗

通信接口 带有同步时钟输出的UART ,智能卡,

红外IrDA,LIN接口 SPI接口最高到8Mbit/s I2C接口最高到400Kbit/s

模数转换器(ADC) 10位,±1LSB的ADC,最多有10路通

道,扫描模式和模拟看门狗功能

5.1.1 备选功能重映射..........................................................................................................19

6 存储器和寄存器映像................................................................................................20

4.3

中断控制器 ..........................................................................................................................8

stm8s指令

Stm8s指令系统1.数据传送指令2.算术运算指令3.增量、减量指令4.逻辑运算指令5.位操作指令6.移位操作指令7.比较指令8.控制及转移指令数据传送指令LD,字节装载指令LDW,字装载指令(16位)LDF, 字装载指令(24位)MOV,字节传送指令EXG, 字节交换EXGW, X与Y交换SWAP, 半字节交换SWAPW,X或Y高低字节对调算术运算指令ADDADCADDWSUBSBCSUBWMULDIV增量/减量指令INCINCWDEC, 字节减1指令DECW 字减1指令逻辑运算指令CLR 清零CLRWCPLCPLW 求反NEG 取补NEGWAND 逻辑与OR 逻辑或XOR, 逻辑异或位操作指令“位所在存储单元地址,#位编号”。

1000H单元的b3位表示为“¥1000,#3”。

移位操作指令SLL 8位逻辑左移SLLW 16位逻辑左移SLA 8位算术左移SLAW 16算术左移SRL 8位逻辑右移SRLW 16逻辑右移SRA 8位算术右移SRAW 16算术右移RLC 字节循环左移RLCW 字循环左移RRC 字节循环右移RRCW 字循环右移RLWA 通过A的字循环左移RRWA 通过A的字循环右移比较指令CP,字节数值比较CPW,字数值比较BCP,逻辑比较控制及转移指令JP,00段内的绝对跳转(16地址)JPF,长跳转(24位目标地址)JRT/JRA,相对跳转CALL,00段内的绝对调用指令(16地址)CALLF, 长调用(24位目标地址)CALLR 相对调用RET,子程序返回指令RETF 长调用对应的子程序的返回指令IRET,中断返回指令条件跳转指令,P110.。

STM8S_简介

允许同时访问指令和数据 读写操作在同一个周期执行

cy

1 F

2 D F

3 E D

4 E D F

5

6

7

8

9

10

独立的指令和数据存储空间 (哈佛架构) , 大多数指令和操作的取址,译码, 执行可在单个机器周期完成。

0xC000 0xC001 0xC003 0xC005 0xC006 0xC007 0xC008 0xC00A

NEG A XOR A, #8 LD X, #20 LD (X), A INC X LD (X), A ADC A, 25 SRL A

1 1 1 1 1 1 1 1

E D E D E D F E D E D E

FETCH

DECODE

EXECUTE

STM8S MCU family

Marketing presentation

Sep 2008

STM8 Simply smarter

STM8S 芯片内部框图

主要性能 :

3.0-5.5伏 -40 to +125 °C 24MHz 内核工作频率 10K 次FLASH擦写次数 300K EEPROM擦写次数 4 种低功耗模式 (~5µ 停机模式) A 可校正的内部 RC 16MHz,精度 +/-1% 红外和智能卡接口 SWIM 快速编程 (<6s for 128KB) LQFP 80, 64, 48, 44, 32 VQFN 20, 32, 48 TSSOP 20

00 0000h 00 17FFh 00 4000h 00 47FFh 00 4800h 00 48FFh 00 5000h 00 6000h 00 67FFh 00 7F00h 00 8080h

stm8l中文参考手册(上)

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx 和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

表一、类型零件号控制器价值线低密度stm8l05xx设备:stm8l051x3 8KB Flash微控制器价值线中密度stm8l05xx设备:stm8l052x6微控制器与32闪光价值线高密度stm8l05xx设备:stm8l052x8 64-KB闪存微控制器低密度stm8l15x设备:stm8l151c2 / K2 / G2/F2,stm8l151c3 / K3 / G3 / F3微控制器与4KB或8KB Flash中密度stm8l15xx设备:stm8l151c4 / K4 / G4,微控制器stm8l151c6 / K6 / G6,stm8l152c4 / K4和stm8l152c6 / K6微控制器与16-KB或32闪光培养基+密度stm8l15xx设备:stm8l151r6和stm8l152r6微控制器与闪存(32比中密度器件广泛的外设范围)高密度stm8l15xx设备:stm8l151x8和stm8l152x8随着64-KB闪存微控制器(相同的外周设置为中等+)高密度stm8l16xx设备:stm8l162x8微控制器与闪存(相同的外周设置为64-KB高密度stm8l152设备加AES硬件加速器1 中央处理单元(CPU)。

STM8 SWIM通信协议和调试模块_图文.

STM8的 SWIM 通信协议(communication protocol 和调试模块介绍本手册为需要建立 STM8微控制器系列的编程, 测试或调试工具的开发者而写。

它解释了 STM8内核的调试结构。

STM8的调试系统包括以下两个模块:●DM :调试模块;●SWIM :单总线接口模块。

相关文档(Related documentation :●How to program STM8S and STM8A Flash program memory and data EEPROM (PM0051 (STM8Aversion is not published yet●How to program STM8L Flash program memory and data EEPROM (PM0054专业术语:DM :Debug ModeSWIM :Serial Wire Interface ModuleWFI :Wait For InterruptWFE :Wait For Event目录1. 调试系统概述 (1)2. 通信层 (2)3. 单总线接口模块(SWIM (3)3.1 操作模式 (3)3.2 SWIM 入口序列 (3)3.3 位格式 (5)3.4 SWIM 通信协议 (6)3.5 SWIM 命令 (7)3.6 SWIM 通信复位 (8)3.7 CPU 寄存器访问 (8)3.8 在停止模式下的 SWIM 通信 (9)3.9 物理层 (9)3.10 STM8的 SWIM 寄存器 (9)4. 调试模块(DM (12)4.1 介绍 (12)4.2 主要特点 (12)4.3 调试 (12)4.4 断点解码表 (14)4.5 软断点模式 (14)4.6 时序描述 (14)4.7 中止 (abort (15)4.8 数据断点 (15)4.9 指令断点(Instruction breakpoint ......................................................................15 4.10 单步模式 .................................................................................................................16 4.11 应用笔记 .. (16)4.12 DM 寄存器 (16)5. 常见问题解答 .........................................................................................................17 5.1 时序相关 (17)1. 调试系统概述STM8的调试系统接口允许一个调试或编程工具, 通过一根基于开漏接口的单总线双向 (bidirectional 通信线连接到 MCU 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM8的SWIM通信协议(communication protocol)和调试模块介绍本手册为需要建立STM8微控制器系列的编程,测试或调试工具的开发者而写。

它解释了STM8内核的调试结构。

STM8的调试系统包括以下两个模块:●DM:调试模块;●SWIM:单总线接口模块。

相关文档(Related documentation):●How to program STM8S and STM8A Flash program memory and data EEPROMversion is not published yet)(PM0051) (STM8A●How to program STM8L Flash program memory and data EEPROM (PM0054)专业术语:DM:Debug ModeSWIM:Serial Wire Interface ModuleWFI:Wait For InterruptWFE:Wait For Event目录1. 调试系统概述 (1)2. 通信层 (2)3. 单总线接口模块(SWIM) (3)3.1 操作模式 (3)3.2 SWIM入口序列 (3)3.3 位格式 (5)3.4 SWIM通信协议 (6)3.5 SWIM命令 (7)3.6 SWIM通信复位 (8)3.7 CPU寄存器访问 (8)3.8 在停止模式下的SWIM通信 (9)3.9 物理层 (9)3.10 STM8的SWIM寄存器 (9)4. 调试模块(DM) (12)4.1 介绍 (12)4.2 主要特点 (12)4.3 调试 (12)4.4 断点解码表 (14)4.5 软断点模式 (14)4.6 时序描述 (14)4.7 中止(abort) (15)4.8 数据断点 (15)4.9 指令断点(Instruction breakpoint) (15)4.10 单步模式 (16)4.11 应用笔记 (16)4.12 DM寄存器 (16)5. 常见问题解答 (17)5.1 时序相关 (17)1. 调试系统概述STM8的调试系统接口允许一个调试或编程工具,通过一根基于开漏接口的单总线双向(bidirectional)通信线连接到MCU。

它提供了非抢占式(non-intrusive)读写方式去访问RAM和外设,在程序执行期间(during program execution)。

方框图(The block diagram)如所示。

调试模块使用设备中的两个内部时钟源,LSI低速内部时钟(通常范围为20KHz-200KHz,视产品而定)和HSI高速内部时钟(通常范围为10MHz-25MHz,视产品而定)。

必要时,时钟会自动启动。

2. 通信层SWIM是一个基于异步(asynchronous),强灌电流(high sink)(8mA),开漏,双向通信(bidirectional communication)的单总线接口。

当CPU正在运行,出于调试目的,SWIM允许非抢占式(non-intrusive)读写访问,去执行on-the-flay到RAM和外设寄存器。

此外(In addition),当CPU停止(stalled),SWIM允许读写访问,去执行MCU存储空间的其它部分(数据EEPROM和程序存储器)。

CPU寄存器(A,X,Y,CC,SP)也可以被访问。

这些寄存器被映射在存储器中,而且可以以相同的方式去访问。

●仅仅当SWIM_DM位置一时,寄存器,外设和存储器才被访问。

●当系统处于停止(HALT),WFI或者读保护模式,SWIM_CSR寄存器的NO_ACCESS标志将置一。

在这种情况下,禁止(it is forbidden to)执行任何的访问,这时因为部分设备可能没有时钟驱动,读访问返回无用的数据(garbage),或者写访问不成功。

SWIM可以执行MCU软件复位操作SWIM引脚可以作为标准IO口用于MCU的目标应用,如果你也想将他用于调试,IO 口功能将会有一些限制(some restrictions)。

最安全的方式是在PCB设计时提供选择项(a strap option)。

3. 单总线接口模块(SWIM)3.1 操作模式上电复位后,SWIM复位,并且进入它的OFF模式。

1. OFF:在此模式下,SWIM引脚一定不能在应用中用作I/O口。

等待SWIM入口序列(entry sequence)或者应用软件打开I/O模式。

2. I/O:软件应用程序设置内核配置寄存器(CFG_GCR)的SWIM禁能位(SWD)(SWIM disable),可以进入此状态。

在此状态下,用户应用程序可以使用SWIM引脚作为标准I/O引脚,仅有的缺陷是无法使用该引脚的内置(bulit-in)调试功能。

一旦复位(In case of a reset),SWIM重新返回OFF模式。

3. ACTIVE:当处于OFF状态,SWIM引脚检测到一个特殊的序列,可以进入此模式。

在此状态下,通过SWIM引脚,主设备工具使用3个命令去控制STM8。

(SRST System Reset,ROTF Read On The Fly,WOTF Write On The Fly)注意:请注意,SWIM可以被设置为Active,而且可以在设备处于复位状态(NRST引脚被强制拉低)时进行通信。

3.2 SWIM入口序列POR(上电复位)后,SWIM一直处于OFF模式,SWIM引脚采样用于检测入口序列。

要实现这一机制,内部低速RC时钟在POR后自动运行,并且在SWIM处于OFF模式下一直保持。

如果SWIM引脚检测到入口序列之前,SWD bit is set,SWIM将工作在I/O模式。

一旦SWIM处于ACTIVE模式,写该位是无效的,并且SWIM仍然处于ACTIVE模式。

如果应用程序使用SWIM引脚作为I/O模式,应用程序会在软件代码的初始化部分将SWIM引脚设置为I/O模式(一般地,会在复位后执行)。

尽管在这种状态下,仍然有可能使得SWIM引脚处于ACTIVE模式,方法是:强制拉低RESET引脚,保持RESET引脚为0持续(duration)到SWIM入口序列完成。

在复位期间或者应用程序运行期间,只要SWIM处于OFF模式,任何时候,SWIM入口序列都会被检测。

如果SWIM引脚和复位引脚都被复用(are multiplexed)为I/O口,那么进入SWIM的ACTIVE状态的方法是:MCU设备掉电,再上电,并且保持MCU复位直到SWIM入口序列发送结束。

SWIM激活时序图如所示,图中每一段的描述如下。

1. 为了激活SWIM,SWIM引脚必须强制拉低16μs(在HSI下最少64个脉冲)。

2. 第一个脉冲后(总线当前为0),在SWIM的ACTIVE状态入口处,SWIM检测一个特殊序列以保证鲁棒性(guarantee robustness).SWIM入口序列式:4个1KHz的脉冲,紧接着4个2KHz的脉冲。

序列的频率很容易被内部RC检测到。

入口序列如所示。

注意序列以SWIM引脚拉高作为开始和结束标志。

3. 入口序列后,SWIM进入ACTIVE状态,HSI振荡器(oscillator)自动开启。

4. 延时过后,SWIM发出一个同步帧给主机。

同步帧描述:MCU的SWIM总线输出低电平,维持128个HSI时钟脉冲表示发出一个同步帧,用于调试主机对RC的测量。

一个高级调试主机可以重新校准(re-calibrate)它的时钟,来适应(adapt)MCU内部RC的频率。

5. 开始SWIM通信之前,SWIM线必须释放为高电平,以保证SWIM准备好通信(至少维持300ns)。

6. 写0A0H到SWIM_CSR寄存器:●Bit5置一,允许访问整个存储器和SRST命令●Bit7置一,掩盖内部复位源7. 释放加载配置字节的序列的复位。

等待1ms以保持稳定。

8. 一旦配置字节加载发生,且稳定时间到,CPU分段(in phase 8):●STM8S停止,且HSI = 16MHz(详见STM8S数据手册)●SWIM时钟为HSI/2 = 8MHz●SWIM在激活状态,在低速位格式(如所示)3.3 位格式位格式采用的是一种归零格式(Return-To-Zero format),它允许位同步。

两个通信速率可选。

在SWIM激活状态下,选择的是低速通信速率。

通过设置SWIM_CSR寄存器的HS位置一,选择高速通信速率。

当在复位阶段(during the RESET phase)进入SWIM模式时,配置项可能已经从非抢占式存储器中加载到相应的寄存器中。

任何内部或外部的复位都会触发加载配置项。

为了确保适当的系统行为,HS位直到配置项加载完成后才能置一。

在配置项加载结束后,SWIM_CSR寄存器的HSIT位被硬件置一。

3.3.1 高速位格式10个HSI振荡器脉冲生成一位。

位格式为:●2个时钟脉冲的0电平,接着8个时钟周期的1电平。

●8个时钟脉冲的0电平,接着2个时钟周期的1电平。

当SWIM收到一包数据时,它将解码:●1:检测到小于或等于4个连续低电平。

●0:检测到大于或等于5个连续低电平。

3.3.2 低速位格式22个HSI振荡器脉冲生成一位。

位格式为:●2个时钟脉冲的0电平,接着20个时钟周期的1电平。

●20个时钟脉冲的0电平,接着2个时钟周期的1电平。

当SWIM收到一包数据时,它将解码:●1:检测到小于或等于8个连续低电平。

●0:检测到大于或等于9个连续低电平。

3.4 SWIM通信协议当处于ACTIVE模式时,通信可以被主机或设备初始化。

每一个字节或命令之前都有一位头,用于仲裁主机和设备发起的通信。

主机的头是“0”,由于是开漏结构,可用于在仲裁时取得优先权。

若无数据传输,主机就可以开始传输。

主机发送的每个命令有以下组成:●1个命令(ROTF,WOTF or SWRST)包含:头:1Bit“0”b2-b0:3-bit 命令pb:奇偶位(parity bit):b(i)异或ack:应答位(1bit“1”)。

若检测到错误或为准备好,接收者必须发送非应答(NACK:1bit“0”)●若干数据包(WOTF下)包含:头:1Bit“0”b2-b0:8-bit 数据pb:奇偶位(parity bit):b(i)异或ack:应答位(1bit“1”)。

3.5 SWIM命令当总线空闲或者设备发送某个数据字节后,主机可以发送一个命令。

发送命令后,主机释放总线。

当SWIM准备好回应命令时,它启动(initiates)转换。

如果SWIM正在相应一个命令,主机发出新的命令,上个命令被取消,且新命令被解码,除WOTF外。

三个命令是有效的(available)。

如所示。

3.5.1 SRST:系统复位格式:一个命令从主机到目标板参数:无只有SWIM_CSR/SWIM_DM位置一,SRST命令产生一个系统复位。