第2章 微处理器结构(1)

微型计算机原理及应用第三版课后答案

微型计算机原理及应用第三版课后答案【篇一:《微型计算机原理及应用》课后习题答案】=txt>第一章1.1 解释题(1) 微处理器【解答】由大规模集成电路芯片构成的中央处理器(cpu),叫做微处理器。

(2) 微型计算机【解答】以微处理器为基础,配以内存储器、输入输出接口电路、总线以及相应的辅助电路而构成的计算机裸机,叫做微型计算机。

(3) 微型计算机系统【解答】微型计算机系统由硬件系统和软件系统组成。

即由微型计算机、配以相应的外部设备(如打印机、显示器、键盘、磁盘机等),再配以足够的软件而构成的系统。

(4) 单板机【解答】将微处理器、ram、rom以及i/o接口电路,再配上相应的外设(如小键盘、led显示器等)和固化在rom中的监控程序等,安装在一块印刷电路板上构成的微型计算机系统称为单板机。

(5) 运算器【解答】运算器是直接完成各种算术运算、逻辑运算的部件,主要由alu(arithmetic and logic unit,算术逻辑部件)、通用寄存器、标志寄存器等组成。

(6) 地址总线【解答】地址总线是cpu对内存或外设进行寻址时,传送内存及外设端口地址的一组信号线。

地址总线的条数多少决定了cpu的寻址能力。

(7) 数据总线【解答】数据总线是cpu与内存或外设进行信息交换时,所用的一组数据信号线。

它决定了cpu一次并行传送二进制信息的位数,反映出cpu的“字长”这个重要性能指标。

(8) 控制总线【解答】控制总线是在cpu与外部部件之间传送控制信息(如读/写命令、中断请求命令等)的一组信号线。

1-2 单片机应包括哪些基本部件?其主要应用于哪些领域?【解答】一般单片机芯片中包括微处理器、ram、rom、i/o接口电路、定时器/计数器,有的还包括a/d、d/a转换器等。

其主要应用于智能化仪器仪表及工业控制领域。

1-3 按图1-11和图1-12,写出取第二条指令操作码和执行第二条指令的过程。

【解答】1) ip的值(002h)送入地址寄存器ar;2) ip的内容自动加1,变为003h;3) ar将地址码通过地址总线送到存储器的地址译码器,经译码后选中002h单元;4) 微处理器给出读命令;5) 所选中的002h单元内容04h送上数据总线db;6) 数据总线db上的数据04h送到数据寄存器dr;7) 因是取指操作,取出的是指令操作码04h,即由dr送入指令寄存器ir;8) ir中的操作码经指令译码器id译码后,通过pla发出执行该指令的有关控制命令。

【教学课件】第2章 8086微处理器

控制 电路

局部总线 接口

SYSB/RESB

1

20

2

19

3

18

4

17

5

8289 16

6

15

7

14

8

13

9

12

10

11

INIT

BCLK BREQ BPRN BPRO BUSY CBRQ

总线仲裁 信号

AEN

V CC S1 S0 CLK

LOCK

CRQLCK ANYRQST

AEN CBRQ BUSY

2021/8/17

DEN CEN

INTA IORC AIOWC IOWC

2021/8/17

23

2.总线仲裁控制器8289

仲裁电路

状态

S2

信号

S1

S0

状态 译码器

多路总线 接口

控制 输入

LOCK CLK

CRQLCK

RESB ANYRQST

IOB

S2 IOB

RESB BCLK INIT BREQ BPRO BPRN

GND

数据总线

2021/8/17

S0

S1

S2

INTR R Q / G T0

R Q / G T1

8288 总线控制器

IN T A

8259A 及有关电路

控制总线 中 断 请 求

22

1.总线控制器8288

状态

S2

信号

S1

S0

状态 译码器

控制 输入

CLK

AEN CEN IOB

控制 电路

命令 信号 发生器

控制信号 发生器

2.3.1 最小模式和最大模式的概念

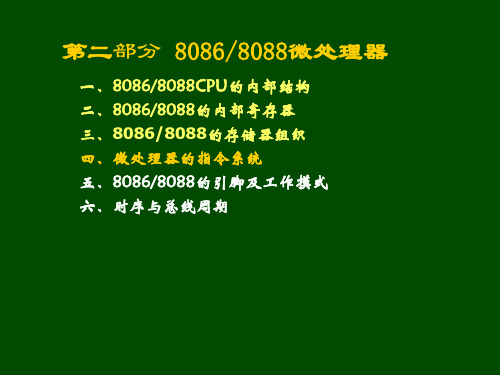

第二章 8086微处理器

第二章8086/8088微处理器及其系统结构内容提要:1.8086微处理器结构:CPU内部结构:总线接口部件BIU,执行部件EU;CPU寄存器结构:通用寄存器,段寄存器,标志寄存器,指令指针寄存器;CPU引脚及其功能:公用引脚,最小模式控制信号引脚,最大模式控制信号引脚。

2.8086微机系统存储器结构:存储器地址空间与数据存储格式;存储器组成;存储器分段。

3.8086微机系统I/O结构4.8086最小/最大模式系统总线的形成5.8086CPU时序6.最小模式系统中8086CPU的读/写总线周期7.微处理器的发展学习目标1.掌握CPU寄存器结构、作用、CPU引脚功能、存储器分段与物理地址形成、最小/最大模式的概念和系统组建、系统总线形成;2.理解存储器读/写时序;3.了解微处理器的发展。

难点:1.引脚功能,最小/最大模式系统形成;2.存储器读/写时序。

学时:8问题:为什么选择8088/8086?•简单、容易理解掌握•与目前流行的P3、P4向下兼容,形成x86体系•16位CPU目前仍在大量应用思考题1、比较8086CPU与8086CPU的异同之处。

2、8086CPU从功能上分为几部分?各部分由什么组成?各部分的功能是什么?3、CPU的运算功能是由ALU实现的,8086CPU中有几个ALU?是多少位的ALU?起什么作用?4、8086CPU有哪些寄存器?各有什么用途?标志寄存器的各标志位在什么情况下置位?5、8086CPU内哪些寄存器可以和I/O端口打交道,它们各有什么作用?6、8086系统中的物理地址是如何得到的?假如CS=2400H,IP=2l00H,其物理地址是多少?思考题1.从时序的观点分析8088完成一次存储器读操作的过程?2.什么是8088的最大、最小模式?3.在最小模式中,8088如何产生其三总线?4.在最大模式中,为什么要使用总线控制器?思考题1.试述最小模式下读/写总线周期的主要区别。

第二章-8086微处理器

答案:A

思考题

8086/8088的状态标志有 A)3 B)4 C)5 答案:D 个。 D)6

思考题

8086/8088的控制标志有 A)3 B)4 C)5 答案:A 个。 D)6

三、引脚信号和功能(图2-5 )

8086总线周期的概念: 为了取得指令或传送数据,就需要CPU的总线接 口单元(BIU)执行一个总线周期。 一个最基本的总线周期由4个时钟周期组成。 习惯上将4个时钟周期分别称为4个状态,即T1状 态、T2状态、T3状态和T4状态。 图2-17

2.方向标志DF(Direction Flag) 用于串操作指令中的地址增量修改(DF =0)还是减量修改(DF=1)。 STD使DF=1 CLD使DF=0

(三)标志寄存器-控制标志(续)

3.跟踪标志TF(Trap Flag) 若TF=1,则CPU按跟踪方式(单步方式) 执行程序,否则将正常执行程序。

思考题

指令队列的作用是 A)暂存操作数地址 。 B)暂存操作数

C)暂存指令地址

D)暂存预取指令 答案:D

思考题

8086的指令队列的长度是 A)4个 B)5个 C)6个 D)8个 字节。

答案: C

思考题

8088的指令队列的长度是 A)4个 B)5个 C)6个 D)8个 字节。

答案:A

思考题

第二章 8086/8088微处理器

8086/8088微处理器的结构 8086/8088典型时序分析

简 介

8086:16位微处理器 数据总线宽度16位:可以处理8位或16位数据 地址总线宽度20位:可直接寻址1MB存储单元和 64KB的I/O端口 8088:准16位处理器 内部寄存器及内部操作均为16位,外部数据总线8位 8088与8086指令系统完全相同,芯片内部逻辑结构、芯片引 脚有个别差异。 设计8088的目的主要是为了与Intel原有的8位外围接口芯片 直接兼容

微机原理第02章1

第2章: 溢出和进位的对比

例1:3AH+7CH=B6H

无符号数运算: 58+124=182 范围内,无进位 有符号数运算: 58+124=182 范围外,有溢出

例2:AAH+7CH=(1)26H

无符号数运算: 170+124=294 范围外,有进位 有符号数运算: -86+124=28 范围内,无溢出

常用来存放双字长数据的高16位,或存放外设端口地址

第2章:(2)变址寄存器

16位变址寄存器SI和DI 常用于存储器变址寻址方式时提供地址

SI是源地址寄存器(Source Index) DI是目的地址寄存器(Destination Index)

在串操作类指令中, SI 、 DI 还有较特殊的 用法 现在不必完全理解,以后会详细展开

第2章:溢出和进位的应用场合

处理器对两个操作数进行运算时,按照无 符号数求得结果,并相应设置进位标志 CF; 同时,根据是否超出有符号数的范围设置 溢出标志OF 应该利用哪个标志,则由程序员来决定。 也就是说,如果将参加运算的操作数认为 是无符号数,就应该关心进位;认为是有 符号数,则要注意是否溢出

第2章:符号标志SF(Sign Flag)

运算结果最高位为1,则SF=1; 否则SF=0

有符号数据用最高有效位表示数据的符号 所以,最高有效位就是符号标志的状态

3AH+7CH=B6H,最高位D7=1:SF=1

84H+7CH=(1)00H,最高位D7=0:SF=0

第2章:奇偶标志PF(Parity Flag)

第2章:辅助进位标志AF(Auxiliary Carry Flag)

运算时D3位(低半字节)有进位或

借位时,AF=1;否则AF=0

这个标志主要由处理器内部使用, 用于十进制算术运算调整指令中, 用户一般不必关心 3AH+7CH=B6H,D3有进位:AF=1

微机原理第二章8086微处理器

▪ 这些引脚就是微处理器级总线。微处理器通过微处理器 级总线沟通与外部部件和设备之间的联系。这些总线及 其信号必须完成以下功能:

▪ (1)和存储器之间交换信息; ▪ (2)和I/O设备之间交换信息; ▪ (3)为了系统工作而接收和输出必要的信号,如输入

▪ 时钟信号输入端。19 CLK(输入) ▪ 8086和8088为5MHz。 ▪ 8086/8088的CLK信号必须由8284A时钟发生器产生。 ▪ 微处理器是在统一的时钟信号CLK控制下,按节拍进行

工作的。

2021/6/12

16

8086/8088微处理器——微处理器的引脚功能

▪ 工作方式控制线 33

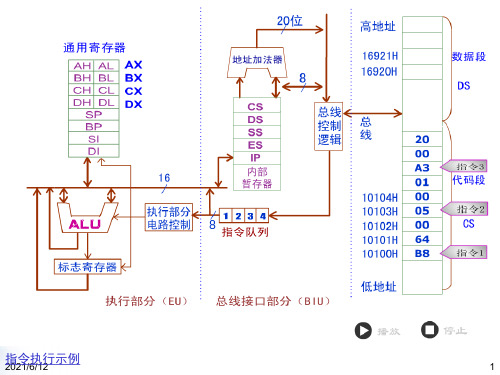

指令执行示例

2021/6/12

1

第二章:8086/8088微处理器

1. 微处理器ห้องสมุดไป่ตู้结构 2. 微处理器的内部寄存器 3. 微处理器的引脚功能 4. 微处理器的存储器组织 5. 最大模式和最小模式 6. 微处理器的时序

2021/6/12

2

2021/6/12

▪ 存储器分段

▪ 由于CPU内部的寄存器都是16位的,为了

2021/6/12

7

第二章:8086/8088微处理器

1. 微处理器的结构 2. 微处理器的内部寄存器 3. 微处理器的引脚功能 4. 微处理器的存储器组织 5. 最大模式和最小模式 6. 微处理器的时序

2021/6/12

8

8086/8088微处理器——微处理器的引脚功能

▪ 一、微处理器的外部结构

时钟脉冲、复位信号、电源和接地等。

第2章8086微处理器1-2

忙碌

1)CPU执行指令时总线处于空闲状态 ) 执行指令时总线处于空闲状态 2)CPU访问存储器 存取数据或指令 时要等待总线操作的完成 访问存储器(存取数据或指令 ) 访问存储器 存取数据或指令)时要等待总线操作的完成 缺点: 缺点:CPU无法全速运行 无法全速运行 解决:总线空闲时预取指令, 解决:总线空闲时预取指令,使CPU需要指令时能立刻得到 需要指令时能立刻得到

6

结论

指令预取队列的存在使EU和 指令预取队列的存在使 和BIU两个部 两个部 分可同时进行工作, 分可同时进行工作,从而 提高了CPU的效率; 降低了对存储器存取速度的要求

7

8088/8086 CPU的特点

采用并行流水线工作方式 对内存空间实行分段管理: 对内存空间实行分段管理:

每段大小为16B~ 每段大小为16B~64KB 16B 用段地址和段内偏移实现对1MB空间的寻址 用段地址和段内偏移实现对1MB空间的寻址 设置地址段寄存器指示段的首地址

支持多处理器系统; 支持多处理器系统; 片内没有浮点运算部件, 片内没有浮点运算部件,浮点运算由数学协处 理器8087支持(也可用软件模拟) 理器 支持(也可用软件模拟) 支持 注:80486DX以后的CPU均将数学协处理 器作为标准部件集成到CPU内部

8

二、8086CPU的内部结构

8086内部由两部分组成: 内部由两部分组成: 内部由两部分组成 执行单元(EU) 执行单元( ) 总线接口单元(BIU) 总线接口单元( )

2

指令预取队列(IPQ)

指令的一般执行过程: 指令的一般执行过程: 取指令 指令译码 读取操作数 执行指令 存放结果

3

串行工作方式:

8086以前的CPU采用串行工作方式: 8086以前的CPU采用串行工作方式: 以前的CPU采用串行工作方式

微型计算机原理及应用第三版课后答案

微型计算机原理及应用第三版课后答案【篇一:《微型计算机原理及应用》课后习题答案】=txt>第一章1.1 解释题(1) 微处理器【解答】由大规模集成电路芯片构成的中央处理器(cpu),叫做微处理器。

(2) 微型计算机【解答】以微处理器为基础,配以内存储器、输入输出接口电路、总线以及相应的辅助电路而构成的计算机裸机,叫做微型计算机。

(3) 微型计算机系统【解答】微型计算机系统由硬件系统和软件系统组成。

即由微型计算机、配以相应的外部设备(如打印机、显示器、键盘、磁盘机等),再配以足够的软件而构成的系统。

(4) 单板机【解答】将微处理器、ram、rom以及i/o接口电路,再配上相应的外设(如小键盘、led显示器等)和固化在rom中的监控程序等,安装在一块印刷电路板上构成的微型计算机系统称为单板机。

(5) 运算器【解答】运算器是直接完成各种算术运算、逻辑运算的部件,主要由alu(arithmetic and logic unit,算术逻辑部件)、通用寄存器、标志寄存器等组成。

(6) 地址总线【解答】地址总线是cpu对内存或外设进行寻址时,传送内存及外设端口地址的一组信号线。

地址总线的条数多少决定了cpu的寻址能力。

(7) 数据总线【解答】数据总线是cpu与内存或外设进行信息交换时,所用的一组数据信号线。

它决定了cpu一次并行传送二进制信息的位数,反映出cpu的“字长”这个重要性能指标。

(8) 控制总线【解答】控制总线是在cpu与外部部件之间传送控制信息(如读/写命令、中断请求命令等)的一组信号线。

1-2 单片机应包括哪些基本部件?其主要应用于哪些领域?【解答】一般单片机芯片中包括微处理器、ram、rom、i/o接口电路、定时器/计数器,有的还包括a/d、d/a转换器等。

其主要应用于智能化仪器仪表及工业控制领域。

1-3 按图1-11和图1-12,写出取第二条指令操作码和执行第二条指令的过程。

【解答】1) ip的值(002h)送入地址寄存器ar;2) ip的内容自动加1,变为003h;3) ar将地址码通过地址总线送到存储器的地址译码器,经译码后选中002h单元;4) 微处理器给出读命令;5) 所选中的002h单元内容04h送上数据总线db;6) 数据总线db上的数据04h送到数据寄存器dr;7) 因是取指操作,取出的是指令操作码04h,即由dr送入指令寄存器ir;8) ir中的操作码经指令译码器id译码后,通过pla发出执行该指令的有关控制命令。

第二章 微处理器

8086CPU的引脚 的引脚——控制总线 的引脚 控制总线

微 机 原 理 汇 编 接 口 技 术

BHE/S7

高8位数据允许/状态

ALE

地址锁存允许

MN/MX

最小/最大模式

DEN

数据允许

RD

读选通

DT/R

数据发送/接收

WR

写选通

READY

准备就绪

第 14 页

8086CPU的引脚 的引脚——控制总线 的引脚 控制总线

第 34 页

堆栈操作

微 机 原 理 汇 编 接 口 技 术

堆栈是按照“先进后出”原则组织的存储区域, 堆栈是按照“先进后出”原则组织的存储区域,堆栈的大小最大为 64KB 堆栈由堆栈段寄存器SS和堆栈指针寄存器 来寻址 堆栈由堆栈段寄存器 和堆栈指针寄存器SP来寻址,SS给出堆栈 和堆栈指针寄存器 来寻址, 给出堆栈 段的段基址, 指向当前栈顶 指向当前栈顶——段基址到栈顶的偏移量 段的段基址,SP指向当前栈顶 段基址到栈顶的偏移量 栈底为堆栈空间的高地址单元,栈顶为低地址单元。 栈底为堆栈空间的高地址单元,栈顶为低地址单元。 堆栈操作以字为单位。 堆栈操作以字为单位。 数据进栈,栈顶向低地址方向浮动,高位字节存入高地址单元, 数据进栈, 数据进栈 栈顶向低地址方向浮动,高位字节存入高地址单元, 低位字节存入低地址单元 数据出栈,栈顶向高地址方向浮动,低位字节弹到目的操作数 数据出栈, 数据出栈 栈顶向高地址方向浮动, 的低位, 的低位,高位字节弹到目的操作数的高位

外部8位数据总线 4 4字节指令队列 IO/M 准十六位CPU

8086

外部16位数据总线 6 6字节指令队列 M/IO 十六位CPU

第 16 页

微机原理2-1:8088CPU内部结构、寄存器组、存储器组织

栈段和附加段。

段寄存器即是存放各个逻辑段段首地址的寄 存器。

23

存储器的分段管理

8088有20条地址线, 20=1MB, 最大可寻址空间为 2 可寻址的地址范围为 00000H~FFFFFH 该地址称物理地址 硬件用 20位的物理地址来对存储单元进行寻 址

24

存储器的分段管理

由于 8088 中的地址寄存器都是 16 位的,用 户不能直接使用20位的物理地址,编程时需 要使用逻辑地址来寻址存储单元。 物理地址 14700H 逻辑地址由两个16位数构成,其形式为: 逻辑地址 1460H:100H 段的起始地址 : 段内的偏移地址 (16位段地址) :( 16位偏移量)

分隔符

7

②指针和变址寄存器 共BP、SP、SI、DI四个 BP:基址指针寄存器Base Pointer ,默认表示

堆栈段基地址;

SP:堆栈指针寄存器Stack Pointer,指示栈顶 SI:源变址寄存器Source Index DI:目的变址寄存器Destination Index

8

2、标志寄存器 标志寄存器( FR )是 一个 十六位的 寄存器,但只利用了其中的9位:六个条 件标志和三个控制标志。

CLI 指令复位中断标志:IF=0

STI 指令置位中断标志:IF=1

20

陷阱标志TF(Trap Flag)

用于控制处理器是否进入单步执行方式: 设置TF=0,处理器正常工作; 设置 TF=1,处理器每执行一条指令就中断一次, 中断编号为 1 (称单步中断), TF 也被称为单 步标志。 单步执行和单步调试

注意: PF 标志仅反映最低 8 位中“ 1 ”的个数

第2章 8086微处理器1

例3 已知逻辑地址,指出下列存储器地址的段内偏 移量、段基址、物理地址。 1)1123H:0015H 2)1124H:0005H

一个物理地址可以对应多个逻辑地址

例如:设当前有效的代码段、数据段、堆栈段、附加段的段基址分别 为1066H、251BH、900CH、F001H,则各段在内存中的分配情况如 图2-5所示。

VCC AD15 A16/S3 A17 /S4 A18 /S5 A19 /S6 (HIGH) (SSO) MN/MX RD RQ/GT0 (HOLD) RQ/GT1 (HLDA) LOCK (WR) S2 (IO/M) S1 (DT/R) S0 (DEN) QS0 (ALE) QS1 (INTA) TEST READY RESET

六个状态标志含义如下: 1.进位标志CF或C 运算结果的最高位产生进位或借位时,则 CF=1,否则CF=0(字节操作D7、字操作D15、 双字D31) 2.奇偶标志PF 运算结果中1的个数为偶数,则PF=1,否 则PF=0 3.辅助进位标志AF 运算时当 D3 向D4 有进位或有借位时 ,则 AF=1,否则AF=0

DS:数据段寄存器 ES:附加段寄存器

数据段和附加段用来存放操作数

SS:堆栈段寄存器

堆栈段用于存放返回地址,保存寄存器内容, 传递参数

3、控制寄存器

IP:指令指针寄存器,其内容为下一条 要执行的指令的偏移地址 FLAGS:标志寄存器

状态标志:存放运算结果的特征

控制标志:控制某些特殊操作

四、存储器寻址

物理地址

8086:20根地址线,可寻址220(1MB)

个存储单元,1M字节的存储器单元编 址为00000H~FFFFFH(16进制) CPU送到AB上的20位的地址称为物理 地址

第2章 Pentium系列微处理器的基本结构

SSE指令集包括了70条指令,其中包含提高3D图形运算效 率的50条SIMD(单指令多数据技术)浮点运算指令、12 条MMX 整数运算增强指令、8条优化内存中连续数据 块传输指令。

与P2时代的MMX相比,SSE也是在原来的处理器指令集 的基础上添加的扩展指令集,都是SIMD(单指令多数据) 指令,不同的是他们处理的数据类型不同. MMX只能在 整数上支持SIMD,而SSE指令增加了单精度浮点数的 SIMD支持.MMX可以进行同时对2个32位的整数操作, 而SSE可以同时对4个32位的浮点数操作。MMX和SSE 的一个主要的区别是MMX并没有定义新的寄存器,而 SSE定义了8个全新的128位寄存器,每个寄存器可以同 时存放4个单精度浮点数(每个32位长),

② 空间并行---指资源重复。实现形式主要为 多处理器系统和多计算机系统;

③ 时间并行+空间并行---时间重叠和资源重 复的综合应用,例:超标量流水技术。

流水工作方式:将一个计算任务细分成若干

个子任务,每个子任务由专门的部件处理,多 个计算任务依次进行并行处理。

流水线中主要存在三种相关冲突,会使流水线 发生断流,而不能充分发挥作用,因此需采 取 相应的技术对策。

2.MMX

8个MMX寄存器MM0—MM7的宽度为64位,但 它们没有单独设置,而是借用浮点处理单元中的8 个(80位)数据寄存器,它是通过使用“别名”的办 法来实现的。即浮点单元的8个数据寄存 器被浮点 指令看成ST0—ST7,被MMX指令看成是MM0— MM7。

这样,8个字节或4个字或2个双字被打包装入一 个64位的MMX寄存器,一旦执行一条MMX指令时, 将所有这些8个、4个或2个的数据同时取出,进行 数学运算或逻辑操作,最后结果写入MMX寄存器。 事实上,这种运算处理过程是一种并行处理过程, 故称为SIMD(单指令 多数据)的并行处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

外设:打印机、键盘、显示器等等。

§2.2 8086CPU的功能结构

一、8086CPU的内部结构

8086CPU是典型的16位微处理器,它具有16位的

内部数据总线和16位的外部数据总线。

8086CPU的内部结构框图如下所示。

8086CPU内部结构框图

从大的结构和功能上讲,8086可分为两个部分,即 执行单元(EU,Execution Unit)

通道,按所传送信息的不同类型,可分为:

地址总线AB:传送地址信息 数据总线DB :传送数据信息

控制总线CB :传送控制信息

三、微型计算机系统

以微型计算机为主体,配上系统软件和外设之后,就 成了微型计算机系统。

系统软件:是使用、管理计算机本身的软件。 软件 应用软件:是为解决某个实际问题而编制的程序。

① CF(Carry Flag)进位标志 CF=1:记录运算时从最高有效位产生进位值。 CF=0:记录运算时从最高有效位不产生进值。 ② PF(Parity Flag)奇偶标志

PF=1:

PF=0:

结果操作数低8位中有偶数个1。

结果操作数低8位中有奇数个1。

用来为机器中传送信息时可能产生的代码出现情况提供检验 条件。

队列中。它们采用 “先进先出”的原则,按顺序存放,并按

顺序取到 EU 中去执行。

其操作将遵循下列原则:

(1)取指时,每当指令队列缓冲器中存满1条指令后,EU就立即开始执

行。 (2)指令队列缓冲器中只要空出2个指令字节时,BIU便自动执行取指操

作,直到填满为止。

(3)在EU执行指令的过程中,指令需要对存储器或I/O设备存取数据时, BIU将在执行完现行取指的存储器周期后的下一个存储器周期,对指定的 内存单元或I/O设备进行存取操作,交换的数据经BIU由EU进行处理。 (4)当 EU执行完转移、调用和返回指令时,则要清除指令队列缓冲器, 并要求BIU从新的地址重新开始取指令,新取的第1条指令将直接经指令 队列送到EU 去执行,随后取来的指令将填人指令队列缓冲器。

① ② ③ ④ ⑤ ⑥ ⑦ ⑧

§2.1 微型计算机系统的组成

微型计算机系统

微处理器

微型计算 机

运算器 控制器

寄存器组 内存储器 输入输出 接口电路 外部设备 软件 总线

微处理器(CPU)、微型计算机(主机) 与微型计算机系统三

者的关系:

ALU 微处理器 微型计算机 累加器、寄存器 控制器 系 统 总 线 : AB、 CB、 DB I/O接 口 : 串 /并 行 接 口 等 微机系统 存 贮 器 : ROM、 RAM 系 统 软 件 : OS、 汇 编 、 编 译 等 外 设 : 打 印 机 、 键 盘 、 CRT等

第二章

微型计算机的组成及微处理器结构

教学目的及要求

掌握微型计算机系统的组成及主要技术性能指标 掌握8086CPU的功能结构; 掌握状态标志和控制标志的意义; 掌握8086CPU的存储器组织及存储器管理; 掌握逻辑地址和物理地址; 理解8086的地址数据引脚和读写控制引脚; 掌握最小工作模式的典型配置; 理解并掌握总线的时序

由于BIU与EU是分开并独立工作的,因此,在一 般情况下,CPU 执行完1条指令后就可以立即执行下1 条指令,而不需要像以往8位CPU那样重复地进行先取

指令和后执行指令的串行操作。16位CPU这种并行重

叠操作的特点,提高了总线的信息传输效率和整个系 统的执行速度。

二、8086CPU的寄存器结构

内部结构?

一、 微处理器

CPU在内部结构上包含下面Biblioteka 些部分:· 算术逻辑部件;

· 累加器和通用寄存器组; · 程序计数器(指令指针)、指令寄存器和译码器; · 时序和控制部件。

CPU功能:

· 可以进行算术和逻辑运算 · 可保存较少量数据 · 能对指令进行译码并执行规定的动作 · 能和存储器、外设交换数据 · 提供整个系统所需要的定时和控制 · 可以响应其他部件发来的中断请求

(3)变址寄存器(SI 、 DI) SI——Source Index Register 源变址寄存器。 DI——Destination Index 目的变址寄存器。

使用场合:常用于变址寻址。

• 一般与DS联用,用来确定数据段中某一存储单元的地址,

SI 、DI具有自动增量和自动减量功能. 例:MOV AX, [SI]

DF=1,每次串处理操作后使变址寄存器SI和DI减量,使串处理从高地址向 低地址方向处理。

DF=0,每次串处理操作后使变址寄存器SI和DI增量,使串处理从低地址向

高地址方向处理。

DF方向标志位是在串处理指令中控制处理信息的方向用的。

② IF(Interupt Flag)中断标志 位

IF=1, 允许外部可屏蔽中断。CPU可以响应可屏蔽中断请求。 IF=0, 关闭中断。CPU禁止响应可屏蔽中断请求。

指令在指令队列中排队;

在一条指令执行完成后,就可以立即执行下一条指令,减少 CPU为取指令而等待的时间,提高CPU的利用率和整个运行速度。

BIU: EU:

取指

取指

取指

取指

得到数据

等待

执行

执行

执行

执行

对于8080与8085及较早的8位微处理器:

程序执行由取指令和执行指令的循环来完成的,每条指令 执行完后CPU必须等待到下条指令取出来后才能执行。

例:MUL BX ; (AX)(BX)(DX)(AX)

(2)指针寄存器(SP、BP )

SP(stack pointer)——堆栈指针寄存器

用来指示栈顶的偏移地址, 必须与SS段寄存器联合使用确 定实际地址。

BP(base pointer)——基址指针寄存器 可以与SS寄存器联合使用来确定堆栈段中某一存储器单 元地址。

取指 执行 取指 执行 ... ... 取指 执行

时间坐标

8086/8088微处理器:

BIU和EU分开,取指和执行可以重迭, 大大减少了等待取指所需的时间,提高CPU的 利用率。

指令队列缓冲器:

8086的指令队列为6个字节。在EU执行指令的同时,BIU 从内存中取下面1条或几条指令,取来的指令就依次放在指令

二、微型计算机

微型计算机由CPU、存储器、输入输出接口电路和系 统总线构成。

1 、内部存储器:按照读写方式的不同,分为 ROM 和

RAM两种类型;

2 、输入 / 输出接口电路是外围设备与微型计算机之间 的连接电路,在两者之间进行信息交换的过程中,起 暂存、缓冲、类型变换及时序匹配的作用; 3、总线是CPU与其它各功能部件之间进行信息传输的

1、通用寄存器

(1)数据寄存器 AX、BX、CX、DX 作为通用寄存器。

用来暂存计算过程中所用到的操作数,结果或其它信息。

访问形式:可以用16位的访问;或者可以用字节(8位)形式访问。

它们的高8位记作 : 它们的低8位记作 : AH 、BH 、CH 、DH 。 AL 、BL 、CL 、DL 。

AX——(Accumulator)作为累加器。

它是算术运算的主要寄存器,所有I/O指令都使用这一寄存器与外 部设备交换数据。

例:IN

AL, 20H

OUT 30H ,AX

BX—— Base 用作基址寄存器使用。

在计算内存储器地址时,经常用来存放基址。

例:MOV AX, [BX+03H]

CX——Count可以作计数寄存器使用。

在循环LOOP指令和串处理指令中用作隐含计数器。

2、段寄存器

段寄存器: 4个16位段寄存器CS、DS、SS、ES。 用来识别当前可寻址的四个段,不可互换使用。

CS —— Code Segment Register 代码段寄存器

用来存放当前代码段基地址(程序一般放在代码段)。 DS —— Data Segment Register数据段寄存器 用来存放当前数据段寄存器基地址。 SS —— Stack Segment Register堆栈段寄存器,

•

状态信息:

由中央处理器,根据计算结果自动设置的,机器提供

了设置状态信息指令,必要时,程序员可以用这些指令来建 立状态信息。

例1:执行两个数的加法,分析对标志位的影响。

0 + 0 0 0 1 1 0 1 0 0 0 0 1 1 1 0 0 0 1 0 0 0 0 1 0 1 1 0 0 0 1 1

例:MOV CX , 200H

AGAIN:

……

…… LOOP AGAIN ;(CX)-1(CX),结果0转AGAIN

DX——Data可以作为数据寄存器使用。

一般在双字长乘除法运算时,把DX和AX组合在一起存放一个双 字长(32位)数,DX用来存放高16位;对某些I/O操作DX可用来存放I/O的端口 地址。

③

AF(Auxiliary Carry Flag)辅助进位标志

AF=1:记录运算时第3位(半个字节)产生进位值。 AF=0:记录运算时第3位(半个字节)不产生进位值。

④

ZF(Zero Flag)零标志 ZF=1:运算结果为0。

ZF=0:运算结果不为0。

⑤SF(Sign Flag)符号标志 SF=1:记录运算结果的符号为负。 SF=0:记录运算结果的符号为正。

0

1

0

1

0

1

0

1

0

1

0

1

1

1

1

0

标志:

最高位没有进位

低8位中1的个数为奇数个 第三位向第四位无进位

∴ CF=0

∴ PF=0; ∴ AF=0;

运算结果本身≠0

运算结果最高位为0

∴ ZF=0

∴ SF=0;

次高位向最高位没有进位 ,最高位向前没有进位 ∴OF=0。