模拟集成电路设计流程课件

合集下载

模拟集成电路版图设计基础专题培训课件

PMOS管,做在N阱中,沟 道为N型,源漏为P型

2) 包括层次:

NWELL,N阱 PIMP,P+注入 DIFF,有源区 Poly,栅 M1,金属 CONT,过孔

3) MOS管的宽长确定

PMOS版图

五、版图的组成

1.1MOS管

反向器

器件剖面图及俯视图

器件版图

五、版图的组成

(1)对P型硅片进行氧化, 生成较 薄的一层Si3N4, 然后进行光刻, 刻出有源区后进行场氧化。

紫外线照射

掩膜版 掩膜版图形

P-Si

Si3 N4

P-Si

Si3 N4

P-Si

SiO2

集成电路工艺基础

P-Si (b)

P-Si (c)

P-Si

N+ (d )

多晶硅 0.5~ 2m

(2) 进行氧化(栅氧化), 在暴露的硅表面生成一 层严格控制的薄SiO2层。 (3) 淀积多晶硅, 刻蚀多晶硅以形成栅极及互连线 图形。

模拟集成电路版图设计基础

目录

• 前言 集成电路工艺基础 • 一、什么是版图? • 二、版图的意义 • 三、版图与线路图、工艺的关系 • 四、版图设计的过程 • 五、版图的组成 • 六、版图的层次 • 七、如何绘制版图 • 八、版图验证与检查 • 九、版图的艺术

集成电路工艺基础

P-Si P-Si

光刻胶 Si3 N4

五、版图的组成

版图其实就是另一种形式的电路图,作为电路图最 基本的有两大组成部分

1.器件(常见)

1 MOS管 2 电阻 3 电容

2.互连

2.2.1金属(第一层金属,第二层金属……) 2.2.2通孔

五、版图的组成

1.1MOS管

2) 包括层次:

NWELL,N阱 PIMP,P+注入 DIFF,有源区 Poly,栅 M1,金属 CONT,过孔

3) MOS管的宽长确定

PMOS版图

五、版图的组成

1.1MOS管

反向器

器件剖面图及俯视图

器件版图

五、版图的组成

(1)对P型硅片进行氧化, 生成较 薄的一层Si3N4, 然后进行光刻, 刻出有源区后进行场氧化。

紫外线照射

掩膜版 掩膜版图形

P-Si

Si3 N4

P-Si

Si3 N4

P-Si

SiO2

集成电路工艺基础

P-Si (b)

P-Si (c)

P-Si

N+ (d )

多晶硅 0.5~ 2m

(2) 进行氧化(栅氧化), 在暴露的硅表面生成一 层严格控制的薄SiO2层。 (3) 淀积多晶硅, 刻蚀多晶硅以形成栅极及互连线 图形。

模拟集成电路版图设计基础

目录

• 前言 集成电路工艺基础 • 一、什么是版图? • 二、版图的意义 • 三、版图与线路图、工艺的关系 • 四、版图设计的过程 • 五、版图的组成 • 六、版图的层次 • 七、如何绘制版图 • 八、版图验证与检查 • 九、版图的艺术

集成电路工艺基础

P-Si P-Si

光刻胶 Si3 N4

五、版图的组成

版图其实就是另一种形式的电路图,作为电路图最 基本的有两大组成部分

1.器件(常见)

1 MOS管 2 电阻 3 电容

2.互连

2.2.1金属(第一层金属,第二层金属……) 2.2.2通孔

五、版图的组成

1.1MOS管

模拟CMOS集成电路设计课件

医学图像处理、音频处理

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

PPT学习交流

6

5

2、集成电路工艺

速度高, 功耗大, 集成度低

最早MOS工 艺,速度低

超高速、高频 IC

光电集成器件

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强

PPT学习交流

7

6

CMOS工艺

B

S

G

D

B

S

G

D

n+

n+

p+

p+

p 型衬底

n 型阱

n 阱CMOS工艺

B

S

G

D

20

沿沟道x点处的电荷密度为: 沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中: 得到:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

PPT学习交流

22

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此:

电流随VGS的 增大而增加

漏极的反型层消失,出现由耗尽层

构成的夹断区。

➢电子沿沟道从源极向漏极运动,达

到夹断区边缘时,受夹断区强电场

的作用,很快漂移到漏极。 B

➢VDS的变化主要体现在夹断区上,

p+

对沟道长度和沟道内的场强影响不

大,因此可以近似认为沟道电流保

p-

持恒定。

VDS

-+

-+

VGS

G

S

D

n+

n+

夹断区

PPT学习交流

20

19

2、NMOS 管IV特性推导与分析

《模拟集成电路》课件

,以便对设计的电路进行全面的测试和评估。

PART 05

模拟集成电路的制造工艺

REPORTING

半导体材料

硅材料

硅是最常用的半导体材料,具有 稳定的物理和化学性质,成熟的 制造工艺以及低成本等优点。

化合物半导体

如砷化镓、磷化铟等化合物半导 体材料,具有高电子迁移率、宽 禁带等特点,常用于高速、高频 和高温电子器件。

《模拟集成电路》课 件

REPORTING

• 模拟集成电路概述 • 模拟集成电路的基本元件 • 模拟集成电路的分析方法 • 模拟集成电路的设计流程 • 模拟集成电路的制造工艺 • 模拟集成电路的优化与改进

目录

PART 01

模拟集成电路概述

REPORTING

定义与特点

定义

模拟集成电路是指由电阻、电容、电 感、晶体管等电子元件按一定电路拓 扑连接在一起,实现模拟信号处理功 能的集成电路。

围和失真。

信号分析方法

01

02

03

04

频域分析

将时域信号转换为频域信号, 分析信号的频率成分和频谱特

性。

时域分析

研究信号的幅度、相位、频率 和时间变化特性,分析信号的

波形和特征参数。

调制解调分析

研究信号的调制与解调过程, 分析信号的调制特性、解调失

真等。

非线性分析

研究电路的非线性效应,分析 信号的非线性失真和互调失真

音频领域

模拟集成电路在音频领域中主要用于 音频信号的放大、滤波、音效处理等 功能,如音响设备、耳机等产品中的 模拟集成电路。

模拟集成电路的发展趋势

集成度不断提高

随着半导体工艺的不断发展,模 拟集成电路的集成度不断提高, 能够实现更加复杂的模拟信号处

最新模拟集成电路设计流程课件

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2021/1/15

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

共88页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2021/1/15

共88页

22

其它有关的菜单项

Outputs/Setup

当然我们需要输出的有时不仅仅是电流、电压,还有一 些更高级的。比如说:带宽、增益等需要计算的值,这时 我们可以在Outputs/setup中设定其名称和表达式。在运行 模拟之后,这些输出将会很直观的显示出来。

2021/1/15

共88页

11

编辑完成的电路图

2021/1/15

共88页

12

一些快捷键

以下是一些常用的快捷键: i 添加元件,即打开添加元件的窗口; [ 缩小两倍; ] 扩大两倍; w 连线(细线); f 全图显示; p 查看元件属性; m 整体移动(带连接关系); shift+m 移动(不带连接关系)。

2021/1/15

共88页

13

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

模拟集成电路设计流程课件

2020/11/11

共88页

15

四、模拟仿真的设置(重点)

Composerschamatic界面中 的Tools → Analog Environment项可 以打开Analog Design Environment 窗口, 如右图所示。

2020/11/11

共88页

16

Analog Design Simulation菜单介绍

2020/11/11

共88页

28

仿真结果

该运放直流增益为80.9dB,单位增益带宽为82M Hz, 相位裕度为67.32deg。

2020/11/11

共88页

29

工艺角与温度

上面运放的仿真实在tt(典型)27度下的仿真 ,但实际的工艺不一定是tt,使用温度也不一 定是室温27度,所以要进行工艺角仿真

2020/11/11

共88页

13

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

在Cellview From Cellview窗口,From View Name栏为:schematic,Tool / Data Type栏为Composer-Symbol。

电源电压Vdc=1.8V; 交流信号源acm=1 V; 负载电容Cload=5p F; 采用Spectre分析方式,选择交流分析(ac),设置如下:

Sweep Variable: Frequency Sweep Range :1 Hz~100M Hz 仿真完成后,点击 Result -> Direct Plot -> AC Gain&Phase 查看运放的幅频特性和相频特性

模拟集成电路的设计4z24页PPT

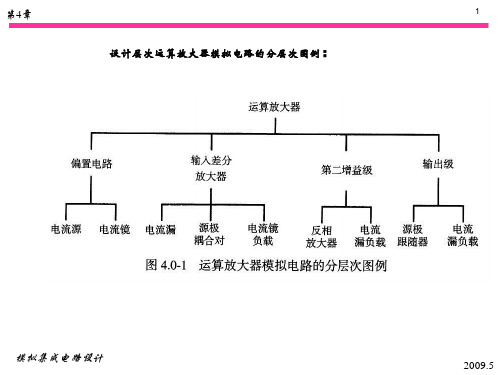

第4章

1

设计层次运算放大器模拟电路的分层1

4.1 MOS开关

目的: 研究与CMOS集成电路兼容的开关特性

模拟集成电路设计

2009.5

§4-1: MOS开关

一、开关模型

● 理想开关 导通时短路,关断时开路

● 实际开关

模拟集成电路设计

41

实际开关 2009.5

情况2, U=5V/10ns=5X108<2.66X109 属慢跃变, Verror=10.95mV

说明:不要期望从误差公式得到关于电荷馈通量的精确答案。 相反,它们只是帮助了解各种电路元件和端口的条件的影响, 以便在设计技术中最大限度地减少不必要的行为。

2009.5

41

§4-1: MOS开关

5.解决电荷注入的方案

2009.5

§4-1: MOS开关 4.近似电荷注入的分析表达式 假设珊极电压从VH到VL变化 所以: 定义: 又:

电荷注入引起的误差:

其中,U是vG(t)的斜率

(1 )慢跃变时

(2 )快跃变时

41

2009.5

41

§4-1: MOS开关 P98 例4.1-1 电荷馈通误差的计算

情况1: U=5V/0.2ns=25X109>2.66X109 属快跃变,Verror=19.7mV

(1)使用最小尺寸的开关,以减少重叠电容;增加CL ; (2)使用虚拟补偿晶体管;

● 需要一个互补时钟; ● 完全消除是困难的,实际上可能会在其他方面产生问题。

(3)使用互补开关;

2009.5

第1节

41

4.2 MOS二极管、有源电阻

模拟集成电路设计

2009.5

41

§4-1: MOS开关

1

设计层次运算放大器模拟电路的分层1

4.1 MOS开关

目的: 研究与CMOS集成电路兼容的开关特性

模拟集成电路设计

2009.5

§4-1: MOS开关

一、开关模型

● 理想开关 导通时短路,关断时开路

● 实际开关

模拟集成电路设计

41

实际开关 2009.5

情况2, U=5V/10ns=5X108<2.66X109 属慢跃变, Verror=10.95mV

说明:不要期望从误差公式得到关于电荷馈通量的精确答案。 相反,它们只是帮助了解各种电路元件和端口的条件的影响, 以便在设计技术中最大限度地减少不必要的行为。

2009.5

41

§4-1: MOS开关

5.解决电荷注入的方案

2009.5

§4-1: MOS开关 4.近似电荷注入的分析表达式 假设珊极电压从VH到VL变化 所以: 定义: 又:

电荷注入引起的误差:

其中,U是vG(t)的斜率

(1 )慢跃变时

(2 )快跃变时

41

2009.5

41

§4-1: MOS开关 P98 例4.1-1 电荷馈通误差的计算

情况1: U=5V/0.2ns=25X109>2.66X109 属快跃变,Verror=19.7mV

(1)使用最小尺寸的开关,以减少重叠电容;增加CL ; (2)使用虚拟补偿晶体管;

● 需要一个互补时钟; ● 完全消除是困难的,实际上可能会在其他方面产生问题。

(3)使用互补开关;

2009.5

第1节

41

4.2 MOS二极管、有源电阻

模拟集成电路设计

2009.5

41

§4-1: MOS开关

集成电路设计与制造的主要流程PPT培训课件

集成电路设计与制造的主要流程 ppt培训课件

目录

• 集成电路概述 • 集成电路设计流程 • 集成电路制造流程 • 集成电路封装与测试 • 集成电路设计与制造的挑战与未来发展

01

集成电路概述

集成电路的定义与特点

总结词

集成电路是将多个电子元件集成在一块衬底上,实现一定电路或系统功能的微型电子部件。其主要特点包括高集 成度、高可靠性、低功耗、低成本等。

制造工艺的发展趋势是不断追求更高的集成度、更小的特征尺寸和更好的性能。

晶圆制备

晶圆是制造集成电路的基础材 料,其质量直接影响集成电路 的性能和良品率。

晶圆制备包括切割、研磨、抛 光等环节,目的是获得表面平 整、晶体结构完整的晶圆。

晶圆制备技术的发展趋势是追 求更薄的晶圆、更小的晶圆直 径和更高的加工精度。

设计审查与后仿真

设计审查

对完成的版图进行审查,确保其符合规格要求和制造工艺要 求。

后仿真

在版图设计完成后,进行后仿真验证,确保电路的功能和性 能符合要求。

03

集成电路制造流程

制造工艺简介

制造工艺是将集成电路设计转化为实际产品的过程,涉及多个复杂的技术环节。

集成电路制造工艺主要包括晶圆制备、薄膜制备、掺杂与刻蚀、工艺集成与良品率 控制等步骤。

详细描述

集成电路的发展历程可以分为三个阶段:小规模集成电路、大规模集成电路和超大规模集成电路。从 小规模集成电路到超大规模集成电路的发展过程中,集成电路的集成度不断提高,性能不断优化,成 本不断降低,推动了电子技术的飞速发展。

集成电路的应用领域

总结词

集成电路的应用领域非常广泛,包括通信、计算机、 消费电子、工业控制、汽车电子等。

测试与可靠性评估

目录

• 集成电路概述 • 集成电路设计流程 • 集成电路制造流程 • 集成电路封装与测试 • 集成电路设计与制造的挑战与未来发展

01

集成电路概述

集成电路的定义与特点

总结词

集成电路是将多个电子元件集成在一块衬底上,实现一定电路或系统功能的微型电子部件。其主要特点包括高集 成度、高可靠性、低功耗、低成本等。

制造工艺的发展趋势是不断追求更高的集成度、更小的特征尺寸和更好的性能。

晶圆制备

晶圆是制造集成电路的基础材 料,其质量直接影响集成电路 的性能和良品率。

晶圆制备包括切割、研磨、抛 光等环节,目的是获得表面平 整、晶体结构完整的晶圆。

晶圆制备技术的发展趋势是追 求更薄的晶圆、更小的晶圆直 径和更高的加工精度。

设计审查与后仿真

设计审查

对完成的版图进行审查,确保其符合规格要求和制造工艺要 求。

后仿真

在版图设计完成后,进行后仿真验证,确保电路的功能和性 能符合要求。

03

集成电路制造流程

制造工艺简介

制造工艺是将集成电路设计转化为实际产品的过程,涉及多个复杂的技术环节。

集成电路制造工艺主要包括晶圆制备、薄膜制备、掺杂与刻蚀、工艺集成与良品率 控制等步骤。

详细描述

集成电路的发展历程可以分为三个阶段:小规模集成电路、大规模集成电路和超大规模集成电路。从 小规模集成电路到超大规模集成电路的发展过程中,集成电路的集成度不断提高,性能不断优化,成 本不断降低,推动了电子技术的飞速发展。

集成电路的应用领域

总结词

集成电路的应用领域非常广泛,包括通信、计算机、 消费电子、工业控制、汽车电子等。

测试与可靠性评估

第6章模拟集成电路PPT课件

结论:

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

第6页/共55页

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

第7页/共55页

6.1.2微电流源(P259)

第24页/共55页

+

+

-vid

差放

vi1 +

-

vi2 -

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

总输出电压

vo

=

v

od

v oc

A VD v id A VC v ic

第25页/共55页

5.主要技术指标计算(P265)

vi1

=

vic

1 2

vid

vi2

=

vic

1 2

vid

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。 若第二级也漂了100 uV, 则输出漂移 10 mV。

采用差分式放大电路

第14页/共55页

漂移 1 V+ 10 mV

6.2.2 基本差分式放大电路

1. 电路组成 两个BJT特性一致,参数相等。

第27页/共55页

(1) 双入双出AVD(P265)

负载开路

时:

AVD

=

Vo Vid

= Vo1 Vo2 Vi1 Vi2

= 2Vo1 Vo1

无论Rc值如何, IC2电流值保持不变(前提:电源要稳定)

第6页/共55页

当较小时,可用 带缓冲级的镜像电流源

增加T0,使IC更加接近IREF 三、镜像电流源特点 1 内阻ro一般在几百千欧以上

2. 电流受电源波动影响大; 3. 电流最低至mA级。 4. 具有温度补偿特性。

第7页/共55页

6.1.2微电流源(P259)

第24页/共55页

+

+

-vid

差放

vi1 +

-

vi2 -

+

-vod

+

+ vo1

vo2 -

-

差分式放大电路输入输出结构示意图

总输出电压

vo

=

v

od

v oc

A VD v id A VC v ic

第25页/共55页

5.主要技术指标计算(P265)

vi1

=

vic

1 2

vid

vi2

=

vic

1 2

vid

假设 AV1 = 100, AV2 = 100, AV3 = 1 。 若第一级漂了100 uV, 则输出漂移 1 V。 若第二级也漂了100 uV, 则输出漂移 10 mV。

采用差分式放大电路

第14页/共55页

漂移 1 V+ 10 mV

6.2.2 基本差分式放大电路

1. 电路组成 两个BJT特性一致,参数相等。

第27页/共55页

(1) 双入双出AVD(P265)

负载开路

时:

AVD

=

Vo Vid

= Vo1 Vo2 Vi1 Vi2

= 2Vo1 Vo1

模拟集成电路的设计流程89页PPT

Hspice: 作为业界标准的电路仿真工具,它自带了许多器 件模型,包括小尺寸的MOSFET和MESFET。Cadence提 供了hspice的基本元件库并提供了与Hspice的全面的接口。

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

2019/11/15

共88页

29

其它有关的菜单项(1)

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分 析的方法,也即参量扫描。可以对温度,用 户自定义的变量(variables)进行扫描,从 而找出最合适的值。

2019/11/15

共88页

30

其它有关的菜单项(2)

举个例子:标识3db的点,我们用到的表达式如下: bandwidth(VF(“/Out),3,“low”)。

需要注意的是:表达式一般都是通过计算器(caculator)输入的。Cadance 自带的计算器功能强大,除了输入一些普通表达式以外,还自带有一些特殊

表达式,如bandwidth、average等等。

2019/11/15

共88页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2019/11/15

共88页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车)

口

退出

23

Setup菜单

Setup菜单

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

2019/11/15

共88页

29

其它有关的菜单项(1)

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分 析的方法,也即参量扫描。可以对温度,用 户自定义的变量(variables)进行扫描,从 而找出最合适的值。

2019/11/15

共88页

30

其它有关的菜单项(2)

举个例子:标识3db的点,我们用到的表达式如下: bandwidth(VF(“/Out),3,“low”)。

需要注意的是:表达式一般都是通过计算器(caculator)输入的。Cadance 自带的计算器功能强大,除了输入一些普通表达式以外,还自带有一些特殊

表达式,如bandwidth、average等等。

2019/11/15

共88页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

2019/11/15

共88页

7

1、键入用户名和密码, 在提示符处键入: source/opt/demo/cds. env(回车)

口

退出

23

Setup菜单

Setup菜单

集成电路模拟版图设计基础106页PPT

第四部分:版图的艺术

1. 模拟版图和数字版图的首要目标 2. 首先考虑的三个问题 3. 匹配 4. 寄生效应 5. 噪声 6. 布局规划 7. ESD 8. 封装

IC模拟版图设计

第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第一部分:了解版图

PMOS版图

第二部分:版图设计基础

2.1 器件

反向器

器件剖面图及俯视图

器件版 图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1)反向器

VDD

3u/0.18u

IN

OUT

1u/0.18u

2)NMOS,PMOS

3)金属连线

GND

4)关于Butting Contact部分

第二部分:版图设计基础

2)它需要设计者具有电路系统原理与工艺制造方面的基 本知识,设计出一套符合设计规则的“正确”版图也 许并不困难,但是设计出最大程度体现高性能、低功 耗、低成本、能实际可靠工作的芯片版图缺不是一朝 一夕能学会的本事。

第一部分:了解版图

3. 版图的工具:

– Cadence

Virtuoso Dracula Assura Diva

IC模拟版图设计

目录

第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件 3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

目录

第三部分:版图的准备

1. 必要文件 2. 设计规则 3. DRC文件 4. LVS文件

第二部分:版图设计基础

1. 模拟版图和数字版图的首要目标 2. 首先考虑的三个问题 3. 匹配 4. 寄生效应 5. 噪声 6. 布局规划 7. ESD 8. 封装

IC模拟版图设计

第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第一部分:了解版图

PMOS版图

第二部分:版图设计基础

2.1 器件

反向器

器件剖面图及俯视图

器件版 图

第二部分:版图设计基础

2.1 器件

2.1.1 MOS管 1)反向器

VDD

3u/0.18u

IN

OUT

1u/0.18u

2)NMOS,PMOS

3)金属连线

GND

4)关于Butting Contact部分

第二部分:版图设计基础

2)它需要设计者具有电路系统原理与工艺制造方面的基 本知识,设计出一套符合设计规则的“正确”版图也 许并不困难,但是设计出最大程度体现高性能、低功 耗、低成本、能实际可靠工作的芯片版图缺不是一朝 一夕能学会的本事。

第一部分:了解版图

3. 版图的工具:

– Cadence

Virtuoso Dracula Assura Diva

IC模拟版图设计

目录

第一部分:了解版图

1. 版图的定义 2. 版图的意义 3. 版图的工具 4. 版图的设计流程

第二部分:版图设计基础

1. 认识版图 2. 版图组成两大部件 3. 版图编辑器 4. 电路图编辑器 5. 了解工艺厂商

目录

第三部分:版图的准备

1. 必要文件 2. 设计规则 3. DRC文件 4. LVS文件

第二部分:版图设计基础

模拟集成电路设计流程(ppt 54页)

source cshrc.iclab

cp ~wanghan/CMOS/cds.lib . ( “.”指当前文件夹)

cp /soft1/cdsmgr/cadence/IC5141/tools.Inx86

(接上行)/dfII/cdsuser/.cds init ~ (设置Cadence快捷键)

setdt ic

需要注意的是:表达式一般都是通过计算器(caculator) 输入的。Cadance自带的计算器功能强大,除了输入一些 普通表达式以外,还自带有一些特殊表达式,如

bandwidth、average等等。

2019/11/14

共88页

24

Calculator的使用

Calculator是 一个重要的数 据处理工具, 可以用来仿真 电源抑制比, 相位裕度,共

口

退出

18

Setup菜单

Setup菜单

Design Simulator/directory/host Temperature Model Library Environment

选择所要 模拟的线

路图

选择模拟使用 的模型一般有

cdsSpice hspiceS spectre等

设置模拟 时的温度

设置库文件 的路径和仿 真方式,修 改工艺角

共88页

14

生成symbol

进入“Virtuoso Schematic Editing: mylib nand2 schematic”窗口。

Design -> Create Cellview->From Cellview

在Cellview From Cellview窗口,From View Name栏为:schematic,Tool / Data Type栏为Composer-Symbol。