(完整版)MIPS处理器设计说明说课讲解

清华微机原理课件2.2MIPS体系结构

MIPS 通用寄存器的使用

为了使用$ gp, 编译器在编译时刻必须知道 一个数据是否在$ gp的64K范围之内。

通常这是不可能的,一般的做法是把small global data (小的全局数据)放在gp覆盖的范围内(比如一 个变量是8字节或更小),并且让linker报警如果 小的全局数据仍然太大从而超过gp作为一个基 指针所能存取的范围。

MIPS 通用寄存器的使用

$ gp: 如果存在一个全局指针,它将指向运行时决定 的静态数据(static data)区域的一个位置。这意味 着,利用gp作基指针,在gp指针32K左右的数 据存取,系统只需要一条指令就可完成。 如果没有全局指针,存取一个静态数据区域的 值需要两条指令: 一条是获取有编译器和loader决定好的32位的 地址常量。 另外一条是对数据的真正存取。

r格式registerformatj格式jumpformat二mips体系结构4存储器和寄存器中的数据类型mipscpu的一次操作可读出或写入18个字节的数据c名称mips名称size字节汇编助记符longlongdwordlongwordshorthalfwordcharbytemips编译器提供了64位指针它把long解释成64位数据总之long不应该小于int三mips指令与汇编指令系统对于一条汇编语言指令来说有两个问题要解决要指出进行什么操作?要指出大多数指令涉及的操作数和操作结果放在何处mips

助记符 zero 永远为0 at v0, v1 a0-a3 t0-t7 t8-t9 s0-s7 k0,k1 gp sp s8/fp ra 子函数调用返回结果 子函数调用的参数

用法

用做汇编器的暂时变量

暂时变量,子函数使用时不需要保存与恢复

子函数寄存器变量。在返回之前子函数必须保存和恢复使 用过的变量,从而调用函数知道这些寄存器的值没有变化 通常被中断或异常处理程序使用作为保存一些系统参数

OpenMIPS教学版讲解

流水线架构

流水线架构是现代处理器中常见的一种架构,通过将指令执行过程划分为多个阶段, 实现并行处理,提高处理器的执行效率。

OpenMIPS教学版的流水线架构分为取指、解码、执行、访存和写回五个阶段,每 个阶段都有相应的硬件单元进行支持,确保指令执行的快速和准确。

流水线架构能够有效地提高处理器的吞吐量,同时使得处理器更加灵活,能够适应 不同的应用场景。

算平台上实现更快速的计算和推理。

嵌入式系统应用

03

OpenMIPS教学版可以应用于嵌入式系统中,为人工智能传感

器和设备提供强大的计算能力。

OpenMIPS在物联网领域的应用

实时数据处理

OpenMIPS教学版适用于物联网设备中的实时数据处理,如传 感器数据的采集、分析和处理。

低功耗设计

针对物联网设备的低功耗要求,OpenMIPS教学版可以进行优 化,降低设备能耗,延长电池寿命。

实验案例选择

选择具有代表性的实验案 例,如简单的加法器、乘 法器等。

实验案例解析

对每个实验案例进行详细 解析,包括输入输出、算 法实现等。

实验案例实现

根据解析结果,在 OpenMIPS教学版上实现 相应的算法。

实验结果分析

实验结果验证

通过实际运行和测试,验证实验结果的正确性。

结果分析

对实验结果进行分析,包括性能指标、优化空间 等。

数据中心优化

通过OpenMIPS教学版的优化,可以提高数据中心的处理能力和能效, 降低运营成本。

THANKS FOR WATCHING

感谢您的观看

C语言与汇编的交互

在OpenMIPS教学版中,可以使用内嵌汇编的方式将C语言与汇编 语言进行交互,实现更高效的代码实现。

MIPS指令多周期CPU设计

– MEMread, IRwrite, PCwrite

译码/取操作数 – ALUsrcA=0, ALUsrcB=11,ALUop=00 执行运算 – ALUsrcA=0, ALUsrcB=00,ALUop=00

写回寄存器

– RegDST=1 RegWrite MemtoReg = 0

MIPS的 LW 指令 的执行过程

A 寄 存 器

1

A A L U

Z

PC

0 1

存 A 储 D 器

B 寄 存 器

4

1 0 2 3

B

R

结 果 寄 存 器

DR

1 0

扩展

Clock

Immediate

左移2位

MIPS的 ADD 指令 的执行过程

取指 周期: 执行 周期:

IR←MEM[PC]

PC ←PC+4 C ← A+B

WritePC IODR WriteMEM WriteIR MEMtoREG SE REGds WriteREG ALUsrcA

0

0

指 令 内 容 IR

rs rt

rd

0 1

N1 寄 Q1 存 N2 器 堆 ND DI Q2

A 寄 存 器

1

A A L U

Z

PC

0 1

存 A 储 D 器

B 寄 存 器

4

1 0 2 3

B

R

结 果 寄 存 器

DR

1 0

Immediate

Clock

扩展

左移2位

存储器存指令和数据。 读指令时由 PC 提供地址,读出的指令保存到 IR; 读写数据时由结果寄存器提供地址,读操作的读出数据保存到 DR; 写操作的写入数据由 B寄存器给出。

stanford_university_mips_组织架构_解释说明

stanford university mips 组织架构解释说明1. 引言1.1 概述引言部分将介绍本文的主题——Stanford University MIPS组织架构。

MIPS (Microprocessor without Interlocked Pipeline Stages)指令集架构是一种经典的RISC(Reduced Instruction Set Computer)体系结构,由斯坦福大学开发和推广。

本文将详细解释MIPS组织架构的概念和原理,并深入讨论其指令集、寄存器、流水线技术以及优化策略。

1.2 文章结构为了更好地说明MIPS组织架构,本文将按照以下结构展开讨论:- 第2部分将简要介绍MIPS组织架构的概述,包括计算机体系结构的发展历程以及MIPS架构的特点。

- 第3部分将着重介绍MIPS指令集和寄存器,包括概述、寄存器结构和作用,以及指令格式和编码规则。

- 第4部分将深入探讨MIPS流水线技术及其优化策略,包括流水线基本概念和原理、MIPS流水线结构以及各个阶段功能介绍,以及相关问题和优化策略的讨论。

- 最后,第5部分将给出本文的结论和总结。

1.3 目的本文的目的是通过对Stanford University MIPS组织架构的详细解释,让读者了解MIPS体系结构及其特点,并探究其中涉及的指令集、寄存器、流水线技术以及优化策略。

通过文章的阅读,读者将能够更好地理解MIPS组织架构并在计算机体系结构领域有所提升。

我们希望这篇长文能够为读者提供一个全面而清晰的指南,进一步推动计算机科学领域的发展与创新。

2. MIPS组织架构:2.1 概述:MIPS(Microprocessor without Interlocked Pipeline Stages)是一种经典的RISC(Reduced Instruction Set Computer)微处理器架构。

它于1981年由斯坦福大学开发,旨在设计简单、高效的计算机体系结构。

自己动手写CPUOpenMIPS教学版讲解主要内容

指令wishbone接口 OpenMIPS 数据wishbone接口

iwishbone

dwishbone

m0

WB_CONMAX

s0

s1

s2

s3

SDRAM Controller

UART Controller

GPIO Controller

FLASH Controller

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

四 OpenMIPS教学版的文件组织

asm_test

包括所有的测试例程,其组织方式是参照《10天实现 处理器——OpenMIPS成长记》一文,按照“天”来组织, 比如Day2文件夹中存放的是《10天实现处理器—— OpenMIPS成长记》一文中第二天对应的测试例程,当 然所有的测试例程都可以在最终的OpenMIPS中进行测 试

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

四 OpenMIPS教学版的文件组织

rtl

所有OpenMIPS的源代码文件在该文件夹下,包括

流水线文件iu.vhd 除法模块div.vhd 寄存器文件Reg 顶层文件OpenMIPS.vhd 宏定义文件stdlib.vhd

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

一 OpenMIPS项目简介

OpenMIPS是采用具有哈佛结构的32位标量处理器,兼容 MIPS32体系结构,这样可以使用现有的MIPS编译环境。

具有以下特点:

五级整数流水线,分别是:取指、译码、执行、访存、 回写

哈佛结构,分开的指令、数据接口

32个32位整数寄存器

大端模式

向量化异常处理,支持精确异常处理

•《自己动手写CPU》OpenMIPS教 学版讲解主要内容

32位MIPS处理器说明

32位MIPS处理器说明一、实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

二、实验原理及实验内容该32位MIPS处理器主要需要设计ALU、单周期、流水线。

下面分别讲述这三个部分的设计原理及实验内容。

1.ALUALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。

输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。

其功能表如下图所示:根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。

设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。

设计框图思路如下:(1)ALU_ADD_SUB这部分是ALU设计中最重要的一部分。

采用了8位超前进位级联,用与门来实现32位全加器。

减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。

需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。

是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。

若为无符号运算,加法结果溢出则最高进位为1,且结果不为负;减法结果溢出等价于结果为负,即最高进位为0。

而结果为0等价于全部位都取0。

(2)ALU_Shift移位运算分别有逻辑左移,逻辑右移,算术右移三种情况。

首先判断是逻辑移位还是算术移位来决定填充0还是填充逻辑位。

之后采取先将操作数根据左移还是右移的判断做出32位扩充,再根据shamt从最高位到最低位判断是否为0来决定取那几位操作数,最后得到移位的结果。

MIPS指令单周期CPU设计

Data memory

rd rs rt

Register File

PC

执行步骤(3/5)

instruction memory

ALU

MUX

+4

imm 2. Decode/ Register Read

1. Instruction Fetch

3. Execute 4. Memory 5. Register Write

– 将结果写入目的寄存器

需要保存的值

– PC、寄存器组、存储器

二、典型指令的数据通路

ADDU and SUBU – addu rd,rs,rt

31 op 6 bits 31 op 6 bits 26 rs 5 bits 26 rs 5 bits 21 rt 5 bits 21 rt 5 bits 16 immediate 16 bits 16 rd 5 bits 11 6 shamt 5 bits funct 6 bits 0 0

ALU

MUX

+4

imm 2. Decode/ Register Read

1. Instruction Fetch

3. Execute 4. Memory5. Register Write

Phase 1: Instruction Fetch (IF)

– Fetch 32-bit instruction from memory – Increment PC (PC = PC + 4)

Data memory

rd rs rt

Register File

PC

执行步骤(2/5)

instruction memory

ALU

MUX

MIPS处理器设计说明要点

西安邮电大学实践课程报告书课程名称:计算机组成与实践院(系)名称:电子工程学院专业班级:**学号/姓名:**实习时间:2015年3月6日至2015年6月19日1 课程主要目的本课程是在上学期《计算机组成与设计》课程学习的基础上,通过实践课的方式,依照集成电路设计流程,完成一个简单独立硬件功能电路模块的设计,从而到达对《计算机组成与设计》课程的深入理解和提高电路设计的实践能力,从理论和实验的结合中巩固计算机基本知识,熟练掌握电路设计的基本流程和原理,同时,加深对MIPS系统的组成部件及其电路结构,原理和功能的理解,掌握利用硬件描述语言和EDA工具进行MIPS设计的一般方法。

2 课程的主要内容和任务MIPS是典型的32位定长指令字RISC处理器,要求深入理解MIPS处理器的内部结构及工作原理。

采用verilogHDL设计一个兼容MIPS指令格式,具有10条以上指令功能的单周期CPU硬件电路,该32位MIPS设计内容主要包括系统中的基本组成部件(存储器,指令寄存器,寄存器堆,算术逻辑运算器,程序计数器,多路选择器,符号扩展等)的设计,仿真及硬件下载的方法和过程。

设计过程中使用ISE仿真工具完成设计电路的仿真验证。

3总体设计方案3.1指令及其功能表:(1)R型指令:(2)I型指令:(3)J型指令:3.2总体结构设计:该MIPS主要由8个模块组成,各个子模块分别设计其特定的功能,最终利用一个总的模块进行子模块间连接,使得整个CPU能连贯执行指令,在仿真结果中观察设计结果,最终进行硬件下载,验证设计。

其中各个模块简单功能如下:(1)存储器模块:具备基本的读写功能,用于存放数据和指令。

(2)寄存器堆模块:由32个32位的寄存器组成,提供较大的存储空间,用于存放暂存数据和指令。

(3)算术逻辑运算器模块:执行加减法等算术运算,与非或等逻辑运算,以及比较移位传送等操作的功能部件,是该CPU的设计核心部分,存在不同的运算处理功能,是体现实验设计结果正确性的模块。

7_存储器设计_154307372

MIPS CPU设计——存储器设计1 存储器系统基础2 存储器体系结构3 Cache技术4 Cache性能评估Ref.2/7.1、7.2、7.3计算机硬件系统的组成主机系统 CPU存储器输出设备输入 设备运算器 控制器数据 通 路控制信号MIPS CPU设计——存储器设计1 存储器系统基础——半导体存储器2 存储器体系结构3 Cache技术4 Cache性能评估1 存储器系统基础:半导体存储器n⏹ 现代系统中绝大部分的半导体电路都是在存储器电路中 n⏹ 存储器是用来进行数据存储的n⏹ 过去若干年里,对存储器容量增长的需求以及对其价格不断降低的需求成为了半导体VLSI 技术发展的推动力之一 n⏹ 随机访问存储器RAM 是其中最常见的形式到底 “random -access”是什么意思?RANDOMACCESS MEMORYAddress R e a d D a t aWrite DataWR“R A M ” 一词是指该存储器的所有内容都可以被读取和写入指的是当存储器中的信息被读取或写入时,所需要的时间与这段信息所在的位置无关存储器无处不在!MIPS 的瓶颈主要集中在存储器i m m 1632 ALUctr ClkbusWRegWr 32 32 busA32busB 55 5 Rw Ra Rb 32 32-bit Registers Rs Rt Rt Rd RegDstExtenderMux3216imm16ALUSrc0ExtOp MuxMemtoRegClkData InWrEn 32 Adr Data MemoryMemWrALUInstruction<31:0>0 111<21:25><16:20><11:15><0:15>Imm16RdRtRs= AdderAdderPCClk00Mux 4PCSrcPC ExtAdrInst MemoryMux0 1Shamt[4:0]ALUsrc11 存储器系统基础:半导体存储器n⏹ 从使用角度:n⏹ “主”存储器⇒大容量,低成本n⏹ 缓存 ⇒快速访问n⏹ 编程信息(BIOS、FPGA 初始化) ⇒非易失存储器FLASH n⏹ 只读存储器: ROM (Read Only Memory,非易失) n⏹ 掩膜编程/ 可编程只读存储器(PROM, Programmable) n⏹ 可擦写PROM(EPROM, Erasable) / 电可擦写EPROM(EEPROM, Electrical EPROM)n⏹ 块可重编程EEPROM:(Flash) PROM1 存储器系统基础:半导体存储器n⏹ 可读/写并随机访问的存储器:RAMn⏹ 静态RAM(SRAM, Static) –快速, 可以保持电平, 并且昂贵(1bit SRAM面积是1bit DRAM的几倍)n⏹ 多端口SRAM(更昂贵)n⏹ 同步SRAM (缓存)在CPU读取前一次请求的数据同时接收下一个数据地址n⏹ 动态存储器(DRAM, Dynamic) –比较慢, 需刷新, 相对廉价1 存储器系统基础:半导体存储器n⏹ 读写速度快n⏹ 所用管子数目多,单个器件容量小 n⏹ 价格昂贵n⏹ SRAM 基本存储电路由MOS 管组成的触发器电路,每个触发器可以存放1位信息1 存储器系统基础:SRAM 单元DCQIN OUTSEL_L WR_L0 011 存储器系统基础:半导体存储器n⏹ DRAM基本存储电路 n⏹ 所用管子少,芯片位密度高n⏹ 需要刷新n⏹ 存取速度慢n⏹ 价格低廉 行选择信号列选择信号数据输入输出线刷新放大器1 存储器系统基础:DRAM单元1 存储器系统基础:电容的问题 n⏹ 充电的效果将在读取时被消耗,所以必须在读取后重新充电n⏹ 更糟糕的是:即便不读,也会有漏电n⏹ 每个单元都必须定期被刷新n⏹ 存储器的控制电路周期性的顺序读取每个单元的内容并回写n⏹ 在刷新周期内CPU不能使用这部分存储器,因此降低系统性能1 存储器系统基础:电容的问题 n⏹ 需要大电容,降低泄漏速度 n⏹ 大电容会带来大的时间常数和延迟 n⏹ 因此n⏹ DRAM 可以做得很大n⏹ 但是它们比SRAM 慢 bit1个DRAM 单元 V REF1 存储器系统基础:存储器的基本参数n⏹ 容量:以字节或比特数表示 n⏹ 速度:以访问时间T A 、存储周期T M 或带宽B M 表示 n⏹ T A ——从接收读申请到将信息读出到存储器输出端的时间 n⏹ T M ——连续两次启动存储器访问所需的最小时间间隔。

完整版类MIPS单周期处理器

一、实验目的1.了解微处理器的基本结构。

2.掌握哈佛结构的计算机工作原理。

3.学会设计简单的微处理器。

4.了解软件控制硬件工作的基本原理。

二、实验任务利用HDL语言,基于Xilinx FPGA nexys4实验平台,设计一个能够执行以下MIPS 指令集的单周期类MIPS处理器,要求完成所有支持指令的功能仿真,验证指令执行的正确性,要求编写汇编程序将本人学号的ASCII码存入RAM的连续内存区域。

(1)支持基本的算术逻辑运算如add,sub,and,or,slt,andi指令(2)支持基本的内存操作如lw,sw指令(3)支持基本的程序控制如beq,j指令三、实验过程1、建立工程在ISE 14.7软件中建立名为Lab1 的工程文件。

芯片系列选择Artix7,具体芯片型号选择XC7A100T,封装类型选择CSG324,速度信息选择-1。

12、分模块设计1)指令存储器ROM设计新建IP core Generator,命名为irom。

设定的指令存储器大小为128字,指令存储器模块在顶层模块中被调用。

输入为指令指针(PC)与时钟信号(clkin),输出为32位的机器指令,并将输出的机器指令送到后续的寄存器组模块、控制器模块、立即数符号扩展模块进行相应的处理。

然后制作COE文件。

先使用UltraEdit 编辑代码,代码如下main:addi $2,$0,85sw $2,0($3)addi $2,$0,50sw $2,4($3)addi $2,$0,48sw $2,8($3)addi $2,$0,49sw $2,12($3)addi $2,$0,53 #sw $2,16($3)addi $2,$0,49 #sw $2,20($3)addi $2,$0,51 #sw $2,24($3)addi $2,$0,52 #sw $2,28($3)addi $2,$0,54 #sw $2,32($3)addi $2,$0,52 #sw $2,36($3)j main2将其导入QtSpim中,选中机器码,加上前缀并将最后一行0x08100009修改为0x08000000,代码如下MEMORY_INITIALIZATION_RADIX=16;MEMORY_INITIALIZATION_VECTOR=20020055,ac620000,20020032,ac620004,20020030,ac620008,20020031,ac62000c,20020035,ac620010,20020031,ac620014,20020033,ac620018,20020034,ac62001c,20020036,ac620020,20020034,ac620024,08000000,保存为.coe文件,在ROM模块里调用。

mips单周期cpu课程设计

mips单周期cpu课程设计一、课程目标知识目标:1. 掌握MIPS单周期CPU的基本结构和工作原理;2. 了解指令集、指令执行过程和指令周期;3. 学会分析并设计简单的MIPS指令;4. 理解CPU性能指标,如时钟频率、吞吐率等。

技能目标:1. 能够运用硬件描述语言(如Verilog)进行单周期CPU的设计与仿真;2. 能够独立编写简单的MIPS汇编程序,并在单周期CPU上运行;3. 能够分析单周期CPU的性能,并进行优化;4. 培养学生的团队合作能力和问题解决能力。

情感态度价值观目标:1. 培养学生对计算机组成原理和硬件设计的兴趣,激发学生的创新意识;2. 增强学生的工程素养,使其认识到工程实践在计算机科学领域的重要性;3. 培养学生严谨、细致、负责任的科学态度,提高学生的自主学习能力。

本课程针对高中年级学生,课程性质为实践性较强的硬件课程。

结合学生特点,课程目标注重理论与实践相结合,通过设计单周期CPU,使学生深入理解计算机硬件原理,提高实践能力。

在教学要求上,注重培养学生的团队合作精神,提高学生分析和解决问题的能力,为后续计算机组成原理及相关课程打下坚实基础。

通过本课程的学习,学生将能够独立完成单周期CPU的设计与仿真,具备一定的硬件编程能力。

二、教学内容1. 引言:介绍CPU在计算机系统中的作用,引出MIPS单周期CPU的概念及其重要性。

相关教材章节:第一章 计算机系统概述2. MIPS单周期CPU基本结构:讲解CPU的基本组成部分,包括寄存器组、控制单元、算术逻辑单元(ALU)、数据通路等。

相关教材章节:第二章 计算机组成原理3. 指令集与指令执行:分析MIPS指令集特点,讲解指令执行过程和指令周期。

相关教材章节:第三章 指令系统4. 硬件描述语言与单周期CPU设计:介绍Verilog硬件描述语言,通过实例讲解如何使用Verilog设计单周期CPU。

相关教材章节:第四章 硬件描述语言与数字电路设计5. 单周期CPU仿真与优化:指导学生进行单周期CPU的仿真,分析性能瓶颈,探讨优化方案。

微机原理实验 类MIPS单周期微处理器设计

电子信息与通信学院实验报告实验名称微机原理实验课程名称类MIPS单周期微处理器设计姓名周乃鼎学号U201313768日期2015.11.13地点南一楼东203成绩教师左冬红一、实验目的1.了解微处理器的基本结构2.掌握哈佛结构的计算机工作原理3.学会设计简单的微处理器4.了解软件控制硬件工作的基本原理二、实验任务利用HDL语言,基于Xilinx FPGA nexys4实验平台,设计一个能够执行以下MIPS指令集的单周期类MIPS处理器,要求完成所有支持指令的功能仿真,验证指令执行的正确性,要求编写汇编程序将本人学号的ASCII码存入RAM的连续内存区域–支持基本的内存操作如lw,sw指令–支持基本的算术逻辑运算如add,sub,and,or,slt,addi指令–支持基本的程序控制如beq,j指令三、基本原理四、 各个硬件模块设计1. 寄存器组寄存器组是指令操作的主要对象,MIPS 处理器里一共有32个32位的寄存器,故可以声明一个包含32个32位的寄存器数组。

读寄存器时需要Rs ,Rd 的地址,得到其数据。

写寄存器Rd 时需要所写地址,所写数据,同时需要写使能。

以上所有操作需要在时钟和复位信号控制下操作。

故寄存器组设计如下:Verilog 代码如下,细节见注释:beginif(!reset)beginif(regWriteEn == 1) // 写使能信号为1时写操作beginregs[regWriteAddr] = regWriteData; // 写入数据endendelsebeginfor(i = 0; i < 32; i = i + 1)regs[i] = 0; // 所有寄存器赋值为0,复位endendendmodule2.控制器模块:控制器模块输入为指令的操作码opCode段,输出各个复用器、存储器读写等的信号,控制数据通路的正常进行。

根据指令的不同,输出不同的信号即可。

Verilog 代码如下,细节见注释:3. ALU 控制译码ALU 主要执行5种操作:与,或,加,减,小于设置。

最新数字系统设计实验--流水线MIPS微处理器设计

一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTISLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

如图1所示,一个指令的执行需要五个时钟周期,每个时钟周期上升沿来临时,此指令所代表的一系列数据和控制信息转移到下一级处理。

图1 流水线流水作业示意图一条MIPS指令分为五个处理步骤,即五级流水线,的具体执行过程如图2所示。

图2 五级流水线MIPS CPU初步原理框图流水线寄存器:为了在其它四级流水线中各条指令保持各自的值,从指令存储器中读出的指令必须保存在寄存器中。

同样的方法应用到每个流水线步骤中,需要在上图中各级之间加入寄存器,如图3所示。

图3.在各级分割线添加寄存器后的框图由于在流水线中,数据和控制信息将在时钟上升沿转移到下一级,所以规定流水线转移的变量命名遵守如下格式:名称_流水线级名称。

计算机组成原理-第11章 MIPS处理器设计(单周期、多周期)1 [兼容模式]

![计算机组成原理-第11章 MIPS处理器设计(单周期、多周期)1 [兼容模式]](https://img.taocdn.com/s3/m/72c9d32567ec102de2bd89a3.png)

llxx@

12

A conceptual view – computational instructions

• Both source

operands and

Read data 2

Register File

Datapath Control Points

RegWrite (“write enable” control point)

寄存器号 Instruction

R-type指令的执行

Read

register 1

Read

Read

data 1

register 2

– beq为相对寻址:以npc为基准,指令中的 target为16位,进行32位有符号扩展后左移两 位(补“00”,字对准)。

– jump为pseudodirect:指令中的target为26位, 而PC为32位。将target左移2位拼装在PC的低 28位上,PC高4位保持不变。

J-type

op(6 bits) rs(5 bits) rt(5 bits) op(6 bits)

data

16 Sign 32 extend

I-type

MemRead

R-type

llxx@

22

Instruction

条件转移beq

PC + 4 from instruction datapath

Add Sum

Branch target

Read

register 1

Read

Read

rt:ld的目的,sw的源

CPU实验——单周期MIPS处理器设计

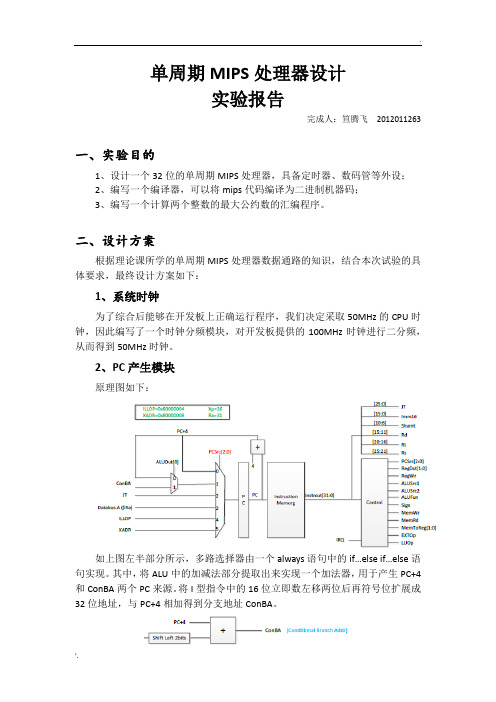

单周期MIPS处理器设计实验报告完成人:笪腾飞2012011263一、实验目的1、设计一个32位的单周期MIPS处理器,具备定时器、数码管等外设;2、编写一个编译器,可以将mips代码编译为二进制机器码;3、编写一个计算两个整数的最大公约数的汇编程序。

二、设计方案根据理论课所学的单周期MIPS处理器数据通路的知识,结合本次试验的具体要求,最终设计方案如下:1、系统时钟为了综合后能够在开发板上正确运行程序,我们决定采取50MHz的CPU时钟,因此编写了一个时钟分频模块,对开发板提供的100MHz时钟进行二分频,从而得到50MHz时钟。

2、PC产生模块原理图如下:如上图左半部分所示,多路选择器由一个always语句中的if…else if…else语句实现。

其中,将ALU中的加减法部分提取出来实现一个加法器,用于产生PC+4和ConBA两个PC来源。

将I型指令中的16位立即数左移两位后再符号位扩展成32位地址,与PC+4相加得到分支地址ConBA。

将跳转指令中的26位目标地址左移两位后,与当前PC的高四位拼接得到跳转地址JT。

将第一个操作数寄存器中的值取出作为PC的一个输入,这是为了实现jr和jalr指令,从$Xp和$Ra寄存器中读取跳转地址。

ILLOP和XADR分别是发生中断和异常时的跳转地址。

下一指令地址的选择由PCSrc决定,而PCSrc是译码后由控制信号模块根据每条指令的操作码(opcode)和函数码(funct)产生。

3、译码模块原理图如上图右半部分所示,将PC作为ROM模块的地址输入,输出即为PC所对应的指令。

分别取出指令中的某些片段,得到$Rs,$Rt,$Rd,shamt,funct,16位立即数和26位跳转地址。

4、控制模块控制模块即控制信号产生模块,六位操作码OpCode,六位函数码[5:0] Funct,定时器中断信号irq和PC最高位PC31作为输入,输出为以下控制信号:(1) R型指令指示信号IsR,值为1表示当前指令为R型指令,否则非R型指令;(2) PC产生的选择信号[2:0] PCSrc,取值0,1,2,3,4及其它,分别选择下一指令不同的PC;(3) 目的寄存器选择信号[1:0]RegDst,被写入的寄存器有四种选择:$Rd,$Rt,$Ra,$Xp,分别由RegDst不同取值完成选择;(4) 写寄存器使能信号RegWr,值为1表示允许对寄存器进行写操作;(5) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将移位量shamt进行0扩展后作为输入,值为0表示将$Rs寄存器中的值作为输入;(6) ALU第一个操作数选择信号ALUSrc1,值为1表示选择将扩展后的32位立即数作为输入,值为0表示将$Rt寄存器中的值作为输入;(7) ALU运算控制信号[5:0] ALUFunc,作为ALU的输入选择不同的运算操作;(8) 有无符号数指示信号Sign,值为1表示有符号数,值为0表示无符号数;(9) 写存储器使能信号MemWr,值为1表示允许对存储器进行写操作;(10) 读存储器使能信号MemRd,值为1表示允许对存储器进行读操作;(11) 写寄存器值的选择信号[1:0] MemToReg,选择ALU结果,存储器读取结果和PC+4其中之一作为写入目的寄存器的值;(12) 符号位扩展指示信号EXTOp,值为1表示对16位立即数进行符号位扩展,值为0表示0扩展;(13) 立即数高位取指令指示信号LUOp,值为1表示当前指令为lui指令,选择将立即数载入高16位低位填0的32位立即数作为ALU输入,值为0表示将正常扩展后的32位立即数作为ALU输入;控制信号的具体产生过程此处略去,在控制信号说明文件中进行详述。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(完整版)M I P S处理器设计说明西安邮电大学实践课程报告书课程名称:计算机组成与实践院(系)名:电子工程学院称专业班级:**学号/姓名:**实习时间:2015年3月6日至2015年6月19日1 课程主要目的本课程是在上学期《计算机组成与设计》课程学习的基础上,通过实践课的方式,依照集成电路设计流程,完成一个简单独立硬件功能电路模块的设计,从而到达对《计算机组成与设计》课程的深入理解和提高电路设计的实践能力,从理论和实验的结合中巩固计算机基本知识,熟练掌握电路设计的基本流程和原理,同时,加深对MIPS系统的组成部件及其电路结构,原理和功能的理解,掌握利用硬件描述语言和EDA工具进行MIPS设计的一般方法。

2 课程的主要内容和任务MIPS是典型的32位定长指令字RISC处理器,要求深入理解MIPS处理器的内部结构及工作原理。

采用verilogHDL设计一个兼容MIPS指令格式,具有10条以上指令功能的单周期CPU硬件电路,该32位MIPS设计内容主要包括系统中的基本组成部件(存储器,指令寄存器,寄存器堆,算术逻辑运算器,程序计数器,多路选择器,符号扩展等)的设计,仿真及硬件下载的方法和过程。

设计过程中使用ISE仿真工具完成设计电路的仿真验证。

3总体设计方案3.1指令及其功能表:(1)R型指令:(2)I型指令:(3)J型指令:3.2总体结构设计:该MIPS主要由8个模块组成,各个子模块分别设计其特定的功能,最终利用一个总的模块进行子模块间连接,使得整个CPU能连贯执行指令,在仿真结果中观察设计结果,最终进行硬件下载,验证设计。

其中各个模块简单功能如下:(1)存储器模块:具备基本的读写功能,用于存放数据和指令。

(2)寄存器堆模块:由32个32位的寄存器组成,提供较大的存储空间,用于存放暂存数据和指令。

(3)算术逻辑运算器模块:执行加减法等算术运算,与非或等逻辑运算,以及比较移位传送等操作的功能部件,是该CPU的设计核心部分,存在不同的运算处理功能,是体现实验设计结果正确性的模块。

(4)立即数扩展模块:执行I型指令时需要立即数扩展,该模块用于MIPS符号扩展,将16位数据扩展为32位数据。

(5)主控制模块:用于控制各个模块之间的分工运行,产生不同数据通路的控制信号,保证指令顺序执行不发生紊乱。

(6)ALU控制模块:用于生成ALU执行各种功能的控制信号,使ALU 内部运行不发生紊乱。

(7)分支跳转指令控制模块:用于生成分支和跳转指令的控制信号。

(8)取指模块:进行指令的取出及译码,同时包括程序计数器PC运行设计。

各模块间关系如下:3.3接口定义和接口时序说明:该CPU由cpu_clk和进行总的控制,并且输出程序计数器低4位进行简易流水灯显示,CPU运行的结果包括逻辑运算等在仿真界面中进行分析和设计验证。

cpu_clk上升沿有效rst位低电平时复位有效4 子模块详细设计4.1 存储器模块设计4.1.1模块方案设计指令存储器用于存放CPU运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit。

4.1.2 接口定义说明序号接口信号名称方向(I/O)1clk I 存储器工作时钟,频率为50Mhz2rst I 存储器片选信号,低有效3ExtMem_Adr [5:0]I 存储器地址线4ExtMem_WR I 存储器读写信号,1为写反之读5ExtMem_Din [31:0]I 存储器输入数据线6ExtMem32 [31:0]O 存储器输出数据线4.1.3 模块仿真验证4.2 寄存器堆模块设计4.2.1模块方案设计该MIPS指令格式中的寄存器号是5bits,指令可以访问32个32位的寄存器。

这32个32位的寄存器构成一个寄存器堆。

4.2.2 接口定义序号接口信号名称方向说明1c lk I 处理器工作时钟2rst I 复位信号3Raddr1[4:0]I 读寄存器堆时的第1个寄存器下标4Raddr2[4:0]I 读寄存器堆时的第2个寄存器下标5Waddr[4:0]I 写寄存器堆时的寄存器下标6We I 寄存器堆写使能7Wdata [31:0]I 待写入寄存器堆的数据8Rdata 1[31:0] O 读寄存器堆时第1个寄存器的输出9Rdata 2[31:0] O 读寄存器堆时第2个寄存器的输出4.2.3 模块仿真验证4.3算术逻辑运算器模块设计4.3.1 模块方案设计运用alu_clt控制运算器的各种运算,包括无符号数的加法运算,有符号数的加法运算,或逻辑运算,与逻辑运算,无符号数的减法运算,无符号小于置1运算,逻辑左移,逻辑右移,算术右移等。

4.3.2 接口定义4.3.3 关键控制信号的产生SUBctr = alu_clt[2];ANDctr = alu_clt[0];OVctr = !alu_clt[1]&alu_clt[0];SIGctr = alu_clt[0];OPctr[1] = alu_clt[2]&alu_clt[1]|alu_clt[3];OPctr[0] = alu_clt[1];4.3.4具体ALU实现如下图所示:ALU操作控制信号O1121异或门异或门ALU_DA[31:0]ALU_DB[31:0]加减法运算器异或门阵列位扩展或门阵列1SUBctr OPctr OVctr SIGctrCinAdd_carryAdd_SignAdd_ResultAdd_OverflowZeroOverflowResult4.3.5 模块仿真验证4.4 立即数扩展模块设计4.4.1 模块方案设计设计一个32位MIPS符号扩展单元SE,用于将16位的数据转换为32位数据。

4.4.2 接口定义序号信号名端口说明描述1 Imm16[15:0] I 来自指令寄存器的16位立即数2 AluSrc I 立即数扩展信号的使能端3 bus[31:0] I4 ExtImm32[31:0] O 符号扩展后的32位立即数4.4.3 模块仿真验证4.5 主控制模块设计4.5.1 模块方案设计以指令译码结果中的6位操作码及相关信号产生整个数据通路中的各个控制信号。

4.5.2 接口定义序号接口信号名称方向(I/O)说明1 op I 操作码2 RegDst O 目的寄存器选择3 AluSrc O ALU输入信号选择4 ExtOp O 立即数扩展的使能信号5 RegWr O 寄存器写使能6 MemWr, O 存储器写使能7 MemtoReg O 寄存器的装载信号选择4.5.3各控制信号的编码规则如下表所示:op 000 001 001 001 001 100 101 001 001 000 000000 000 001 100 101 011 011 010 011 100 101 RegDst 0 1 1 1 1 1 0 1 1 0 0 RegWr 1 1 1 1 1 1 0 1 1 0 0 ExtOp 0 1 0 0 0 1 1 1 0 1 1 AluSrc 0 1 1 1 1 1 1 1 1 0 0 MemWr 0 0 0 0 0 0 1 0 0 0 0 MemtoRe0 0 0 0 0 1 0 0 0 0 0 g4.5.4 模块仿真验证4.6 ALU控制模块设计4.6.1 模块方案设计通过译码结果中的高6位以及相关信号编码出数据通路中各个控制信号。

4.6.2 接口定义序号端口名称输入输出端口说明1 rst I 复位信号(高电平1有效)2 cpu_clk I 时钟(上升沿有效)3 func[5:0] I 功能区分4 op I 操作码5 Alu_ctrl[3:0] O Alu功能信号4.6.3 执行R型指令func对应的Alu_ctrl编码如下表所示:func Alu_ctrl100000 0001100001 0000100010 0101100011 0100100100 0100100101 0011101011 0110101010 0111000000 1001000010 1001000011 1100001000 00004.6.4 模块仿真验证4.7 分支跳转指令控制模块设计4.7.1 模块方案设计运用译码结果的高6位以及ALU的两个输入数据决定分支及分支和跳转指令的控制信号。

4.7.2 接口定义序号信号名端口定义描述1 ALU_DA I 算术逻辑单元数据A2 ALU_DB I 算术逻辑单元数据B3 op I 指令操作码4 func, I R指令的功能操作码5 Jump O 跳转信号使能端6 Branch O 分支信号使能端4.7.3 模块仿真验证4.8 取指模块设计4.8.1 模块方案设计由程序计数器,取出指令以及译码三个子模块构成总的取指模块。

4.8.2 接口定义序号信号名方向(I/O)端口说明1 clk I2 rst I3 ALU_DA I算术逻辑单元数据A4 Branch I分支信号使能端4.8.3 电路基本构成如下图所示:4.8.4 跳转和分支指令执行时PC_out的编码规律Jump:Pc_out<= ALU_DABranch : Pc_out<= Pc_out+1+ALU_DB正常情况下:Pc_out<=Pc_out+14.8.5 模块仿真验证5 设计总体连接及仿真验证5.1 设计总体连线Main_c trRegfileMemALU_ctrclk rstRaddr1[4:0]Raddr2[4:0]Waddr[4:0]WeWdata [31:0]Rdata 1[31:0]Rdata 2[31:0]ALU_DAALU_DBALU_DCALUctrRegDst AluSrc ExtOp RegWr MemWr MemtoRegExtMem_dout1010ImmFlagFetchPCDecodezero overflow Aluctroprs rt rdshamt func imm16Pc_outALU_DA Jump BranchALU_DB rst5.2 在ISE 仿真环境下仿真验证设计结果,仿真结果如下图所示:5.3 仿真结果分析由仿真结果得知该CPU执行的12条指令均正常运行,实验基本成功,但是设计较为简单,并未涵盖太多复杂指令,需要进一步改善,使其趋于完善。

6、实践课总结和心得体会西安邮电大学电子工程学院计算机组成与实践实践课程过程考核表西安邮电大学电子工程学院计算机组成与实践实践课程成绩鉴定表精品文档收集于网络,如有侵权请联系管理员删除。