74LS194芯片资料

移位寄存器194

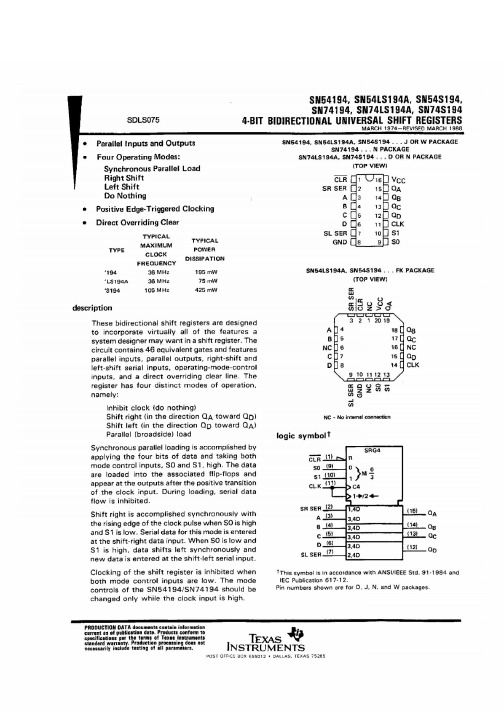

一、74LS194的功能 的功能

二、74LS194构成环形计数器 构成环形计数器

Q 0 Q 1 Q 2 Q 3

74 L S 19 4 SR

C P

把移位寄存器的输出反馈到它的串行输入端, 把移位寄存器的输出反馈到它的串行输入端,就可以进行循 环移位,如图所示,把输出端Q 和右移串行输入端S 相连接, 环移位,如图所示,把输出端Q3 和右移串行输入端SR 相连接, 设初始状态Q =1000,则在时钟脉冲作用下 则在时钟脉冲作用下Q 设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次 边为0100→0010→0001→1000→````` 如图所示, 0100→0010→0001→1000→`````, 边为0100→0010→0001→1000→`````,如图所示,可见它是一 个具有四个有效状态的计数器, 个具有四个有效状态的计数器,这种类型的计数器通常称为环 形计数器。 形计数器。

两片74LS194扩展为 位移位寄存器 扩展为8位移位寄存器 三、两片 扩展为

两片74LS194实现串并转换器 四、两片 实现串并转换器

两片7转换器

移位寄存器实验预习报告要求: 移位寄存器实验预习报告要求:

1、画出74194功能测试的功能表格 、画出 功能测试的功能表格 2、画出由 、画出由74194构成环形计数器的接线图 构成环形计数器的接线图 3、画出两片 扩展成8位的移位寄存器的 、画出两片74194扩展成 位的移位寄存器的 扩展成 接线图 4、画出用两片 构成的七位左移 、画出用两片74194构成的七位左移串/并行 构成的七位左移串 并行 转换器接线路。 转换器接线路。 5、画出用两片 构成的七位左移 、画出用两片74194构成的七位左移并/串行 构成的七位左移并 串行 转换器接线路。 转换器接线路。

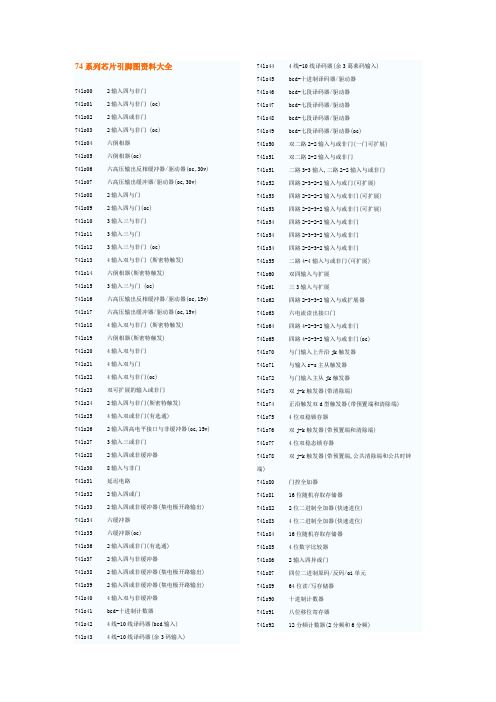

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛/b bs/反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门LS02 LS32 LS51 LS64 LS65异或门比较器LS86译码器LS138 LS139寄存器LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门74LS08│1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门74LS10│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ 8输入与非门74LS30│ 1 2 3 4 5 6 7│ ________└┬—┬—┬—┬—┬—┬—┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或门74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐ 2输入四或非门74LS02│14 13 12 11 10 9 8│___)│Y = A+B│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴—┴—┴—┴—┴—┴—┴┐双与或非门74S51│14 13 12 11 10 9 8│_____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│_______└┬—┬—┬—┬—┬—┬—┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴—┴—┴—┴—┴—┴—┴┐ 4-2-3-2与或非门74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴—┴—┴—┴—┴—┴—┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬—┬—┬—┬—┬—┬—┬—┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴—┴—┴—┴—┴—┴—┴—┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬—┬—┬—┬—┬—┬—┬—┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8*2输入比较器74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴—┴—┴—┴—┴—┴—┴┐双D触发器74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位锁存器74LS373 │20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND等.下面介绍一下常用的74芯片,以便大家在电路中遇到了查询----------------------------------------------------型号内容----------------------------------------------------74ls00 2输入四与非门74ls01 2输入四与非门(oc)74ls02 2输入四或非门74ls03 2输入四与非门(oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门(oc)74ls13 4输入双与非门(斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门(oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门(斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展) 74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展) 74ls53 四路2-2-3-2输入与或非门(可扩展) 74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端) 74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制) 74ls191 同步可逆计数器(bcd,二进制) 74ls192 同步可逆计数器(bcd,二进制) 74ls193 同步可逆计数器(bcd,二进制) 74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制) 74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出) 74ls241 八缓冲器/线驱动器/线接收器(原码三态输出) 74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出) 74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器【发表评论】【告诉好友】【收藏此文】【关闭窗口】上一篇:74LS74引脚图(双D触发器)下一篇:DAC0832引脚图及接口电路。

74LS194中文资料_数据手册_参数

74LS194是一种高速4位双向通用移位寄存器。

作为一种高速、多功能的顺序构建块,它在许多应用中都很有用。

它可以用于插入-串行、左移、右移、串行-并行、并行-串行和并行-并行数据寄存器传输。

LS194A类似于LS195A通用移位寄存器,增加了没有外部连接的移位和保持(什么也不做)modesof操作的功能。

74LS194它利用肖特基二极管夹紧工艺实现高速,并完全兼容于所有的半导体晶体管家族。

•典型的移频为36mhz•异步主复位•保持(什么也不做)模式•完全同步串行或并行数据传输•输入箝位二极管限制高速终止效果逻辑图和真值表显示了LS194A四位双向移位寄存器的功能特性。

LS194A在操作上类似于席恩半导体LS195A通用移位寄存器,用于串行或并行数据寄存器传输。

这两种设备的一些共同特征如下:所有数据和模式控制输入都是边缘触发的,只响应时钟的低到高转换(CP)。

因此,唯一的时间限制是modecontrol和所选的数据输入必须在时钟脉冲正转换之前的一个设置时间是稳定的。

寄存器是完全同步的,所有操作都在15 ns以内(通常),这使得设备对于实现高速cpu或内存缓冲寄存器特别有用。

74LS194四个并行数据输入(P0、P1、P2、P3)是d类型的输入。

当S0和S1都很高时,出现在P0、P1、P2和P3输入上的数据在时钟的下一个低到高的跃迁之后分别被传输到Q0、Q1、Q2和Q3输出。

异步主重置(MR)在低时覆盖所有其他输入条件,并强制Q输出变慢。

增加应用范围的LS194A设计的特殊逻辑特性描述如下:两个模式控制输入(S0, S1)决定设备的同步运行。

如ModeSelection表所示,数据可以从左到右(右移,Q0!)Q1,等等)或者从右向左(左移,Q3!,或者可以输入并行数据,同时加载寄存器的所有四位。

当S0和S1都很低时,74LS194现有的数据被保留在一个“什么也不做”的模式中,而不限制从高到低的时钟转换。

74LS194左右移位寄存器

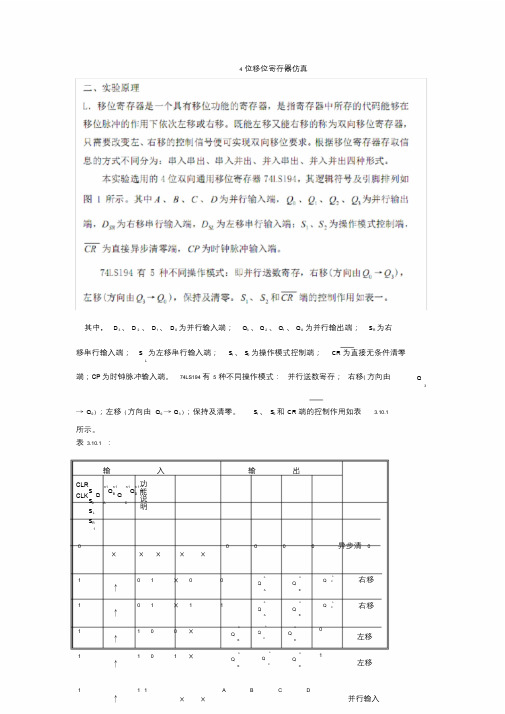

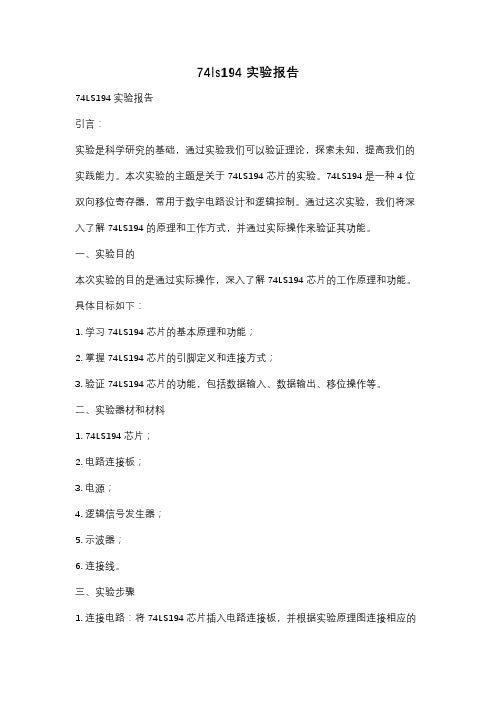

4 位移位寄存器仿真其中, D 3 、 D 2 、 D 1、 D 0 为并行输入端; Q 3 、Q 2 、Q 1 、Q 0 为并行输出端; S R 为右 移串行输入端; S 为左移串行输入端; S 1、S 0 为操作模式控制端; CR 为直接无条件清零L端;CP 为时钟脉冲输入端。

74LS194 有 5 种不同操作模式: 并行送数寄存; 右移( 方向由Q 3 → Q 0 ) ;左移 ( 方向由 Q 0 →Q 3 ) ;保持及清零。

S 1、 S 0 和 CR 端的控制作用如表 3.10.1 所示。

表 3.10.1 :输 入 输 出C LR CLK S S 0 S L S R 1n Q A 1 Q n B 1 n Q C 1 Q n D 1功能说明 0 0 0 0 0 异步清 0× × × × × 1 0 1 × 0 0 ↑ n Q A n Q BQ n C右移1 0 1 × 1 1 ↑ n Q A n Q BQ n C右移1 1 0 0 × ↑ n Q B n Q C n Q D左移1 1 0 1 × ↑ n Q B n Q Cn Q D1左移1 1 1 A B C D ↑ × × 并行输入1 ↑0 0 ××nQAnQBQ n C nQ 保持D移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或并行数据转换为串行数据等。

把移位寄存器的输出反馈到它的串行输入端,就可进行循环移位,如图 3.10.2 所示。

把输出端Q和右移串行输入端S R 相连接,设初始状态Q3 Q2 Q1 Q0 =1000,则在时钟脉冲0作用下,Q Q2 Q1 Q0 将依次变为0100→0010→0001→1000→⋯⋯,可见,它是一个具有3四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

移位寄存器74LS194的逻辑功能及使用方法

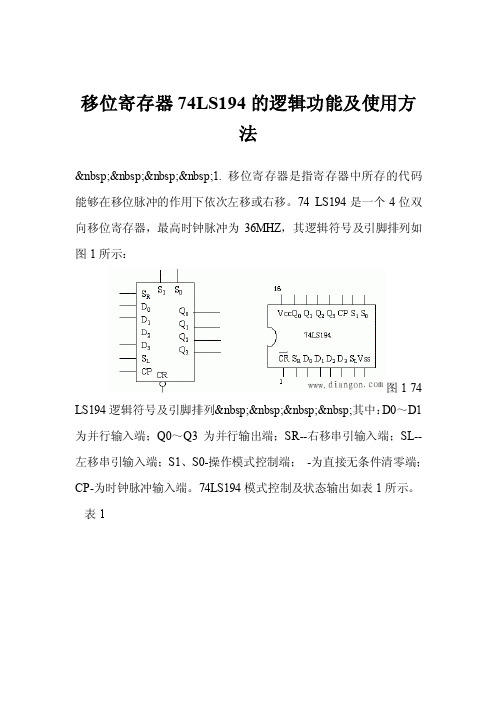

移位寄存器74LS194的逻辑功能及使用方法 1. 移位寄存器是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

74 LS194是一个4位双向移位寄存器,最高时钟脉冲为36MHZ,其逻辑符号及引脚排列如图1所示:图1 74 LS194逻辑符号及引脚排列 其中:D0~D1为并行输入端;Q0~Q3为并行输出端;SR--右移串引输入端;SL--左移串引输入端;S1、S0-操作模式控制端;-为直接无条件清零端;CP-为时钟脉冲输入端。

74LS194模式控制及状态输出如表1所示。

表12. 用74 LS194构成8位移位寄存器 电路如图2所示,将芯片(1)的Q3)接至芯片(2)的SR,将芯片(2)的Q4接至芯片(1)的SL,即可构成8位的移位寄存器。

图2为8位的移位寄存器3. 74 LS194构成环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图3所示。

设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为: 图3环形计数器 图3电路是一个有四个有效状态的计数器,这种类型计数器通常称为环形计数器。

同时输出端输出脉冲在时间上有先后顺序,因此也可以作为顺序脉冲发生器。

74ls194寄存器逻辑功能测试实验原理 -回复

74ls194寄存器逻辑功能测试实验原理-回复74LS194寄存器逻辑功能测试实验原理一、简介74LS194是一种集成电路芯片,属于74系列的高速并行数据输入和串行输出寄存器。

它具有多种逻辑功能,包括数据输入、输出、锁存等。

在数字电路实验中,通常需要对这类芯片进行逻辑功能测试,以验证其是否正常工作。

本实验将介绍如何进行74LS194寄存器的逻辑功能测试,并解释其实验原理。

二、实验器材与测量工具1. 实验器材- 74LS194寄存器芯片- 蜂鸣器- 杜邦线- 面包板- 电源模块2. 测量工具- 逻辑分析仪- 示波器- 万用表- 信号发生器三、实验步骤1. 搭建电路将74LS194芯片插入面包板,并根据芯片的引脚定义连线。

具体电路连接方式如下:- 引脚1和引脚16接地;- 引脚2连接信号发生器的输出端;- 引脚3和引脚4分别连接示波器的通道1和通道2;- 引脚5、引脚6和引脚7连接蜂鸣器;- 引脚8、引脚9、引脚10和引脚11分别连接示波器的通道3、通道4、通道5和通道6;- 引脚12和引脚13分别连接逻辑分析仪的输入端;- 引脚14和引脚15连接电源正负极。

2. 设置信号发生器根据74LS194的信号输入要求,设置信号发生器的输出为有效的高电平和低电平信号。

这里可以设置输出频率为1kHz,并将占空比设置为50。

这样可以确保产生的信号满足寄存器芯片的要求。

3. 运行测试程序使用信号发生器给74LS194芯片输入信号。

首先,输入序列的时间长度为16个时钟周期,通过示波器监测输入序列的波形,确保信号输入正确。

然后,将信号发生器的输出与74LS194芯片的D0引脚相连接,将示波器的通道1选择为D0信号。

通过示波器监测D0信号的波形,确保输入信号成功进入寄存器。

接下来,使用逻辑分析仪监测寄存器的输出数据。

将逻辑分析仪的输入端分别与74LS194芯片的Q0到Q7引脚连接。

通过逻辑分析仪,可以实时观察寄存器的输出数据,并验证其是否与输入数据一致。

194芯片

194芯片194芯片是一种高度集成的数字电路芯片,它由194个晶体管组成,可以执行简单的逻辑运算和存储数据。

该芯片采用的是MOS技术,具有很高的集成度和低功耗特性,广泛应用于计算机、电子设备、通讯等领域。

194芯片的核心是由许多晶体管组成的逻辑电路,它能够实现与、或、非等基本逻辑运算。

这些逻辑门的输出可以与其他芯片或器件相连,通过电信号传递和处理信息。

因此,194芯片在电子设备中起到了至关重要的作用。

除了基本逻辑运算的功能外,194芯片还可以存储和处理数据。

它内部包含了存储单元,可以用来存储二进制数或其他数据。

这使得计算机能够进行数据处理和存储,从而实现各种应用。

194芯片采用的是MOS技术,即金属氧化物半导体技术。

这种技术能够将晶体管等器件制造在硅基底上,并使用薄膜层保护和连接各个器件。

这样可以实现非常高的集成度,将复杂的电路集成在小小的芯片上。

与传统的电子元器件相比,194芯片具有很多优点。

首先,由于采用了MOS技术,194芯片的功耗非常低。

这意味着它可以在低电压下工作,减少了能量消耗和发热问题。

其次,由于高度集成,194芯片的尺寸非常小,可以方便地嵌入各种电子设备中。

此外,由于晶体管的使用寿命很长,194芯片的可靠性也非常高。

然而,194芯片也存在一些局限性。

首先,由于晶体管数量有限,它只能处理简单的逻辑运算和存储少量数据。

对于复杂的计算和数据处理任务,需要更大规模的芯片或者芯片组合才能完成。

其次,由于电子器件的特性和工艺限制,194芯片的工作速度相对较慢。

对于一些对速度要求较高的应用,可能需要采用更先进的芯片技术。

综上所述,194芯片是一种高度集成的数字电路芯片,具有简单逻辑运算和数据存储功能。

它采用MOS技术,具有高集成度和低功耗的特点,适用于计算机、电子设备和通讯等领域。

尽管存在一些局限性,但随着技术的不断进步,芯片的功能和性能也将得到进一步提升。

74LS194中文资料

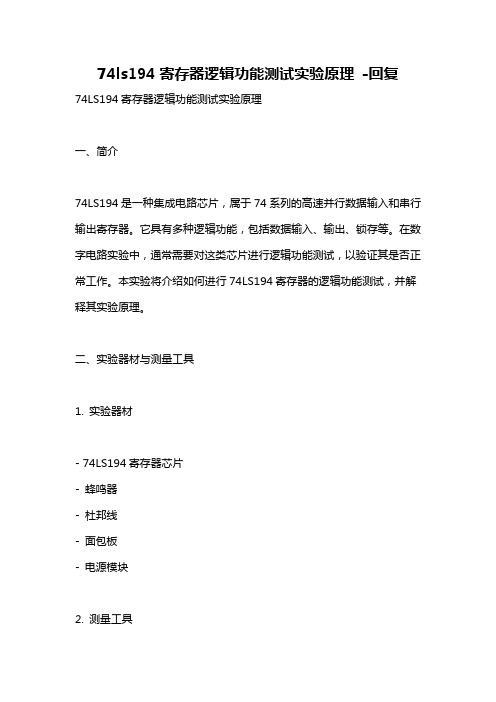

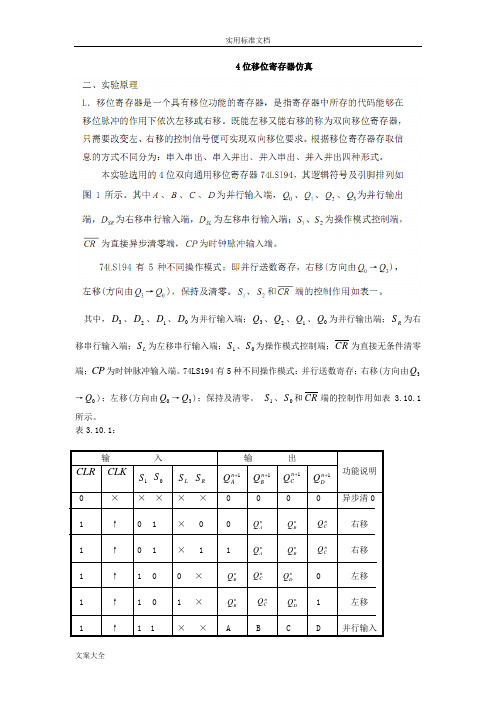

© 2000 Fairchild Semiconductor Corporation DS006407August 1986Revised March 2000DM74LS194A 4-Bit Bidirectional Universal Shift RegisterDM74LS194A4-Bit Bidirectional Universal Shift RegisterGeneral DescriptionThis bidirectional shift register is designed to incorporate virtually all of the features a system designer may want in a shift register; they feature parallel inputs, parallel outputs,right-shift and left-shift serial inputs, operating-mode-con-trol inputs, and a direct overriding clear line. The register has four distinct modes of operation, namely:Parallel (broadside) loadShift right (in the direction Q A toward Q D )Shift left (in the direction Q D toward Q A )Inhibit clock (do nothing)Synchronous parallel loading is accomplished by applying the four bits of data and taking both mode control inputs,S0 and S1, HIGH. The data is loaded into the associated flip-flops and appear at the outputs after the positive transi-tion of the clock input. During loading, serial data flow is inhibited.Shift right is accomplished synchronously with the rising edge of the clock pulse when S0 is HIGH and S1 is LOW.Serial data for this mode is entered at the shift-right data input. When S0 is LOW and S1 is HIGH, data shifts left synchronously and new data is entered at the shift-left serial input.Clocking of the flip-flop is inhibited when both mode control inputs are LOW.Featuress Parallel inputs and outputs s Four operating modes:Synchronous parallel load Right shift Left shift Do nothings Positive edge-triggered clocking s Direct overriding clearOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramOrder Number Package NumberPackage DescriptionDM74LS194AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow DM74LS194ANN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 2D M 74L S 194AFunction TableH = HIGH Level (steady state)L = LOW Level (steady state)X = Don’t Care (any input, including transitions)↑ = Transition from LOW-to-HIGH levela, b, c, d = The level of steady state input at inputs A, B, C or D, respectively.Q A0, Q B0, Q C0, Q D0 = The level of Q A , Q B , Q C , or Q D , respectively, before the indicated steady state input conditions were established.Q An , Q Bn , Q Cn , Q Dn = The level of Q A , Q B , Q C , respectively, before the most-recent ↑ transition of the clock.Logic DiagramInputsOutputs Clear Mode Clock Serial Parallel Q A Q B Q C Q D S1S0Left Right A B C D L X X X X X X X X X L L L L H X X L X X X X X X Q A0Q B0Q C0Q D0H H H ↑X X a b c d a b c d H L H ↑X H X X X X H Q An Q Bn Q Cn H L H ↑X L X X X X L Q An Q Bn Q Cn H H L ↑H X X X X X Q Bn Q Cn Q Dn H H H L ↑L X X X X X Q Bn Q Cn Q Dn L HLLXXXXXXXQ A0Q B0Q C0Q D0DM74LS194AAbsolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsNote 2: C L = 15 pF , T A = 25°C and V CC = 5V.Note 3: C L = 50 pF , R L = 2 k Ω, T A = 25°C and V CC = 5V.Note 4: T A = 25°C and V CC = 5V.Electrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 5: All typicals are at V CC = 5V, T A = 25°C.Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.Note 7: With all outputs open, inputs A through D grounded, and 4.5V applied to S0, S1, CLEAR, and the serial inputs, I CC is tested with momentary ground,then 4.5V applied to CLOCK.Supply Voltage 7V Input Voltage7VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range−65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −0.4mA I OL LOW Level Output Current 8mA f CLK Clock Frequency (Note 2)025MHz Clock Frequency (Note 3)020t W Pulse Width Clock 20ns (Note 4)Clear 20t SU Setup Time Mode 30ns (Note 4)Data20t H Hold Time (Note 4)0ns t REL Clear Release Time (Note 4)25ns T AFree Air Operating Temperature70°CSymbol ParameterConditionsMinTyp Max Units (Note 5)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.73.4VOutput Voltage V IL = Max, V IH = Min V OLLOW Level V CC = Min, I OL = Max 0.350.5Output VoltageV IL = Max, V IH = Min VI OL = 4 mA, V CC = Min 0.4I I Input Current @ Max Input Voltage V CC = Max, V I = 7V 0.1mA I IH HIGH Level Input Current V CC = Max, V I = 2.7V 20µA I IL LOW Level Input Current V CC = Max, V I = 0.4V −0.4mA I OS Short Circuit Output Current V CC = Max (Note 6)−20−100mA I CCSupply CurrentV CC = Max (Note 7)1523mA 4D M 74L S 194ASwitching Characteristicsat V CC = 5V and T A = 25°C Note 8: All typicals are at V CC = 5V, T A = 25°C.Note 9: Not more than one output should be shorted at a time, and the duration should not exceed one second.Note 10: With all outputs open, inputs A through D grounded, and 4.5V applied to S0, S1, CLEAR, and the serial inputs, I CC is tested with momentary ground, then 4.5V applied to CLOCK.Timing DiagramTypical Clear, Load, Right-Shift, Left-Shift, Inhibit, and Clear SequencesSymbol ParameterFrom (Input)C L = 50 pF, R L = 2 k ΩUnits To (Output)Min Maxf MAX Maximum Clock Frequency 20MHz t PLH Propagation Delay Time Clock to Any Q 26ns LOW-to-HIGH Level Output t PHL Propagation Delay Time Clock to Any Q 35ns HIGH-to-LOW Level Output t PHLPropagation Delay Time Clear to Any Q38nsHIGH-to-LOW Output DM74LS194APhysical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 NarrowPackage Number M16A6D M 74L S 194A 4-B i t B i d i r e c t i o n a l U n i v e r s a l S h i f t R e g i s t e rPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

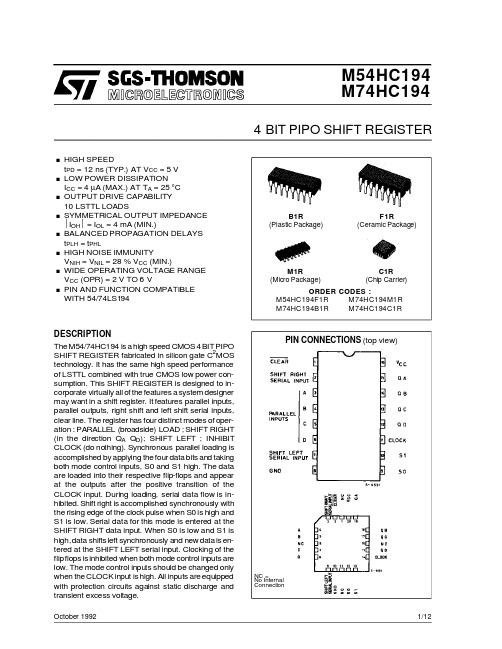

四位可逆计数器74194芯片功能

M54HC194M74HC194October 19924BIT PIPO SHIFT REGISTERB1R(Plastic Package)ORDER CODES :M54HC194F1R M74HC194M1R M74HC194B1R M74HC194C1RF1R(Ceramic Package)M1R(Micro Package)C1R (Chip Carrier)PIN CONNECTIONS (top view)NC =No Internal Connecti o nDESCRIPTION.HIGH SPEEDt PD =12ns (TYP.)AT V CC =5V .LOW POWER DISSIPATION I CC =4µA (MAX.)AT T A =25°C .OUTPUT DRIVE CAPABILITY 10LSTTL LOADS.SYMMETRICAL OUTPUT IMPEDANCE I OH =I OL =4mA (MIN.).BALANCED PROPAGATION DELAYS t PLH =t PHL.HIGH NOISE IMMUNITYV NIH =V NIL =28%V CC (MIN.).WIDE OPERATING VOLTAGE RANGE V CC (OPR)=2V TO 6V.PIN AND FUNCTION COMPATIBLE WITH 54/74LS194The M54/74HC194isa high speed CMOS 4BITPIPOSHIFT REGISTER fabricated in silicon gate C 2MOS technology.It has the same high speed performance of LSTTL combined with true CMOS low power con-sumption.This SHIFT REGISTER is designed to in-corporate virtually all of the features a system designer may want in a shift register.It features parallel inputs,parallel outputs,right shift and left shift serial inputs,clear line.The register has four distinct modes of oper-ation :PARALLEL (broadside)LOAD ;SHIFT RIGHT (in the direction Q A Q D );SHIFT LEFT ;INHIBIT CLOCK (do nothing).Synchronous parallel loading is accomplished by applying the four data bitsand taking both mode control inputs,S0and S1high.The data are loaded into their respective flip-flops and appear at the outputs after the positive transition of the CLOCK input.During loading,serial data flow is in-hibited.Shift right is accomplished synchronously with the rising edge of the clock pulse when S0is high and S1is low.Serial data for this mode is entered at the SHIFT RIGHT data input.When S0is low and S1is high,data shiftsleft synchronously and new data is en-tered at the SHIFT LEFT serial input.Clocking of the flipflops isinhibited when both mode control inputs are low.The mode control inputs should be changed only when the CLOCK input ishigh.All inputs are equipped with protection circuits against static discharge and transient excess voltage.1/12INPUT AND OUTPUT EQUIVALENT CIRCUITTRUTH TABLEINPUTSOUTPUSCLEARMODE CLOCK SERIAL PARALLEL QA QB QC QD S1S0LEFT RIGHT A B C D L X X XX X X X X X L L L L H X X X X X X X X QA0QB0QC0QD0H H H X X a b c d a b c d H L H X H X X X X H QAn QBn QCn H L H X L X X X X L QAn QBn QCn H H L H X X X X X QBn QCn QDn H H H L LX X X X X QBn QCn QDn L HLLX XXXXXXQA0QB0QC0QD0X:Don’t Care :Don’t Carea ~d:The level of stead y state input voltage at input A ~D respact ively QA0~QD0:No chan geQAn ~QDn:The level of QA,QB,QC,respec tively,before the mst recent positive transition of the clock.PIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION 1CLEAR Asynchronous Reset Input (Active LOW)2SR Serial Data Input (Shift Right)3,4,5,6A to D Parallel Data Input 7SL Serial Data Input (Shift Left)9,10S0,S1Mode Control Inputs 11CLOCK Clock Input (LOW to HIGH Edge-triggered)15,14,13,12QA to QD Paralle Outputs 8GND Ground (0V)16V CCPositive Supply VoltageIEC LOGIC SYMBOLM54/M74HC1942/12M54/M74HC194 LOGIC DIAGRAMTIMING CHART3/12ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Source Sink Current Per Output Pin±25mAI CC or I GND DC V CC or Ground Current±50mAP D Power Dissipation500(*)mW T stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied. (*)500mW:≅65o C derate to300mW by10mW/o C:65o C to85o CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage2to6V V I Input Voltage0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:M54HC SeriesM74HC Series -55to+125-40to+85o Co Ct r,t f Input Rise and Fall Time V CC=2V0to1000nsV CC=4.5V0to500V CC=6V0to400M54/M74HC1944/12DC SPECIFICATIONSSymbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL Low Level InputVoltage 2.00.50.50.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH High LevelOutput Voltage 2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-4.0mA 4.18 4.31 4.13 4.106.0I O=-5.2mA 5.68 5.8 5.63 5.60V OL Low Level OutputVoltage 2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=4.0mA0.170.260.330.406.0I O=5.2mA0.180.260.330.40I I Input LeakageCurrent 6.0V I=V CC or GND±0.1±1±1µAI CC Quiescent SupplyCurrent 6.0V I=V CC or GND44080µAM54/M74HC1945/12AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime2.0307595115ns4.581519236.07131620t PLH t PHL PropagationDelay Time(CLOCK-Q)2.048115145175ns4.5152329356.013202530t PHL PropagationDelay Time(CLEAR-Q)2.052125155190ns 4.5172531386.015212632f MAX Maximum ClockFrequency 2.0 6.213 5.0 4.2MHz 4.5315025216.037593025t W(H) t W(L)Minimum PulseWidth(CLOCK)2.020*******ns4.551519226.04131619t W(L)Minimum PulseWidth(CLEAR)2.024*******ns 4.561519226.05131619t s Minimum Set-upTime(SI,PI-CK)2.020*******ns 4.551519226.04131620t s Minimum Set-upTime(S0,S1-CK)2.028*******ns 4.571519236.06131620t h Minimum HoldTime 2.0000ns 4.50006.0000t REM MinimumRemoval Time 2.0555ns 4.55556.0555C IN Input Capacitance5101010pFC PD(*)Power DissipationCapacitance 85pF(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load. (Refer to Test Circuit).Average operting current can be obtained by the following equ ation.I CC(opr)=C PD•V CC•f IN+I CCM54/M74HC1946/12M54/M74HC194 SWITCHING CHARACTERISTICS TEST WAVEFORMTEST CIRCUIT I CC(Opr.)7/12M54/M74HC194Plastic DIP16(0.25)MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B0.77 1.650.0300.065 b0.50.020b10.250.010D200.787 E8.50.335e 2.540.100e317.780.700F7.10.280I 5.10.201L 3.30.130Z 1.270.050P001C 8/12M54/M74HC194 Ceramic DIP16/1MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A200.787B70.276D 3.30.130E0.380.015e317.780.700F 2.29 2.790.0900.110G0.40.550.0160.022H 1.17 1.520.0460.060L0.220.310.0090.012M0.51 1.270.0200.050N10.30.406P7.88.050.3070.317Q 5.080.200P053D9/12M54/M74HC194SO16(Narrow)MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0040.007 a2 1.650.064 b0.350.460.0130.018 b10.190.250.0070.010 C0.50.019c145°(typ.)D9.8100.3850.393E 5.8 6.20.2280.244e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208L0.5 1.270.0190.050 M0.620.024 S8°(max.)P013H 10/12M54/M74HC194PLCC20MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A9.7810.030.3850.395B8.899.040.3500.356D 4.2 4.570.1650.180d1 2.540.100d20.560.022E7.378.380.2900.330e 1.270.050e3 5.080.200F0.380.015G0.1010.004M 1.270.050M1 1.140.045P027A11/12M54/M74HC194Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A12/12。

74LS194左右移位寄存器

74LS194左右移位寄存器4位移位寄存器仿真其中,3D、2D、1D、0D为并行输入端;3Q、2Q、1Q、0Q为并行输出端;R S为右移串行输入端;L S为左移串行输入端;1S、0S为操作模式控制端;R C为直接无条件清零端;CP为时钟脉冲输入端。

74LS194有5种不同操作模式:并行送数寄存;右移(方向由3Q→0Q);左移(方向由0Q→3Q);保持及清零。

1S、0S和R C端的控制作用如表3.10.1所示。

表3.10.1:输入输出功能移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或并行数据转换为串行数据等。

把移位寄存器的输出反馈到它的串行输入端,就可进行循环移位,如图3.10.2所示。

把输出端0Q 和右移串行输入端RS 相连接,设初始状态3Q2Q 1Q 0Q =1000,则在时钟脉冲作用下,3Q2Q 1Q 0Q 将依次变为0100→0010→0001→1000→……,可见,它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图3.10.2电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

图3.10.2四、实验室操作实验内容:1.逻辑功能验证移位寄存器(1)将两块74LS74集成片插入IC 空插座中,按图41(a)连线,接成左移移位寄存器。

接好电源即可开始实验。

先置数据0001,然后输入移位脉冲。

置数,即把Q3、Q2、Q1、Q置成0001,按动单次脉冲,移位寄存器实现左移功能。

(2)按图42(b)连线,方法同(1)则完成右移移位功能验证。

(a)左移移位(b)右移移位图41 D触发器组成移位寄存器的实验线路图(1). 并行输入:参阅图 3.10.3,设计画出实验电路图,在THD-1型(或Dais-2B型)实验台上将实验线路搭好。

根据74LS194功能表3.10.1要求,进行并行输入实验,并填写表3.10.2。

74ls194

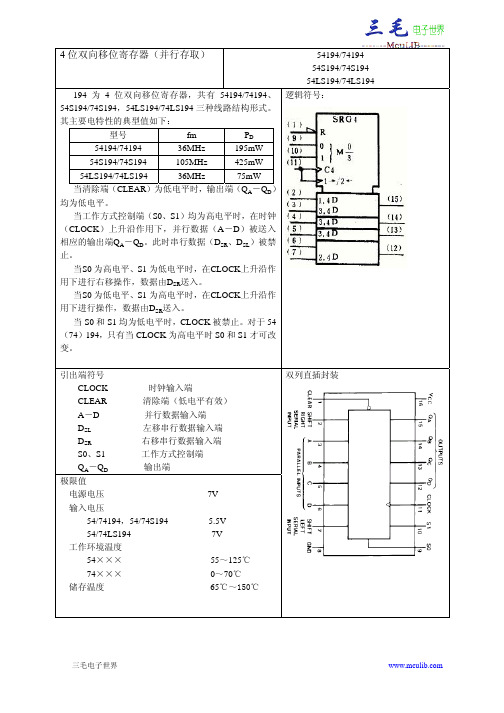

54194/74194

54S194/74S194

194 为 4 位双向移位寄存器,共有 54194/74194、 54S194/74S194,54LS194/74LS194 三种线路结构形式。 其主要电特性的典型值如下:

54LS194/74LS194 逻辑符号:

型号 54194/74194

23

单位 V V V mA µA mA mA mA

动态特性(TA=25℃)

参

数[2]

测试条件

‘194

‘S194

‘LS194

单位

最小 最大 最小 最大 最小 最大

fmax

Vcc =5V,CL=15Pf,RL=400Ω 25

70

25

MHz

tPLH CLOCK → 任一 (‘194 为 280Ω,‘LS194 为

引出端符号

CLOCK

时钟输入端

CLEAR A-D

清除端(低电平有效) 并行数据输入端

DSL DSR S0、S1 QA-QD 极限值

左移串行数据输入端 右移串行数据输入端 工作方式控制端 输出端

电源电压

7V

输入电压

54/74194,54/74S194

5.5V

54/74LS194

7V

工作环境温度

54××× 74×××

0.4 0.4

0.5 0.5

II最大输入电压时输入电 Vcc=最大 流

IIH输入高电平电流

Vcc=最大

VI=5.5V VI=7V VIH=2.4V VIH=2.7V

1

1

40 50

IIL输入低电平电流

Vcc=最大,

VIL=0.4V VIL=0.5V

74ls194实验报告

74ls194实验报告《74LS194实验报告》实验目的:1. 了解74LS194的基本原理和工作方式2. 掌握使用74LS194进行数据移位操作的方法3. 熟悉74LS194的应用场景和特点实验器材:1. 74LS194芯片2. 时钟信号发生器3. 电源供应器4. 示波器5. 逻辑分析仪6. 连接线7. 电路板实验原理:74LS194是一种4位并行输入、串行输出的移位寄存器。

它可以将并行输入的数据按照时钟信号进行移位操作,并且输出到串行输出端。

其内部结构包括4个D触发器和一组控制逻辑电路,能够实现数据的移位、存储和输出功能。

实验步骤:1. 将74LS194芯片插入电路板中,并连接好电源供应器和时钟信号发生器。

2. 使用连接线将74LS194的并行输入端连接到示波器和逻辑分析仪,以便观察输入数据的变化。

3. 设置时钟信号发生器的频率和占空比,观察并记录74LS194输出端的数据变化。

4. 通过改变并行输入端的数据和时钟信号的频率,观察74LS194的移位操作情况。

实验结果:经过实验观察和记录,我们发现74LS194能够准确地按照时钟信号进行数据移位操作,并将移位后的数据输出到串行输出端。

同时,通过改变输入数据和时钟信号的频率,可以实现不同的移位模式和速度。

实验结论:通过本次实验,我们深入了解了74LS194移位寄存器的工作原理和特点,掌握了使用74LS194进行数据移位操作的方法,同时也熟悉了其应用场景和实际应用价值。

这将为我们今后的电子电路设计和数字信号处理提供重要的参考和指导。

总结:本次实验不仅加深了我们对数字电路和移位寄存器的理解,同时也提高了我们的动手能力和实验操作技巧。

通过实际操作和观察,我们对74LS194的工作原理和应用有了更加深入的认识,为我们今后的学习和工作打下了坚实的基础。

74系列芯片引脚图资料大1

74系列芯片引脚图资料大全74ls00 2输入四与非门74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入) 74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展)74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展)74ls53 四路2-2-3-2输入与或非门(可扩展)74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端)74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出) 74ls156 双2-4译码器/分配器(集电极开路输出) 74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步) 74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步) 74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制)74ls191 同步可逆计数器(bcd,二进制)74ls192 同步可逆计数器(bcd,二进制)74ls193 同步可逆计数器(bcd,二进制)74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制)74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出)74ls241 八缓冲器/线驱动器/线接收器(原码三态输出)74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出) 74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除)74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器。

74ls194功能

74ls194功能

74LS194是一种具有四个主要功能的16位边缘触发通用串行-

并行移位寄存器。

以下是74LS194的主要功能:

1. 并行输入:74LS194有16个并行输入引脚,称为A0-A15,

可以同时将16位数据并行输入到寄存器中。

2. 串行输入:74LS194有一个串行输入引脚,称为D。

通过串

行输入,可以逐位输入的方式将数据输入到寄存器中。

3. 串行输出:74LS194有一个串行输出引脚,称为Q。

通过串

行输出引脚,可以逐位输出寄存器中的数据。

4. 并行输出:74LS194有16个并行输出引脚,称为Q0-Q15。

可以同时从寄存器中将16位数据并行输出。

5. 移位功能:74LS194具有向左和向右移位的能力。

通过控制

引脚,可以选择移位方向。

6. 边缘触发:74LS194是边缘触发器件,这意味着它只在时钟

信号的边沿触发数据输入和输出。

可以通过时钟引脚控制寄存器的操作。

7. 计数功能:74LS194可以用作计数器。

通过适当连接控制引脚,可以将多个74LS194级联,以实现更大范围的计数器。

8. 加载功能:74LS194可以将并行输入的数据加载到寄存器中,

而不进行移位操作。

总而言之,74LS194是一个功能强大的通用寄存器,可以实现并行输入、并行输出、串行输入、串行输出、移位和计数等多种功能。

它适用于广泛的应用,如数据存储和计数器设计。

74ls系列芯片功能和参数详细介绍

74、74HC、74LS系列芯片资料系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。

7400 QUAD 2-INPUT NAND GATES 与非门7401 QUAD 2-INPUT NAND GATES OC 与非门7402 QUAD 2-INPUT NOR GATES 或非门7403 QUAD 2-INPUT NAND GATES 与非门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV 高输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与非门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与非门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选一74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发生检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输入与非门7426 QUAD 2-INPUT NAND GATES 与非门7427 TRIPLE 3-INPUT NOR GATES 三输入或非门7430 8-INPUT NAND GATES 八输入端与非门7432 QUAD 2-INPUT OR GATES 二输入或门7438 2-INPUT NAND GATE BUFFER 与非门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位比较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输入与非门74HC02 QUAD 2-INPUT NOR GATES 双输入或非门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与非门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输入与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输入与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与非门74HC133 13-INPUT NAND GATES 十三输入与非门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线至8线译码器74HC139 2-4 LINE DECODER 2线至4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输入多路器74HC154 4-16 LINE DECODER 4线至16线译码器74HC155 2-4 LINE DECODER 2线至4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER 二进制计数器74HC163 DECADE COUNTERS 十进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串入并出74HC165 PARALLEL-SERIAL SHIFT REG 并入串出74HC166 SERIAL-PARALLEL SHIFT REG 串入并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发生器74HC190 BINARY UP/DN COUNTER 二进制加减计数器74HC191 DECADE UP/DN COUNTER 十进制加减计数器74HC192 DECADE UP/DN COUNTER 十进制加减计数器74HC193 BINARY UP/DN COUNTER 二进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并行移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四入与非门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线至8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER 八个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或非74HC27 TRIPLE 3-INPUT NOR GATE三个3输入或非门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发生器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输入端与非门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER 非反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位二进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输入或门74HC42 BCD TO DECIMAL BCD转十进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4至16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD用的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或非门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器入锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER 八路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER 八路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或非门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输入异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与非门74LS02 QUAD 2-INPUT NOR GATES 或非门74LS03 QUAD 2-INPUT NAND GATES 与非门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与非门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线至8线译码器74LS139 2-4 LINE DECODER 2线至4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输入多路器74LS155 2-4 LINE DECODER 2线至4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER 二进制计数器74LS161A BINARY COUNTER 二进制计数器74LS162A BINARY COUNTER 二进制计数器74LS163A DECADE COUNTERS 十进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串入并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS169 4BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER 二进制加减计数器74LS191 DECADE UP/DN COUNTER 十进制加减计数器74LS192 DECADE UP/DN COUNTER 十进制加减计数器74LS193 BINARY UP/DN COUNTER 二进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并行移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四入与非门74LS21 4-INPUT AND GATE 四输入端与门74LS240 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS244 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输入或非门74LS279 QUAD R-S LATCHES 四个RS非锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或非缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES 八输入端与非门74LS32 QUAD 2-INPUT OR GATES 二输入或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并行寄存器74LS38 2-INPUT NAND GATE BUFFER 与非门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转十进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或非门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路比较器74LS684 8BIT MAGNITUDE COMPARATOR 8路比较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输入异或门74LS90 DECADE/BINARY COUNTER 十/二进制计数器74LS95B 4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输入异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。

74194中文资料

2/12

元器件交易网

M54/M74HC194

LOGIC DIAGRAM

TIMING CHART

3/12

元器件交易网

M54/M74HC194

ABSOLUTE MAXIMUM RATINGS

Symbol VCC VI VO IIK IOK IO ICC or IGND PD Tstg TL Supply Voltage DC Input Voltage DC Output Voltage DC Input Diode Current DC Output Diode Current DC Output Source Sink Current Per Output Pin DC VCC or Ground Current Power Dissipation Storage Temperature Lead Temperature (10 sec) Parameter Value -0.5 to +7 -0.5 to VCC + 0.5 -0.5 to VCC + 0.5 ± 20 ± 20 ± 25 ± 50 500 (*) -65 to +150 300 Unit V V V mA mA mA mA mW

MODE S1 X X H L L H H L S0 X X H H H L L L

CLOCK X

SERIAL LEFT X X X X X H L

X

X

: Don’t Care : The level of steady state input voltage at input A ~ D respactively : No change : The level of QA, QB, QC, respectively, before the mst recent positive transition of the clock.

74ls194实验报告

74ls194实验报告74LS194实验报告引言:实验是科学研究的基础,通过实验我们可以验证理论,探索未知,提高我们的实践能力。

本次实验的主题是关于74LS194芯片的实验。

74LS194是一种4位双向移位寄存器,常用于数字电路设计和逻辑控制。

通过这次实验,我们将深入了解74LS194的原理和工作方式,并通过实际操作来验证其功能。

一、实验目的本次实验的目的是通过实际操作,深入了解74LS194芯片的工作原理和功能。

具体目标如下:1. 学习74LS194芯片的基本原理和功能;2. 掌握74LS194芯片的引脚定义和连接方式;3. 验证74LS194芯片的功能,包括数据输入、数据输出、移位操作等。

二、实验器材和材料1. 74LS194芯片;2. 电路连接板;3. 电源;4. 逻辑信号发生器;5. 示波器;6. 连接线。

三、实验步骤1. 连接电路:将74LS194芯片插入电路连接板,并根据实验原理图连接相应的电源和信号线。

2. 设置逻辑信号发生器:根据实验要求,设置逻辑信号发生器的输出频率和幅度。

3. 测量电压波形:使用示波器测量74LS194芯片的输出电压波形,并记录下相应的数据。

4. 进行数据输入操作:通过逻辑信号发生器输入相应的数据,观察74LS194芯片的输出是否正确。

5. 进行移位操作:通过逻辑信号发生器输入移位信号,观察74LS194芯片的输出是否正确。

6. 记录实验数据:将实验过程中的数据和观察结果记录下来,方便后续分析和总结。

四、实验结果与分析通过实验,我们得到了74LS194芯片的输出电压波形,并观察到了数据输入和移位操作的结果。

根据实验数据和观察结果,我们可以得出以下结论:1. 74LS194芯片能够正确地接收和输出数据,实现数据的存储和传输功能;2. 在进行移位操作时,74LS194芯片能够按照预期的方式将数据进行移位,并输出正确的结果;3. 在实验过程中,我们还发现了一些异常情况,例如输入信号的幅度过大或过小时,芯片可能无法正常工作。

74LS194左右移位寄存器

4位移位寄存器仿真其中,3D 、2D 、1D 、0D 为并行输入端;3Q 、2Q 、1Q 、0Q 为并行输出端;R S 为右移串行输入端;L S 为左移串行输入端;1S 、0S 为操作模式控制端;R C 为直接无条件清零端;CP 为时钟脉冲输入端。

74LS194有5种不同操作模式:并行送数寄存;右移(方向由3Q →0Q );左移(方向由0Q →3Q );保持及清零。

1S 、0S 和R C 端的控制作用如表3.10.1所示。

表3.10.1:移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或并行数据转换为串行数据等。

把移位寄存器的输出反馈到它的串行输入端,就可进行循环移位,如图3.10.2所示。

把输出端0Q 和右移串行输入端R S 相连接,设初始状态3Q 2Q 1Q 0Q =1000,则在时钟脉冲作用下,3Q 2Q 1Q 0Q 将依次变为0100→0010→0001→1000→……,可见,它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。

图3.10.2电路可以由各1. 逻辑功能验证移位寄存器(1)将两块74LS74集成片插入IC 空插座中,按图41(a )连线,接成左移移位寄存器。

接好电源即可开始实验。

先置数据0001,然后输入移位脉冲。

置数,即把Q 3、Q 2、Q 1、Q 0置成0001,按动单次脉冲,移位寄存器实现左移功能。

(2)按图42(b )连线,方法同(1)则完成右移移位功能验证。

(a)左移移位(b)右移移位图41D触发器组成移位寄存器的实验线路图(1). 并行输入:参阅图3.10.3,设计画出实验电路图,在THD-1型(或Dais-2B 型)实验台上将实验线路搭好。

根据74LS194功能表3.10.1要求,进行并行输入实验,并填写表3.10.2。

(2). 动态保持:根据74LS194功能表3.10.1“保持”功能,观察单脉冲作用时输出端变化情况,并填表3.10.3。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单脉冲的提供有两种途径:

实验目的

逻辑箱脉冲源

单脉冲

实验原理

低频信号源TTL 输出(1Hz)

实验内容

注意事项

现代电子技术实验

四、注意事项

1、出现故障应作哪些基本检查? 电源

实验目的

时钟 功能端(Cr 、S1、 S0 ) 数据输入是否正确

实验原理

实验内容

注意事项

2、实验中的环形计数器不具备自启动功能,抗 干扰能力差。改变电路连接时如进入死循环,必 须给电路重新赋初值。

实验目的

DSR

清零 置数

CP

0 1

DR

1 1

DL

1 1

Q0

0 0

Q1

0 1

Q2

0 0

Q3

0 1

实验原理

左移

实验内容

2 3

4

0 0

1

0 0

1

左移

右移

注意事项

右移 保持

5 6

1 0

1 0

现代电子技术实验

2、环形计数器的测试。首先应给寄存器置入初始 值(自拟),之后将工作状态设为对应的串行移 位,完成下表。

现代电子技术实验

移位寄存器的扩展

实验目的

实验原理

ห้องสมุดไป่ตู้

74LS194(1)

实验内容

74LS194(2)

注意事项

串行输入

构成八位右移串行移位寄存器

现代电子技术实验

2、环形计数器(又称循环移位寄存器)

把移位寄存器的串行输入端与输出端相连可以 构成环形计数器。例:DSR和Q3相连,可构成右移环 形计数器。

实验目的

n 2

0 X X

1 1 1 1 1 1

X

X

X

X X d0 X

X X

↑ a

X X X

b c

0

0

b

0

c

0

d

d a

0 1 d0 1 0 0 0 X X

↑ X ↑ X X X

X X X d0 X X X X X X

n 1

n n Q 0 Q1n Q 2 d

0

n Q n Q3 Q 2

n n Q 0 Q1n Q n Q 3 2

实验目的

CP序号 1

Q0 0

Q1 1

Q2 0

Q3 0

实验原理

2

实验内容

3

注意事项

4 5

现代电子技术实验

3、将CP改为10kHz连续脉冲,重复以上操作,用示波 器观测CP, Q0--Q3的波形(双踪观测)。

实验目的

CP

v t

实验原理

Q0

Q1 Q2 Q3

v

t v

实验内容

t

v t v

注意事项

参考波形

t

现代电子技术实验

1

0 0

0

1 0

0

注意事项

5

74LS194

现代电子技术实验

把移位寄存器的输出端Q3和DSR相连,可构成 简单的右移环形计数器。若把移位寄存器的输出 端Q0和DSL相连,可构成简单的左移环形计数器。

实验目的

实验原理

实验内容

注意事项

三、实验内容

现代电子技术实验

1、基本功能测试。要求针对74LS194各项基本功能。

y1

y2 若选用y2 做触发源 示波器上显 示的y2波形

level

顺序脉冲发生器

现代电子技术实验

v

CP

实验目的

t

v t v t v

Q0

实验原理

实验内容

Q1

注意事项

Q2

参考波形

t v

Q3

t

现代电子技术实验

5、注意测试的顺序

不要将每一个输出与CP比较,否则不能读 出各输出相互之间的时间关系!

实验目的

现代电子技术实验

移位寄存器及其应用研究

实验目的

实验原理

实验内容

注意事项

现代电子技术实验

一、实验目的

实验目的

1、掌握4位双向移位寄存器的逻辑功 能及使用方法。 2、熟悉移位寄存器的应用—构成环形 计数器。

实验原理

实验内容

注意事项

现代电子技术实验

二、实验原理

实验目的

1、74LS194 逻辑功能

移位寄存器是指所存的代码能在移位脉冲 的作用下依次位移的寄存器,它是一种可以用 二进制形式保存数据的双稳器件。即能左移又 能右移的寄存器称为双向移位寄存器。

并行输入端

左 移 串 行 输 入

现代电子技术实验

实验目的 实验原理 实验内容 注意事项

74LS194

74LS194功能表

功能 清 零 控制 信号 串行输入 时 并行输入 钟 DSR DSL CP D0 D1 D2 D3 输 出

n Q Q Q Q3

n 0

Cr S1 S0

清零

送数 右移 左移 保持

n 1

现代电子技术实验

3、切忌将两个输出端连到一起

实验目的

实验原理

逻辑电 平开关

实验内容

注意事项

此处DSR既与开关相 连又与Q3相连

74X194

现代电子技术实验

4、用双踪示波器观测波形时应选择恰当的触发源。

y1

level

y2

若选用y1 做触发源

示波器上 显示的y2 波形

现代电子技术实验

用双踪示波器观测波形时应选择恰当的触发源。

有效 状态

0100

0000

0001

0010

0 1 74X194

该电路不能自启动

现代电子技术实验

首先应给输出端赋初值,此时S1 S0为11。

再将S1 S0改为01,使之工作在右移状态。

实验目的

CP 1

1

Q0 1 0

Q1 0 1

Q2 0 0

Q3 0 0

实验原理

0 0

2

实验内容

3

4

0 1

0

0 1

0

0 0

实验原理

实验内容

注意事项

现代电子技术实验

实验目的

实验原理

74LS194

实验内容

注意事项

逻辑符号

引脚图

移位寄存器存取信息的方式有:串入串出、串入并 出、并入串出、并入并出四种形式。

现代电子技术实验

输出端

时 钟

控制信号

实验目的

实验原理

74LS194 74LS194

实验内容

注意事项

清 零 端

右 移 串 行 输 入

v

CP

实验原理

t

v

Q0

实验内容

t

注意事项

v

CP

t v t

Q1

现代电子技术实验

5、数字示波器读数前应调整好各通道比例。

五、思考题 教材1、2

实验原理

实验内容

注意事项

74X194

现代电子技术实验

若希望该环形计数器为单个“1”在其中循环 时,其工作状态为: CP Q 0 Q1 Q 2 Q3 1 2 3 1 0 0 1 0 0 0 0

0

0 1

1000

0

0 0

1

0 0

0100

0

1 0

4

5

0

1 74X194

0001

0010

现代电子技术实验

1000