loadboard及测试板PCB设计参考

PCB设计指导书

PCB 设计指导书1.术语:1PCB(Print circuit Board) 印制电路板2原理图电路原理图,使用原理图设计工具设计的表达硬件电路中器件关系的图。

3SMT:外表组装技术〔外表贴装技术〕〔Surface Mount Technology 的缩写〕,是目前电子组装行业里最流行的一种技术和工艺。

4AI:AI 是(Auto-Insert)的简写,意思是自动插件技术,自动将元器件安装在PCB 上面。

5EMC: 电磁兼容性EMC(Electro Magnetic Compatibility),是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的力量。

6波峰焊接:波峰焊是让插件板的焊接面直接与高温液态锡接触到达焊接目的,其高温液态锡保持一个斜面,并由特别装置使液态锡形成一道道类似波浪的现象,所以叫“波峰焊“,其主要材料是焊锡条。

又称 FS。

7回流焊接:回流焊机也叫再流焊机或“回流炉”(Reflow Oven),它是通过供给一种加热环境,使焊锡膏受热溶化从而让外表贴装元器件和 PCB 焊盘通过焊锡膏合金牢靠地结合在一起。

简称 RF。

8通孔回流焊接:通孔回流焊接技术(THR,Through-hole Reflow),又称为穿孔回流焊 PIHR(Pin-in-Hole Reflow)。

该技术原理是在印制板完成贴片后,使用一种安装有很多针管的特别模板,调整模板位置使针管与插装元件的过孔焊盘对齐,使用刮刀将模板上的锡膏漏印到焊盘上,然后安装插装元件,最终插装元件与贴片元件同时通过回流焊完成焊接。

9微带线:微带线是由支在介质基片上的单一导体带构成的微波传输线。

适合制作微波集成电路的平面构造传输线。

与金属波导相比,其体积小、重量轻、使用频带宽、牢靠性高和制造本钱低等;但损耗稍大,功率容量小。

10带状线:带状线是介于两个接地层之间的印制导线,它是一条置于两层导电平面之间的电介质中间的铜带线。

PCB多层板设计建议及实例

PCB多层板设计建议及实例

一、PCB多层板设计建议

(1)PCB多层板应采用等厚层材料,芯材厚度一般采用1.6mm、

2.0mm、2.5mm;

(2)信号层厚度应采用35μm,集电层应采用18μm;

(3)在选用电路板材料时应确定电路板的阻抗要求;

(4)端面阻抗Rz≥50Ω是最常见的,其他阻抗可根据电路板的要求

单独设计;

(5)采用线宽线距技术设计,其最小线宽≥4mil,最小间距≥3mil;

(6)在设计PCB多层板时,应给出各层信号的布局方案;

(7)在设计PCB多层板时,应考虑各层之间连接的接头位置,尤其

是多层板调节时的内芯孔位;

(8)保护线设计时,应考虑电磁兼容(EMC),采用粗线宽;

(9)PCB多层板设计应采用相同的图档号,左右层应分别采用左右

图示;

(10)PCB多层板设计应采用数字线绝缘,数字线绝缘主要有8mil,10mil,12mil等;

(11)在设计PCB多层板时,应考虑热点位置,保证各层之间的衔接

点不能过热,以免引起信号和电路的失效;

(12)PCB多层板设计应限制尽量减少内芯孔,减少衔接负载;

(13)在设计多层板时,应采用节点单元来确定信号路径,以及信号的传输速率;。

线路板onpad设计

线路板onpad设计

线路板(PCB板)是电子设备中重要的组成部分之一,在电路设计中起到了非常重要的作用。

以下是线路板(PCB板)的onpad设计步骤:

1. 选择尺寸和工艺标准:首先,在进行线路板设计时,需要根据电子设备的具体要求来确定线路板的尺寸和工艺标准。

线路板的尺寸和工艺标准会对电路性能、成本和可靠性等方面产生较大的影响。

2. 布置器件和连线:线路板设计重要的一步是将器件布置在板上,并连接相应的引脚和连线。

在这个过程中,需要特别注意器件之间的距离和方向,以保证电路的稳定性和可靠性。

3. 适配机械尺寸:在进行线路板设计时,还需要考虑机械尺寸因素。

要根据电子设备的机械尺寸要求对线路板的尺寸和连接方式进行适配,确保线路板与其他组件的相互匹配性。

4. 检查和验证:完成线路板的设计后,需要进行检查和验证。

检查确认电路中没有错误或冲突,验证确认线路板的性能够得到执行。

5. 打样和生产:珂能在完成验证之后打样并进行生产,开始批量生成线路板供电子设备使用。

以上是简要的线路板(PCB板)onpad设计步骤,需要特别注意的是,在进行设计时一定要遵循相关的设计规范和标准。

PCB常用阻抗设计方案及叠层

PCB常用阻抗设计方案及叠层PCB(Printed Circuit Board,印刷电路板)是电子设备中最常见的一种电路板,用于连接和支持电子组件。

在PCB设计中,阻抗是一个重要的考虑因素,特别是在高频电路和信号传输中。

以下是PCB常用阻抗设计方案及叠层的介绍:1.阻抗定义和常见值:阻抗是指电路中电流和电压之间的比率,表示电路对交流信号的阻碍程度。

在PCB设计中,常见的阻抗值包括50Ω,75Ω和100Ω等,其中50Ω应用最为广泛。

2.单层PCB阻抗设计:在单层PCB设计中,通过控制信号线的宽度和距离来实现特定的阻抗值。

一般来说,信号线的宽度越宽,阻抗越低。

在设计过程中,可以使用阻抗计算工具或阻抗计算公式来确定合适的信号线宽度。

3.双层PCB阻抗设计:在双层PCB设计中,可以使用不同的叠层结构来实现特定的阻抗值。

常见的叠层结构包括两层相邻的信号层,两层信号层之间夹一层地层,以及两层信号层之间夹一层电源层等。

4.多层PCB阻抗设计:多层PCB通常包含四层或六层,在更高层数的PCB中,可以使用更复杂的阻抗设计方案。

常见的多层PCB阻抗设计方案包括均匀分布阻抗线和差分阻抗线。

5.均匀分布阻抗线:均匀分布阻抗线是指在PCB内部平面层上均匀分布的阻抗线。

通过控制平面层与信号层之间的距离和信号层上的信号线宽度,可以实现特定的阻抗值。

这种设计方案适用于高频电路和差分信号传输。

6.差分阻抗线:差分阻抗线是指将信号和其反相信号同时传输在两条平行的信号线上。

差分信号传输具有很好的抗干扰能力和信号完整性。

在PCB设计中,通过控制差分信号线和地线之间的距离和信号线宽度,可以实现特定的阻抗值。

总之,PCB阻抗设计是非常重要的一部分,在高频电路和信号传输中尤其关键。

通过合理选择信号线宽度、距离以及叠层结构等设计参数,可以实现所需的阻抗值。

在PCB设计过程中,可以借助专业的设计软件和计算工具,以及参考相关的设计规范和指南来进行阻抗设计。

PCB版图设计(Ultiboard)

PCB版图设计任何电子设计的最终物理实现都必须有PCB板,它既是各类电路元器件的承载体,又起到保障电气连接的作用,现代电子设计人员学习PCB板制意义十分重大。

Ultiboard 9的功能与应用第一节Ultiboard 9概论一、Ultiboard 9的特点电路设计的主要物理实现形式之一就是印制电路板(PCB:Printed Circuit Board),它既是各类电路元器件的承载体,又起到保障电气连接的作用。

对于研发电子设备或电子电路系统的设计者而言,无论使用集成度多么高的IC器件,总是不能回避PCB 设计环节。

对比较复杂的电路系统进行PCB设计时,如果采用纯粹的手工布线,需要投入比其电气原理图设计更多的精力和时间,而且难以做到设计无误,不但浪费了时间,还会增加研制开发费用。

显然,设计者只有具备和掌握出色的PCB设计工具,才能适应日益激烈的电子技术市场竞争的需要。

EDA开发软件Electronics Workbench是加拿大公司Interactive Image Technologies Ltd.于1988推出的一个很有特色的EDA工具,自发布以来,已经有35个国家、10种语言的人在使用这种工具。

它(Electronics Workbench)与其他同类工具相比,不但设计功能比较完善,而且操作界面十分友好、形象,易于使用掌握。

电子设计工具平台Electronics Workbench主要包括Multisim和Ultiboard两个基本工具模块。

Ultiboard是Electronics Workbench中用于PCB设计的后端工具模块,它可以直接接收来自Multisim模块输出的前端设计信息,并按照确定的设计规则进行PCB 的自动化设计。

为了达到良好的PCB自动布线效果,通常还在系统中附带一个称为Ultiroute的自动布线模块,并采用基于网格的“拆线—重试”布线算法进行自动布线。

Ultiboard的设计结果可以生成光绘机需要的Gerber格式板图设计文件。

pcb线路板设计方案

pcb线路板设计方案PCB(Printed Circuit Board)线路板设计方案是指在电子设备中使用的PCB的设计和布局方案。

PCB线路板是连接和支持电子器件的基础,它承载了电子器件之间的互连、电路信号的传输和电源的供应。

下面将详细介绍PCB线路板设计方案的几个关键要素:1. PCB尺寸及形状:PCB的尺寸和形状应根据实际应用需求进行定义。

尺寸的选择应兼顾电路元件的布局和设备容量的限制,形状的设计应适合于设备外壳的安装。

2. 线路板层数:根据电路复杂度和空间限制,选择单面、双面或多层PCB。

单面PCB适用于简单电路,双面PCB可提供更多的互连路线,而多层PCB可以进一步增加互连路线密度和减小信号干扰。

3. 元件布局:在PCB上安排电子元件的位置和布局是设计的重要一步。

元件布局考虑到信号传输的最短路径、电源线的布置、热量分散和连接距离等因素。

4. 电路连线:根据电路原理图进行连线设计,将电子元件互相连接并满足电路的功能要求。

在连线过程中应尽量避免交叉连线和冲突,同时考虑到信号传输的最短路径和电流规划。

5. 电源规划:合理规划电源,包括电源芯片的布局、滤波电容和稳压电路等。

电源线应尽量短,以减少电压降和电磁干扰。

6. 地线设计:良好的地线设计是减少电磁干扰和保障信号完整性的关键。

地线应尽量宽,且与信号线尽量分离。

扩展分析:PCB线路板设计方案的实施需要依赖专业的设计软件,如Altium Designer、Cadence Allegro等。

设计过程中还需考虑EMC (Electromagnetic Compatibility)和SI(Signal Integrity)等问题。

EMC设计涉及抑制电磁辐射和提高抗干扰能力,SI设计包括减小信号失真和时钟信号的传输等。

在PCB线路板设计方案中还需要考虑到PCB的制造工艺。

通过合理的层叠方式、板厚控制、焊盘设计等措施,尽量减少制造过程中的问题。

PCB设计完成后,需要进行电气检查、原型制作和样品测试等验证工作。

pcb板的实验报告

pcb板的实验报告标题:PCB板的实验报告摘要:本实验报告旨在通过对PCB板的实验研究,探讨其在电子工程中的应用和性能评估。

实验过程中,我们使用了不同的材料和工艺制作出多种PCB板样品,并对其导电性、耐热性、机械强度等性能进行了测试。

结果表明,PCB板在电子设备制造中具有广泛的应用前景。

引言:PCB板(Printed Circuit Board),又称印制电路板,是电子设备中不可或缺的基础组件之一。

它通过将导线、电子元件和其他电子元器件固定在一块绝缘基板上,实现了电路的连接和支持。

PCB板的设计和制造对于电子工程的成功实施至关重要,因此对其性能的评估和研究具有重要意义。

实验方法:1. 材料准备:准备FR-4玻璃纤维增强环氧树脂基板、铜箔、化学溶剂等材料。

2. 设计和制作:使用CAD软件设计电路图,然后通过光刻和腐蚀等工艺制作出PCB板样品。

3. 性能测试:对PCB板样品进行导电性测试、耐热性测试、机械强度测试等。

实验结果与讨论:1. 导电性测试:将导线连接到PCB板上的不同位置,通过电阻测试仪测量导通情况。

结果显示,PCB板具有良好的导电性能,能够实现电路的正常连接。

2. 耐热性测试:将PCB板样品置于高温环境中,观察其是否出现热胀冷缩等问题。

实验结果表明,PCB板具有较好的耐热性能,能够在一定温度范围内正常工作。

3. 机械强度测试:通过压力测试仪对PCB板样品进行压力加载,观察其是否发生破裂或变形。

结果显示,PCB板具有较高的机械强度,能够承受一定的外力。

结论:通过对PCB板的实验研究,我们发现其在电子工程中具有重要的应用价值。

PCB板具有良好的导电性、耐热性和机械强度,能够满足电子设备制造的需求。

然而,我们也发现PCB板在制作过程中可能存在一些问题,如光刻误差、腐蚀不均匀等,需要进一步改进和优化。

展望:随着电子技术的不断发展,PCB板的应用也将越来越广泛。

未来的研究可以着重于改进PCB板的制作工艺,提高其性能和可靠性。

某公司PCB设计规范样本

某公司PCB设计规范样本1. 引言PCB(Printed Circuit Board,印刷电路板)是现代电子设备中常见的一种重要组成部分,它承载着电子元器件,并提供了电子元器件之间的电气连接。

为了保证PCB的质量和可靠性,某公司制定了一套严格的PCB设计规范样本,本文将介绍该规范样本的具体内容和要求。

2. PCB设计规范2.1 PCB尺寸和层数根据不同的应用需求,PCB的尺寸和层数会有所不同。

在某公司的设计规范样本中,PCB的尺寸通常不超过20cm×20cm,并且层数不超过4层。

若需要超出这个范围,需要额外申请和审批。

2.2 PCB布局和布线2.2.1 元器件布局•元器件应按照电路图要求合理布局,尽量缩短信号传输路径,降低信号干扰。

•元器件之间应保留足够的间距,以便于安装和维修。

•高功率元器件和高频元器件应与敏感元器件保持一定的间距,防止互相干扰。

2.2.2 信号和电源平面•PCB上应划分信号和电源平面,以降低信号串扰和提供稳定的电源供应。

•信号和电源平面之间应保持一定的距离,以减少互相干扰。

2.2.3 信号走线•信号走线应尽量保持短、直、对称。

•临近平面的信号线应与平面保持一定距离,以减少互电容和互感。

•若有高速信号或高频信号,应采取差分走线或者层间引线走线方式,以减少信号衰减和串扰。

2.3 焊盘和焊接2.3.1 焊盘设计•焊盘的大小应根据元器件引脚的尺寸和数量合理确定,避免太小或太大。

•焊盘的形状应选择圆形或方形,避免使用带尖角的形状。

2.3.2 焊盘与元器件引脚的间距•焊盘与元器件引脚之间应保留一定的间距,避免短路或接触不良。

2.3.3 焊接工艺•焊接工艺应符合IPC标准,并采用无铅焊接方式。

•焊接时应遵循良好的工艺控制,如控制温度、焊接时间和焊接扩展量等。

2.4 丝印和字体2.4.1 PCB丝印•PCB上的丝印应清晰、易读,方便组装和维修。

•丝印的颜色应与PCB背景颜色形成明显对比,以提高可视性。

PCB设计规范范文

PCB设计规范范文pcb设计规范PCB(Printed Circuit Board)设计规范是指在进行电路板设计时,应遵循的相关规范和要求。

遵循这些规范可以确保设计的精度和可靠性,并提高生产的效率和质量。

以下是一些常见的PCB设计规范。

1.尺寸和布局规范:2.电路分布规范:在布局电路时,需要将功能相似的电路元件归为一组,并保持它们之间的距离尽可能短,以便减少信号传输时的干扰。

同时,需要将高频电路和低频电路分开,以避免相互干扰。

3.电源规范:在PCB设计中,电源线路应注意保持稳定的供电。

此外,对于高频电路和模拟电路,需要提供相应的电源滤波器和去耦电容,以降低噪声和交叉干扰。

4.信号走线规范:为了保证信号传输的稳定性和可靠性,需要遵循一些信号走线的规范。

信号线应尽量避免走并行,并尽量保持直线走向。

对于高频信号,应采用差分走线方式,并与地线或屏蔽层相邻,以减少干扰。

5.地线规范:地线在PCB设计中起到连接、屏蔽和引流的作用。

因此,需要确保地线宽度足够,且与信号线保持相邻,并尽量缩短长度。

在布局时,需要将地线划分为数个区域,以避免大面积的地线循环引起的回流问题。

6.散热规范:对于功耗较大的电路或存在散热问题的电路元件,需要考虑散热的设计。

可以通过增加散热片、散热器或增大散热面积来提高散热效果。

7.符号和标注规范:8.禁忌规范:在PCB设计过程中,需要遵循一些禁忌规范,以避免常见的错误。

例如,避免信号线和电源线重叠,避免不必要的直角走线,避免不合理的走线方式等。

总结:。

PCB电路板制图课程设计模板

PCB电路板制图课程设计模板目录1p r o t e l简介 (2)2电路原理图绘制 (4)2.1电路原理图 (4)2.2原理图的绘制过程 (5)2.3遇到的问题 (5)2.4小结 (5)3印刷版电路的设计 (6)3.1印刷电路板的设计过程 (6)3.2遇到的问题 (6)3.3小结 (6)3.4元件清单 (7)3.5网络表 (8)4.总结 (10)5.附录 (11)5.1P C B全图 (11)5.2PCBtopoverlayer (12)5.3P C B t o p l a y e r (13)5.4PC Bb ottomlaye r (14)5.6PCB铺地图 (15)5.7PCB未铺地图 (15)Protel简介Altium(前身为Protel国际有限公司)由NickMartin于1985年始创于澳大利亚,致力于开发基于PC的软件,为印刷电路板,提供辅助的设计。

PCB (printedcircuitboard印刷电路板)。

Altium公司成功进行公开募股(IPO),于1999年8月在澳大利亚股票市场上市。

所筹集的资金用于在2000年1月收购适当的公司和技术,包括收购ACCELTechnologies公司、Metamor公司、InnovativeCADSoftware公司和TASKINGBV公司等。

产品简介:Protel是目前EDA行业中使用最方便,操作最快捷,人性化界面最好的辅助工具。

在中国用得最多的EDA工具,电子专业的大学生在大学基本上都学过protel99se,所以学习资源也最广,公司在招聘新人的时候用Protel新人会很快上手。

在电子行业的CAD软件中,它当之无愧地排在众多EDA软件的前面,是电子设计者的首选软件,它较早就在国内开始使用,在国内的普及率也最高,有些高校的电子专业还专门开设了课程来学习它,几乎所有的电子公司都要用到它,许多大公司在招聘电子设计人才时在其条件栏上常会写着要求会使用PROTEL。

PCB设计参考

PCB设计参考一、铜箔厚度、直线宽度与电流的关系在PCB的加工中,常用OZ(盎司)作为铜皮厚度的单位。

一平方英尺面积内铜箔的重量为1OZ,对应的物理厚度为35um。

PCB板的铜厚一般分为1OZ(35um)、2OZ(70um)、3OZ(105um),如有特殊要求,则可选择更厚的PCB板。

一般双面板所用的铜厚为1OZ(35um),像开关电源走大电流要选用2OZ(70um)的铜厚的PCB板。

多层PCB板一般内层选用1/2OZ、1/3OZ,外层选用1OZ、1/2OZ、1/3OZ。

如果对PCB板有厚度要求,最好和厂家进行详细沟通,以达到理想的设计效果,但是PCB铜厚有一定的上限值,要特别注意。

PCB铜厚确定后,信号的电流强度与布线宽度有一定的关系。

铜厚、线宽与电流的关系如下表1:注:表1只是作为PCB设计中的参考值,实际设计中线宽的载流量最好降额考虑(常降额50%考虑)。

以典型0.03mm厚度为例:如果将铜箔作为宽度为W(mm),长度为L(mm)的条状导线,其电阻为0.0005*L/W欧姆。

另外铜箔的载流量还与印刷电路板上安装的元件种类、数量以及散热条件有关。

在考虑到安全的情况下,一般可按经验公式0.15*W(A)来计算铜箔的载流量。

(表1)二、布局规则在PCB设计中,布局是一个重要的环节。

布局的好坏直接影响到布线的效果。

1.PCB板布局前要先了解元件的封装形式。

2.要有合理的走向:如输入\输出,交流\直流,强\弱信号,高频\低频,高压\低压等。

它们的走向应该是分离的,不得相互交融。

其目的是避免相互干扰。

最好是按直线走,最不利的走向是环形。

元件放置能不挤尽量不要挤在一起。

3.选择好接地点:4.合理考虑滤波元件以及退耦电容:对于滤波元件以及退耦电容,要尽量靠近相应元件。

电源和地信号要先过滤波元件以及退耦电容,再进相应的元件,以达到很好的滤波和退耦效果。

三、布线规则在PCB设计中,布线是完成产品设计的重要步骤。

PCB设计基础及实训教案

⑵双面印制板 双面印制板指两面都有导电图形的印制板,板的厚度约为0.2~5.0mm,它是在两面敷有铜箔的绝缘基板上,通过印制和腐蚀的方法在基板上形成印制电路,两面的电气互连通过金属化孔实现。 它适用于要求较高的电子设备,如计算机、电子仪表等,由于双面印制板的布线密度较高,所以能减小设备的体积。

第7页/共31页

三、PCB设计中的基本组件

1.板层(Layer) 板层分为敷铜层和非敷铜层,平常所说的几层板是指敷铜层的层面数。一般在敷铜层上放置焊盘、线条等完成电气连接;在非敷铜层上放置元件描述字符或注释字符等;还有一些层面(如禁止布线层)用来放置一些特殊的图形来完成一些特殊的作用或指导生产。 敷铜层一般包括顶层(又称元件面)、底层(又称焊接面)、中间层、电源层、地线层等;非敷铜层包括印记层(又称丝网层、丝印层)、板面层、禁止布线层、阻焊层、助焊层、钻孔层等。

第13页/共31页

元件封装的命名一般与管脚间距和管脚数有关,如电阻的封装AXIAL-0.3中的0.3表示管脚间距为0.3英寸或300mil(1英寸=1000mil=2.54cm);双列直插式IC的封装DIP-8中的8表示集成块的管脚数为8。元件封装中数值的意义如图4-17所示。

第14页/共31页

一、印制电路板概述

第1页/共31页

⑴单面印制板 单面印制板指仅一面有导电图形的印制板,板的厚度约在0.2~5.0mm,它是在一面敷有铜箔的绝缘基板上,通过印制和腐蚀的方法在基板上形成印制电路。它适用于一般要求的电子设备,如收音机、电视机。

1.根据PCB导电板层划分

二、印制电路板的种类

第17页/共31页

四、Protel 2004 PCB编辑器使用

1.启动PCB编辑器 进入Protel 2004主窗口,执行菜单“文件”→ “创建”→“项目”→“PCB项目”建立PCB工程项目文件,执行菜单“文件”→ “创建” →“PCB文件”,系统自动产生默认文件名为PCB1.PcbDoc的PCB文件,并进入PCB编辑器状态。 PCB编辑器的主菜单与原理图编辑器的主菜单基本相似,操作方法也类似。 PCB编辑器的工具栏主要有PCB标准工具栏、配线工具栏和实用工具栏等。 执行菜单“查看”→ “工具栏”下的相关菜单,可以设置打开或关闭相应的工具栏。

常用PCB层叠参考NEW

常用PCB层叠

说明:以下为常用的2-8层板公司最常用的层叠, 在之前成熟层叠的根底上汇总,这些层叠都是我们公司经过批量验证OK的,请在设计时调用.因为这是是个通用模板,适合所有情况,整理在一起的时侯,可能有些微调.各种叠法很多,未包含的后续再补充.未包含的情况大家类似目前处理方法,找到之前曾设计单板参考,根本都有.

备注:

1)改版还按之前的方式,新版设计,包括套用之前的模块布线,如果有更改,请修改下,方便后续重用.

2)设计中如果没有用到模板中的阻抗线,请在模板中删除

3)其他信号不得与有阻抗控制的信号线宽一致.有一致,其他信号线宽要稍作修改

4)根据实际情况选择对应的层叠,特别是如果没有及其以下间距的BGA器件的,选用对应的.请务必对应好,方便后续套用.

一.2层板

层叠:

阻抗控制表,一般不控制阻抗,无须填写

备注:不同板厚的2层板根据板厚修改1,2层之间的介质厚度即可,其他不变

二.4层板

:

阻抗要求:

:

1.单板上有及其以下PIN间距的BGA器件,有1或者2个布线内层. 如果一个内层布线,默认第3层为布线层,第4层为POWER.其他不变1)板厚

典型应用:含365,368,A5,8107等IC的PCB

2)板厚

典型应用:含365,368,A5,8107等IC的PCB

3. 单板上无及其以下PIN间距的BGA器件, 有1或者2个布线内层1)板厚

2)板厚

四.8层板

标准层叠,2个布线内层.

1.单板上有及其以下PIN间距的BGA器件,且2个内层1)板厚

1)板厚

2)板厚

及其以下PIN间距的BGA器件, 标准层叠,2个布线内层

1)板厚

2)板厚。

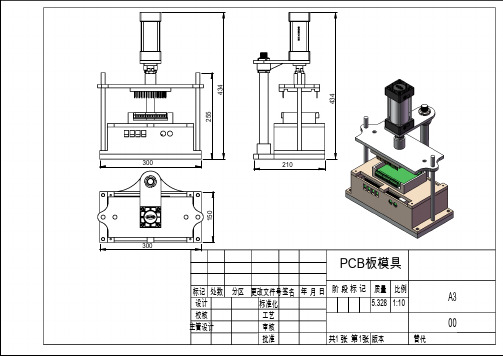

PCB测试板模具全套图纸

替代

15 255

M10

A

A

12

数量1件

B

6061 铝合金 Φ12导柱

标记 处数 分区 更改文件号 签名 年 月 日 阶 段 标 记 质量 比例

设计

标准化

0.076 1:5

A4

校核

工艺

主管设计

审核

06

批准

共1张 第1张 版本

替代

62 47 7.5 18 8 28 8 28

40

10 62

4- 8

7.5

20

10 19 19.5 10 80

22.5

22.5

150

300

4- 10

255

15

5

15

4-M4

R5

12

235

5

5

10 300

130

10

10

12 5

10

150

数量1件

绝缘材料

控制器底箱

标记 处数 分区 更改文件号签名 年 月 日 阶 段 标 记 质量 比例

设计

标准化

0.739 1:5

A4

校核

工艺

主管设计

96C

6

48

53 4- 3

116

35

R5 3- 6

10 6

25 25

96

80 53

15

15

132

数量1件

绝缘材料

COM16控制器模具板

标记 处数 分区 更改文件号签名 年 月 日 阶 段 标 记 质量 比例

设计

标准化

0.154 1:2

A4

校核

工艺

主管设计

审核

PCB设计基本概述

PCB设计基础知识印刷电路板(Printed circuitboard,PCB)几乎会出现在每一种电子设备当中。

如果在某样设备中有电子零件,那么它们也都是镶在大小各异的PCB上。

除了固定各种小零件外,PCB的主要功能是提供上头各项零件的相互电气连接。

随着电子设备越来越复杂,需要的零件越来越多,PCB上头的线路与零件也越来越密集了。

规范的PCB长得就像这样。

裸板(上头没有零件)也常被称为「印刷线路板Printed WiringBoard(PWB)」。

板子本身的基板是由绝缘隔热、并不易弯曲的材质所制作成。

在表面可以看到的细小线路材料是铜箔,原本铜箔是覆盖在整个板子上的,而在制造过程中部份被蚀刻处理掉,留下来的部份就变成网状的细小线路了。

这些线路被称作导线(conductorpattern)或称布线,并用来提供PCB上零件的电路连接。

为了将零件固定在PCB上面,我们将它们的接脚直接焊在布线上。

在最基本的PCB(单面板)上,零件都集中在其中一面,导线则都集中在另一面。

这么一来我们就需要在板子上打洞,这样接脚才能穿过板子到另一面,所以零件的接脚是焊在另一面上的。

因为如此,PCB的正反面分别被称为零件面(ComponentSide)与焊接面(Solder Side)。

如果PCB上头有某些零件,需要在制作完成后也可以拿掉或装回去,那么该零件安装时会用到插座(Socket)。

由于插座是直接焊在板子上的,零件可以任意的拆装。

下面看到的是ZIF(ZeroInsertionForce,零拨插力式)插座,它可以让零件(这里指的是CPU)可以轻松插进插座,也可以拆下来。

插座旁的固定杆,可以在您插进零件后将其固定。

如果要将两块PCB相互连结,一般我们都会用到俗称「金手指」的边接头(edgeconnector)。

金手指上包含了许多裸露的铜垫,这些铜垫事实上也是PCB布线的一部份。

通常连接时,我们将其中一片PCB上的金手指插进另一片PCB上合适的插槽上(一般叫做扩充槽Slot)。

loadboard及测试板PCB设计参考

问:在当今无线通信设备中,射频部分往往采用小型化的室外单元结构,而室外单元的射频部分、中频部分,以及对室外单元进行监控的低频电路部分往往部署在同一PCB上。请问,对这样的PCB布线在材质上有何要求?如何防止射频、中频以及低频电路互相之间的干扰?

答:混合电路设计是一个很大的问题,很难有一个完美的解决方案。一般射频电路在系统中都作为一个独立的单板进行布局布线,甚至会有专门的屏蔽腔体。而且射频电路一般为单面或双面板,电路较为简单,所有这些都是为了减少对射频电路分布参数的影响,提高射频系统的一致性。相对于一般的FR4材质,射频电路板倾向与采用高Q值的基材,这种材料的介电常数比较小,传输线分布电容较小,阻抗高,信号传输时延小。

在处理布线密度时应注意哪些问题?

问:在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请问在高速(>100MHz)高密度PCB设计中有哪些技巧?

答:在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方: 1.控制走线特性阻抗的连续与匹配。 2.走线间距的大小。一般常看到的间距为两倍线宽。可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。不同芯片信号的结果可能不同。 3.选择适当的端接方式。 4.避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。 5.利用盲埋孔(blind/buried via)来增加走线面积。但是PCB板的制作成本会增加。在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。除此以外,可以预留差分端接和共模端接,以速PCB设计中的EMC、EMI问题

pcb叠层参考

pcb叠层参考名词定义:SIG:信号层;GND:地层;PWR:电源层;电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:2.1 单面板和双面板的叠层;对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.2 四层板的叠层;推荐叠层方式:2.2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

loadboard及测试板pcb设计参考

loadboard及测试板PCB设计参考问:在当今无线通信设备中,射频部分往往采用小型化的室外单元结构,而室外单元的射频部分、中频部分,以及对室外单元进行监控的低频电路部分往往部署在同一PCB上。

请问,对这样的PCB布线在材质上有何要求?如何防止射频、中频以及低频电路互相之间的干扰?答:混合电路设计是一个很大的问题,很难有一个完美的解决方案。

一般射频电路在系统中都作为一个独立的单板进行布局布线,甚至会有专门的屏蔽腔体。

而且射频电路一般为单面或双面板,电路较为简单,所有这些都是为了减少对射频电路分布参数的影响,提高射频系统的一致性。

相对于一般的FR4材质,射频电路板倾向与采用高Q值的基材,这种材料的介电常数比较小,传输线分布电容较小,阻抗高,信号传输时延小。

在混合电路设计中,虽然射频,数字电路做在同一块PCB上,但一般都分成射频电路区和数字电路区,分别布局布线。

之间用接地过孔带和屏蔽盒屏蔽。

关于输入、输出端接的方式与规则问:现代高速PCB设计中,为了保证信号的完整性,常常需要对器件的输入或输出端进行端接。

请问端接的方式有哪些?采用端接的方式是由什么因素决定的?有什么规则?答:端接(terminal),也称匹配。

一般按照匹配位置分有源端匹配和终端匹配。

其中源端匹配一般为电阻串联匹配,终端匹配一般为并联匹配,方式比较多,有电阻上拉,电阻下拉,戴维南匹配,AC匹配,肖特基二极管匹配。

匹配采用方式一般由BUFFER特性,拓普情况,电平种类和判决方式来决定,也要考虑信号占空比,系统功耗等。

数字电路最关键的是时序问题,加匹配的目的是改善信号质量,在判决时刻得到可以确定的信号。

对于电平有效信号,在保证建立、保持时间的前提下,信号质量稳定;对延有效信号,在保证信号延单调性前提下,信号变化延速度满足要求。

在处理布线密度时应注意哪些问题?问:在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请问在高速(>100MHz)高密度PCB设计中有哪些技巧?答:在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

loadboard及测试板PCB设计参考

问:在当今无线通信设备中,射频部分往往采用小型化的室外单元结构,而室外单元的射频部分、中频部分,以及对室外单元进行监控的低频电路部分往往部署在同一PCB上。

请问,对这样的PCB布线在材质上有何要求?如何防止射频、中频以及低频电路互相之间的干扰?

答:混合电路设计是一个很大的问题,很难有一个完美的解决方案。

一般射频电路在系统中都作为一个独立的单板进行布局布线,甚至会有专门的屏蔽腔体。

而且射频电路一般为单面或双面板,电路较为简单,所有这些都是为了减少对射频电路分布参数的影响,提高射频系统的一致性。

相对于一般的FR4材质,射频电路板倾向与采用高Q值的基材,这种材料的介电常数比较小,传输线分布电容较小,阻抗高,信号传输时延小。

在混合电路设计中,虽然射频,数字电路做在同一块PCB上,但一般都分成射频电路区和数字电路区,分别布局布线。

之间用接地过孔带和屏蔽盒屏蔽。

关于输入、输出端接的方式与规则

问:现代高速PCB设计中,为了保证信号的完整性,常常需要对器件的输入或输出端进行端接。

请问端接的方式有哪些?采用端接的方式是由什么因素决定的?有什么规则?

答:端接(terminal),也称匹配。

一般按照匹配位置分有源端匹配和终端匹配。

其中源端匹配一般为电阻串联匹配,终端匹配一般为并联匹配,方式比较多,有电阻上拉,电阻下拉,戴维南匹配,AC匹配,肖特基二极管匹配。

匹配采用方式一般由BUFFER特性,拓普情况,电平种类和判决方式来决定,也要考虑信号占空比,系统功耗等。

数字电路最关键的是时序问题,加匹配的目的是改善信号质量,在判决时刻得到可以确定的信号。

对于电平有效信号,在保证建立、保持时间的前提下,信号质量稳定;对延有效信号,在保证信号延单调性前提下,信号变化延速度满足要求。

在处理布线密度时应注意哪些问题?

问:在电路板尺寸固定的情况下,如果设计中需要容纳更多的功能,就往往需要提高PCB的走线密度,但是这样有可能导致走线的相互干扰增强,同时走线过细也使阻抗无法降低,请问在高速(>100MHz)高密度PCB设计中有哪些技巧?

答:在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。

以下提供几个注意的地方:1.控制走线特性阻抗的连续与匹配。

2.走线间距的大小。

一般常看到的间距为两倍线宽。

可以透过仿真来知道走线间距对时序及信号完整性的影响,找出可容忍的最小间距。

不同芯片信号的

结果可能不同。

3.选择适当的端接方式。

4.避免上下相邻两层的走线方向相同,甚至有走线正好上下重迭在一起,因为这种串扰比同层相邻走线的情形还大。

5.利用盲埋孔(blind/buried via)来增加走线面积。

但是PCB板的制作成本会增加。

在实际执行时确实很难达到完全平行与等长,不过还是要尽量做到。

除此以外,可以预留差分端接和共模端接,以缓和对时序与信号完整性的影响。

关于PCB设计中的阻抗匹配问题

-

问:在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?另外关于IBIS模型,不知在那里能提供比较准确的IBIS模型库。

我们从网上下载的库大多数都不太准确,很影响仿真的参考性。

答:在设计高速PCB电路时,阻抗匹配是设计的要素之一。

而阻抗值跟走线方式有绝对的关系,例如是走在表面层(microstrip)或内层(stripline/double stripline),与参考层(电源层或地层)的距离,走线宽度,PCB材质等均会影响走线的特性阻抗值。

也就是说要在布线后才能确定阻抗值。

一般仿真软件会因线路模型或所使用的数学算法的限制而无法考虑到一些阻抗不连续的布线情况,这时候在原理图上只能预留一些terminators(端接),如串联电阻等,来缓和走线阻抗不连续的效应。

真正根本解决问题的方法还是布线时尽量注意避免阻抗不连续的发生。

IBIS模型的准确性直接影响到仿真的结果。

基本上IBIS可看成是实际芯片I/O buffer等效电路的电气特性资料,一般可由SPICE模型转换而得 (亦可采用测量,但限制较多),而SPICE的资料与芯片制造有绝对的关系,所以同样一个器件不同芯片厂商提供,其SPICE的资料是不同的,进而转换后的IBIS模型内之资料也会随之而异。

也就是说,如果用了A厂商的器件,只有他们有能力提供他们器件准确模型资料,因为没有其它人会比他们更清楚他们的器件是由何种工艺做出来的。

如果厂商所提供的IBIS不准确,只能不断要求该厂商改进才是根本解决之道。

关于高速PCB设计中的EMC、EMI问题

问:在高速PCB设计时我们使用的软件都只不过是对设置好的EMC、EMI规则进行检查,而设计者应该从那些方面去考虑EMC、EMI的规则?怎样设置规则?

答:一般EMI/EMC设计时需要同时考虑辐射(radiated)与传导(conducted)两个方面. 前者归属于频率较高的部分(>30MHz)后者则是较低频的部分(<30MHz). 所以不能只注意高频而忽略

低频的部分. 一个好的EMI/EMC设计必须一开始布局时就要考虑到器件的位置, PCB迭层的安排, 重要联机的走法, 器件的选择等, 如果这些没有事前有较佳的安排, 事后解决则会事倍功半,

增加成本. 例如时钟产生器的位置尽量不要靠近对外的连接器, 高速信号尽量走内层并注意特

性阻抗匹配与参考层的连续以减少反射, 器件所推的信号之斜率(slew rate)尽量小以减低高频

成分, 选择去耦合(decoupling/bypass)电容时注意其频率响应是否符合需求以降低电源层噪声. 另外, 注意高频信号电流之回流路径使其回路面积尽量小(也就是回路阻抗loop impedance尽量小)以减少辐射. 还可以用分割地层的方式以控制高频噪声的范围. 最后, 适当的选择PCB与外

壳的接地点(chassis ground)。

关于高速差分信号的布线技巧

问:在pcb上靠近平行走高速差分信号线对的时候,在阻抗匹配的情况下,由于两线的相互耦合,会带来很多好处。

但是有观点认为这样会增大信号的衰减,影响传输距离,为什么?我在一些大公司的评估板上看到高速布线有的尽量靠近且平行,而有的却有意的使两线距离忽远忽近,哪一种效果会更好?我的信号1GHz以上,阻抗为50欧姆。

在用软件计算时,差分线对也是以50欧姆来计算吗?还是以100欧姆来算?接收端差分线对之间可否加一匹配电阻?

答:会使高频信号能量衰减的原因一是导体本身的电阻特性(conductor loss), 包括集肤效应(skin effect), 另一是介电物质的dielectric loss。

这两种因子在电磁理论分析传输线效

应(transmission line effect)时, 可看出他们对信号衰减的影响程度。

差分线的耦合是会影

响各自的特性阻抗, 变的较小, 根据分压原理(voltage divider)这会使信号源送到线上的电压

小一点。

至于, 因耦合而使信号衰减的理论分析我并没有看过, 所以我无法评论。

对差分对的布线方式应该要适当的靠近且平行。

所谓适当的靠近是因为这间距会影响到差分阻抗(differential impedance)的值, 此值是设计差分对的重要参数。

需要平行也是因为要保持差

分阻抗的一致性。

若两线忽远忽近, 差分阻抗就会不一致, 就会影响信号完整性(signal integrity)及时间延迟(timing delay)。

差分阻抗的计算是 2(Z11 - Z12), 其中, Z11是走线

本身的特性阻抗, Z12是两条差分线间因为耦合而产生的阻抗, 与线距有关。

所以, 要设计差分阻抗为100欧姆时, 走线本身的特性阻抗一定要稍大于50欧姆。

至于要大多少, 可用仿真软件算出来。

接收端差分线对间的匹配电阻通常会加, 其值应等于差分阻抗的值。

这样信号品质会好些。