EDA技术_组合逻辑电路设计_Verilog

EDA技术题库

EDA技术题库一.填空题1. Verilog的基本设计单元是模块.它是由两部分组成,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的.2。

用assign描述的语句我们一般称之为组合逻辑,并且它们是属于并行语句,即于语句的书写次序无关.而用always描述的语句我们一般称之为组合逻辑或时序逻辑,并且它们是属于串行语句,即于语句的书写有关。

3.在case语句中至少要有一条default语句。

4. 已知x=4'b1001,y=4'0110,则x的4位补码为4’b1111,而y的4位的补码为4'b0110 。

5. 两个进程之间是并行语句。

而在Always中的语句则是顺序语句。

6.综合是将高层次上描述的电子系统转换为低层次上描述的电子系统,以便于系统的具体硬件实现。

综合器是能自动将高层次的表述(系统级、行为级)转化为低层次的表述(门级、结构级)的计算机程序7. 设计输入的方式有原理图、硬件描述语言、状态图以及波形图。

8.按照仿真的电路描述级别的不同,HDL仿真器可以完成:系统级仿真,行为级仿真,RTL 级仿真,门级(时序)仿真。

按照仿真是否考虑硬件延时分类,可以分为:功能仿真和时序仿真。

仿真器可分为基于元件(逻辑门)仿真器和基于HDL语言的仿真器9. IP核是知识产权核或知识产权模块,在EDA技术中具有十分重要的地位。

半导体产业的IP定义为用于ASIC或FPGA中的预先设计好的电路功能模块。

IP分为软IP、固IP和硬IP.10.可编程逻辑器件PLD是一种通过用户编程或配置实现所需逻辑功能的逻辑器件,也就是说用户可以根据自己的需求,通过EDA开发技术对其硬件结构和工作方式进行重构,重新设计其逻辑功能11.两种可编程逻辑结构是基于与—或阵列可编程结构(乘积项逻辑可编程结构)、基于SRAM 查找表的可编程逻辑结构12。

PLD按集成度分类:简单PLD、复杂PLD;按结构分类:基于“与—或”阵列结构的器件、基于查找表结构的器件;从编程工艺上分类:熔丝型、反熔丝型、EPROM型、EEPROM 型、SRAM型、Flash型13。

2024版华为Verilog入门教程

目录•Verilog概述•Verilog基础语法•组合逻辑电路设计•时序逻辑电路设计•数字系统设计方法学•华为Verilog编程规范与技巧Verilog概述1 2 3Verilog语言诞生,最初用于模拟电子系统的行为。

1980年代初期Verilog逐渐发展成为硬件描述语言(HDL),用于描述数字电路和系统的结构和行为。

1980年代中期Verilog不断完善和发展,成为电子设计自动化(EDA)领域的重要标准之一,广泛应用于集成电路设计、FPGA开发等领域。

1990年代至今Verilog历史与发展集成电路设计Verilog可用于描述数字集成电路的逻辑功能、时序关系和电路结构,是IC设计领域的重要工具。

FPGA开发Verilog可用于FPGA的逻辑设计和编程,实现复杂的数字系统和算法。

ASIC设计Verilog可用于ASIC设计的各个阶段,包括逻辑设计、综合、布局布线等。

系统级建模与仿真Verilog可用于构建系统级模型,进行系统仿真和性能分析。

Verilog应用领域01Verilog 是一种硬件描述语言(HDL ),用于描述数字电路和系统的结构和行为。

02与其他硬件描述语言(如VHDL )相比,Verilog具有更接近C 语言的语法风格,易于学习和使用。

Verilog 支持多种抽象层次的描述,包括行为级、寄存器传输级(RTL )、门级和开关级,方便设计师在不同设计阶段使用。

Verilog 与硬件描述语言关系02Verilog基础语法标识符与关键字标识符用于标识变量、模块、函数等程序实体的名称,由字母、数字和下划线组成,首字符必须是字母或下划线。

关键字Verilog语言中的保留字,用于定义语言结构和控制语句,如`module`、`input`、`output`、`if`、`else`等。

数据类型与运算符数据类型包括整型(`integer`)、实型(`real`)、时间型(`time`)以及用户自定义类型等。

EDA技术及应用—基于FPGA的电子系统设计:基于Verilog hdl的数字电路设计

10100

1111

15

10101

8421BC 余三码 D码

0000

0011

0001

0100

0010

0101

0011

0110

0100

0111

0101

1000

0110

1001

0111

1010

1000

1011

1001

1100

-

-

-

-

-

-

-

-

-

-

-

-

4位格雷码

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000

4'b0011:a_to_g=7'b1111001; //显示3

4'b0100:a_to_g=7'b0110011; //显示4

4'b0101:a_to_g=7'b1011011; //显示5

4'b0110:a_to_g=7'b1011111; //显示6

4'b0111:a_to_g=7'b1110000; //显示7

4: y= {d[2:0],d[3]}; // rol

5: y= {d[3],d[3:1]}; // asr

6: y= {d[1:0],d[3:2]}; // ror2

7: y= d;

// noshift

default: y = d;

图6-2 基本门电路仿真结果

综合结果如图6-3所示。

图6-3 基本门电路综合结果

2、 三态逻辑电路

EDA-Verilog,HDL期末复习题总结必过

EDA-Verilog,HDL期末复习题总结必过EDA-Verilog HDL期末复习题总结必过选择题1. 大规模可编程器件主要有FPGA、CPLD 两类,下列对FPGA 结构与工作原理的描述中,正确的是( C )。

A.FPGA 全称为复杂可编程逻辑器件;B.FPGA 是基于乘积项结构的可编程逻辑器件;C.基于SRAM 的FPGA 器件,在每次上电后必须进行一次配置;D.在Altera 公司生产的器件中,__ 系列属FPGA 结构。

2. 不完整的IF语句,其综合结果可实现(A )A. 时序逻辑电路B.组合逻辑电C. 双向电路D. 三态控制电路 3. 综合是EDA设计流程的关键步骤,在下面对综合的描述中,( D )是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

4. 大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA 结构与工作原理的描述中,正确的是( C )。

A. FPGA全称为复杂可编程逻辑器件;B. FPGA是基于乘积项结构的可编程逻辑器件;C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D. 在Altera公司生产的器件中,__系列属FPGA结构。

5. 以下关于状态机的描述中正确的是(B )A.Moore型状态机其输出是当前状态和所有输入的函数B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数D.以上都不对 6. 目前应用最广泛的硬件描述语言是( B )。

A. VHDLB. Verilog HDLC. 汇编语言D. C语言7. 一模块的I/O 端口说明:“input [7:0] a;”,则关于该端口说法正确的是(A )。

EDA技术及应用—Verilog HDL版(第三版) (1)

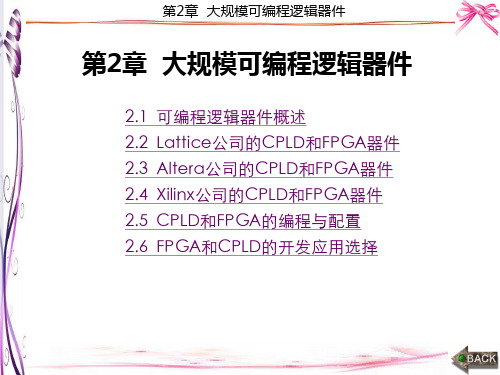

第2章 大规模可编程逻辑器件

(4) 封装代码。如Altera公司的EPM7128SLC84中的LC, 表示采用PLCC封装(Plastic Leaded Chip Carrier,塑料方形扁 平封装)。PLD封装除PLCC外,还有BGA(Ball Grid Array, 球形网状阵列)、C/JLCC(Ceramic /J-Leaded Chip Carrier,)、 C/M/P/TQFP(Ceramic/Metal/Plastic/Thin Quard Flat Package)、 PDIP/DIP(Plastic Double In line Package)、PGA(Ceramic Pin Grid Array)等,多以其缩写来描述,但要注意各公司稍有差 别,如PLCC,Altera公司用LC描述,Xilinx公司用PC描述, Lattice公司用J来描述。

第2章 大规模可编程逻辑器件

2.1.1 PLD的发展进程

最早的可编程逻辑器件出现在20世纪70年代初,主要是 可编程只读存储器(PROM)和可编程逻辑阵列(PLA)。20世 纪70年代末出现了可编程阵列逻辑(Programmable Array Logic,简称PAL)器件。20世纪80年代初期,美国Lattice公 司推出了一种新型的PLD器件,称为通用阵列逻辑(Generic Array Logic,简称GAL),一般认为它是第二代PLD器件。 随着技术进步,生产工艺不断改进,器件规模不断扩大,逻 辑功能不断增强,各种可编程逻辑器件如雨后春笋般涌现, 如PROM、EPROM、EEPROM等。

第2章 大规模可编程逻辑器件

采用ISP技术之后,硬件设计可以变得像软件设计那样灵活 而易于修改,硬件的功能也可以实时地加以更新或按预定的 程序改变配置。这不仅扩展了器件的用途,缩短了系统的设 计和调试周期,而且还省去了对器件单独编程的环节,因而 也省去了器件编程设备,简化了目标系统的现场升级和维护 工作。

Verilog复习题

Verilog 复习题一、填空题1.用EDA技术进行电子系统设计的目标是最终完成ASIC的设计与实现。

2.可编程器件分为CPLD和FPGA。

3.随着EDA技术的不断完善与成熟,自顶向下的设计方法更多的被应用于Verilog HDL设计当中。

4.目前国际上较大的PLD器件制造公司有ALtera和Xilinx公司。

5.完整的条件语句将产生组合电路,不完整的条件语句将产生时序电路。

6.阻塞性赋值符号为,非阻塞性赋值符号为<=_。

7.有限状态机分为Moore和Mealy两种类型。

8.EDA缩写的含义为电子设计自动化(Electronic Design Automation) |9.状态机常用状态编码有二进制、格雷码和独热码。

10.Verilog HDL中任务可以调用其他任务和函数。

11.系统函数和任务函数的首字符标志为_$_,预编译指令首字符标志为。

12 .可编程逻辑器件的优化过程主要是对速度和资源的处理过程。

13、大型数字逻辑电路设计采用的IP核有软IP、固IP和硬IP。

二、选择题1、已知“a =1b' 1; b=3b'001; ”那么{a,b} =( C )(A) 4b'0011 (B) 3b'001 (C) 4b'1001 (D) 3b'1012、在verilog中,下列语句哪个不是分支语句? ( D )(A) if-else (B) case (C) casez (D) repeat3、V erilog HDL语言进行电路设计方法有哪几种( 8分)①自上而下的设计方法(Top-Down )②自下而上的设计方法(Bottom-Up )③综合设计的方法4、在verilog 语言中,a=4b'1011,那么&a= (D )(A) 4b'1011 (B) 4b'1111 (C) 1b'1 (D) 1b'05、在verilog语言中整型数据与(C )位寄存器数据在实际意义上是相同的。

第五章组合逻辑电路的VerilogHDL实现

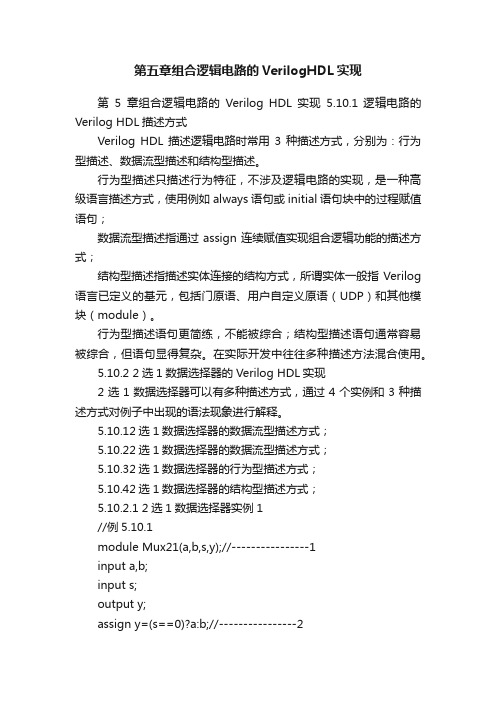

第五章组合逻辑电路的VerilogHDL实现第5章组合逻辑电路的Verilog HDL实现5.10.1 逻辑电路的Verilog HDL描述方式Verilog HDL描述逻辑电路时常用3种描述方式,分别为:行为型描述、数据流型描述和结构型描述。

行为型描述只描述行为特征,不涉及逻辑电路的实现,是一种高级语言描述方式,使用例如always语句或initial 语句块中的过程赋值语句;数据流型描述指通过assign连续赋值实现组合逻辑功能的描述方式;结构型描述指描述实体连接的结构方式,所谓实体一般指Verilog 语言已定义的基元,包括门原语、用户自定义原语(UDP)和其他模块(module)。

行为型描述语句更简练,不能被综合;结构型描述语句通常容易被综合,但语句显得复杂。

在实际开发中往往多种描述方法混合使用。

5.10.2 2选1数据选择器的Verilog HDL实现2选1数据选择器可以有多种描述方式,通过4个实例和3种描述方式对例子中出现的语法现象进行解释。

5.10.12选1数据选择器的数据流型描述方式;5.10.22选1数据选择器的数据流型描述方式;5.10.32选1数据选择器的行为型描述方式;5.10.42选1数据选择器的结构型描述方式;5.10.2.1 2选1数据选择器实例1//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------310.2.1 2选1数据选择器实例11. Verilog语言描述//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------32. 程序说明(1)注释行(2)模块定义语句module和endmodule所有的程序都置于模块(module)框架结构内。

《EDA技术基础》复习资料

EDA复习资料《EDA技术基础》题库及参考答案(试用版)目录一、填空题 (I)二、单选题 (4)三、简答题 (10)四、应用题 (11)五、上机实验题 (15)一、填空题1.现代电子技术经历了CAD 、CAE 和EDA 三个主要的发展阶段。

2.EDA技术包括大规模可编程器件、硬件描述语言HDL 、EDA工具软件和实验开发系统四大要素。

3.EDA的设计输入主要包括文本输入方式、图形输入方式和波形输入方式三种形式。

4.目前已经成为IEEE标准、应用最为广泛的硬件描述语言有VHDL 和Verilog HDL 。

仿真是一种对所设计电路进行间接检测的方法,包括_ 功能仿真和_ 时序仿真。

5.层次化设计是将一个大的设计项目分解为若干个子项目或若干个层次来完成的。

先从底层的电路设计开始,然后在___高层次___的设计中逐级调用低层次的设计结果,直至实现系统电路的设计。

6.用HDL设计的电路,既可以被高层次的系统调用,成为系统的一部分,也可以作为一个电路的功能块独立存在和独立运行____。

7.可编程逻辑器件从结构上可分为乘积项结构器件和查找表结构器件。

8.PLD(FPGA、CLPD)种类繁多,特点各异。

共同之处包括的三大部分是逻辑块阵列、输入/输出块和互连资源。

9.FPGA两类配置下载方式是主动配置方式和被动配置方式。

10.Quartus II是EDA器件制造商Altera公司自己开发的___EDA工具___软件。

11.Quartus II工具软件安装成功后、第一次运行前,还必授权。

12.Q uartus II支持原理图、__文本和波形等不同的编辑方式。

13.在Quartus II集成环境下,设计文件不能直接保存在计算机磁盘根目录中,因此设计者在进入设计之前,应当在磁盘根目录中建立保存设计文件的工程目录(文件夹)。

14.在Quartus II集成环境下执行原理图输入设计法,应选择___模块/原理图文件(Block Diagram/Schematic File ).__方法,设计文件的扩展名是__ .bdf_______。

Verilog入门教程笔记

将编码后的信号还原成原始信号,常用于数据解压缩和控制信号生成。例如, 将3个输入信号译码成8个输出信号的3-8译码器。

多路选择器设计实例

多路选择器(Multiplexer)

根据选择信号从多个输入信号中选择一个输出,常用于数据选择和路由。例如,2选1 多路选择器、4选1多路选择器等。

明确CPU需要实现哪些指令集,具备哪些功能,以及达到什么样的性 能指标。

选择合适的架构

根据需求和性能指标,选择适合的CPU架构,如RISC或CISC。

设计指令集

根据所选架构,设计相应的指令集,包括指令格式、操作码、寻址方 式等。

规划寄存器组

设计寄存器组,包括通用寄存器、特殊功能寄存器等,以满足指令执 行和数据存储的需求。

03

组合逻辑电路设计

基本门电路实现方法

01

02

03

04

05

与门(AND Gate)或门(OR Gate) 非门(NOT Gate)与非门(NAND 或非门(NOR

Ga…

Gat…

实现逻辑与操作,当所有输 入为高电平时输出高电平。

实现逻辑或操作,当任一输 入为高电平时输出高电平。

实现逻辑非操作,将输入信 号取反后输出。

实现二进制数的减法运算,可 以通过加法器和取反器来实现。

实现二进制数的乘法运算,通 常采用逐位相乘再相加的方式 实现。

实现二进制数的除法运算,通 常采用逐位相除再减去的方式 实现,也可以使用更高效的算 法如SRT除法算法等。

04

时序逻辑电路设计

触发器类型及特点介绍

RS触发器

具有置0、置1和保持功能,是基 本存储单元。

数字电路的设计。

发展历程

EDA技术与Verilog设计第六章课后习题部分答案

else case(in) 3'd0: out=8'b11111110; 3'd1: out=8'b11111101; 3'd2: out=8'b11111011; 3'd3: out=8'b11110111; 3'd4: out=8'b11101111; 3'd5: out=8'b11011111; 3'd6: out=8'b10111111; 3'd7: out=8'b01111111; endcase end

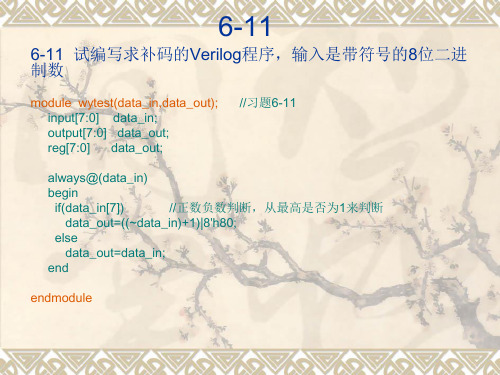

6-11仿真波形

8A-原码表示的十进制数-10 B6-原码表示的十进制数-54 80-原码表示的十进制数128 0A----十进制数10 36-----十进制数53

6-12

6-12 编写两个四位二进制数相减的verilog程序

module wytest(opr1,opr2,out_data); //完成Opr1-opr2的运算 input[3:0] opr1,opr2; output[4:0] out_data; reg[3:0] out; reg cout; function[3:0] abs; input[3:0] data; case(data[3]) 1'b0:abs=data; 1'b1:abs=(~data)+1; //对负数求绝对值,按位取反再加1 endcase endfunction

6-13

仿真波形

6-13

module wytest(bcd_in,out); //习题6-13 input[3:0] bcd_in; output out; //assign out=(bcd_in>4)?1:0;

EDA技术与Verilog_HDL(潘松)第四章与第六章课后习题答案

4-5 用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。比 较这两种方式。

4-5 用Verilog设计一个3-8译码器,要求分别用case语句和if_else语句。比较这两 种方式。

module decoder3_8 ( G1 ,Y ,G2 ,A ,G3 ); input G1, G2, G3; wire G1, G2, G3; input [2:0] A ; wire [2:0] A ; output [7:0] Y ; reg [7:0] Y ; reg s; always @ ( A ,G1, G2, G3) begin s <= G2 | G3 ; if (G1 == 0) Y <= 8'b1111_1111; else if (s) Y <= 8'b1111_1111; else case ( A ) 3'b000: Y = 8'b11111110; 3'b001: Y = 8'b11111101; 3'b010: Y = 8'b11111011; 3'b011: Y = 8'b11110111; 3'b100: Y = 8'b11101111; 3'b101: Y = 8'b11011111; 3'b110: Y = 8'b10111111; 3'b111: Y = 8'b01111111; default:Y = 8'bxxxxxxxx; endcase end endmodule

reg [2:0]A ;

wire[7:0]Y ; reg G1 ,G2 ,G3;

decoder3_8 DUT ( G1 ,Y ,G2 ,A ,G3 );

EDA与FPGA,Verilog第2章

例2.11 调用门元件实现的半加器 module half_add1(a,b,so,co); input a,b; output so,co; and(co,a,b); xor(so,a,b); endmodule

2.4 数据流描述

0

1

图2.2 2选1数据选择器

图2.3 2选1数据选择器门级原理图

2.4 数据流描述

例2.6 门级结构描述的2选1数据选择器 module mux2_1a(out,s,b,sel); input a,b,sel;output out; not(sel_,sel);and(a1,a,sel_),(a2,b,sel);or(out,a1,a2); endmodule 例2.7 行为描述的2选1数据选择器 module mux2_1b(out,a,b,sel); input a,b,sel; output reg out; always@* begin if(sel) out=b; else out=a; end endmodule

and (w,in1,s0_n,s1_n),(x,in2,s0_n,s1),

(y,in3,s0,s1_n),(z,in4,s0,s1); or (out,w,x,y,z); endmodule

2.3

行为描述

【例2.2】 用case语句描述的4选1 MUX module mux4_1b(out,in1,in2,in3,in4,s0,s1); input in1,in2,in3,in4,s0,s1; output reg out; always@(*) //使用通配符 case({s0,s1}) 2'b00:out=in1; 2'b01:out=in2; 2'b10:out=in3; 2'b11:out=in4; default:out=2'bx; endcase endmodule

(EDA技术及应用)第6章VerilogHDL设计应用实例

第6章 Verilog HDL设计应用实例

6.1 8位加法器的设计

1.系统设计思路 加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器 都可由加法器来构成。多位加法器的构成有两种方式:并行进位和 串行进位。并行进位加法器设有进位产生逻辑,运算速度较快;串 行进位方式是将全加器级联构成多位加法器。并行进位加法器通常 比串行级联加法器占用更多的资源。随着位数的增加,相同位数的 并行加法器与串行加法器的资源占用差距也越来越大。因此,在工 程中使用加法器时,要在速度和容量之间寻找平衡点。 实践证明, 4位二进制并行加法器和串行级联加法器占用几乎相 同的资源。这样,多位加法器由 4位二进制并行加法器级联构成是 较好的折中选择。本设计中的8位二进制并行加法器即是由两个4位 二进制并行加法器级联而成的,其电路原理图如图6.1所示。

在掌握了EDA技术的基础知识和基本操作后,学习 EDA技术最有效地方法就是进行EDA技术的综合应用设计 。本章阐述了12个非常实用的Verilog HDL综合应用设计实 例的系统设计思路,主要Verilog HDL源程序,部分时序仿 真和逻辑综合结果及分析,以及硬件的逻辑验证方法。这些 综合应用设计实例包括8位加法器、8位乘法器、8位除法器 等基本运算电路,数字频率计、数字秒表、交通灯信号控制 器、可调信号发生电路、闹钟系统等常用应用电路,PWM 信号发生器、高速PID控制器,FIR滤波器,CORDIC算法 的应用等电机控制、数字信号处理、模糊控制、神经网络中 经常用到的基本电路。

EDA技术的基础知识

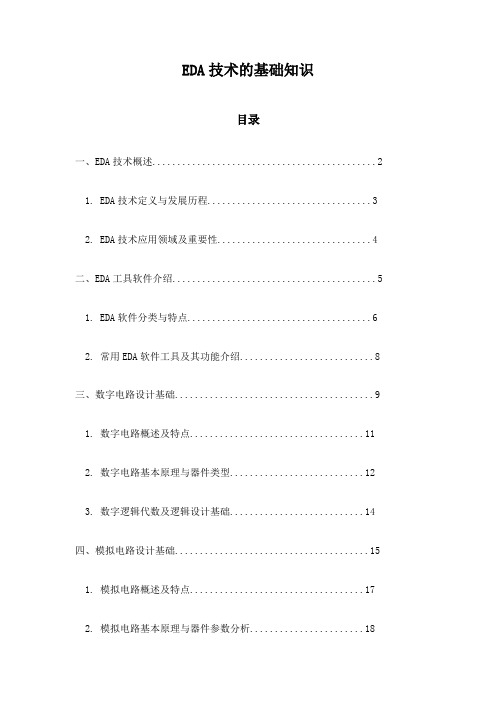

EDA技术的基础知识目录一、EDA技术概述 (2)1. EDA技术定义与发展历程 (3)2. EDA技术应用领域及重要性 (4)二、EDA工具软件介绍 (5)1. EDA软件分类与特点 (6)2. 常用EDA软件工具及其功能介绍 (8)三、数字电路设计基础 (9)1. 数字电路概述及特点 (11)2. 数字电路基本原理与器件类型 (12)3. 数字逻辑代数及逻辑设计基础 (14)四、模拟电路设计基础 (15)1. 模拟电路概述及特点 (17)2. 模拟电路基本原理与器件参数分析 (18)3. 模拟电路设计与仿真分析 (19)五、EDA设计流程与实现方法 (20)1. 设计需求分析 (22)2. 设计原理框图与功能验证 (23)3. 逻辑设计与仿真验证 (24)4. 物理设计与布局布线优化 (26)5. 测试验证与可靠性分析 (27)六、EDA技术中的关键概念与技术点解析 (28)1. 原理图输入与混合信号仿真技术解析 (29)2. 布局布线优化算法与技巧探讨 (30)3. 自动化测试生成与验证技术介绍 (32)4. EDA设计中的知识产权保护问题探讨等)进一步深入介绍不同章节内容34七、设计流程详细解析 (36)一、EDA技术概述EDA技术,即电子设计自动化(Electronic Design Automation),是电子工程领域的一门重要技术。

它利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计等一系列流程。

EDA技术能够大大提高电子设计的效率和可靠性,降低设计成本,缩短产品上市时间。

随着半导体技术的飞速发展,集成电路(IC)的设计越来越复杂,传统的硬件描述语言(如Verilog HDL和VHDL)已经无法满足设计需求。

EDA技术应运而生,成为电子设计领域的重要工具。

EDA技术涵盖了数字电路设计和模拟电路设计两个方面。

数字电路设计主要关注逻辑电路的设计和实现,包括组合逻辑电路、时序逻辑电路等。

EDA技术_组合逻辑电路设计_Verilog

再对9527从二进制到 abdcdefg译码

reg[6:0] abcdefg; always@(bin) begin case(bin) 4„b0000: abcdefg<= 7'b0111111; …. …. default: abcdefg<= 7'b0000000; endcase

3.5 实例3:计数牌子

CMOS传输门三态门电路

3.5 数码管显示

3.5 例:在数码管上显示‟2‟

module seg7(data_out); output[6:0] data_out; assign data_out=7‟b 1011011

endmodule

3.5 七段译码器结构

七段 LED 数码管显 示电路

a

in0

3.3 常用过程语句 if else

// “begin” 和 “end”就好比C语言中的“{”和“}”. if (enable = = 1'b1) begin data = 10; // 十进制赋值 address = 16'hDEAD; //十六进制 wr_enable = 1'b1; //二进制 end else begin data = 32'b0; wr_enable = 1'b0; address = address + 1; end

end endmodule

b=a; c=b;

3.3译码器电路

2线-4线译码器真值表 输入 A B 输出 Y0 Y 1 Y2 Y3

0

0 1 1

0

1 0 1

1

0 0 0

0

1 0 0

0

0 1 0

0

Verilog HDL

燕 山 大 学 电 子 实 验 中 心

(四)结构声明语句 结构声明语句包括always,initial,task和 function等4种结构。 always块语法结构 always@(敏感信号表达式)//列出影响块内取 值的所有信号; begin //过程赋值语句; //if语句,case语句; //tast语句、function语句; end

用结构描述实现电路系统设计 任何用Verilog HDL描述的电路设计模块 任何用 描述的电路设计模块 (module),均可用模块例化语句,例化 ,均可用模块例化语句, 一个元件,来实现电路系统的设计。 一个元件,来实现电路系统的设计。 模块例化语句格式与逻辑门例化语句格 式相同,具体格式如下: 式相同,具体格式如下: 元件名〈例化元件的名称〉 端口列表 端口列表); 元件名〈例化元件的名称〉(端口列表

燕 山合逻辑电路中,任何时刻的输出仅 决定于当时的输入信号 在数字系统中,有些逻辑电路是经常使 用的,如加法器、编码器、译码器、数 据选择器、数据比较器、奇偶校验器等。

燕 山 大 学 电 子 实 验 中 心

用Verilog HDL的case语句可以直接描述真值表3-3表示的逻辑抽象 结果,完整的源程序bcd8421.v如下: module bcd8421(A,B); input[3:0] A; output[3:0] B; reg[3:0] B; always@(A) begin case(A) 0:B=3; 1:B=4; 2:B=5; 3:B=6; 4:B=7; 5:B=8; 6:B=9; 7:B=10; 8:B=11; 9:B=12; default:B=4’bx; endcase end endmodule

Verilog HDL的语句 的语句 (一)赋值语句 一 赋值语句 (1)门基元赋值语句 门基元赋值语句 例化门标识符(门输出 门输出,门输 基本逻辑门关键词 例化门标识符 门输出 门输 门输入2,…, 门输入 门输入n); 入1,门输入 门输入 例如: 例如: 具有a, , , 输入和 输入和y输出与非门的门基元 具有 ,b,c,d输入和 输出与非门的门基元 赋值语句为: 赋值语句为: nand u1(y,a,b,c,d);

4 组合逻辑电路的Verilog HDL描述精品PPT课件

(a)bufif1 (b)notif1

bufif1真值表

notif1真值表

控制输入 01 x z

z 0 0/z 0/z

z 1 1/z 1/z

zx zx

xx xx

notif1 控制输入 01 xz

0 z 1 1/z 1/z

数 据

1

z

0

0/z 0/z

输xz x x x

入zz x x x

4.6.1 组合逻辑电路的门级建模

门级建模:将逻辑电路图用HDL规定的文本语言表示出来。

三态门

元件符号 功能说明

基本门级元件模型 多输出门

元件符号 功能说明

多输入门

and or xor buf

bufif1

bufif0

多输入端的与门

多输入端的或门

多输入端的异或门

多输出端的缓冲器

控制信号高电平有效的三态缓冲 器

endmodule

下面用条件运算符描述了一个2选1的数据选择器。

//Dataflow description of 2-to-1-line multiplexer module mux2x1_df (A,B,SEL,L);

input A,B,SEL; output L; assign L = SEL ? A : B; endmodule

//Gate-level description of a 2-

4、设计举例

to-4-line decoder

试用Verilog语言的门级

module _2to4decoder

(A1,A0,E,Y);

元件描述2线-4线译码器.

input A,B,E;

EDA实验报告 常用组合逻辑电路设计

EDA实验报告实验目的:1.常用组合逻辑电路设计方法2.VHDL设计思想与调试方法3.LPM元件定制4.电路设计的仿真验证和硬件验证实验要求:学习常用组合逻辑的可综合代码的编写,学习VHDL语言的编程思想与调试方法,学习通过定制LPM元件实现逻辑设计,通过波形仿真及硬件实验箱验证设计的正确与否。

实验流程:1.利用VHDL代码实现2.利用LPM元件定制实现3.运用分析调试工具RTL viewer查看景软件解释生成的原理图并分析实验具体步骤:1.利用VHDL代码实现(1)VHDL代码(2)编译通过后进行波形仿真2.利用LPM元件定制实现(1)Tools→ Mega Wizard Plug_in Manager或在图形编辑窗口空白处双击(2)Create a new custom megafunction variation(3)Installed Plug_Ins→ Arithmetic lpm_compare(4)然后进行相应的设置,Generate netlist ,选择要生成的文件,完成生成的VHDL语言代码:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY lpm;USE lpm.all;ENTITY lpm_compare2 ISPORT(dataa : IN STD_LOGIC_VECTOR (1 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (1 DOWNTO 0);AeB : OUT STD_LOGIC ;AgB : OUT STD_LOGIC ;AgeB : OUT STD_LOGIC ;AlB : OUT STD_LOGIC ;AleB : OUT STD_LOGIC ;AneB : OUT STD_LOGIC);END lpm_compare2;ARCHITECTURE SYN OF lpm_compare2 ISSIGNAL sub_wire0 : STD_LOGIC ;SIGNAL sub_wire1 : STD_LOGIC ;SIGNAL sub_wire2 : STD_LOGIC ;SIGNAL sub_wire3 : STD_LOGIC ;SIGNAL sub_wire4 : STD_LOGIC ;SIGNAL sub_wire5 : STD_LOGIC ;COMPONENT lpm_compareGENERIC (lpm_representation : STRING;lpm_type : STRING;lpm_width : NA TURAL);PORT (dataa : IN STD_LOGIC_VECTOR (1 DOWNTO 0);datab : IN STD_LOGIC_VECTOR (1 DOWNTO 0);AgeB : OUT STD_LOGIC ;AlB : OUT STD_LOGIC ;AleB : OUT STD_LOGIC ;AneB : OUT STD_LOGIC ;AgB : OUT STD_LOGIC ;AeB : OUT STD_LOGIC);END COMPONENT;BEGINAgeB <= sub_wire0;AlB <= sub_wire1;AleB <= sub_wire2;AneB <= sub_wire3;AgB <= sub_wire4;AeB <= sub_wire5;lpm_compare_component : lpm_compareGENERIC MAP (lpm_representation => "UNSIGNED",lpm_type => "LPM_COMPARE",lpm_width => 2)PORT MAP (dataa => dataa,datab => datab,AgeB => sub_wire0,AlB => sub_wire1,AleB => sub_wire2,AneB => sub_wire3,AgB => sub_wire4,AeB => sub_wire5);END SYN;生成的波形图:生成的RTL viewer原理图思考题1、VHDL实体描述方式有哪些类型?优缺点是什么?答:(1)结构描述:使用元件例化方法描述硬件构造特征,定义实现实体的信号与实体的精确互连结构。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

always @ (state)

case (state)

2‟b00 : scan<=4‟b0001; 2‟b01 : scan <=4‟b0010; 2‟b10 : scan <=4‟b0100; 2‟b11 : scan <=4‟b1000; default: scan <=4‟b0000; endcase

4.打开scan3的时候, 在abcdefg线上赋值 “7”

首先:设计SCAN信号

首先要降低扫描速度,生成一个大约为 0.01s-0.1s的时钟 利用这个时钟信号产生一个scan信号如 下: reg[1:0] state; reg[3:0] scan;//注意要用always就必 须是reg always@(posedge clk_div) state<=state+1‟b1;

reg[3:0] shiwei; //十位数 always@(posedge clk_1s) if(reset==1‟b1) shiwei<=4‟b0; else if(gewei==4‟d9) begin if(shiwei==4‟d9); shiwei<=4‟b0; else shiwei<=shiwei+1‟b1; end

endcase

3.3 过程语句while

module counter (clock,rst,enable,count); input clock, rst, enable; output [3:0] count; reg [3:0] count; always @ (posedge clock or posedge rst) if (rst) count <= 0; else begin : COUNT while (enable) begin count <= count + 1; disable COUNT; end end endmodule

分不同的时间把9、5、2、7 放到bin上面去

reg[3:0] bin;//不在always里面赋值就用wire,否则用 reg always@(state) case (state) 2‟b00 : bin<=4‟d9; 2‟b01 : bin<=4‟d5; 2‟b10 : bin<=4‟d2; 2‟b11 : bin<=4‟d7; default: bin<=4‟d0; endcase

1011011 1001111 1100110 1101101 1111100 0000111

1

2 3 4 5 6 7

1 0 0 0

1 0 0 1

1111111

1100111

8

9

3.5 代码

module qiduan( data_in;//七段数码管显示电路的输入,对应图的in3-in0,in3对应高位 data_out);//七段数码管显示电路的输出,对应图中的g-a,g对应高位 input[3:0] data_in;//输入输出端口定义 output[6:0] data_out; reg[6:0] data_out;//使用always建模组合逻辑需要定义输出为寄存器 always@(data_in) //输入为data_in begin case(data_in)//输入的不同情况 4'b0000: data_out = 7'b0111111; // 0 4'b0001: data_out = 7'b0000110; // 1 4'b0010: data_out = 7'b1011011; // 2 4'b0011: data_out = 7'b1001111; // 3 4'b0100: data_out = 7'b1100110; // 4 4'b0101: data_out = 7'b1101101; // 5 4'b0110: data_out = 7'b1111100; // 6 4'b0111: data_out = 7'b0000111; // 7 4'b1000: data_out = 7'b1111111; // 8 4'b1001: data_out = 7'b1100111; // 9 default: data_out = 7'b0000000; //default,当输入为其他值时, 输出有效,为全0 endcase end endmodule

第 3章

组合逻辑电路设计

数字电路

组合电路

电路输出完全依赖电路输入

与非门等

运算

电路输出在一定程度不依赖电路输入

时序电路

D触发器

记忆

1

组合电路

实现功能

时序电路

使功能有序

2

3.3 Verilog 过程及译码电路

Always 过程语句

always定义的过程块是一个电路,电路 从上电开始就会一直执行; (从代码一开始就执行,执行完了再回 到过程块的最初来执行,周而复始,不 会停止,直到代码执行完毕)

reg[3:0] qianwei; //千位数 always@(posedge clk_1s) if(reset==1‟b1) qianwei<=4‟b0; else

if((gewei==4‟d9)&&(shiwei==4‟d9)&&(baiwei ==4‟d9)) begin if(qianwei==4‟d9); qianwei<=4‟b0; else qianwei<=shiwei+1‟b1; end

再对9527从二进制到 abdcdefg译码

reg[6:0] abcdefg; always@(bin) begin case(bin) 4„b0000: abcdefg<= 7'b0111111; …. …. default: abcdefg<= 7'b0000000; endcase

3.5 实例3:计数牌子

3.3 过程语句caቤተ መጻሕፍቲ ባይዱe

case(address) 0 : $display ("It is 11:40PM"); 1 : $display ("I am feeling sleepy"); 2 : $display ("Let me skip this tutorial"); default : $display ("Need to complete");

reg[3:0] baiwei; //百位数 always@(posedge clk_1s) if(reset==1‟b1) baiwei<=4‟b0; else if((gewei==4‟d9)&&(shiwei==4‟d9)) begin if(baiwei==4‟d9); baiwei<=4‟b0; else baiwei<=baiwei+1‟b1; end

end endmodule

b=a; c=b;

3.3译码器电路

2线-4线译码器真值表 输入 A B 输出 Y0 Y 1 Y2 Y3

0

0 1 1

0

1 0 1

1

0 0 0

0

1 0 0

0

0 1 0

0

0 0 1

逻辑函数:

Y0 AB m0

Y1 AB m1 Y2 AB m2

Y3 AB m3

任务分析: 设计一个计数牌子,能从0000计数 到9999,每隔1秒钟跳动一下。通过复 位可以把系统清零为0000

【涉及】 动态数码管显示,复位,分频电路等

设计思路:

1.内部所有数据都是2进制的,所以需要设

计4个4位2进制的reg,分别对应显示的

4个数字,再通过动态扫描电路送到LED

上面去显示。

2.利用1秒的时钟,构建“个、十、百、千”

位的变换规律

设计模块1:分频电路

代码:略…

1.产生一个1秒的时钟:clk_1s

2.产生一个0.01秒的时钟(为了动态显示 使用):clk_div

设计模块2:计数器

reg[3:0] gewei; //各位数 always@(posedge clk_1s) if(reset==1‟b1) gewei<=4‟b0; else if(gewei==4‟d9) gewei<=4‟b0; else gewei<=gewei+1‟b1;

CMOS传输门三态门电路

3.5 数码管显示

3.5 例:在数码管上显示‟2‟

module seg7(data_out); output[6:0] data_out; assign data_out=7‟b 1011011

endmodule

3.5 七段译码器结构

七段 LED 数码管显 示电路

a

in0

3'b101:data_out<=8'b0010_0000; 3'b110:data_out<=8'b0100_0000; 3'b111:data_out<=8'b1000_0000; endcase end endmodule

3.4 三态门电路

输入信号 rw 1 0 co_data co_data out_data

3.3 过程中的阻塞赋值与 非阻塞赋值

阻塞式 (blocking) 的操作符为 “=” 非阻塞式 (non-blocking)的操作符 为 “ <= ” 阻塞赋值和非阻塞赋值的基本区别是: 阻塞赋值是顺序执行语句,而非阻塞赋 值是并行执行语句。两种语句的含义不 同,建模的应用也就不同。