AT89C51单片机八路抢答器

毕业设计-基于AT89C51单片机的八路智力抢答器设计

智力抢答器设计摘要:随着科学技术的不断发展,促使人们学科学、学技术、学知识的手段多种多样。

抢答器作为一种工具,已广泛应用于各种智力和知识竞赛场合。

但抢答器的使用频率较低,且有的要么制作复杂,要么可靠性低,减少兴致。

作为一个单位若专购一台抢答器虽然在经济上可以承受,但每年使用的次数极少,往往因长期存放使抢答器损坏,再购置的麻烦和及时性就会影响活动的展开,因此设计了本抢答器。

本设计是以八路抢答为基本理念。

考虑到依需设定限时回答的功能,利用AT89C51单片机及外围接口实现的抢答系统,利用单片机的定时器/计数器定时和记数的原理,将软、硬件有机的结合起来,使得系统能够正确地进行计时,同时使LED数码管能够正确的显示时间。

用开关做键盘输出,扬声器发生提示。

同时系统能够实现:在抢答中,只有开始后抢答才有效,如果在开始抢答前抢答为无效;抢答限定时间和回答问题的时间可在1~99s设定;可以显示是哪位选手有效抢答,正确按键后有音乐提示;抢答时间和回答问题时间倒计时显示,满时后系统计时自动复位及主控强制复位;按键锁定,在有效状态下,按键无效非法。

关键词:AT98C51,抢答器,倒计时,报警Design on Intellectual Answer DevicesAbstract:With the continuous development of science and technology, promote learning science, science and technology, knowledge of the variety of means. With a tool for Answer devices, this has been widely used in all kinds of intelligence and knowledge contests occasions. But Answer devices are used for lower frequency, and some production complex or low reliability, and reduced interest. As a unit, if the purchase is a Answer devices. Although the economy can bear, each year the number is extremely small, because of the long-term storage Answer devices for damage to the purchase of the trouble and timeliness of activities. The development will be affected, so this Answer devices is designed.This design is eight road Answer devices as the basic concept. By taking into account the need for setting time and limiting to answer the function, which uses AT89C51 microcontroller and external interface of answer system, and uses SCM timer/counter timing and the count principle, the software and hardware organically combined, which could allow the right to show time, and the LED digital tube display to the correct time. Switching with the keyboard output, speakers in tips. At the same time, system can be realized: In the answer only after the answer to be valid, it is invalid if at the beginning of answer before the answer; The answer time and answer the questions time can be set in the 1-99s; players who can show that it is effective, right after the music keys; answer time and answer the questions time will show countdown, over time, the system automatically rest control and mandatory reduction; keys locked in an effective state, the key is invalid illegal.Key words: AT89C51, Answer devices, countdown, alarm目录1 引言 (1)1.1课题研究的相关背景 (1)1.2选题的目的和意义 (1)1.3国内外研究现状 (2)1.4抢答器目前存在的主要问题 (2)1.5课题研究的内容 (2)2 抢答器的系统概述 (4)2.1系统的主要功能 (4)2.2系统需求分析 (5)2.3抢答器的工作流程 (5)2.4抢答器的工作过程 (6)2.5AT89C51特殊功能寄存器 (7)2.6AT89C51的功能及简介 (8)2.6.1 89系列单片机的概况 (8)2.6.2 AT89C51单片机 (9)2.6.3 AT89C51单片机的内部结构 (10)2.6.4 各类型单片机的比较分析 (10)2.7抢答器的优点及组成 (11)2.8本章小结 (11)3 系统总体方案的设计 (13)3.1硬件电路的设计 (13)3.2总体原理图 (14)3.3时钟频率电路的设计 (15)3.4复位电路的设计 (15)3.5显示电路的设计 (16)3.6键盘扫描电路的设计 (18)3.7发声 (19)第I 页共II 页3.8系统复位 (20)3.9本章小结 (21)4 软件设计 (23)4.1主程序系统结构图 (23)4.2软件任务分析 (23)4.3主要程序分析 (24)5 PROTEUS仿真 (34)5.1PROTEUS总仿真图 (34)5.2PROTEUS各功能仿真图 (35)5.2.1 抢答器复位仿真 (35)5.2.2 抢答器抢答时间+1调整 (35)5.2.3 抢答器抢答时间-1调整 (36)5.2.4 抢答器回答时间+1调整 (36)5.2.5 抢答器回答时间-1调整 (37)5.2.6 抢答开始后倒计时仿真 (37)5.2.7 抢答开始后五秒倒计时发声仿真 (38)5.2.8 八号选手抢答成功后倒计时仿真 (38)6 PCB制版7 总结 (39)参考文献 (41)致谢 (42)第II 页共II 页计说明书1 引言随着科学技术的不断发展,促使人们学科学、学技术、学知识的手段多种多样。

毕业设计-基于AT89C51单片机的八路多功能抢答器设计

基于AT89C51单片机的八路多功能抢答器设计目录摘要 (2)绪论 (3)1 抢答器系概述 (4)1.1抢答器的功能模块 (4)1.2抢答器的工作原理 (5)1.3抢答器的特点及组成 (7)2硬件设计 (7)2.1硬件详细清单 (7)2.2 抢答器总电路图 (8)2.3 AT89C51的内部结构和功能 (8)2.4 晶体振荡器和电容的设计 (10)2.5 七段数码管显示电路的设计 (10)2.6 扬声器的设计 (11)2.7 按钮的设计 (11)2.8 芯片74HC30、74LS04的设计 (12)3软件设计 (12)3.1 软件系统结构图和程序流程图 (12)3.2 程序分析 (13)结束语 (24)致谢 (25)参考文献 (26)附录 (27)在以往企业或学校举行知识竞赛中,都是主持人读题,观众选手得安静仔细听题目,有条件的花上万元买个电子抢答器,算是给知识竞赛赛场添彩了。

现实中大多数是依靠主持人发挥水平,但选手和观众要渴望类似跟电视台搞的知识竞赛中的效果一样是难以实现的。

而我们设计的抢答器节省的不小的开支,还能直观公正的看清哪位选手先抢答到题并有主持人来往下读题目。

它的功能实现是由主持人按键来控制总开关,在抢答中,只要主持人按下开始后抢答才有效,如果在开始抢答前抢答为无效;抢答限定时间和回答问题的时间可在1-99s设定;可以显示是哪位选手有效抢答和无效抢答,正确按键后有声音提示;抢答时间和回答问题时间倒记时显示,满时后系统计时自动复位及主持人强制复位;按键锁定,在有效状态下,按键无效非法。

本次设计是用AT89C51单片机为核心控制元件,设计一个八路多功能抢答器。

以AT89C51单片机作为主控核心,与芯片74LS04、74HC30;扬声器等等构成硬件操作,再利用汇编语言来编程,来控制抢答器的功能实现。

这次设计的系统实用性强、判断精确、操作简单、扩展功能强。

关键词:抢答器 AT89C51 汇编语言计时在知识竞赛中,特别是做抢答题时,在抢答过程中,为了更确切的知道哪一组或哪一位选手先抢答到题,必须要有一个系统来完成这个任务。

单片机-八路抢答器--仿真图

基于51单片机的8路抢答器摘要此次设计提出了用AT89C51单片机为核心控制元件,设计一个简易的抢答器,本方案以AT89C51单片机作为主控核心,与晶振、数码管、蜂鸣器等构成八路抢答器,利用了单片机的延时电路、按键复位电路、时钟电路、定时/中断等电路,设计的八路抢答器具有实时显示抢答选手的号码和抢答时间的特点,还有复位电路,使其再开始新的一轮的答题和比赛,同时还利用C语言编程,使其实现一些基本的功能。

本设计的系统实用性强、判断精确、操作简单、扩展功能强。

它的功能实现是比赛开始,主持人读完题之后按下总开关,即计时开始,此时数码管开始进行30s的倒计时,直到有一个选手抢答时,对应的会在数码管上显示出该选手的编号和抢答所用的时间,同时蜂鸣器也会发出声音,以提示有人抢答本题,如果在规定的60s时间内没有做出抢答,则此题作废,即开始重新一轮的抢答。

在抢答和回答时间的最后5s,蜂鸣器都会给予报警提示。

关键词:单片机、AT89C51、抢答器、编码器、计数器、触发器、定时器目录引言------------------------------------------------------------------------------------------------------------- 3 绪论------------------------------------------------------------------------------------------------------------- 4 第1章系统设计内容--------------------------------------------------------------------------------- 4 1.1 系统设计依据------------------------------------------------------------------------------------------- 4 1.2 设计任务和要求------------------------------------------------------- 4 1.3 设计目的------------------------------------------------------------------------------------------------- 4第2章硬件设计-------------------------------------------------------------------------------------- 5 2.1 单片机控制原理---------------------------------------------------------------------------------------- 5 2.2 抢答器的原理------------------------------------------------------------------------------------------- 5 2.2.1 原理框图---------------------------------------------------------------------------------------------- 6 2.3 功能模块电路------------------------------------------------------------------------------------------- 6 2.3.1 晶振复位及开始抢答电路------------------------------------------------------------------------ 6 2.3.2 选手抢答键(矩阵式键盘)--------------------------------------------------------------------- 8 2.3.3.显示与显示驱动电路------------------------------------------------------------------------------ 8 2.3.4 蜂鸣器音频输出电路------------------------------------------------------------------------------ 9 第3章软件设计---------------------------------------------------------------------------------------- 10 3.1程序设计-------------------------------------------------------------------------------------------------- 10 3.1.1 系统流程图------------------------------------------------------------------------------------------- 10 3.1.2 显示抢答违规流程图------------------------------------------------- 10 3.1.3 抢答成功流程图----------------------------------------------------- 10 第4章系统调试-------------------------------------------------------- 11第5章总结------------------------------------------------------------ 11附录一程序代码---------------------------------------------------------- 12 附录二仿真电路原理图---------------------------------------------------- 16参考文献----------------------------------------------------------------- 16·引言随着电子技术的飞速发展,基于单片机的控制系统已经广泛应用于工业、农业、电力、电子、智能楼宇等行业。

(附汇编语言源码)基于89C51的8路抢答器

《微机原理》课程项目实施报告题目:基于89C51的8路抢答器二零二年六月十五日摘要现如今电视节目日益丰富其中的竞赛环节也越来越多,其中智力抢答器是不可或缺的器材。

采本次课程设计,我们设计了一种以单片机AT89C51为核心的八路抢答器,与晶振、数码管、蜂鸣器等构成八路抢答器,利用了单片机的延时电路、按键复位电路、时钟电路、定时/中断等电路,设计的八路抢答器具有实时显示抢答选手的号码和抢答时间的特点,还有复位电路,使其再开始新的一轮的答题和比赛,同时还利用汇编语言编程,使其实现一些基本的功能。

通过Proteus软件仿真,仿真结果表明,该抢答器的设计实现了预期的目标。

关键词:89C51,抢答器,proteus仿真,汇编语言目录第一章项目概述 (3)1.1项目要求 (3)1.2 项目软件 (3)1.3 功能实现 (3)1.4 所需器件清单 (3)第二章硬件模块设计 (4)2.1 系统框图 (4)2.2 系统硬件 (4)2.2.1 A T89C51介绍 (4)2.2.2 A T89C51引脚功能说明 (5)2.2.3 电源电路 (6)2.3 时钟频率 (7)2.4 复位电路 (7)2.5 显示模块 (8)2.6 键盘扫描电路 (9)2.6.1 抢答键盘 (9)2.6.2 主持人按键 (9)2.7 报警电路 (10)第三章软件设计 (11)3.1 主程序流程 (11)3.2 抢答器的软件设计 (12)3.3程序分析总结 (12)第四章系统调试与仿真结果 (13)4.1 软件调试 (13)4.2 系统仿真结果 (13)项目分工............................................................................................................... 错误!未定义书签。

参考文献 (15)附件主程序 (16)第一章项目概述1.1项目要求(1)构建proteus 仿真平台:包含抢答输入+串口+数码管;(2)通过串口设置计时器的开始,并把抢答结果通过串口输出;(3)数码管输出抢答结果+组号;(4)比赛结束,能发出报警声。

基于单片机的八路智能抢答器的设计_毕业设计

The intelligent vies to answer first as a kind of electronic products have been widely applied in all kinds of intelligence and knowledge competition situation. But using the current is some complicated circuit vies to answer first, do not facilitate production, and reliability, low difficult to achieve; Others use some special integrated chips, and the purchase of the special integrated chips and very difficult. In order to adapt to the needs of the many players vies to answer first activities and design a intelligent vies to answer first device, this vies to answer first instruments have circuit is simple, components, easy to buy ordinary etc, and solves the difficult and hard to buy makers make the problem. This system is AT89C51 microcontroller as the core and the design of the intelligent vies to answer first 8.

基于AT89C51的八路抢答器

电子综合设计实验报告题目综合电子技术8路抢答器学生姓名学号系部计算机与信息工程系专业班级指导教师职称年月电子综合设计实验报告评审表姓名专业班级学号题目:8路抢答器评审意见成绩签名:评审时间:年月日内容摘要随着科学技术的发展和普及,各种各样的竞赛越来越多,其中抢答器的作用也越来越重要。

本文设计出以AT89C51单片机为核心的八路抢答器,采用了数字显示器直接指示,自动锁存显示结果,并自动复位的设计思想,它能根据不同的抢答输入信号,经过单片机的控制处理并产生不同的与输入信号相对应的输出信号,最后通过LED数码管显示相应的路数,即使两组的抢答时间相差几微秒,也可分辨出是哪组优先按下的按键,充分利用了单片机系统结构简单、功能强大、可靠性好、实用性强的特点。

本设计是以抢答为出发点。

考虑到依需设定限时回答的功能,利用89C51单片机及外围接口实现的抢答系统,利用单片机的定时器/计数器定时和记数的原理,将软、硬件有机地结合起来,使得系统能够正确地进行计时,同时使数码管能够正确地显示时间。

用开关做键盘输出,扬声器发生提示。

同时系统能够实现:在抢答中,只有开始后抢答才有效,如果在开始抢答前抢答为无效;满时后系统计时自动复位及主控强制复位;按键锁定,在有效状态下,按键无效非法,定时功能,计分功能等。

关键词抢答器;单片机;LED数码显示管;定时器/计数器;扬声器。

ABSTRACTWith the development and popularization of science and technology , more and more kinds of competitions , including Responder role has become increasingly important . This paper designed to AT89C51 microcontroller as the core of eight Responder , using a direct digital display indicator, automatic latching display the results, and automatically resets design ideas that can answer depending on the input signal, after the MCU control processing and produce different with the input signal corresponding to the output signal , and finally through the LED digital tube display the corresponding ones , even if the difference in time between the two groups to answer in a few microseconds , which can distinguish the pressed key priority groups , taking advantage of SCM system structure is simple , powerful, good reliability, practical features .The design is based on Responder as a starting point . By taking into account the need to set the limit to answer function, using 89C51 microcontroller and peripheral interface Responder system, using single-chip timer / counter timing and counting principle, the software and hardware organically combined , making the system can correctly for a time, while enabling digital tube display time correctly . Keyboard to do with the switch output , speakers from tips. While the system can be achieved : In the answer , the only answer is only valid after the start , if before the start Responder Responder as invalid ; full, the system automatically resets and Master Chronograph forced reset ; keys locked in the active state , the button is not illegal , timing , scoring functions.KEY WORDSResponder ;chip ;LED digital display ;tube timer ;counter Speaker目录1 设计任务要求 (1)1.1 设计任务 (1)1.2 设计要求 (1)2 方案论证与选择 (2)3 理论分析与计算 (3)4 单元电路设计 (5)4.1 主要电路设计 (5)4.1.1 输入模块设计 (5)4.1.2 单片机模块 (6)4.1.3 显示模块 (7)4.1.4 声音模块 (8)4.2 软件设计 (8)4.2.1 主程序设计 (8)4.2.2 定时器设计 (10)5 仿真分析 (11)5.1 Proteus 软件 (11)5.2 调试过程 (11)6 设计总结 (16)6.1 心得体会 (16)6.2 实践总结 (16)参考文献 (17)附录 (18)8路抢答器1.设计任务与要求1.1设计任务设计能独立显示得分和组别的8路抢答器;且在主持人显示屏上能显示答题时间、答题的分值、抢答和犯规组别。

20240710 基于51单片机的八路抢答器课程设计

基于51单片机的八路抢答器课程设计设计题目:八路抢答器系别:班级:设计学生:指导老师:设计时间:摘要针对课程设计要求设计一款八路抢答器。

利用AT89C51单片机为核心器件以及数码管、蜂鸣器、按键等外围器件作为硬件基础以及结合软件开发实现八路抢答器的课程设计。

本课程设计的与用户交互的为12个按键、一个4位数码管和一个蜂鸣器。

12个按键分别为“确认键”、“返回键”“UP键”“DOWN键”和8个选手键S1~S8。

上电后为初试状态显示“0 00”,短按确认键蜂鸣器滴一声后进入答题倒计时,显示“0 抢答倒计时”。

在倒计时归零之前选手S1~S8可以抢答,有选手抢答成功后滴一声后显示“选手号答题倒计时”。

若抢答倒计时小于5s则蜂鸣器滴滴报警,若抢答倒计时归零无人抢答则返回初试状态。

在答题倒计时过程中若选手答题完成,主持人可按返回键结束本轮答题,并等待主此人下一次按下确认键盘。

在初试状态下主持人长按确认键3s以上进入参数设置状态,可设置抢答倒计时初始值,显示“A 抢答倒计时初始值”,可通过UP或DOWN对参数进行修改。

为避免程序溢出,设置范围为5~99。

再次长按长按确认键3s以上可设置答题倒计时初始值,显示“V 抢答倒计时初始值”。

可通过UP或DOWN对参数进行修改。

为避免程序溢出,设置范围为5~99。

按下返回键,进入初始状态。

经过总体方案设计、原理图绘制、PCB板绘制、程序编写并通过proteus软件进行软硬件仿真。

仿真结果表明了本设计的有效性。

目录摘要 (2)第1章总体方案设计 (4)设计任务与要求 (4)方案设计 (4)器件选择方案 (5)第2章硬件设计与原理 (6)原理图设计 (6)2.1.1 时钟电路 (6)2.1.2 复位电路 (7)2.1.3 显示电路 (7)2.1.4 报警电路 (8)2.1.5 外部电源 (8)2.1.6 键盘输入 (8)2.1.7 主控制器件 (9)PCB设计 (9)第3章软件设计 (11)系统主程序设计 (11)主程序清单 (12)第4章软件仿真 (21)PROTEUS 简介 (21)仿真图 (22)第5章总结 (23)第1章总体方案设计设计任务与要求1.抢答器可同时供8名选手或8个代表队比赛,分别用8个按键S1~S8进行抢答。

基于AT89C51的八路抢答器方案设计书

基于A T89C51的八路抢答器设计班级08(4)学号0810425学生姓名张锋学院名称物理机电工程学院专业名称电子信息技术指导教师董安明2010年05月20日目录1 绪论1目的与意义2 系统概述2.1 系统的主要功能2.2 抢答器的工作流程2.3 抢答器的工作过程2.4 器件的选择3 系统总体方案的设计3.1 硬件原理图3.2 显示电路的设计3.3 键盘扫描电路的设计3.4 发声电路的设计4 软件设计4.1 设计思想4.2 方案实现结论附录1 绪论1.1目的与意义通过这次设计,掌握51单片机的原理,了解简单多功能抢答器组成原理,初步掌握多功能抢答器的调整及测试方法,提高动手能力和排除故障的能力。

同时通过本课题设计与装配、调试,提高自己的动手能力,巩固已学的理论知识,建立单片机理论和实践的结合,了解多功能抢答器各单元电路之间的关系及相互影响,从而能正确设计、计算定时计数的各个单元电路。

初步掌握多功能抢答器的调整及测试方法。

提高动手能力和排除故障的能力。

2 系统概述2.1 系统的主要功能本系统是借用单片机采用模块化设计的八路抢答器,包括8路抢答按纽、计时显示、提示功能等(根据需要可另设或多设相关功能)、开始与结束控制按钮、时限设定、各种相关显示调控功能等(根据需要也可另设或多设相关功能)。

参赛者系统,除享有抢答按纽的权利功能外,还有人性化的提示功能和时间提示功能,也可设定由主控控制在参赛者终端表现的趣味性功能等;主控系统的控制按钮做开始与结束控制,根据活动参赛者的层次,对提前抡答者的行为设定为非法或阻隔,若设有非法抢答控制功能时,在主控处带有公示性显示的非法抡答者的台位号,对抢答限时及回答问题限时设为倒计时,并有显示提示。

系统的主要功能模块方框图如图2-1所示。

图2-1 系统主要功能模块本系统采用模块化设计的八路抢答器,在抢答比赛中广泛应用,各组分别有一个抢答按钮。

一共有8个按键输入,分别对应8路选手的抢答按键。

八路智能抢答器的设计 单片机毕业设计外文翻译 单片机AT89C51

AT89C51Features• Compatible with MCS-51™ Products• 4K Bytes of In-System Reprogrammable Flash Memory• Endurance: 1,000 Write/Erase Cycles• Fully Static Operation: 0 Hz to 24 MHz• Three-level Program Memory Lock• 128 x 8-bit Internal RAM• 32 Programmable I/O Lines• Two 16-bit Timer/Counters• Six Interrupt Sources• Programmable Serial Channel• Low-power Idle and Power-down ModesDescriptionThe AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4Kbytes of Flash programmable and erasable read only memory (PEROM). The deviceis manufactured using Atmel’s high-density nonvolatile memory technology and iscompatible with the industry-standard MCS-51 instruction set and pinout. The on-chipFlash allows the program memory to be reprogrammed in-system or by a conventionalnonvolatile memory programmer. By combining a versatile 8-bit CPU with Flashon a monolithic chip, the Atmel AT89C51 is a powerful microcomputer which providesa highly-flexible and cost-effective solution to many embedded control applications.The AT89C51 provides the following standard features: 4Kbytes of Flash, 128 bytes of RAM, 32 I/O lines, two 16-bittimer/counters, a five vector two-level interrupt architecture,a full duplex serial port, on-chip oscillator and clock circuitry.In addition, the AT89C51 is designed with static logicfor operation down to zero frequency and supports twosoftware selectable power saving modes. The Idle Modestops the CPU while allowing the RAM, timer/counters,serial port and interrupt system to continue functioning. ThePower-down Mode saves the RAM contents but freezesthe oscillator disabling all other chip functions until the nexthardware reset.八路智能抢答器的设计Pin ConfigurationsPin DescriptionVCC:Supply voltage.GND:Ground.Port 0:Port 0 is an 8-bit open-drain bi-directional I/O port. As anoutput port, each pin can sink eight TTL inputs. When 1sare written to port 0 pins, the pins can be used as highimpedanceinputs.Port 0 may also be configured to be the multiplexed loworderaddress/data bus during accesses to external programand data memory. In this mode P0 has internalpullups.Port 0 also receives the code bytes during Flash programming,and outputs the code bytes during programverification. External pullups are required during program verification.Port 1:Port 1 is an 8-bit bi-directional I/O port with internal pullups.The Port 1 output buffers can sink/source four TTL inputs.When 1s are written to Port 1 pins they are pulled high bythe internal pullups and can be used as inputs. As inputs,Port 1 pins that are externallybeing pulled low will source current (IIL) because of the internal pullups.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bi-directional I/O port with internal pullups.The Port 2 output buffers can sink/source four TTL inputs.When 1s are written to Port 2 pins they are pulled high by the internal pullups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3:Port 3 is an 8-bit bi-directional I/O port with internal pullups.The Port 3 output buffers can sink/source four TTL inputs.When 1s are written to Port 3 pins they are pulled high by the internal pullups and can be used as inputs. As inputs,Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of the AT89C51 as listed below:Port 3 also receives some control signals for Flash programmingand verification.ALE/PROG:Address Latch Enable output pulse for latching the low byte of the address八路智能抢答器的设计during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation ALE is emitted at a constant rate of 1/6the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has no effect if the microcontroller is in external execution mode.PSEN:Program Store Enable is the read strobe to external program memory.When the AT89C51 is executing code from external programmemory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000H up to FFFFH.Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset. EA should be strapped to VCC for internal program executions. This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming, for parts that require 12-volt VPP.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2:Output from the inverting oscillator amplifier.Oscillator CharacteristicsXTAL1 and XTAL2 are the input and output, respectively,of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.Idle ModeIn idle mode, the CPU puts itself to sleep while all the onchip peripherals remain active.The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset. It should be noted that when idle is terminated by a hard ware reset, the device normally resumes program execution,from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.Figure 1. Oscillator ConnectionsFigure 2. External Clock Drive Configuration八路智能抢答器的设计Power-down ModeIn the power-down mode, the oscillator is stopped, and the instruction that invokes power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the power-down mode is terminated. The only exit from power-down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before VCC is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.Program Memory Lock BitsOn the chip are three lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in the table below.When lock bit 1 is programmed, the logic level at the EA pin is sampled and latched during reset. If the device is powered up without a reset, the latch initializes to a random value, and holds that value until reset is activated. It is necessary that the latched value of EA be in agreement with the current logic level at that pin in order for the device to function properly.Programming the FlashThe AT89C51 is normally shipped with the on-chip Flash memory array in the erased state (that is, contents = FFH) and ready to be programmed. The programming interface accepts either a high-voltage (12-volt) or a low-voltage (VCC) program enable signal. The low-voltage programming mode provides a convenient way to program the AT89C51 inside the user’s system, while the high-voltage programming mode is compatible with conventionalthirdparty Flash or EPROM programmers. The AT89C51 is shipped with either the high-voltage or low-voltage programming mode enabled.The AT89C51 code memory array is programmed byte-bybyte in either programming mode. To program any nonblank byte in the on-chip Flash Memory, the entire memory must be erased using the Chip Erase Mode.八路智能抢答器的设计AT89C51主要性能参数:●与MCS-51产品指令系统完全兼容●4K字节可重檫写Flash闪速存储器●1000次檫写周期●全静态操作:0HZ-24MHZ●三级加密程序存储器●128*8字节内部RAM●32个可编程I/O口线●2个16位定时/记数器●6个中断源●可编程串行UART通道●低功耗空闲和掉电模式功能特性概述:AT89C51提供以下标准功能:4K字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/记数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

单片机课设 AT89C51八路抢答器

单片机课程设计任务书1.课题名称抢答器设计2.设计目的1.进一步理解和掌握单片机理论课程知识,加强对专业知识的合运用;2.学会熟练使用单片机编程工具软件及单片机软件编程;3.学习单片机小系统的硬件设计及PCB布线。

4.学会如何整理资料,划分模块,提高自己的编程技巧;3.设计思路a.了解抢答器的工作方式;b.单片机按键输入的设计;c.单片机驱动发光二极管显示及数码管的动态扫描工作方式;d.延时子程序设计;e.定时器的应用;4.设计要求1.在本设计中要求设计一个八组单片机控制的抢答器模拟器;2.要求由两个LED(红绿)指示抢答成功或失败;3.要求由1位数码管显示抢答成功(或失败)的组;4.发挥部分:剩余时间显示,各组积分显示;5.课程设计结束后,要求交设计心得,课程设计报告;目录第一章概述 (1)第二章八路抢答器设计方案及选取 (2)2.1电路设计方案一 (2)2.2电路设计方案二 (2)2.3电路设计方案的选取 (2)第三章电路设计原理及硬件设计 (3)3.1单片机最小系统的原理 (3)3.2八路抢答器工作原理 (4)3.3控制系统及所需元件 (5)第四章软件系统设计及仿真 (7)4.1软件系统设计 (7)4.2电路仿真 (8)第五章电路板制作与调试 (9)5.1电路板制作 (9)5.2电路调试 (9)第六章心得体会 (11)第七章参考文献 (12)鸣谢 (12)附录一源程序 (13)第一章概述《单片机原理及应用技术》是一门技术性,应用性、实践性很强的学科。

课程设计是学好本门课程的又一重要实践性教学环节,课程设计的目的和任务就是配合单片机的教学和平时实验,以达到巩固消化课程的内容,进一步加强综合应用能力及单片机应用系统开发和设计能力的训练,启发创新思维,使之具有独立单片机产品和科研的基本技能,是以培养学生综合运用所学知识的过程,是知识转化为能力和能力转化为工程素质的重要阶段。

在实际生活中有好多地方都用到了单片机,因此学习好这门课程有着十分重要的意义。

毕业设计-基于AT89C51单片机的八位智力抢答器设计

八位智力抢答器摘要能够实现抢答器功能的方式有多种,可以采用前期的模拟电路、数字电路或模拟与数字电路相结合的方式。

近年来随着科技的飞速发展,单片机的应用正在不断深入,同时带动传统控制检测日新月异更新。

本文介绍一种用AT89C51作为核心部件进行逻辑控制及信号产生的单片机技术和汇编语言编程设计的8路数字抢答器。

文章对抢答器的背景与现状、硬件设计、软件设计及其仿真都做了详细的介绍,使我们不仅答器的原理及设计有了深入的了解,也对单片机的设计研发过程有了更加深刻的体会本设计主要采用单片机控制,采用手动抢答的方式,有人抢答后,系统自动封锁其他人的抢答按钮,使其不能再抢答,从而实现抢答功能。

该系统还增加了抢答倒计时和答题倒计时功能,另外抢答倒计时和答题倒计时的时间都可以调整。

若有人在主持人按下开始按钮之前按下抢答按钮,系统自动视其为犯规,抢答器自动报警,显示器同时显示犯规选手的号码,使抢答达到公平、公开的效果。

关键字:单片机;抢答器;倒计时作者:指导老师:ABSTRACTResponder function can be achieved in different ways, can be used early in the analog circuits, digital circuits or analog and digital circuit combination. With the rapid development of science and technology in recent years, SCM applications are deepening, while the traditional control test drive rapid updated. This paper introduces a core component with AT89C51 as logical control signals and single-chip microcomputer and assembly language programming design of 8 digital vies to answer first. Article on the Responder's background and present, hardware design, software design and simulation have made a detailed introduction, so we not only answer the principle and design of devices with in-depth understanding of microcontroller design and development and also have a more profound experience. This design mainly uses the MCU control, with manual answer in the way, some people answer in, the system automatically block other people's answer in the button, so that it can not answer in order to achieve Responder feature.The system also increased the answer in the countdown countdown and answer features, and answer another answer in the countdown to the countdown time can be adjusted. If one host press the start button before pressing the answer in the button, the system automatically view them as foul, Responder automatic alarm, the display also shows the number of fouls players to answer in a fair, open effect.Keywords : single chip ;viing to answer first ;count downAuthor:GuidingTeacher:目录第1章绪论 (1)1.1课题研究的背景及意义 (1)1.2抢答器的分类 (1)1.3设计的主要目标任务 (3)第2章总体方案的设计 (4)2.1 功能要求 (4)2.2 系统功能框图 (4)第3章硬件电路的设计 (5)3.1 硬件主要组成电路 (5)3.2 电路工作的基本原理 (5)3.3主控电路的设计 (5)3.3.1 关于AT89C51单片机 (5)3.3.2振荡器电路的设计 (6)3.3.3复位电路的设计 (7)3.4 按键电路的设计 (8)3.5 显示电路的设计 (8)3.5.1 LED显示器件简介 (8)3.5.2 显示部分的设计 (9)3.6报警电路的设计 (9)3.6.1蜂鸣器的介绍 (9)3.6.2 报警电路 (10)3.7 总电路图 (11)第4章软件的设计 (12)4.1 语言选择 (12)4.2 软件总体设计 (12)4.3系统程序 (13)第5章仿真及调试 (23)5.1 仿真软件介绍 (23)5.1.1 Proteus软件介绍 (23)5.1.2 keil软件介绍 (23)5.2 仿真过程 (23)5.2.1仿真过程操作如下: (23)5.2.2 仿真结果: (24)第六章总结 (26)参考文献 (27)附录 (28)附录1 电路原理图 (28)第1章绪论1.1课题研究的背景及意义无论是学校、工厂、军队还是益智性电视节目,都会举办各种各样的智力竞赛,都会用到抢答器。

基于单片机AT89C51控制的抢答器_课题设计报告

宁波技师学院课程设计报告论文题目抢答器摘要:在日常生活中,我们可以在电视,或者现实生活活动现场可以看到在答题或者游戏中,他总能第一时间测到谁是第一个,让我们的世界少了那些不必要的争议,那是什么,那就是抢答器。

通过一次又一次科学的进步,单片机在发展,各种功能运用到现实生活的各种领域让我们生活更加的接近理想话以及通过简单的操作完成手工无法完成或者很难做到的事情,例如家电,通信,商业,工业,航空,航天,军事以及汽车方面。

当然这次我们做的是其中的一种那就是抢答器,它具有很高的安全性、可靠性,准确性,应用日益广泛。

随着人们经济生活的发展以及生活条件的上去,大家都希望生活在一个无争议的日子里,那么科学就努力的去完成它,这次的抢答器就是一个很好的反馈以及显示更加直观的展现在大家的眼前。

基于以上思路,本次设计使用 ATMEL公司的 AT89C51 实现一基于单片机的抢答器设计,其主要具有如下功能:(1)抢答时间调试,限时时间调试这两个功能都是要在最开始时调试。

可以改变调试抢答时间和限时时间。

(2)声光报警系统。

抢答时间倒计时时会报警闪烁,以及蜂鸣器报警还有时间提示。

(3)锁定功能。

为了很好的在第一时间锁定第一位,抢答器做了很好的反馈功能,为此能够更加精确的锁定反馈第一位抢答器是由一个AT89C51、输出八段显示电路。

另外系统还有 LED 提示灯,报警蜂鸣器等。

抢答器的功能在于反馈以及最快的时间做出选择:(1)限时时间调试·抢答时间调试功能:这是一个十分人性化的设计,他可以在不同的场合用不同的时间来限定抢答以及限时时间的调试。

(2)抢答锁定功能:当按下抢答键时,抢答器会判断第一个抢答的以及显示抢答人的编号。

(3)报警系统:当抢答倒计时到5秒时开始二极管开始闪烁报警蜂鸣器开始鸣叫。

主要的设计实施过程:首先,选用 ATMEL公司的单片机 AT89C51,以及选购其他电子元器件。

第二步,使用Protel设计硬件电路原理图,并设计 PCB图完成人工布线。

基于AT89C51单片机八位抢答器的设计

基于AT89C51单片机八位抢答器的设计一、本文概述随着电子技术的不断发展,单片机作为微型计算机的重要分支,已广泛应用于各种智能控制系统中。

AT89C51作为一款经典的8位单片机,以其高性能、低功耗、易编程等特点,在嵌入式系统设计中占据了重要地位。

本文旨在探讨基于AT89C51单片机的八位抢答器设计,通过分析其硬件组成、软件设计以及工作原理,为相关领域的开发人员提供一种实用的设计方案。

本文首先介绍了抢答器的应用场景和基本要求,随后详细阐述了AT89C51单片机的核心特性及其在系统中的作用。

接着,文章将重点介绍抢答器的硬件电路设计,包括按键输入电路、显示电路、声音提示电路等关键模块。

在软件设计方面,文章将给出抢答器程序的主要流程,包括按键扫描、状态判断、结果显示等功能模块的实现方法。

文章还将对抢答器的性能进行测试和分析,以确保其在实际应用中的稳定性和可靠性。

通过本文的研究,读者可以深入了解基于AT89C51单片机的八位抢答器的设计过程,掌握相关电子技术和编程技巧,为未来的嵌入式系统开发打下坚实基础。

本文的研究成果也可为类似系统的设计提供有益的参考和借鉴。

二、AT89C51单片机简介AT89C51是Atmel公司生产的一款低功耗、高性能的8位CMOS微控制器,它采用了Atmel公司的高密度、非易失性存储技术,并且与工业标准的8051指令集和输出管脚相兼容。

AT89C51单片机内部集成了4KB的可编程Flash闪烁存储器,这为用户提供了足够大的空间进行程序编写和存储。

它还拥有128字节的内部RAM、32个可编程的I/O口线、两个16位定时/计数器、一个5向量两级中断结构、一个全双工串行通信口、以及片内振荡器和时钟电路。

AT89C51单片机具有低功耗的空闲模式和掉电模式,使其在便携式产品和电池供电的应用中具有显著的优势。

其强大的功能集和灵活的编程能力使得AT89C51单片机在各种控制系统中得到了广泛的应用,包括抢答器设计、智能家居、工业自动化、医疗设备、安全系统等。

基于AT89C51的智能抢答与表决计时器的设计与实现

(题目):基于AT89C51的智能抢答与表决计时器的设计与实现摘要本设计是以八路抢答为基本思想。

按照单片机AT89C51的定时和记数的道理,利用单片机AT89C51的优点,熟练地将硬件与软件结合起来。

最终使系统可以实现:由主持人控制抢答开关,选手只有在抢答开始后抢答才被视为有效,在开始前抢答则被认定为违规。

抢答时间和回答问题的时间,采用倒记时显示,倒计时为0后系统计时自动复位,禁止选手超时抢答。

能够显示有效抢答和违规抢答的选手,正确按键后有声音提示,违规抢答时会报警。

关键词:单片机八路抢答器AT89C51毕业设计(论文)外文摘要Title : Design and implementation of intelligent answering and voting timer based on AT89C5 1Abstract: The design is based on eight vies for basic ideas. The use of single-chip timer / co unter timing and counting principle, the software and hardware organically and makes the system can be realized: in the answer, only after the answer is valid, if at the beginning of pre answer answer is invalid; can show who's effect and answer answer invalid, the right button is the voice prompt answer in time and answer questions; time countdown display, full automatic reset after t he system timing and control forced reset; key lock in the effective state, the key is invalid.keywords: SCM Eight way responder AT89C51目录目录1. 绪论 (4)1.1 背景 (4)1.2 目的与意义 (4)2.总体设计 (5)2.1 功能介绍 (5)2.2抢答器的工作原理 (6)3. 硬件电路设计 (7)3.1原理图的设计 (7)3.2抢答器电路 (8)3.3时序控制电路设计 (8)3.4复位电路的设计 (8)3.5 晶振电路的设计 (9)3.6 报警电路设计 (9)3.7选手抢答键的设计 (10)4. 软件设计 (11)4.1系统主程序设计 (11)4.2 显示抢答违规流程图 (13)4.3 抢答成功流程图 (14)4.4 程序清单 (14)5.仿真调试 (14)6 表决器的设计 (16)6.1 设计说明 (16)6.2 电路原理图设计 (16)6.3 程序的设计 (16)总结 (17)致谢 (17)参考文献 (18)附录一 (19)附录二 (19)1. 绪论1.1 背景随着科学技术的发展与进步,智能抢答器已经深深地融入到我们的生活之中。

AT89C51单片机八路抢答器

摘要抢答器是为智力竞赛参赛者答题时进行抢答而设计的一种优先判决器电路,广泛应用于各种知识竞赛、文娱活动等场合。

以前的抢答器大部分都是基于数字电路组成的,制作过程复杂,而且准确性与可靠性不高,成品面积大,安装、维护困难。

随着电子技术的发展,现在的抢答器功能越来越强,可靠性和准确性也越来越高。

能够实现抢答器功能的方式有多种,可以采用前期的模拟电路、数字电路或模拟与数字电路相结合的方式,但这种方式制作过程复杂,而且准确性与可靠性不高,成品面积大。

对于目前抢答器的功能描述,如涵盖抢答器、抢答限时、选手答题计时及犯规组号抢答器具有抢答自锁,灯光指示、暂停复位、电子音乐报声、自动定时等功能,还有工作模式的切换和时间设定,对于这些,随着科学技术的发展,肯定还要得到进一步的改进。

一般都要趋向于智能化。

在各类竞赛中,特别是做抢答题时,在抢答过程中,为了知道哪一组或哪一名选手先答题,必须要有一个系统来完成这个任务。

如果在抢答过程中,只靠人的视觉是很难判断出哪组先答题。

利用单片机来设计抢答器,使以上问题得以解决,即使有两组的抢答时间相差几微秒,也可分辨出哪组优先答题。

抢答器是一种应用非常广泛的设备,在各种竞赛、抢答场合中,它能迅速、客观地分辨出最先获得发言权的选手。

早期的抢答器只由几个三极管、可控硅、发光管等组成,能通过发光管的指示辨认出选手号码。

本文是以AT89C51单片机为核心的八路抢答器,可以满足最多8组选手进行抢答,利用单片机最小系统设计及单片机键盘输入实现,根据不同的抢答输入信号,经过单片机的控制处理并产生不同的与输入信号相对应的输出信号,同时通过数码管显示相应组号。

控制系统包括抢答电路,显示电路和报警电路。

关键字:单片机抢答显示报警一、设计目的通过基于AT89C51单片机实现八路抢答器的设计实验,要求学生回顾所学单片机原理,掌握利用PROTUSS,掌握利用软件进行程序设计并调试,将程序拷入单片机中控制电路实现八路抢答。

单片机控制的八路抢答器设计

教学研究单片机控制的八路抢答器设计■ 文/甘肃工业职业技术学院 高皑琼 摘要:本文介绍了以AT89C51单片机为核心器件的八路抢答器系统。

通过软件仿真和硬件实现的结果表明该系统实现了八路选手抢答,并具有限时抢答、限时答题、报警显示等功能。

由于本系统采用单片机控制,因此电路简单、易于实现且性能稳定,具有一定的实用性。

关键词:八路抢答器 单片机 定时中断 随着科技的发展,在各类知识竞赛中,特别是抢答环节,抢答器的使用越来越普遍,因此设计一款操作简单、区分度高的抢答器具有一定的现实意义。

但现在很多的抢答器还采用小规模数字集成电路来实现,使用起来很不理想。

目前在很多智能控制领域,单片机的使用非常普及,以其功耗小、智能化而著称,所以本设计基于单片机控制,因而具有结构小、反应快、实用性强等特点。

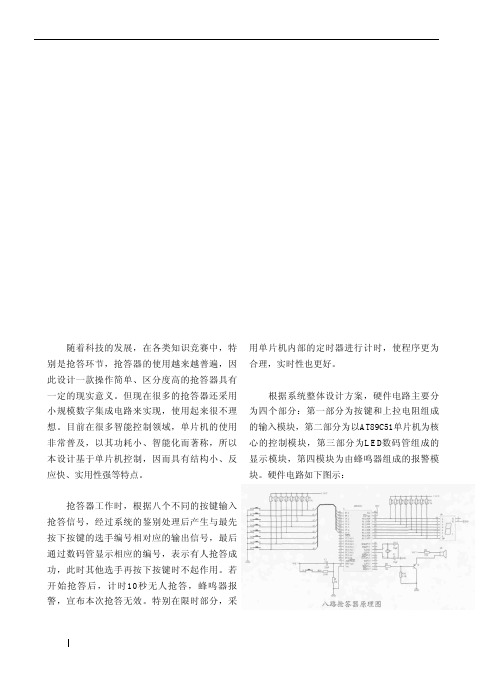

一、功能设计 抢答器工作时,根据八个不同的按键输入抢答信号,经过系统的鉴别处理后产生与最先按下按键的选手编号相对应的输出信号,最后通过数码管显示相应的编号,表示有人抢答成功,此时其他选手再按下按键时不起作用。

若开始抢答后,计时10秒无人抢答,蜂鸣器报警,宣布本次抢答无效。

特别在限时部分,采用单片机内部的定时器进行计时,使程序更为合理,实时性也更好。

二、硬件电路 根据系统整体设计方案,硬件电路主要分为四个部分:第一部分为按键和上拉电阻组成的输入模块,第二部分为以A T89C51单片机为核心的控制模块,第三部分为L E D数码管组成的显示模块,第四模块为由蜂鸣器组成的报警模块。

硬件电路如下图示:八路抢答器原理图教学研究三、软件设计 1.流程图 主程序 中断程序 2.程序 ORG 0000H AJMP MAIN ORG 000BH AJMP JT0 MAIN:NOP;初始化 MOV SP,#40H MOV 30H,#3 MOV 60H,#20 MOV R0,#00H MOV P1,#0FFH MOV P0,#00H MOV R5,#200 MOV TMOD,#01H MOV TH0,#3CH MOV TL0,#0B0H SETB TR0 SETB ET0 SETB EA BB:JNB P1.0,KE0;键盘扫描 JNB P1.1,KE1 JNB P1.2,KE2 JNB P1.3,KE3 JNB P1.4,KE4 JNB P1.5,KE5 JNB P1.6,KE6 JNB P1.7,KE7 CJNE R0,#00H,JS AJMP BB KE0:CLR EA;关中断送组号 CLR TR0 MOV R1,#00H LJMP SH KE1:CLR EA CLR TR0 MOV R1,#01H LJMP SH KE2:CLR EA CLR TR0 MOV R1,#02H LJMP SH KE3:CLR EA CLR TR0 MOV R1,#03H LJMP SH KE4:CLR EA CLR TR0 MOV R1,#04H LJMP SH KE5:CLR EA CLR TR0 MOV R1,#05H LJMP SH KE6:CLR EA CLR TR0 MOV R1,#06H LJMP SH KE7:CLR EA CLR TR0 MOV R1,#07H LJMP SH SH:MOV A,R1 MOV DPTR,#TABLE MOVC A,@A+DPTR;查表 MOV P0,A;显示组号 AA: LCALL YS1 DJNZ 0H,AA;延时3秒 LJMP MAIN JT0:NOP;中断服务子程序 CLR EA PUSH 02H PUSH 03H PUSH 04H PUSH 06H PUSH 07H DJNZ R5,RRT BJ:SETB P3.6;喇叭驱动 LCALL YS50;延时50m秒 CLR P3.6 LCALL YS50 DJNZ 60H,BJ MOV P1,#0FFH MOV R0,#10 RRT:MOV TH0,#3CH MOV TL0,#0B0H POP 07H POP 06H POP 04H POP 03H POP 02H SETB EA RETI YS1:MOV R4,#2;延时1s子程序 L0:MOV R3,#200 L1:MOV R2,#250 L2:NOP NOP DJNZ R2,L2 DJNZ R3,L1 DJNZ R4,L0 RET YS50:MOV R6,#99;延时50m秒 L50:MOV R7,#124 L5:NOP NOP DJNZ R7,L5 NOP NOP DJNZ R6,L50 NOP NOP NOP RET JS:NOP TABLE:DB 06H,5BH,4FH,66H;段码表 DB 6DH,7DH,07H,7FH END四、结论 本文以A T89C51单片机为核心设计了八路抢答器系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要

抢答器是为智力竞赛参赛者答题时进行抢答而设计的一种优先判决器电路,广泛应用于各种知识竞赛、文娱活动等场合。

以前的抢答器大部分都是基于数字电路组成的,制作过程复杂,而且准确性与可靠性不高,成品面积大,安装、维护困难。

随着电子技术的发展,现在的抢答器功能越来越强,可靠性和准确性也越来越高。

能够实现抢答器功能的方式有多种,可以采用前期的模拟电路、数字电路或模拟与数字电路相结合的方式,但这种方式制作过程复杂,而且准确性与可靠性不高,成品面积大。

对于目前抢答器的功能描述,如涵盖抢答器、抢答限时、选手答题计时及犯规组号抢答器具有抢答自锁,灯光指示、暂停复位、电子音乐报声、自动定时等功能,还有工作模式的切换和时间设定,对于这些,随着科学技术的发展,肯定还要得到进一步的改进。

一般都要趋向于智能化。

在各类竞赛中,特别是做抢答题时,在抢答过程中,为了知道哪一组或哪一名选手先答题,必须要有一个系统来完成这个任务。

如果在抢答过程中,只靠人的视觉是很难判断出哪组先答题。

利用单片机来设计抢答器,使以上问题得以解决,即使有两组的抢答时间相差几微秒,也可分辨出哪组优先答题。

抢答器是一种应用非常广泛的设备,在各种竞赛、抢答场合中,它能迅速、客观地分辨出最先获得发言权的选手。

早期的抢答器只由几个三极管、可控硅、发光管等组成,能通过发光管的指示辨认出选手号码。

本文是以AT89C51单片机为核心的八路抢答器,可以满足最多8组选手进行抢答,利用单片机最小系统设计及单片机键盘输入实现,根据不同的抢答输入信号,经过单片机的控制处理并产生不同的与输入信号相对应的输出信号,同时通过数码管显示相应组号。

控制系统包括抢答电路,显示电路和报警电路。

关键字:单片机抢答显示报警

一、设计目的

通过基于AT89C51单片机实现八路抢答器的设计实验,要求学生回顾所学单片机原理,掌握利用PROTUSS,掌握利用软件进行程序设计并调试,将程序拷入单片机中控制电路实现八路抢答。

同时锻炼动手能力,制作样板实现八路抢答器功能。

二、设计要求与内容

1、主要技术要求:

1、抢答器可同时供8名选手分别用8个按键S1-S8进行抢答

2、总开关和复位开关由主持人控制

3、抢答器具有显示和报警功能

2、完成形式:

1、设计与制作可供实际检测的实物样机。

2、完成课程设计报告。

三、设计方案与原理

3.1设计思路

1.课设根本任务是准确判断出抢答者的信号。

本设计选在得到信号之后应立即将电路的输入封锁,使其他组的抢答信号无效,并同时蜂鸣器发出警报。

同时还必须注意,抢答信号应该在主持人发出抢答命令之后才有效。

当电路形成抢答信号之后,用数码管显示电路显示出抢答者的组别。

3.2 总原理图及流程图

设计流程图

N

Y

N

N

Y

N

Y

3.3抢答电路

本电路的主要功能是实现八路抢答,本电路的主要器件是开关按钮,由8个开关按钮组成,可供最多8主选手抢答。

按照键盘与单片机的连接方式可分为独立式键盘与矩阵式键盘,所以本次设计采用的是独立式键盘。

如图3-2所示。

3-2抢答电路

上图是抢答器选手的按键端,自上往下分别是1号至八号选手,在没有选手按键是P0口的值全为高电平,在抢答开始时,最快的选手按下一个键后P0口的一个输入端为低电平,其他端口的值不能再改变。

开始 是否开始抢答 哪一个选手首先抢答 显示选手的号码 是否复位 关电源 结束

3.4显示电路及控制电路

本电路的主要功能是利用数码管显示抢答的组别,对于开关按钮输入信号输出相应组别,分别编号为1到8号。

本电路部分的主要器件是LED数码管。

在单片机系统中,LED数码管的驱动方式主要有动态显示和静态显示两种类型,每种类型的驱动电路各部相同。

由于显示电路只运用了一个数码管故采用静态显示方式。

本电路部分是利用两个按键来控制抢答,对抢答器的开始和复位进行控制。

如3-3所示。

图3-3

显示电路及控制电路的设计是采用8口输出做LED数码管的显示,另外再使用两个口作为控制位,一个是总的开关控制,另外一个是在抢答器工作以后,对抢答器的显示进行复位,如此可以进行下一次的比赛。

显示的输出是按照LED数码管的特性进行连接的,由于P2.0-P2.7分别是P2口的低位到高位,如此LED数码管自左往右一一对应P2口的低位到高位,查表可知显示1-8的阿拉伯数字对应的P2口的值。

输出数码管的设计是采用静态显示方式,如此往各个LED数码管所显示的段码一旦确定,则相应输出口的输出值也一样保持不变,直到传送下一个字符的段码为止,如此一来,静态显示的方式将无闪烁,亮度较高,软件控制比较容易。

四.设计结果及分析开启时模拟仿真图:

开启时实物运行图:

选手抢答模拟仿真图: 选手抢答实物运行图:

复位运行效果图:

抢答运行效果图:

在本次试验设计和制作的过程中,我们的团队先后遇到了各种困难,在我们细心的查阅相关资料和文献之后都一一克服,对此我们感到无比的激动。

在本次实验设计中我们收获了许多知识和经验,我们设计的八路抢答器虽然有部分的成功点,但也存在了许多的不足之处,具体的优点和不足一下一一介绍:

1.就电路而言,所言使用了相对较少的元器件,这样在实际的生产制造中降低了产品的成本,但是设计时使用了19个AT89C51的的端口,这样对芯片的端口是极大的浪费。

2.就输出的音响--蜂鸣器而言,设计使用的蜂鸣器是直接在单片机的P1口直接接上外部引脚,由于使用的蜂鸣器本生的内部结构有振荡电路,如此就不要再加振荡电路,又由于使用的是P1口作为输出,它在所有的输出口的电压最大,如此可以使蜂鸣器更加的响亮,但是在此设计上也存在不足,第一点是输出的音符过于单调。

3.在设计的过程中,源代码比较短小,占用的空间和对主机的内存使用较小,但是,源代码的编写过于占用单片机的使用时间,源代码是采用查询的方式进行工作,这样就降低了AT89C51的使用效率。

4.八路抢答器源代码的编写造成的误差也有待改善,在本次代码的编写中存在的误差为16uS,也就是说如果两个或者多个选手在抢答时,如果按键的时间等于或者小于16us的话对标号比较大的选手是不公平的,如此源代码还有待改善。

参考文献:

1.单片机原理及应用.张毅刚(第二版)高等教育出版社

2.单片机原理及接口技术(第3版).李朝青.北京航空航天大学出版社.2002

3. 单片机系统设计与实例指导.冯育长.西安电子科技大学出版社.2007

4. 单片机课程设计实例指导.李光飞.北京航天航空大学出版社.2004

5.单片机初级教程.张迎新.北京航空航天大学出版社.2000

6.单片机原理与应用技术.喻宗泉.西安电子科技大学出版社.2005

7.单片机实验与实践教程.王光毅.北京航空航天大学出版社.2007

附录1:程序代码:

ORG 0000H LJMP MAIN ORG 0100H MAIN:

mov p2,#0c0h JNB P3.3,MAIN1 AJMP MAIN MAIN1:

MOV A,#00H JNB P0.0,ONE MOV A,#01H JNB P0.1,ONE MOV A,#02H JNB P0.2,ONE MOV A,#03H JNB P0.3,ONE MOV A,#04H JNB P0.4,ONE MOV A,#05H JNB P0.5,ONE MOV A,#06H JNB P0.6,ONE

MOV A,#07H

JNB P0.7,ONE

LJMP MAIN1

ONE:MOV DPTR,#0300H

MOVC A,@A+DPTR

PRINT:

CLR P1.0

MOV P2,A

JNB P3.2,TP

LJMP PRINT

TP:

SETB P1.0

MOV P2,#0FFH

LJMP MAIN

ORG 0300H

DB

0F9H,0A4H,0B0H,99H,92H,82H,0F8H, 80H

END。