verilog- HDL实现流水灯

Verilog流水灯实验报告

流水灯实验报告实验二 流水灯一、 实验目的学会编写一个简单的流水灯程序并掌握分频的方法。

熟悉Modelsim 仿真软件的使用。

二、 实验要求用Quartus 编写流水灯程序,在Modelsim 软件中进行仿真。

三、 实验仪器和设备1、 硬件:计算机2、 软件:Quartus 、Modelsim 、(UE )四、 实验内容1、 将时钟周期进行分频。

2、 编写Verilog 程序实现LED 等依次亮灭,用Modelsim 进行仿真,绘制波形图。

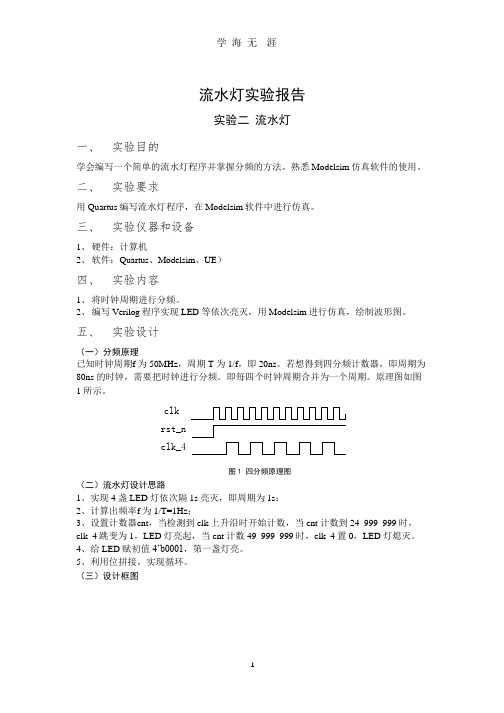

五、 实验设计(一)分频原理已知时钟周期f 为50MHz ,周期T 为1/f ,即20ns 。

若想得到四分频计数器,即周期为80ns 的时钟,需要把时钟进行分频。

即每四个时钟周期合并为一个周期。

原理图如图1所示。

rst_nclkclk_4图1 四分频原理图 (二)流水灯设计思路1、实现4盏LED灯依次隔1s亮灭,即周期为1s;2、计算出频率f为1/T=1Hz;3、设置计数器cnt,当检测到clk上升沿时开始计数,当cnt计数到24_999_999时,clk_4跳变为1,LED灯亮起,当cnt计数49_999_999时,clk_4置0,LED灯熄灭。

4、给LED赋初值4’b0001,第一盏灯亮。

5、利用位拼接,实现循环。

(三)设计框图图2 设计基本框图(四)位拼接的用法若输入a=4'b1010,b=3'b101,c=4'b0101,想要使输出d=5'b10001用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]}即把b的低1~2位10,c的低1位0,a的低1~2位01拼接起来,得到10 0 01。

流水灯4'b00014'b00104'b01004'b1000相当于把低三位左移,并最高位放在最低位。

用位拼接可写为:led<={led[2:0], led[3]};低三位最高位六、实验方法和步骤(一)时钟分频1、编写分频程序。

verilog- HDL实现流水灯

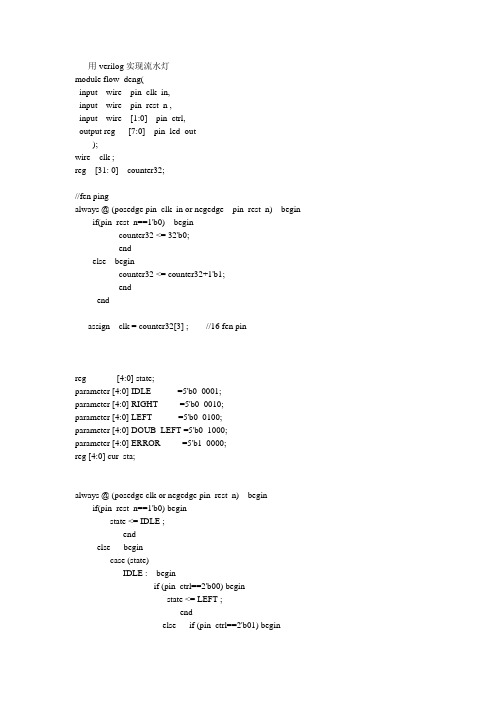

用verilog实现流水灯module flow_deng(input wire pin_clk_in,input wire pin_rest_n ,input wire [1:0] pin_ctrl,output reg [7:0] pin_led_out);wire clk ;reg [31: 0] counter32;//fen pingalways @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begincounter32 <= 32'b0;endelse begincounter32 <= counter32+1'b1;endendassign clk = counter32[3] ; //16 fen pinreg [4:0] state;parameter [4:0] IDLE =5'b0_0001;parameter [4:0] RIGHT =5'b0_0010;parameter [4:0] LEFT =5'b0_0100;parameter [4:0] DOUB_LEFT =5'b0_1000;parameter [4:0] ERROR =5'b1_0000;reg [4:0] cur_sta;always @ (posedge clk or negedge pin_rest_n) begin if(pin_rest_n==1'b0) beginstate <= IDLE ;endelse begincase (state)IDLE : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendLEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendRIGHT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendDOUB_LEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendERROR : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endenddefault: state <= IDLE ;endcaseendendalways @ (posedge clk or negedge pin_rest_n) beginif (pin_rest_n == 1'b0) beginpin_led_out[7:0]<=8'b0000_0000 ;endelse begincase (state)IDLE : beginpin_led_out [7:0] <=8'b0000_0000 ;endLEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out[7:0] <= 8'b0000_0001;endelse beginpin_led_out[7:1] <= pin_led_out[6:0];pin_led_out[0] <= pin_led_out[7];endendRIGHT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5 ]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out [7:0] <= 8'b0000_0001 ;endelse beginpin_led_out [6:0] <= pin_led_out [7:1] ;pin_led_out [7] <= pin_led_out [0] ;endendDOUB_LEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5] +pin_led_out[6]+pin_led_out[7])!=8'd2 ) beginpin_led_out [7:0] <= 8'b0000_0011 ;endelse beginpin_led_out [7:1] <= pin_led_out [6:0] ;pin_led_out [0] <= pin_led_out [7] ;endendERROR : beginpin_led_out [7:0]<=8'b1111_1111;enddefault : pin_led_out [7:0] <= 8'b0000_0000;endcaseendendendmodule。

Verilog流水灯实验报告

流火灯真验报告之阳早格格创做真验两流火灯一、真验手段教会编写一个简朴的流火灯步调并掌握分频的要领.认识Modelsim仿真硬件的使用.二、真验央供用Quartus编写流火灯步调,正在Modelsim硬件中举止仿真.三、真验仪器战设备1、硬件:估计机2、硬件:Quartus、Modelsim、(UE)四、真验真质1、将时钟周期举止分频.2、编写Verilog步调真止LED等依次明灭,用Modelsim举止仿真,画造波形图.五、真验安排(一)分频本理已知时钟周期f为50MHz,周期T为1/f,即20ns.若念得到四分频计数器,即周期为80ns的时钟,需要把时钟举止分频.即每四个时钟周期合并为一个周期.本理图如图1所示.图1四分频本理图(两)流火灯安排思路1、真止4盏LED灯依次隔1s明灭,即周期为1s;2、估计出频次f为1/T=1Hz;3、树坐计数器cnt,当检测到clk降下沿时启初计数,当cnt计数到24_999_999时,clk_4跳形成1,LED灯明起,当cnt计数49_999_999时,clk_4置0,LED灯燃烧.4、给LED赋初值4’b0001,第一盏灯明.5、利用位拼交,真止循环.(三)安排框图图2安排基础框图(四)位拼交的用法若输进a=4'b1010,b=3'b101,c=4'b0101,念要使输出d=5'b10001用位拼交,标记“{}”:d<={b[2:1],c[1],a[2:1]}即把b的矮1~2位10,c的矮1位0,a的矮1~2位01拼交起去,得到10001.流火灯4'b00014'b00104'b01004'b1000相称于把矮三位左移,并最下位搁正在最矮位.用位拼交可写为:led<={led[2:0],led[3]};矮三位最下位六、真验要领战步调(一)时钟分频1、编写分频步调.2、编写尝试步调.3、举止仿真,波形如图3所示.图3分频仿真截止(两)流火灯1、编写分频步调.3、编写尝试步调.3、举止仿真,为了俭朴时间战便当瞅察波形,将计数器值分别改为24、49跳转.波形如图4所示.图4流火灯仿真截止七、真验参照步调(一)时钟分频1、步调文献module div_clk( //模块名取文献名普遍.定义端心列表,input wire clk, //输进线型input wire rst_n,output reg clk_4 //输出定义为寄存器型);reg[3:0] cnt; //中括号定义位宽,定义中间变量cntalways@(posedge clk)if(rst_n==0)cnt <= 0; //复位为0,计数器也为0else if(cnt==3) //当计数器=3时浑整(可用else if)cnt <= 0;elsecnt <= cnt+1; //计数器自加1 always@(posedge clk)if(rst_n==0)else if(cnt==1)clk_4 <= 1; //当计数器为1时,时钟跳形成1else if(cnt==3)clk_4 <= 0; //当计数器为3时,时钟跳形成0endmodule2、尝试文献`timescale 1ns/1ns module tb_div_clk();reg clk;reg rst_n;wire clk_4;initialbeginclk = 0;rst_n = 0;#100rst_n = 1;endalways #5 clk=~clk; div_clk div_clk_inst(.clk(clk),.rst_n(rst_n),.clk_4(clk_4));endmodule(二)流火灯1、步调文献module LSD( //模块名取文献名普遍.定义端心列表,input wire clk, //输进线型input wire rst_n,output reg[3:0] led);reg[25:0] cnt; //中括号定义位宽,定义中间变量cntreg clk_4;always@(posedge clk)if(rst_n==0)cnt <= 0; //复位为0,计数器也为0else if(cnt==49_999_999) //当计数器=49999999时浑整(可用else if)cnt <= 0;elsecnt <= cnt+1; //计数器自加1 always@(posedge clk or negedge clk) //同步复位if(rst_n==0)else if(cnt==24_999_999)clk_4 <= 1; //当计数器为24999999时,时钟跳形成1else if(cnt==49_999_999)clk_4 <= 0; //当计数器为49999999时,时钟跳形成0elseclk_4 =clk_4;always@(posedge clk_4 or negedge clk_4)if(rst_n==0)led <= 4'b0001;elseled <= {led[2:0],led[3]};//位拼交endmodule2、尝试文献`timescale 1ns/1nsmodule LSD();reg clk;reg rst_n;reg cnt;wire led;initialbeginclk = 0;rst_n = 0;#100rst_n = 1;endalways #5 clk=~clk;LSD LSD_inst(.clk(clk),.rst_n(rst_n),.led(led));endmodule八、真验小结1、干真验要养成良佳的习惯,屡屡干真验时,皆要修坐一个新的文献夹存搁真验所需的步调文献,为仿真时增加文献干准备,也便当以去的查找战使用.2、写步调前要念领会电路真止本理,根据所教数电知识对于各个元器件举止统造.3、写步调时注意排版好瞅整净,共时注意增加注释.4、注意步调中模块名要战文献名普遍,可则步调报错,无法编译通过.5、仿真时,不妨采用分歧的进造.正在念要变动的场合左键,采用【Radix】,其中【Binary】为两进造.如图5所示.图5更矫正造6、正在流火灯仿真时,LED灯的波形一启初是过失的,果为步调中只检测了降下沿always@(posedge clk) ,加上下落沿检测always@(posedge clk or negedge clk) ,即可办理问题,乐成画造波形图.。

流水灯实验报告

实验二流水灯一、实验目的通过此实验进一步了解,熟悉FPGA开发软件的使用方法及V erilog.HDL,的编程方法;学习简单时序电路的设计。

二、实验原理和内容实验内容:在实验板上实现LED1~LED8发光二极管流水灯显示实验原理:在LED1~LED8引脚上周期性地输出流水数据,如原来输出的数据是11111100则表示点亮LED1,LED2,流水一次后,输出数据应该为11111000,而此时则应点亮LED1~LED3三个LED发光二极管,这样就可以实现LED流水灯,为了观察方便,流水速率最好在2Hz左右。

在QuickSOPC核心板上有-48MHz的标准时钟源,该时钟脉冲CLOCK 与芯片的28脚相连,为了产生2Hz的时钟脉冲,在此调用了一个分频模块int_div模块,通过修改分频系数来改变输出频率,int-div模块是一个占空比为50%的任意整数分频器。

三、实验步骤1,启动QuartusⅡ建立一个空白工程,然后命名为led-water.qpf。

2,新建V erilog HDL源程序文件ledwater.v,输入程序代码并保存,然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

3,从设计文件创建模块,由ledwater.v生成名为ledwater.bsf的模块符号文件。

4,将光盘中EDA-Component目录下的int-div.bsf和int-div.v拷贝到工程目录。

5,新建图形设计文件命名为led-water.bdf并保存。

在空白处双击鼠标左键,在Symbol对话框左上角的libraries.v中,分别将project下的ledwater和int-div模块放在图形文件led-water.bdf中,加入输入,输出引脚,双击各引脚符号进行引脚命名。

将与ledwater模块led[7..0]连接的引脚命名为led[7..0],与int-div模块clock连接的引脚命名为clock,int-div模块的clk-out与ledwater模块的clk相连接。

基于FPGA的流水灯

基于FPGA的流水灯概述流水灯是一种常见的电子实验项目,也是学习数字电路和FPGA编程的入门项目之一。

本文介绍了如何使用FPGA实现一个基于流水灯的电子项目。

需求流水灯项目的主要需求是将一组LED灯以一定的速率顺序点亮,然后逐个熄灭,再以同样的速率顺序点亮下一个LED 灯,如此循环。

硬件设计FPGA板在本项目中,我们使用一块支持FPGA编程的开发板。

可选的FPGA开发板包括Xilinx的Nexys 4或Digilent的Basys 3等。

LED灯流水灯需要一组LED灯来显示效果。

我们将使用FPGA开发板上的LED灯作为显示单元。

连接将LED灯的阳极连接到FPGA开发板的GPIO引脚上,并将其地连接到电路板上的公共地线。

软件设计硬件描述语言(HDL)HDL是一种用于描述数字电路和FPGA的语言。

常用的HDL包括VHDL和Verilog。

我们将使用Verilog作为本项目的HDL语言。

Verilog代码下面是一个基于FPGA的流水灯的Verilog代码示例:module led_shifter(input clk,output reg [7:0] leds);reg [25:0] counter;always @(posedge clk) begincounter <= counter + 1;if (counter == 26'd255) begincounter <= 0;leds <= leds << 1;endendendmodule上述Verilog代码中,我们定义了一个led_shifter模块,该模块接受一条时钟信号(clk)和一个用于控制LED灯的8位寄存器(leds)。

leds寄存器表示LED灯的状态,其中每个位代表一个LED灯。

在always块中,我们使用一个计数器counter来计算时钟脉冲的数量。

当计数器的值达到255时,即过了一定的时钟周期,我们将计数器重置为0,并将leds寄存器向左移动一位,即将下一个LED灯点亮。

Verilog流水灯实验报告.pptx

initial begin clk = 0; rst_n = 0; #100 rst_n = 1; end

always #5 clk=~clk;

LSD LSD_inst( .clk(clk), .rst_n(rst_n),

学海无 涯

流水灯实验报告

实验二 流水灯

一、 实验目的

学会编写一个简单的流水灯程序并掌握分频的方法。熟悉 Modelsim 仿真软件的使用。

二、 实验要求

用 Quartus 编写流水灯程序,在 Modelsim 软件中进行仿真。

三、 实验仪器和设备

1、 硬件:计算机 2、 软件:Quartus、Modelsim、(UE)

四、 实验内容

1、 将时钟周期进行分频。 2、 编写 Verilog 程序实现 LED 等依次亮灭,用 Modelsim 进行仿真,绘制波形图。

五、 实验设计

(一)分频原理 已知时钟周期f 为 50MHz,周期 T 为 1/f,即 20ns。若想得到四分频计数器,即周期为 80ns 的时钟,需要把时钟进行分频。即每四个时钟周期合并为一个周期。原理图如图 1 所示。

1

学海无 涯

clk LED

LED

FPGA

cnt

图 2 设计基本框图

(四)位拼接的用法 若输入 a=4'b1010,b=3'b101,c=4'b0101,想要使输出 d=5'b10001 用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]} 即把 b 的低 1~2 位 10,c 的低 1 位 0,a 的低 1~2 位 01 拼接起来,得到 10 0 01。 流水灯

verilogCPLD流水灯课程设计

verilogCPLD流水灯课程设计一、课程目标知识目标:1. 学生理解Verilog HDL基本语法和结构,掌握CPLD的基本原理和使用方法。

2. 学生能够描述流水灯的工作原理,并运用Verilog HDL编写程序实现流水灯的功能。

3. 学生了解数字电路设计中时序控制的重要性,并掌握基本时序电路的设计方法。

技能目标:1. 学生能够使用Verilog HDL进行基本程序编写,具备CPLD程序烧录和调试的能力。

2. 学生通过课程实践,培养动手操作能力,提高问题解决能力。

3. 学生能够运用所学知识,进行小组合作,完成流水灯课程的综合性设计。

情感态度价值观目标:1. 学生培养对电子设计的兴趣,增强学习主动性和积极性。

2. 学生在课程实践中,培养团队合作精神,提高沟通与协作能力。

3. 学生认识到电子技术在日常生活中的应用,激发创新意识和实践欲望。

课程性质:本课程为电子技术实践课程,以培养学生的实际操作能力和综合设计能力为主。

学生特点:学生已具备一定的电子技术基础知识,对Verilog HDL和CPLD有一定了解,但实际操作能力有待提高。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的动手能力和创新意识。

在教学过程中,强调团队合作,培养学生沟通协作能力。

通过课程目标的实现,使学生能够独立完成流水灯的设计与实现。

二、教学内容1. Verilog HDL基础语法与结构复习:重点回顾数据类型、运算符、控制语句等基本概念,确保学生能够熟练运用Verilog进行编程。

教材章节:第二章Verilog HDL基础2. CPLD基本原理与使用方法:介绍CPLD的内部结构、工作原理以及编程方法,使学生了解并掌握CPLD的基本使用。

教材章节:第三章CPLD/FPGA原理与应用3. 流水灯工作原理与设计:详细讲解流水灯的工作原理,分析设计思路,指导学生进行Verilog程序编写。

教材章节:第四章数字电路设计实例4. 时序控制与基本时序电路设计:探讨时序控制的重要性,教授基本时序电路的设计方法,为流水灯设计提供技术支持。

FPGA入门系列实验教程——流水灯

FPGA入门系列实验教程——LED流水灯1.实验任务让实验板上的8个LED实现流水灯的功能。

通过这个实验,进一步掌握采用计数与判断的方式来实现分频的Verilog HDL的编程方法以及移位运算符的使用。

2.实验环境硬件实验环境为艾米电子工作室型号EP2C8Q208C8增强版开发套件。

软件实验环境为Quartus II8.1开发软件。

3.实验原理流水灯,顾名思义就是让LED象水一样的点亮。

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水。

同样,如果使得最左边的灯先亮;然后,通过移位,在其右侧的灯,由左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯。

初始状态时,8个灯都不亮。

每来一个时钟脉冲CLK,计数器就加1。

每当判断出计数器中的数值达到25000000时,就会点亮一个灯,并进行移位。

FPGA输出的数据就应该首先是10000000,隔1秒钟变成11000000……一直变化到11111111,这样,依次点亮所有的灯,就形成了流水灯。

而当8个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态,即:灯都不亮。

然后,再一次流水即可。

如果是右移位,就出现向右流水的现象;反之,向左流水。

4.实验程序module ledwater(clk,led);//模块名及端口参数output[7:0]led;//输出端口定义input clk;//输入端口定义,50M时钟reg[8:0]led_out;//变量led_out定义为寄存器型reg[8:0]led_out1;//变量led_out1定义为寄存器型reg[25:0]buffer;//中间变量buffer定义为寄存器型always@(posedge clk)beginbuffer=buffer+1;if(buffer==26'd2*******)//判别buffer数值为25000000时,做输出处理beginled_out=led_out<<1;//led向左移位,空闲位自动添0补位if(led_out==9'b000000000)led_out=9'b111111111;led_out1=~led_out;//取反输出endendassign led=led_out1[7:0];endmodule5.实验步骤(1)建立新工程项目:打开Quartus II软件,进入集成开发环境,点击File→New project wizard建立一个工程项目ledwater。

verilog语言循环流水灯LED流水从中间向两边点依次点亮

verilog语言循环流水灯LED流水从中间向两边点依

次点亮

目的是实现FPGA开发板上的四个LED灯依次点亮,每次只点亮一个,每个点亮时间是0.5s。

输入有时钟和复位信号,一路输出连接到FPGA开发板上的四个LED灯。

设置输出信号位宽四位宽,刚好一个位宽控制一个LED灯亮灭。

需要设置一个中间变量计数器,初值为0,因为50MHz晶振,0.5秒计数为25000000,从0开始计数,所以计数器计数最大值为24_999_999,当计数器在复位信号无效或计数到最大值时,对计数器进行清零操作。

再设置一个计数标致信号,在计数器计数到最大值时,拉高一个时钟周期的高电平,其他时刻保持低电平。

led灯是低电平点亮,所以想要第一个灯点亮就需要对输出信号赋初值1110,然后当计数标致信号为高电平且复位信号无效时,赋值为1101,下一个周期为1011,再下一个周期为0111,然后再是1110,这样就实现了流水灯效果。

这里需要用到移位操作,但需要注意的是在移位过程中,补位补的是0,及1101,1010,0100,1000,0000这就意味着最后所有灯都处于被点亮的状态,与目标不符。

于是再定义一个新的变量,对输出信号进行寄存。

初值为0001,接下来是0010,0100,1000,0001,输出信号对这个变量取反就可以得到预期结果。

计数到最大值时归零,计数器标致信号在最大值处拉高一个时钟周期,led输出与预期吻合。

[Keil][Verilog][微机原理]流水灯、存储器、外部中断实验_北京邮电大学计算机。。。

![[Keil][Verilog][微机原理]流水灯、存储器、外部中断实验_北京邮电大学计算机。。。](https://img.taocdn.com/s3/m/5212916000f69e3143323968011ca300a6c3f676.png)

[Keil][Verilog][微机原理]流⽔灯、存储器、外部中断实验_北京邮电⼤学计算机。

计算机原理与应⽤实验-流⽔灯、存储器、外部中断实验1 实验⼀流⽔灯实验1.1 实验⽬的1. 掌握ARM开发⼯具的使⽤。

2. 掌握基本IO的使⽤。

1.2 实验原理及内容1. 电路结构图实现流⽔灯的电路结构图如图1所⽰。

以两条红⾊虚线为界,从左⾄右第⼀部分为ARM系统部分,第三部分为外围电路,第⼆部分是接⼝部分,需要⾃⼰将其连接。

图 1 流⽔灯的电路结构图接线⽅式为:GPIOF_0~GPIOF_7(P12接⼝)接LED1~LED8(P2接⼝)。

1. LED电路原理LED灯的驱动原理如图2所⽰。

当发光⼆极管正向导通时,LED灯点亮。

图 2 LED灯正向导通如图3所⽰,LED灯与MCU引脚连接,MCU IO额定电流为25mA,例如0603封装红⾊LED灯额定电流为20mA,已经接近MCU IO的额定电流,可能会损毁器件。

因此图1.3微控制器驱动LED灯⽅案不可取。

图 3 微控制器驱动 LED 灯实际微控制驱动LED灯的电路模型包括:控制器、驱动器和执⾏器三部分,控制器提供控制信号,再由驱动器驱动执⾏器,如图4所⽰。

图 4 LED 灯去驱动电路模型如图5所⽰LED灯通过N沟道MOS管驱动,MCU IO输出⾼电平时MOS管漏极和源极导通LED灯被点亮,反之MCU输出低电平时MOS管漏极和源极截⽌,LED灯不能被点亮。

假设VCC电压3.3V,MOS管导通阻值为零,通过LED灯的电流将远超额定电流出现短路现象,故此⽅案不可取。

图 5 MOS 管驱动 LED 灯电路如图6所⽰,LED驱动电路中增加电阻(R),以此保证通过LED灯的电流不超过额定电流,避免损坏器件,故将电阻R称为限流电阻。

图 6 限流电阻如图7所⽰LED电路原理图,R1位置电阻作为限流电阻,R29位置电阻作为下拉电阻,避免MOS管栅极出现亚稳态。

图 7 LED 电路原理图1. 微控制器IO输出控制原理如图8所⽰,基本结构针对STM32F407有7组IO。

verilog流水灯控制器++

verilog流水灯控制器//学习3 8译码器的原理,//拨码开关的 1 2 3作为输入//本实验采用拨码开关来作为输入,LED作为状态显示//当然如果你的学习板没有拨码开关,可以用key1 key2 key3 作为数据输入。

//视频教程适合我们21EDA电子的所有学习板module decoder_38(out,key_in);output[7:0] out; //3 8译码器输出有8钟状态,所以要8个LED灯。

input[2:0] key_in; //(1 2 3)key1 key2 key3 作为数据输入reg[7:0] out;always @(key_in)begincase(key_in)3'd0: out=8'b11111110; //LED作为状态显示,低电平有效3'd1: out=8'b11111101;3'd2: out=8'b11111011;3'd3: out=8'b11110111;3'd4: out=8'b11101111;3'd5: out=8'b11011111;3'd6: out=8'b10111111;3'd7: out=8'b01111111;endcaseendendmodule1位数码管动态显示//一位数码管试验//利用分频计数器得到数码管,效果//视频教程适合我们21EDA电子的所有学习板module SMG_LED (clk_50M,rst,led_bit,dataout);input clk_50M,rst; //系统时钟50M输入从12脚输入。

output [7:0] dataout; //我们这里用数码管,output led_bit; //一位数码管的位选择reg [7:0] dataout;reg led_bit;reg [27:0] count; //分频计数器//分频计数器always @ ( posedge clk_50M )begincount<=count+1; //计数器自加endalways @ ( posedge clk_50M or negedge rst)beginled_bit <= 'b0; //是数码管的位选择处于导通状态case ( count[27:24] )// case ( count[27:24] )这一句希望初学者看明白,// 也是分频的关键// 在数码管上面显示0到F0: dataout<=8'b11000000; //01: dataout<=8'b11111001;2: dataout<=8'b10100100;3: dataout<=8'b10110000;4: dataout<=8'b10011001;5: dataout<=8'b10010010;6: dataout<=8'b10000010;7: dataout<=8'b11111000;8: dataout<=8'b10000000;9: dataout<=8'b10010000;10:dataout<=8'b10001000;11:dataout<=8'b10000011;12:dataout<=8'b11000110;13:dataout<=8'b10100001;14:dataout<=8'b10000110;15:dataout<=8'b10001110; //fendcaseendendmodule7段数码管静态显示//本实验就是学习单个数码管的显示//视频教程适合我们21EDA电子的所有学习板module SMG_LED (clk_50M,led_bit,dataout);input clk_50M ; //系统时钟50M输入从12脚输入。

verilog程序-流水灯

/****************************************************程序功能:流水灯版本:1.1 版权:分享快乐*****************************************************/ module liu_shui_deng(input wire pin_clk_in,input wire pin_rest_n ,input wire [1:0] pin_ctrl,output reg [7:0] pin_led_out);wire clk ;reg [31: 0] counter32;always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begincounter32 <= 32'b0;endelse begincounter32 <= counter32+1'b1;endendassign clk = counter32[3] ;reg [2:0] cur_sta,stateparameter [2:0] IDLE =3'b000;parameter [2:0] RIGHT =5'b001;parameter [2:0] LEFT =5'b010;parameter [2:0] DOUB_LEFT =5'b011;parameter [2:0] ERROR =5'b100;always @ (posedge clk or negedge pin_rest_n) beginif(pin_rest_n==1'b0) beginstate <= IDLE ;endelse begincase (state)IDLE : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendLEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendRIGHT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendDOUB_LEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendERROR : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endenddefault: state <= IDLE ;endcaseendendalways @ (posedge clk or negedge pin_rest_n) beginif (pin_rest_n == 1'b0) beginpin_led_out[7:0]<=8'b0000_0000 ;endelse begincase (state)IDLE : beginpin_led_out [7:0] <=8'b0000_0000 ;endLEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out[7:0] <= 8'b0000_0001;endelse beginpin_led_out[7:1] <= pin_led_out[6:0];pin_led_out[0] <= pin_led_out[7];endendRIGHT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out [7:0] <= 8'b0000_0001 ;endelse beginpin_led_out [6:0] <= pin_led_out [7:1] ;pin_led_out [7] <= pin_led_out [0] ;endendDOUB_LEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd2 ) beginpin_led_out [7:0] <= 8'b0000_0011 ;endelse beginpin_led_out [7:1] <= pin_led_out [6:0] ;pin_led_out [0] <= pin_led_out [7] ;endendERROR : beginpin_led_out [7:0]<=8'b1111_1111;enddefault : pin_led_out [7:0] <= 8'b0000_0000;endcaseendendendmodule。

Verilog流水灯设计_SegLed

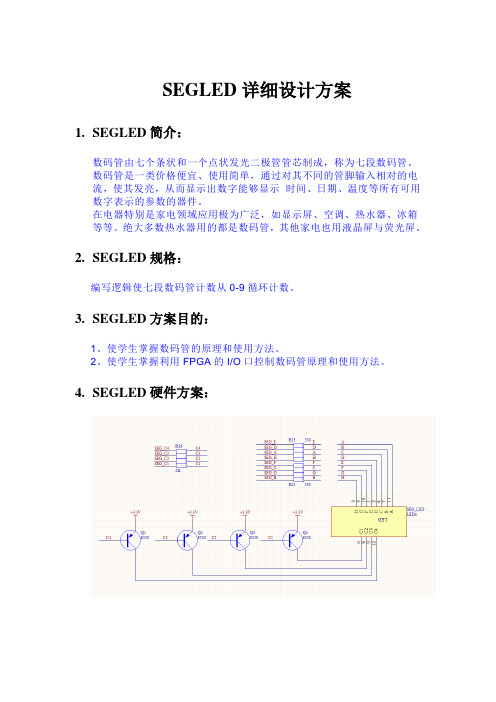

SEGLED详细设计方案1.SEGLED简介:数码管由七个条状和一个点状发光二极管管芯制成,称为七段数码管。

数码管是一类价格便宜、使用简单,通过对其不同的管脚输入相对的电流,使其发亮,从而显示出数字能够显示时间、日期、温度等所有可用数字表示的参数的器件。

在电器特别是家电领域应用极为广泛,如显示屏、空调、热水器、冰箱等等。

绝大多数热水器用的都是数码管,其他家电也用液晶屏与荧光屏。

2.SEGLED规格:编写逻辑使七段数码管计数从0-9循环计数。

3.SEGLED方案目的:1、使学生掌握数码管的原理和使用方法。

2、使学生掌握利用FPGA的I/O口控制数码管原理和使用方法。

4.SEGLED硬件方案:5.实现原理七段数码管实物图片:七段数码管原理:拿显示8举例子;1 1 1 0 1 1 1 1 对应:e gf dp c d b a数码管类型:根据其结构的不同,可分为共阳极数码管和共阴极数码管两种。

共阳共阴,是针对数码管的公共脚而说的。

典型的一位数码管,一般有10个脚,8个段码(7段加1个小数点),剩下两个脚接在一起。

各个段码实际上是一个发光二极管,既然是发光二极管,就有正负极。

共阳,也就是说公共脚是正极(阳极),所有的段码实际上是负极,当某一个或某几个段码位接低电平,公共脚接高电平时,对应的段码位就能点亮,进而组合成数字或字母。

共阴是公共脚是负极(阴极),段码位是阳极,当公共脚接地,段码位接高电平时,对应段码位点亮。

一位数码管就是这样,多位的数码管原理类似。

LED数码管中各段发光二极管的伏安特性和普通二极管类似,只是正向压降较大,正向电阻也较大。

在一定范围内,其正向电流与发光亮度成正比。

由于常规的数码管起辉电流只有1~2 mA,最大极限电流也只有10~30 m A。

共阴共阳与电路接线密切相关,决定了驱动电路的接法,因此在电路设计前要考虑好数码管的类型,否则就不能实现显示的效果了。

共阳极的比较容易驱动,共阴极的比较好编程。

FPGA流水灯实验

编写代码的首要任务是管理复杂度,研究表明人能同时关注的智 力模型为 7+2,而嵌套关注通常不超过 5 层。编写一段代码的同时关 注点很容易会超过 9 个。通过智力训练提供关注智力模型数的效果微 乎其微。所以为了能编写任意大规模的代码,把同一时间关注的智力 模型数降低的方法是很有效的。而且软件工程也是在制定相关的编程 规范,对编程限制的基础上发展起来的。VerilogHDL 虽然是硬件描述 语言,但它已经摆脱了原始的电路图输入的方式,具有更高的抽象性, 所以它应该可以应该软件开发中的类似的结论来提高开发效率。就像 高级语言相对于 01 机器码编程一样。我觉得在 verilogHDL 在模仿顺 序操作上更像汇编语言,因为它没有实现顺序,选择,循环结构的相

10

了对 Led_Driver 更高层次的操作,使得操作每个 LED 站在了抽象层, 而不是是底层。

在底层你需要考虑定时器翻转多少次才能到这个时间,然后还要 用这个时间打开或关闭 LED,这样需要考虑的问题很复杂也容易出错。 在抽象层你只需要给什么时候打开或关闭 LED 就够了,它就会自动的 完成翻转工作。抽象性也是人脑处理信息的方式,例如自己的家你甚 至说不清门是什么颜色的,门的把手是什么样式的。人脑对门的处理 是抽象的,它是一个可以开和关的门。你只需要知道这个就可以进入 家中,根本不需要记得门的颜色是什么。

verilog语言的FPGA变速花样流水灯设计

verilog语言的FPGA变速花样流水灯设计基于XILINX--XSE500E型FPGA的变速流水灯以及花样流水灯的verilog语言设计摘要临近大四毕业,诸多工科院校电子电科通信等专业会选择用FPGA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FPGA设计。

FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。

此次设计采用XILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。

板载时钟50MHz,如需其他时钟周期,可采用IP核中的clocking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。

此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。

本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。

谢谢大家的支持!正文一,普通流水灯 1,建模思想普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。

普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。

还有复位输入rst,高电平有效。

此外就是led端口,这个端口有8根管脚,共8位,连接8个led灯。

采用verilog语言,端口定义格式如下:module led(input clk, input rst,output reg[7:0] led //此行定义说明led端口既是驱动管脚的,又是寄存器 );采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。

由于板载时钟50MHz,如果每个时钟周期都要滚动流水灯,那么速度是惊人的,人眼根本无法分辨。

所以采用计数器延时,当计数达到约4千万时候,驱动系统进行动作,可以判断,也可以进行流水灯动作。

用FPGA实现的流水灯VHDL代码

双击图标选择 bit 文件。右键图标选 择

可编辑

-------------精选文档-----------------

Program

可编辑

-------------精选文档-----------------

设计目的:

在 8 盏 LED 灯每隔一秒钟顺序循环提供高电平使 LED 亮,复位键使 LED 全部置低电平使 LED 灭,重新进行流ED(1) LED(2) LED(3) LED(4) LED(5) LED(6) LED(7)

entity LED_FLASH_VHD is Port ( clk : in STD_LOGIC;

可编辑

-------------精选文档-----------------

rst : in STD_LOGIC; LED_RUN : out STD_LOGIC_VECTOR (7 downto 0)); end LED_FLASH_VHD;

其中 cnt 实现记数功能,对时钟进行分频。 Step 实现让具体哪一盏灯亮。 使用引脚: 复位 rst(Y18)、时钟 clk(D11)、LED 灯(N19、 N15、 R20、R18、U20、

T18、U18、W20);

具体设计:

1、 打开设计软件 Xilinx ISE 11,新建工程 2、 新建 VHDL Module 设置代码,对时钟进行分频: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

可编辑

verilog程序-流水灯

/****************************************************程序功能:流水灯版本:1.1 版权:分享快乐*****************************************************/ module liu_shui_deng(input wire pin_clk_in,input wire pin_rest_n ,input wire [1:0] pin_ctrl,output reg [7:0] pin_led_out);wire clk ;reg [31: 0] counter32;always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begincounter32 <= 32'b0;endelse begincounter32 <= counter32+1'b1;endendassign clk = counter32[3] ;reg [2:0] cur_sta,stateparameter [2:0] IDLE =3'b000;parameter [2:0] RIGHT =5'b001;parameter [2:0] LEFT =5'b010;parameter [2:0] DOUB_LEFT =5'b011;parameter [2:0] ERROR =5'b100;always @ (posedge clk or negedge pin_rest_n) beginif(pin_rest_n==1'b0) beginstate <= IDLE ;endelse begincase (state)IDLE : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendLEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendRIGHT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) begin state <= DOUB_LEFT ;endelse beginstate <= ERROR ;endendDOUB_LEFT : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) begin state <= RIGHT ;endelse if (pin_ctrl==2'b10) beginendelse beginstate <= ERROR ;endendERROR : beginif (pin_ctrl==2'b00) beginstate <= LEFT ;endelse if (pin_ctrl==2'b01) beginstate <= RIGHT ;endelse if (pin_ctrl==2'b10) beginstate <= DOUB_LEFT ;endelse beginstate <= ERROR ;endenddefault: state <= IDLE ;endcaseendendalways @ (posedge clk or negedge pin_rest_n) beginif (pin_rest_n == 1'b0) beginpin_led_out[7:0]<=8'b0000_0000 ;endelse begincase (state)IDLE : beginpin_led_out [7:0] <=8'b0000_0000 ;endLEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out[7:0] <= 8'b0000_0001;endelse beginpin_led_out[7:1] <= pin_led_out[6:0];pin_led_out[0] <= pin_led_out[7];endendRIGHT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) beginpin_led_out [7:0] <= 8'b0000_0001 ;endelse beginpin_led_out [6:0] <= pin_led_out [7:1] ;pin_led_out [7] <= pin_led_out [0] ;endendDOUB_LEFT : beginif((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]+pin_led_out[6]+pin_led_out[7])!=8'd2 ) beginpin_led_out [7:0] <= 8'b0000_0011 ;endelse beginpin_led_out [7:1] <= pin_led_out [6:0] ;pin_led_out [0] <= pin_led_out [7] ;endendERROR : beginpin_led_out [7:0]<=8'b1111_1111;enddefault : pin_led_out [7:0] <= 8'b0000_0000;endcaseendendendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用verilog实现流水灯

module flow_deng(

input wire pin_clk_in,

input wire pin_rest_n ,

input wire [1:0] pin_ctrl,

output reg [7:0] pin_led_out

);

wire clk ;

reg [31: 0] counter32;

//fen ping

always @ (posedge pin_clk_in or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin

counter32 <= 32'b0;

end

else begin

counter32 <= counter32+1'b1;

end

end

assign clk = counter32[3] ; //16 fen pin

reg [4:0] state;

parameter [4:0] IDLE =5'b0_0001;

parameter [4:0] RIGHT =5'b0_0010;

parameter [4:0] LEFT =5'b0_0100;

parameter [4:0] DOUB_LEFT =5'b0_1000;

parameter [4:0] ERROR =5'b1_0000;

reg [4:0] cur_sta;

always @ (posedge clk or negedge pin_rest_n) begin if(pin_rest_n==1'b0) begin

state <= IDLE ;

end

else begin

case (state)

IDLE : begin

if (pin_ctrl==2'b00) begin

state <= LEFT ;

end

else if (pin_ctrl==2'b01) begin

state <= RIGHT ;

end

else if (pin_ctrl==2'b10) begin

state <= DOUB_LEFT ;

end

else begin

state <= ERROR ;

end

end

LEFT : begin

if (pin_ctrl==2'b00) begin

state <= LEFT ;

end

else if (pin_ctrl==2'b01) begin

state <= RIGHT ;

end

else if (pin_ctrl==2'b10) begin

state <= DOUB_LEFT ;

end

else begin

state <= ERROR ;

end

end

RIGHT : begin

if (pin_ctrl==2'b00) begin

state <= LEFT ;

end

else if (pin_ctrl==2'b01) begin

state <= RIGHT ;

end

else if (pin_ctrl==2'b10) begin

state <= DOUB_LEFT ;

end

else begin

state <= ERROR ;

end

end

DOUB_LEFT : begin

if (pin_ctrl==2'b00) begin

state <= LEFT ;

end

else if (pin_ctrl==2'b01) begin

state <= RIGHT ;

end

else if (pin_ctrl==2'b10) begin

state <= DOUB_LEFT ;

end

else begin

state <= ERROR ;

end

end

ERROR : begin

if (pin_ctrl==2'b00) begin

state <= LEFT ;

end

else if (pin_ctrl==2'b01) begin

state <= RIGHT ;

end

else if (pin_ctrl==2'b10) begin

state <= DOUB_LEFT ;

end

else begin

state <= ERROR ;

end

end

default: state <= IDLE ;

endcase

end

end

always @ (posedge clk or negedge pin_rest_n) begin

if (pin_rest_n == 1'b0) begin

pin_led_out[7:0]<=8'b0000_0000 ;

end

else begin

case (state)

IDLE : begin

pin_led_out [7:0] <=8'b0000_0000 ;

end

LEFT : begin

if

((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5]

+pin_led_out[6]+pin_led_out[7])!=8'd1 ) begin

pin_led_out[7:0] <= 8'b0000_0001;

end

else begin

pin_led_out[7:1] <= pin_led_out[6:0];

pin_led_out[0] <= pin_led_out[7];

end

end

RIGHT : begin

if((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5 ]+pin_led_out[6]+pin_led_out[7])!=8'd1 ) begin

pin_led_out [7:0] <= 8'b0000_0001 ;

end

else begin

pin_led_out [6:0] <= pin_led_out [7:1] ;

pin_led_out [7] <= pin_led_out [0] ;

end

end

DOUB_LEFT : begin

if

((pin_led_out[0]+pin_led_out[1]+pin_led_out[2]+pin_led_out[3]+pin_led_out[4]+pin_led_out[5] +pin_led_out[6]+pin_led_out[7])!=8'd2 ) begin

pin_led_out [7:0] <= 8'b0000_0011 ;

end

else begin

pin_led_out [7:1] <= pin_led_out [6:0] ;

pin_led_out [0] <= pin_led_out [7] ;

end

end

ERROR : begin

pin_led_out [7:0]<=8'b1111_1111;

end

default : pin_led_out [7:0] <= 8'b0000_0000;

endcase

end

end

endmodule。