用CPU对Altera公司的FPGA进行配置功能模块设计

Altera_FPGA_配置模式

FPGA配置模式时间:2011-09-12 23:15:16 来源:作者:FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其编程。

如何实现快速的时序收敛、降低功耗和成本、优化时钟管理并降低FPGA与PCB并行设计的复杂性等问题,一直是采用FPGA的系统设计工程师需要考虑的关键问题。

如今,随着FPGA向更高密度、更大容量、更低功耗和集成更多IP的方向发展,系统设计工程师在从这些优异性能获益的同时,不得不面对由于FPGA前所未有的性能和能力水平而带来的新的设计挑战。

在很多项目设计中采用Altera 公司基于SRAM架构Cyclone系列器件。

Cyclone器件与其他FPGA器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA内部的SRAM中,由于SRAM的易失性,每次上电时,都必须对FPGA进行重新配置。

1 Cyclone FPGA 配置模式Cyclone系列FPGA器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS)配置、被动串行(PS)配置以及基于JTAG配置,实际应用时可以使用其中的一种方案配置Cyclone系列FPGA器件,来实现用户编程所要实现的功能。

Cyclone系列FPGA器件是用SRAM单元配置数据的。

由于SRAM掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone器件中。

不同的配置模式可采用不同的专用配置芯片或数据源这三种配置模式是由Cyclone器件的模式选择引脚MSEL1和MSEL0的高低电平来决定的,如果你的实际应用只要求单一的配置模式,可以把模式选择引脚连接到VCC端或接地端在切换引脚的过程中,器件的运行状态不会被影响。

alterafpga配置

alterafpga配置配置是连接FPGA软件设计到硬件功能实现的桥梁,配置电路部分有误,配置文件无法下载到配置器件中,对FPGA编程,则再好的设计都是浮云。

上电后,配置数据保存在配置RAM中,将配置数据载入配置RAM即是对FPGA编程。

配置方式有很多种,主要区别为FPGA所处的地位和打入数据的方式不同,其基本时序基本相同。

基本时序波形如下:配置过程主要由nCONFIG、nSTATUS、CONF_DONE以及可选的INIT_DONE四个状态信号控制。

一个器件完整的配置过程包括上电复位、配置、初始化三个阶段。

正常上电后,nCONFIG管脚被拉低,器件复位,此时配置RAM的所有内容被清空,所有I/O处于高阻态,其余三个状态信号亦均被拉低,复位结束后,FPGA释放nCONFIG管脚,使其被外部上拉电阻拉高,FPGA在nCONFIG检测到由低到高的跳变沿,配置开始,同时FPGA 采样MSEL的信号状态,决定接受何种配置模式。

随后,FPGA释放nSTATUS管脚,外不上拉电阻将其拉高,FPGA在nSTATUS管脚检测到由低到高的跳变沿,表示FPGA开始接受数据。

配置数据由DATA管脚打入,配置时钟经DCLK管脚送入(被动方式下,主动方式DCLK 由FPGA提供),配置数据在上升沿锁存至FPGA中,配置数据全部打入到FPGA后,FPGA释放CONF_DONE管脚,使其由外部上拉电阻拉高,说明配置结束,进入初始化过程。

INIT_DONE是一个可选的指示初始化完成的信号(Device-Pin&Options-general),INIT_DONE在nCONFIG信号为低或配置的初期时为高电平,而当使能INIT_DONE的比特位(在配置数据的第一帧中)被配置进FPGA后,INIT_DONE信号变低,因此INIT_DONE信号由高到低的跳变表示FPGA配置真正开始,开始接收配置数据,如果INIT_DONE一直保持为高,说明FPGA没有接收到正确配置数据的文件头。

嵌入式开发笔记——MCU配置Altera-Cyclone系列FPGA

嵌入式开发笔记——MCU配置Altera-Cyclone系列FPGA作者:zzssdd2E-mail:*******************1、需求描述FPGA内部是SRAM储存结构,掉电后程序就会丢失,故需要将FPGA程序保存在掉电不丢失的储存介质中(比如FLASH、EMMC、SD卡等),在每次上电时读取程序进行配置。

2、功能分析项目中使用的FPGA型号是Altera公司(现属于Intel)的Cyclone系列。

在Altera的文档《Cyclone Device Handbook,Volume1》的第13章节讲述了该系列FPGA的几种配置方式。

FPGA'的三种配置模式模式描述AS(Active serial)模式FPGA主动配置。

该模式由FPGA主动从外部储存器读取配置数据PS(Passive serial)模式FPGA被动控制。

该模式由外部控制器对FPGA进行配置JTAG模式通过外部下载器下载到FPGA内部SRAM中FPGA选择配置模式通过MSEL0和MSEL1引脚不同的电平来选择配置方式(如果使用JTAG配置则可以忽略这些引脚配置)MSEL1 MSEL0 模式0 0 AS0 1 PSx x JTAG最终确定的方案是使用PS模式通过MCU来升级、配置FPGA。

下面主要讲使用MCU对FPGA进行PS模式下的配置过程。

PS模式配置引脚时序•发起配置请求o nCONFIG引脚拉低tCFG时间然后拉高,等待nSTATU拉低响应请求•进行配置o FPGA在DCLK引脚的上升沿采集DATA引脚Bit数据,LSB在前传输方式•配置完成o等待CONF_DONE引脚回应一个高电平表示配置完成PS配置模式时序参数3、功能实现配置FPGA用到的变量和标志static uint8_t fpga_cfg_buf[W25Q_SECTOR_SIZE]; //储存从FLASH读出数据static __IO uint8_t fpga_cfg_sta = 0x00; //记录配置状态//配置过程用到的标识enum{FPGA_CFG_ENABLE = 0x01,FPGA_CFG_START = 0x02,FPGA_CFG_DONE = 0x04,FPGA_CFG_OVER = 0x08,};MCU与FPGA连接引脚配置/**************************************************************** ******** 函数: fpga_config_init* 功能: 配置FPGA引脚* 输入: 无* 输出: 无*************************************************************** ********/void fpga_config_init(void){GPIO_InitTypeDef GPIO_InitStruct = {0};/* 引脚时钟使能 */FPGA_PIN_CLK_ENABLE();/* nCFG、DAT、CLK配置为输出 */GPIO_InitStruct.Pin = FPGA_nCFG_PIN;GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;GPIO_InitStruct.Pull = GPIO_NOPULL;GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;HAL_GPIO_Init(FPGA_nCFG_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_DAT_PIN;HAL_GPIO_Init(FPGA_DAT_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CLK_PIN;HAL_GPIO_Init(FPGA_CLK_PORT, &GPIO_InitStruct);/* nSTA、CFG_DONE配置为输入 */GPIO_InitStruct.Pin = FPGA_nSTA_PIN;GPIO_InitStruct.Mode = GPIO_MODE_INPUT;GPIO_InitStruct.Pull = GPIO_NOPULL;HAL_GPIO_Init(FPGA_nSTA_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CFG_DONE_PIN;HAL_GPIO_Init(FPGA_CFG_DONE_PORT, &GPIO_InitStruct);/* 配置引脚默认状态 */HAL_GPIO_WritePin(FPGA_nCFG_PORT, FPGA_nCFG_PIN, GPIO_PIN_SET);HAL_GPIO_WritePin(FPGA_DAT_PORT, FPGA_DAT_PIN, GPIO_PIN_RESET);HAL_GPIO_WritePin(FPGA_CLK_PORT, FPGA_CLK_PIN, GPIO_PIN_RESET);}MCU对FPGA配置过程/**************************************************************** ******** 函数: fpga_config_process* 功能: FPGA程序配置* 输入: _uiDataSize:FPGA配置文件大小* _uiStartAddr:FLASH储存FPGA配置文件地址* 输出: 失败:< 0; 成功:0*************************************************************** ********/int fpga_config_process(uint32_t _uiDataSize, uint32_t _uiStartAddr){UINT interrupt_save;uint16_t i, j;uint32_t uiTout, uiRdAddr, uiCnt = 0;fpga_cfg_sta = 0;uiRdAddr = _uiStartAddr;/*############## 第一阶段:发起配置请求########################*/FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_RESET);dwt_delay_us(100);FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_SET);dwt_delay_us(40);/* 等待FPGA回应:100ms超时 */for (uiT out = 0; uiT out < 10000; uiTout++){if (GPIO_PIN_RESET == FPGA_PinRead(FPGA_nSTA_PORT,FPGA_nSTA_PIN)){SET_BIT(fpga_cfg_sta, FPGA_CFG_START);break;}dwt_delay_us(10);}/* 是否响应? */if (!READ_BIT(fpga_cfg_sta, FPGA_CFG_START)){return -1;}/*############## 第二阶段:进行配置########################*/do{W25Q_ReadBuffer(fpga_cfg_buf, uiRdAddr, W25Q_SECTOR_SIZE);uiRdAddr += W25Q_SECTOR_SIZE;for (i = 0; i < W25Q_SECTOR_SIZE; i++){/* 按bit写入,LSB在前 */DISABLE_IRQ();for (j = 0; j < 8; j++){if (fpga_cfg_buf[i] & 0x01){FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_S ET);}else{FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_ RESET);}FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_S ET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);fpga_cfg_buf[i] >>= 1;ENABLE_IRQ();/* 数据写入完毕退出 */if (++uiCnt >= _uiDataSize){SET_BIT(fpga_cfg_sta, FPGA_CFG_OVER);break;}}}while(RESET == READ_BIT(fpga_cfg_sta, FPGA_CFG_OVER));/*############## 第三阶段:等待配置完成回应########################*/for (i = 0, uiT out = 0; uiTout < 20000; uiTout++){dwt_delay_us(100);if (GPIO_PIN_SET == FPGA_PinRead(FPGA_CFG_DONE_PORT,FPGA_CFG_DONE_PIN)) {if (++i >= 10){SET_BIT(fpga_cfg_sta, FPGA_CFG_DONE);break;}}else{i = 0;}if (READ_BIT(fpga_cfg_sta, FPGA_CFG_DONE)) {return 0;}else{return -1;}}。

Altera公司FPGA的配置

•

针对FPGA器件不同的内部结构,Altera公司

提供了不同的器件配置方式。Altera FPGA的配

置可通过编程器、JATG接口在线编程及Altera在

线配置等方式进行。

•

Altera器件编程下载电缆的有:

ByteBlaster并行下载电缆,ByteBlasterMV并行

MAX9000(包括MAX9000A)、MAX7000S和MAX7000A

进行编程。ByteBlaster为FPGA提供了一种快速而

廉价的配置方法,设计人员的设计可以直接通过

ByteBlaster下载电缆下载到芯片中去。

(1)下载模式

ByteBlaster并行下载电缆提供两种下载模式: • ①Passive serial mode(PS,被动串行模式)

1. PS(被动串行)模式

•

在PS(被动串行)模式下,MasterBlaster

下载电缆和ByteBlasterMV下载电缆可以对单个

与多个APEXⅡ、APEX20K、Mercury、ACEX1K、

FLEX10K或 FLEX6000系列器件进行配置。在PS模

式,配置数据从数据源通过MasterBlaster下载

电缆和ByteBlasterMV下载电缆串行地传送到器

件,配置数据由数据源提供的时钟同步。

(1)PS模式单个器件的配置电路设计

•

PS模式可以完成对单个APEXⅡ、 NhomakorabeaPEX20K、

Mercury、ACEX1K、FLEX10K或 FLEX6000系列器件

的配置,配置电路如图6.2所示。

•

图中:除 APEX20KE、APEX20KC系列器件外,

Altera FPGA配置及升级

Altera FPGA配置方式及升级方式(针对cyclone II器件)1、配置cyclone II FPGA对于altera fpga,主要配置方式为AS,PS,JTAG三种配置方式。

这几种配置方式在于电路上对器件配置方式引脚选择不同:如图1.1所示:图1.1注意1:对于快速AS模式,只支持配置芯片EPCS16,EPCS64;2:对于JTAG配置模式,只应用JTAG,该引脚连接到地;2、配置器件(图2.1):图2.13、FPGA配置方式具体分体3.1AS(Active Serial)配置:3.1.1原理AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone器件处于主动地位,配置器件处于从属地位。

AS配置器件采用四引脚接口处理:DCLK、DATA、ASDI、nCS;配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

3.1.2电路连接方式(图3.1)图3.13.1.3配置时序(图3.2)图3.2在配置完成后到初始化完成所需要299个时钟周期(100M)3.1.4配置文件.pof .jic .rbf3.2PS(Passive Serial)配置方式3.2.1配置原理主动串行配置方式可以通过altera配置器件,一个下载电缆,或者通过一个主控制器,诸如MAX II器件、MCU等来配置FPGA。

配置数据通过DATA0在每个DCLK的上升沿送入器件。

FPGA配置方式选择引脚配置如图3.3所示图3.33.2.2电路连接:配置器件配置(图3.4)图3.4MAX II配置,图3.5图3.5MCU配置,图3.6图图3.63.2.3配置时序图3.73.2.4配置文件格式.rbf .hex .ttf3.3JTAG配置方式3.3.1原理对于cyclone II器件来说,JTAG配置方式优先于其他器件配置方式。

ALTERAFPGA在微处理器系统中的在应用配置

ALTERA FPG 在微处理器系统中的在应用配置摘要:ALTERA 公司SRAM 工艺可编程器件应用广泛,专用配置器件比较昂贵。

在具有微处理器的系统中, 使用微处理器系统的存储器来存储配置数据,并通过微处理器配置FPGA 这种方法几乎不增加成本。

微处理器根据不同的程序应用, 采用不同的配置数据对 FPGA 进行配置,使FPGA 实现与该应用有关的特定功能。

详细介绍了微处理器系统中连接简单的被动串行配置方法和被动并行异步配置方法。

关键词:在应用配置FPGA 配置被动串行被动并行异步可编程逻辑器件(PLD 广泛应用在各种电路设计中。

基于查找表技术、 SRAM 工艺的大规模PLD/FPGA 密度高且触发器多,适用于复杂的时序逻辑, 如数字信号处理和各种算法的设计。

这类器件使用SRAM 单元存储配置数据。

配置数据决定了 PLD 内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。

SRAM编程时间短,为系统动态改变PLD 的逻辑功能创造了条件。

但由于 SRAM 的数据是易失的,配置数据必须保存 在PLD 器件以外的非易失存储器内,才能实现在线可重配置(ICR )。

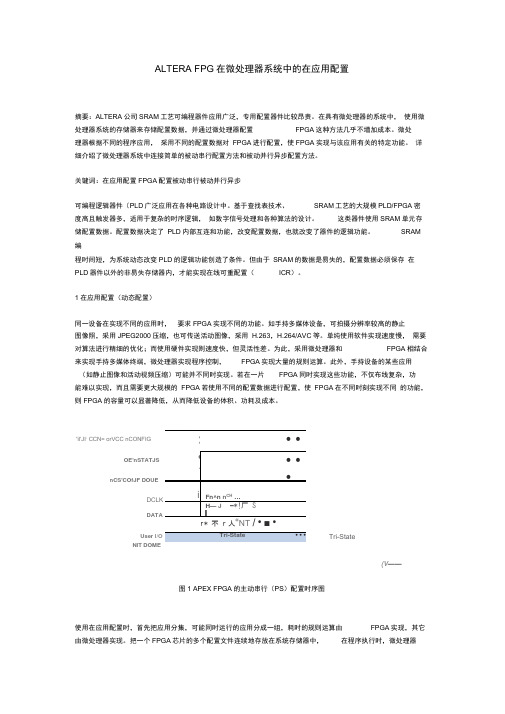

1在应用配置(动态配置)同一设备在实现不同的应用时, 要求FPGA 实现不同的功能。

如手持多媒体设备,可拍摄分辨率较高的静止 图像照,采用JPEG2000压缩,也可传送活动图像,采用 H.263,H.264/AVC 等。

单纯使用软件实现速度慢, 需要对算法进行精细的优化;而使用硬件实现则速度快,但灵活性差。

为此,采用微处理器和 FPGA 相结合来实现手持多媒体终端,微处理器实现程序控制,FPGA 实现大量的规则运算。

此外,手持设备的某些应用(如静止图像和活动视频压缩)可能并不同时实现。

若在一片FPGA 同时实现这些功能,不仅布线复杂,功能难以实现,而且需要更大规模的 FPGA 若使用不同的配置数据进行配置,使 FPGA 在不同时刻实现不同 的功能,则FPGA 的容量可以显著降低,从而降低设备的体积、功耗及成本。

Altera公司FPGA的配置

10

(4)PCB电路板上的10针连接插头

PCB板上的10针插头连接到FPGA器件的编程 或配置引脚上,ByteBlaster下载电缆的10针插座 连接到PCB板上的10针插头,ByteBlaster电缆通 过10针插头获得电源并下载数据到FPGA器件上。

编辑ppt

11

2. ByteBlasterMV并行下载电缆

编辑ppt

4

(2)电缆插头与插座

ByteBlaster与PC机并口相连的是25针插头,与FPGA 应用电路PCB电路板相连的是10针插座。编程数据从PC机 并口通过ByteBlaster电缆下载到电路板。连接示意图如 图6.1所示。

注意:利用 ByteBlaster下载电缆配置/编程3.3V器 件(如FLEX10KA、MAX7000A器件)时,要将电缆的VCC脚 连到5.0V电源,而器件的VCC脚连到3.3V电源。FLEX10KA 和 MAX7000A器件能够耐压到 5.0V,因此,ByteBlaster 电缆的5.0 V输出不会对 3.3 V器件造成损害,但5.0V电 源中应连接上拉电阻。

编辑ppt

15

(3)电缆插头与插座

ByteBlasterMV的25针插头,与ByteBlaster 下载电缆的区别仅是第15脚不同,ByteBlaster 连到GND,而ByteBlasterMV连到VCC。

ByteBlasterMV的10针插座与ByteBlaster电 缆的10针插座完缆

针对FPGA器件不同的内部结构,Altera公司 提供了不同的器件配置方式。Altera FPGA的配 置可通过编程器、JATG接口在线编程及Altera在 线配置等方式进行。

Altera器件编程下载电缆的有: ByteBlaster并行下载电缆,ByteBlasterMV并行 下载电缆,MasterBlaster串行/USB通信电缆, BitBlaster串口下载电缆。

配置 ALTERA_FPGA

刚学FPGA,唉,有点困难,呵,搞了很长时间,略懂一点,发个文章,保存经验。

先建一个工程,这个工程主要是为了验证FPGA的配置。

ALTERA 的FPGA配置有两种方式:一种是在线配置方式,即用.SOF(SRAM Object File)文件来配置FPGA。

这种方式断电后数据就消失。

另一种是通过EPCS来配置FPGA。

在这种方式下,我们要先把FPGA的配置数据下载到EPCS存储器中,这里有三种方式,可以进行,本文只讲两种,后一种在以后的博文中会体现。

先写用.SOF文件在线配置FPGA。

工具 EP2C8Q208C8N SDRAM EPCS4 CFI Flash QUTARTUS II 9.0 先建一个工程,目的是点亮开发板上的四个LED。

如上图,我们让四个LED两个亮起来,两个灭掉。

下一步是给其指定管角。

建一个TCL文件。

单击 FILE->new->tcl script file,这样就建立一个TCL(Tool Command Language)文件,来为其指定管角。

编辑之后,保存。

单击 Tools->TCL scripts…单击RUN,进行配置。

之后信息栏中会提示成功:下一步要对FPGA进行一些配置的设定。

点击Q II软件工具栏上的,进入此界面:在Device这一栏中,我们看右边,有我们所要用到器件,正确选择后,点击:,进入界面后,进行如下设定:将 unused pins 设为 as input tri-stated;再将dual-purpose pins 都设定为use as regular I/O,不能设定的就算了。

如下图。

好了,设定完了,就确定。

以上对FPGA的设计就算是完成了。

我们要生成.SOF文件和.POF文件,就要综合,编译。

点击工具栏上的:,进行综合编译。

这个时候可能会长一点,根据你的设计大小不同而不同。

之后会提示成功。

会有很多WARNINGS,这个没有关系,我们不去管它。

利用Altera增强型配置片实现FPGA动态配置

利用Altera增强型配置片实现FPGA动态配置在当今复杂数字设计中,大多采纳以"微控制器+"为核心的体系结构此体系结构中FPGA配置效率和灵便性的差异影响了产品的开周期和产品升级的易施性。

传统的FPGA配置计划(例如调试阶段的专用下载电缆方式。

成品阶段的专用配置片方式)在成本、效率、灵便性方面都存在着显然不足。

针对这样的实际问题,基于嵌入式微控制器与FPGA广泛共存于复杂数字系统的背景,借鉴软件"一机多能"的思想,提出了一种对现有传统FPGA配置计划硬件电路稍做调节并增强部分软件功能。

即可实现FPGA动态配置的计划。

本文将在介绍公司Stratix系列FPGA配置模式、FPGA配置流程、增加型配置片内部工作原理的基础上给出利用EPCI6实现FPGA动态配置的计划。

并给出软硬件接口电路。

2 FPGA配置方式可编程器件的配置方式分为主动配置和被动配置两类。

主动配置由可编程器件引导配置过程,被动配置则由外部处理器控制配置过程。

按照配置数据线数,器件配置可分为并行配置和串行配置两类。

串行配置以Bit(比特)为单位将配置数据载人可编程器件:而并行配置普通以Byte(字节)为单位向可编程器件载入配置数据。

被动配置按照配置数据与时钟的关系可分为同步和异步两种方式。

表1列举了Altera公司常用FPGA(Stratix、Cyclone、APEXⅡ、APEX20K、Mercury、ACE XK、FLEXlOK和FLEX6000)的配置方式。

3 FPGA配置流程FPGA的配置数据存储在内部SRAM单元中。

因为SRAM掉电后配置数据会走失,因此每次上电时必需重新将配置数据写入SRAM中。

这个过程称为FPGA的配置。

FPGA配置过程1所示。

表2为Stratix配置引脚定义。

第1页共6页。

6.2.3 Altera芯片配置电路设计

使用微处理器配置单个APEXⅡ、APEX20K、 APEX20KC、Mercury、ACEX1K、FLEX10K和 APEX20KE及 FLEX6000器件的配置电路如图 6.2.10所示。使用微处理器配置多个APEXⅡ、 APEX20K、APEX20KC、Mercury、ACEX1K、 FLEX10K和APEX20KE及 FLEX6000器件的配置电 路如图6.2.11所示。

图6.2.8 PS模式配置与芯片配置组合电路

多个APEXⅡ、APEX20K、APEX20KC、Mercury、 ACEX1K、FLEX10K和APEX20KE及 FLEX6000器件 的配置电路如图6.2.9所示。

图6.2.9 多个FPGA器件的配置电路

在图6.2.9中: (1)在进行多器件主动配置时,设计人员必 须从每个设计项目的SRAM目标文件(.sof)中产 生配置芯片的编程目标文件(.pof),即在MAX+ PLUSⅡ软件的 File菜单中打开 Combine Programming Files对话框,在该对话框中组合多 个.sof文件以形成一个.pof文件。对 APEX20K系列 器件,QuartusⅡ软件提供类似的选项,即在 QuartusⅡ软件的 Processing菜单中选择 Compiler Settings,并在 Compiler Settings 对话框中点击 Chips&Devices条,然后在Device&Pin Option对 话框中组合多个.sof文件以形成一个.pof文件。

(2)在器件链的最后一个器件的nCEO引脚端 不连接。 (3)对于APEX 20KE 和APEX 20KC系列器件, 上拉电阻是10kΩ。如果有其它器件与APEX 20KE 和APEX 20KC器件组合,在nSTATUS和 CONF_DONE引脚端也使用10kΩ的上拉电阻。

用CPU实现FPGA动态配置

经验与交流

EXP ERIENCE AND EXCHANGE

CHINA NEW TELECOMMUNICATIONS ( Te chnica l Edition )

基于查找表的

功放数字预失真方法

傅佳晨 石江宏

( 厦门大学 通信工程系 厦门 361005)

摘 要 对功率放大器的失真原理进行了数学 分 析 , 描 述 了 三 阶 , 五 阶 互 调 的 产 生 机 理 。介 绍 了 基 于 查找表的数字预失真的两种算法, 并对算法进行了仿真, 分析了算法的有效性。 关键词 AM- AM AM- PM 功放模型 查找表 数字预失真

( 1) 使用的配置文件是二进制的.rbf 文件。配置 文件.rbf 文件不是直接将存在 flash 上, 而是使用一 个脚本工具及将.rbf 文件转为.h 文件。这样可以把配 置文件作为一个头文件直接包含在软件版本里, 为 日后的升级带来了很多便利。这个脚本工具就不多 介绍了, 很容易实现。在.h 文件中,定义了一个字符数

1 引言

无线通信系统中, 为达到发射要求, 射频信号需 具有较高的功率, 因此需要通过功放将其放大, 以获 得所需信号功率值, 因此功放往往在非线性状态工 作, 这 些 非 线 性 将 产 生 如 AM—AM 转 换 、AM—PM 转换等谐波失真、互调失真等失真产物[1]。

工程上为避免非线性失真, 通常情况下, 功放从 饱和功率点作较大回退来满足线性放大需要, 但是, 这会导致功放效率下降和热扩散等向题。这就使设 计人员面临两种选择:或者采用以牺牲功放效率为代

( 6) 准备下一位数据, 并重复执行步骤 4、5, 直到 所有数据送出为止。

( 7) 此时 Conf_done 应变成 "1", 表明 FPGA 的配 置 已 完 成 。 如 果 所 有 数 据 送 出 后 , Conf_done 不 为 "1", 必须重新配置( 从步骤 1 开始) 。

Altera新型FPGA器件的配置方式

Altera新型FPGA器件的配置方式

张小平;赵不贿

【期刊名称】《微处理机》

【年(卷),期】2006(027)004

【摘要】介绍了如何对Altera的新型FPGA器件Cyclone系列进行配

置,Cyclone支持使用被动配置(PS)、主动配置(AS)、JTAG配置方式中的任何一种,或者是它们的组合配置方式.

【总页数】3页(P93-95)

【作者】张小平;赵不贿

【作者单位】江苏大学,镇江,212013;江苏大学,镇江,212013

【正文语种】中文

【中图分类】TP3

【相关文献】

1.中阶FPGA器件的新型安全解决方案 [J], Ted Marena

2.Altera SRAM型FPGA器件总剂量辐射损伤及退火效应 [J], 高博;余学峰;任迪远;王义元;李豫东;孙静;李茂顺;崔江维

3.FPGA器件在嵌入式系统中的配置方式的探讨 [J], 缪云青;李永刚

4.FPGA器件在嵌入式系统中的配置方式的探讨 [J], 缪云青;李永刚

5.FPGA器件的配置方式研究 [J], 宁李谱;杨宾峰;苗青林

因版权原因,仅展示原文概要,查看原文内容请购买。

AlteraFPGASoC搭建步骤

AlteraFPGASoC搭建步骤Altera SoC 官⽅搭建指南:官⽅⽂档中除了讲解搭建⽅法之外,还有很多原理性的介绍,感兴趣的朋友可以⾃⼰阅读。

准备⼯作:1. 安装Altera官⽅提供的IDE ( 和 ), 不需要安装DS-5. ⽂档中的⼯作是基于v15.0版本2. ⼀块FPGA SoC开发板。

官⽅Guide中的硬件平台是友晶系列的DE0-Nano-SoC,但对⼤多Altera板⼦都适⽤3. ⼀台Linux主机4. ⼀张SD卡5. ⽹络可以访问github搭建步骤:1. ⽣成Preloader2.配置和编译Bootloader (U-Boot)3. ⽣成和编译Device Tree4. 测试系统(⼀)5. 配置和编译Linux Kernel6. ⽣成Root Filesystem7. 测试系统(⼆)搭建⽅法:1. ⽣成Preloader下载并解压GHRD,并解压⾄某⽬录:tar -xvzf atlas_linux_ghrd.tar.gz运⾏EDS配置环境变量的脚本<path-to-soceds-tools>/embedded/embedded_command_shell.sh运⾏BSP Editor⼯具:cd atlas_linux_ghrdbsp-editor &将弹出如下窗⼝:配置BSP Editor:File→New HPS BSP在弹出的窗⼝中,点击"Preloader settings directory"右侧的"..."按钮,选择“atlas_linux_ghrd/hps_isw_handoff/soc_system_hps_0”,然后点击Open。

完成后的界⾯如下图,点击确定:在⽣成的窗⼝中,选中"FAT_SUPPORT",其他的使⽤默认,结果如下图:点击Generate,正常结束后点击Exit退出。

用CPU配置FPGA软件和硬件的详细描述

用CPU配置FPGA(一)概述一.概述二.目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对FPGA进行配置。

专用的EPROM价格不便宜,且大不跟上都是一次性OPT方式编程。

一旦更改FPGA设计,代价不小。

为了进一步降低产品的成本和升级成本,可以考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU 模拟专用EPROM对FPGA进行配置。

本文将以PowerPC860和EP1K30为例,讲解如何利用CPU来配置FPGA。

CPU配置FPGA的优点与Configuration EPROM方式相比本设计有如下优点:1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。

以ALTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的价格要几十元,容量1M位。

提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。

即使增加1Mb存储空间,通用存储器也会比FPGA专用EPROM便宜。

2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。

如果使用本设计对FPGA配置,选用可擦除的通用存储器保存FPGA的编程数据,更换FPGA版本,无须付出任何硬件代价。

这也是降低硬件成本的一个方面。

3.实现真正"现场可编程"--FPGA的特点就是"现场可编程",只有使用CPU对FPGA编程才能体现这一特点。

如果设计周全的话,单板上的FPGA可以做到在线升级。

4.减少生产工序--省去了对"FPGA专用EPROM"烧结的工序,对提高生产率,降低生产成本等均有好处。

对于双面再流焊的单板,更可省去手工补焊DIP器件的工序。

当然,与Configuration EPROM方式相比也有一些需要注意的的地方:1.需要CPU提供5根I/O线--一般来说,这并不困难。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录1 设计准则 (1)2 模块功能摘要 (1)3 参考资料 (1)4 基本原理 (1)4.1 硬件连接 (2)4.2 操作过程 (3)4.3 数据转换 (4)4.4 在线升级 (5)4.4.1 硬件要求 (6)4.4.2 软件要求 (6)4.4.3具体过程 (6)5 技术指标 (7)6 电原理图 (7)7 PCB图.................................................................................................... 错误!未定义书签。

8 结构图..................................................................................................... 错误!未定义书签。

9 输入、输出接口及性能参数................................................................. 错误!未定义书签。

10 软件 (7)11 元器件说明..................................................................................... 错误!未定义书签。

12 可编程器件说明............................................................................. 错误!未定义书签。

13 可信性设计说明............................................................................. 错误!未定义书签。

14 电源和接地..................................................................................... 错误!未定义书签。

15 成本预计 (7)16 背景资料 (7)16.1.1 性能 (8)16.1.2 特点 (8)17 使用、调试、维护说明 (8)17.1 调试环境................................................................................. 错误!未定义书签。

17.2 调试方法................................................................................. 错误!未定义书签。

17.3 故障解决方法 (8)18 经验教训 (8)19 应用示例 (9)19.1 FPGA在线更改配置 (9)19.2电缆下载 (10)19.3 应用示例之源程序 (10)用CPU对Altera公司FPGA进行配置功能模块设计1设计准则本设计是利用CPU对RAM-Based FPGA进行配置。

因此,对CPU子系统有一些要求,即CPU子系统应在FPGA被配置前可独立运行并访问所需资源。

CPU对FPGA进行配置所需的资源很少,一般来说,仅RAM和BootROM的访问而已。

当然,其他挂在CPU总线上的设备必须处于非访问态,FPGA所控制的设备也应处于非工作态或不影响其他设备工作的稳定态。

2模块功能摘要本模块属于电路级功能模块。

本模块设计是利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU模拟专用EPROM对FPGA进行配置,以降低硬件成本并实现FPGA的在线升级。

本模块将主要讨论对Altera的FPGA进行配置。

本模块设计已在MPC860和EP1K30环境下完成验证,适用于有5个多余I/O的CPU 对Altera FPGA的配置。

关键词:FPGA,配置,在线升级,Altera,CPU3参考资料ALTERA AN-116: Configuring SRAM-Based LUT DevicesALTERA: ACEX 1K Programmable Logic Device Family4基本原理RAM-Based FPGA由于SRAM工艺的特点,掉电后数据会消失。

因此,每次系统上电后,均需对FPGA进行配置。

对于Altera的FPGA,配置方法可分为:专用的EPROM (Configuration EPROM)、PS(Passive serial 无源串行)、PPS(Passive parallel synchronous 无源同步并行)、PPA(Passive parallel asynchronous 无源异步并行)、JTAG(不是所有器件都支持)。

图 1 FPGA配置时序本设计采用PS方式对FPGA进行配置,是基于如下几个方面的考虑:1.PS方式连线最简单2.与Configuration EPROM方式可以兼容(MSEL0、1设置不变)3.与并行配置相比,误操作的几率小,可靠性高图 2 PS配置时序只需利用CPU的5个I/O线,就可按图2所指示的时序对FPGA 进行PS方式的配置。

4.1硬件连接CPU仅需要利用5个I/O脚与FPGA相连,就实现了PS方式的硬件连接,具体信号见图 3 PS配置单片FPGA的硬件连接图 4 PS配置多片FPGA的硬件连接4.2操作过程CPU按下列步骤操作I/O口线,即可完成对FPGA的配置:1.nCONFIG=“0”、DCLK=“0”,保持2μS以上。

2.检测nSTATUS,如果为“0”,表明FPGA已响应配置要求,可开始进行配置。

否则报错。

正常情况下,nCONFIG=“0”后1μS内nSTATUS将为“0”。

3.nCONFIG=“1”,并等待5μS。

4.Data0上放置数据(LSB first),DCLK=“1”,延时。

5.DCLK=“0”,并检测nSTATUS,若为“0”,则报错并重新开始。

6.准备下一位数据,并重复执行步骤4、5,直到所有数据送出为止。

7.此时Conf_done应变成“1”,表明FPGA的配置已完成。

如果所有数据送出后,Conf_done不为“1”,必须重新配置(从步骤1开始)。

8.配置完成后,再送出10个周期的DCLK,以使FPGA完成初始化。

注意:1.DCLK2.步骤7和FLEX 10KE的。

如果是APEX 20K,则需要40个周期。

3.在配置过程中,如果检测到nSTATUS为“0”,表明FPGA配置有错误,则应回到步骤1重新开始。

图 5 操作流程框图4.3数据转换MAX+plus II生成的SOF文件不能直接用于CPU配置FPGA中,需要进行数据转换才能得到软件可用的配置数据。

具体步骤如下:1.进入数据转换对话框。

图 6 进入数据转换对话框2.选择需要转换的SOF文件,对于配置多个FPGA的场合,应选择所有的SOF文件并排好次序。

输出文件的格式选rbf(Sequential)。

图7 选择相应的输出数据格式4.4在线升级采用本模块的最大优点是可以实现单板FPGA的在线升级。

4.4.1硬件要求要实现在线升级,单板设计必须考虑以下几个问题:1.CPU的启动必须不依赖于FPGA,即CPU子系统应在FPGA被配置前可独立运行并访问所需资源。

CPU对FPGA进行配置所需的资源很少,一般来说,仅RAM和BootROM的访问而已。

2.FPGA配置前(或配置过程中)必须保证控制的设备处于非工作态或不影响其他设备工作的稳定态。

3.为了实现FPGA的在线升级,存放FPGA配置数据的存储器器必须是CPU可重写的,且此存储器应是非易失性的,以保证单板断电后,FPGA数据不需从后台重新获得。

4.4.2软件要求4.4.3具体过程结合图8的实例,对FPGA在线升级作一具体描述。

图8 FPGA在线升级1.使用编译和连接工具,将FPGA的第一个版本与MPC860的工作程序连接在一起,分别占用地址为0x70000-0x7FFFF和0x00000-0x6FFFF的存储空间。

2.单板启动时,MPC860自动将0x70000-0x7FFFF的数据下载到FPGA中,完成FPGA配置。

3.当FPGA需升级时,将新的RBF配置文件放在后台计算机中。

4.MPC860把BOOTROM的0x70000-0x7FFFF空间当作普通数据存储区,通过后台将新的RBF配置文件放在0x70000-0x7FFFF中。

5.MPC860调用BOOTROM中的FPGA配置子程序,对FPGA从新下载数据,完成FPGA升级。

5技术指标利用CPU完成对FPGA的配置。

本模块设计已在MPC860和EP1K30环境下完成验证,对于Altera的FPGA均适用。

6电原理图以MPC860和Altera EP1K30为例,电原理图如下:图9 电原理图7软件以MPC860小系统为例,我们可以将转换完成的RBF文件作为二进制文件,直接写到MPC860小系统的某一ROM/Flash区域。

由于这段数据的起始地址和长度都是已知的,相应的软件编写是很方便的。

12 应用示例中将给出相应的应用程序。

8成本预计与Configuration EPROM方式相比,本模块设计省去了Configuration EPROM的硬件成本。

同时,利用现有资源,不增加硬件成本。

9背景资料我们的产品中很多单板都用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对RAM-Based FPGA进行配置。

专用的EPROM价格不便宜,且基本上都是OTP。

一旦更换FPGA版本,代价不小。

为了进一步降低产品的成本,考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU模拟专用EPROM对FPGA进行配置。

9.1.1性能本模块设计严格按照FPGA的PS配置流程进行,并在配置过程中始终监测工作状态,在完善的软件配合下,可纠正如上电次序导致配置不正常等错误。

因此,采用此方法对FPGA 进行配置,性能将优于Configuration EPROM方式。

9.1.2特点与Configuration EPROM方式相比本设计有如下优点:1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。

以ALTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的批量价是30多元,容量1M位。

提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。

即使增加1Mb存储空间,通用存储器也会比FPGA 专用EPROM便宜。

2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。