quartus学习笔记

自己整理的:学习verilogDHL问题笔记——Quartus常见错误

⾃⼰整理的:学习verilogDHL问题笔记——Quartus常见错误我初学verilog语⾔,很多细节都没注意,按着⾃⼰的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同⼀变量赋值,这个细节⼀般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:⼤意了,端⼝类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时⽤⾮阻塞赋值,有时⽤阻塞赋值,这是禁⽌的。

在初学的时候,可能分得不是很清楚,所以在检查时,⼀定要⼀步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细⼼点。

FPGA学习笔记之引脚分配

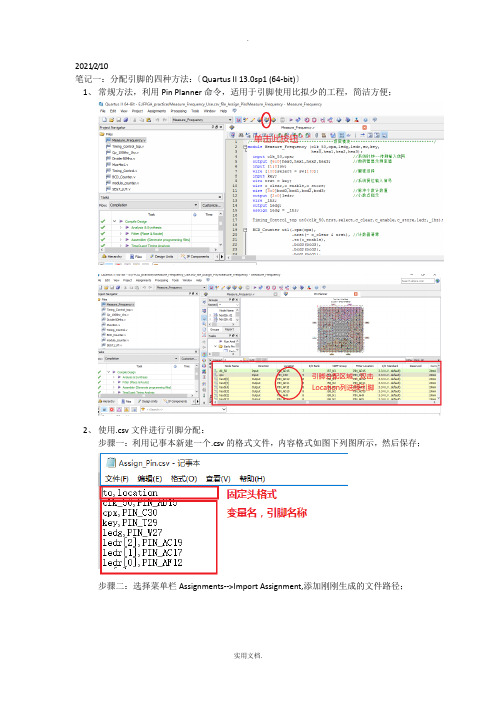

2021/2/10笔记一:分配引脚的四种方法:〔Quartus II 13.0sp1 (64-bit)〕1、常规方法,利用Pin Planner命令,适用于引脚使用比拟少的工程,简洁方便;2、使用.csv文件进行引脚分配:步骤一:利用记事本新建一个.csv的格式文件,内容格式如图下列图所示,然后保存;步骤二:选择菜单栏Assignments-->Import Assignment,添加刚刚生成的文件路径;步骤三:点击OK,引脚分配完成。

注意:.csv文件保存路径不要有中文,建议保存在工程文件夹下。

3、使用.qsf文件进行引脚分配:步骤一:在Quartus II中翻开.qsf文件〔系统默认生成.qsf文件,默认保存在该工程文件夹下〕步骤二:添加以下格式内容,格式如下列图所示;步骤三:点击保存,引脚分配完成。

4、使用.tcl文件进行引脚分配:步骤一:生成.tcl文件,选择菜单栏Project-->Generate Tcl File For Project,点击OK,默认保存路径为该工程文件夹;步骤二:添加以下格式内容,格式和.qsf文件格式一致;步骤三:选择菜单栏Tool-->Tcl Scripts,选择生成的.tcl文件,点击Run,引脚分配完成。

说明:在实际的应用过程中,我们应该根据工程的子模块个数和引脚的使用多少来选择适宜的引脚分配方式,笔者总结了以下几条:〔不喜勿喷,还望多多赐教〕1、工程中使用的引脚数为个位数时,并且特别少,建议使用常规方法,利用Pin Planner 命令进行引脚分配;2、文件进行引脚分配;如下图,.tcl文件中标识符和变量名已经给出,只需要输入对应引脚,比拟方便。

在多子模块的情况下,.tcl文件中没有给出标识符和变量名,这点需要注意。

3、多个子模块,使用引脚众多的情况下,利用.tcl文件、.csv文件和.qsf文件进行引脚分配大同小异,不过个人更喜欢利用.csv文件进行引脚分配,因为格式相对简单。

quartus_II教程笔记

***编译***(compilation , compile) 1、利用编译程序从源语言编写的源程序产生目标程序的过程。

2、用编译程序产生目标程序的动作。

编译就是把高级语言变成计算机可以识别的2进制语言,计算机只认识1和0,编译程序把人们熟悉的语言换成2进制的。

编译程序把一个源程序翻译成目标程序的工作过程分为五个阶段:词法分析;语法分析;语义检查和中间代码生成;代码优化;目标代码生成。

主要是进行词法分析和语法分析,又称为源程序分析,分析过程中发现有语法错误,给出提示信息。

***综合***(synthesis):将较高级抽象层次的设计描述自动转化为较低层次描述的过程。

综合有下面几种方式:1.将算法表示、行为描述转化到寄存器传输级(RTL),即从行为描述到结构描述。

2.将RTL级描述转化为逻辑门级(包括触发器),称为逻辑综合。

3.将逻辑门表示转化为版图表述,或转化到PLD器件的配置网表表示;根据版图信息能够进行ASIC生产,有了配置网表可完成基于PLD器件的系统实现。

***EDIF***是电子设计交换格式(Electronic Design Interchange Format)的英文字头缩写。

EDIF综合了多种格式中的最佳特性,1985年的EDIF100版本提供了门阵列、半导体集成电路设计和布线自动化交换信息的格式,而后的EDIF200版本是不同EDA厂家之间交换设计数据的标准格式。

EDIF格式解决的是用不同EDA厂家工具完成设计的数据交流问题。

***仿真***过程是正确实现设计的关键环节,用来验证设计者的设计思想是否正确,及在设计实现过程中各种分布参数引入后,其设计的功能是否依然正确无误。

仿真主要分为功能仿真和时序仿真。

功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。

1. 功能仿真 ( 前仿真 )功能仿真是指在一个设计中,在设计实现前对所创建的逻辑进行的验证其功能是否正确的过程。

Quartus II 学习笔记

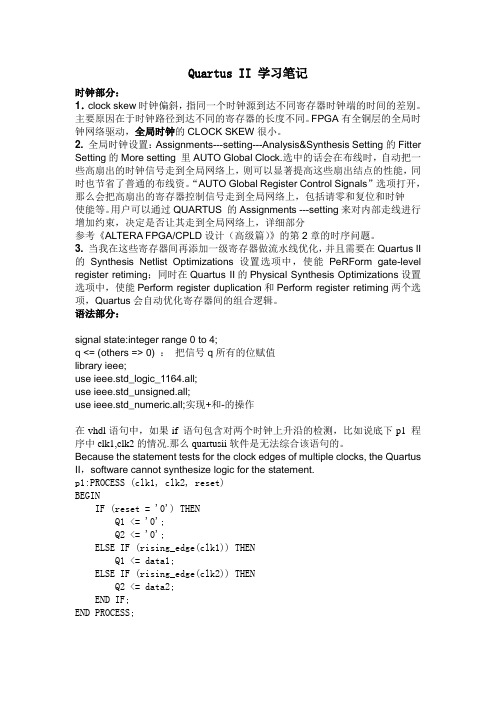

Quartus II 学习笔记时钟部分:1.clock skew时钟偏斜,指同一个时钟源到达不同寄存器时钟端的时间的差别。

主要原因在于时钟路径到达不同的寄存器的长度不同。

FPGA有全铜层的全局时钟网络驱动,全局时钟的CLOCK SKEW很小。

2. 全局时钟设置:Assignments---setting---Analysis&Synthesis Setting的Fitter Setting的More setting 里AUTO Global Clock.选中的话会在布线时,自动把一些高扇出的时钟信号走到全局网络上,则可以显著提高这些扇出结点的性能,同时也节省了普通的布线资。

“AUTO Global Register Control Signals”选项打开,那么会把高扇出的寄存器控制信号走到全局网络上,包括请零和复位和时钟使能等。

用户可以通过QUARTUS 的Assignments ---setting来对内部走线进行增加约束,决定是否让其走到全局网络上,详细部分参考《ALTERA FPGA/CPLD设计(高级篇)》的第2章的时序问题。

3. 当我在这些寄存器间再添加一级寄存器做流水线优化,并且需要在Quartus II 的Synthesis Netlist Optimizations设置选项中,使能PeRForm gate-level register retiming;同时在Quartus II的Physical Synthesis Optimizations设置选项中,使能Perform register duplication和Perform register retiming两个选项,Quartus会自动优化寄存器间的组合逻辑。

语法部分:signal state:integer range 0 to 4;q <= (others => 0) :把信号q所有的位赋值library ieee;use ieee.std_logic_1164.all;use ieee.std_unsigned.all;use ieee.std_numeric.all;实现+和-的操作在vhdl语句中,如果if 语句包含对两个时钟上升沿的检测,比如说底下p1 程序中clk1,clk2的情况.那么quartusii软件是无法综合该语句的。

学习verilog DHL问题笔记——Quartus常见错误

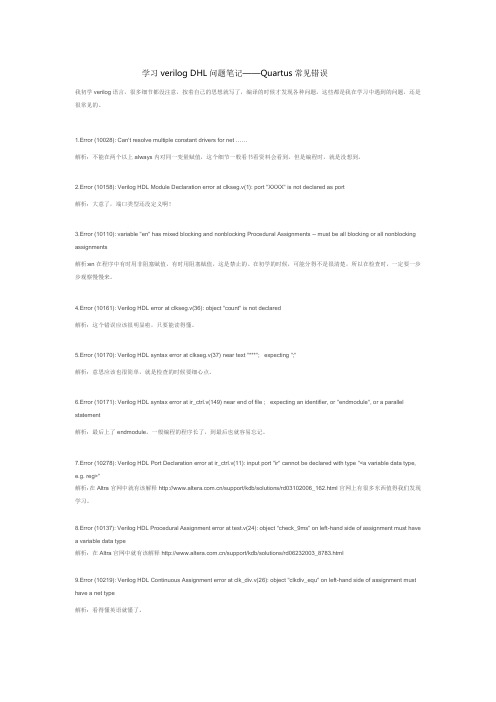

学习verilog DHL问题笔记——Quartus常见错误我初学verilog语言,很多细节都没注意,按着自己的思想就写了,编译的时候才发现各种问题。

这些都是我在学习中遇到的问题,还是很常见的。

1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

小梅哥FPGA学习笔记之Quartus II 15.0中仿真Altera三速以太网IP核

小梅哥FPGA学习笔记之Quartus II 15.0中仿真Altera三速以太网IP核2015年6月19日近期的项目需要用到网络端口通过UDP协议来进行数据的与PC机的交互。

FPGA系统中实现网口有多种方式,包括友晶的DE2-35开发板上使用的NIOS II处理器通过外部MAC芯片DM9000实现的web server,以及DE2-115开发板上使用NIOS II处理器与三速以太网(TSE)IP核实现web server,再就是W5X00系列的硬件TCP/IP网络芯片,配合FPGA实现网络数据传输。

当然,我自己也曾经在项目中直接使用完全自己编写的UDP协议网络收发逻辑配合外部网络PHY芯片,实现数据的收发。

早就知道Quartus II中提供了有三速以太网的MAC层IP,今天,在新项目的网络接口开工前,先通过仿真来了解一下该IP核的基本情况,相信该IP核的仿真结果一定很标准,能够为我后期手动写MAC层逻辑提供一个标准的时序参照。

这里我使用Altera 公司最新的FPGA开发工具Quartus II15.0(前天刚刚出了update1版本,不过公司网速慢,我还没来得及更新)来生成该以太网IP核以及设计实例,并使用Modelsim – Altera来仿真,来得到仿真波形。

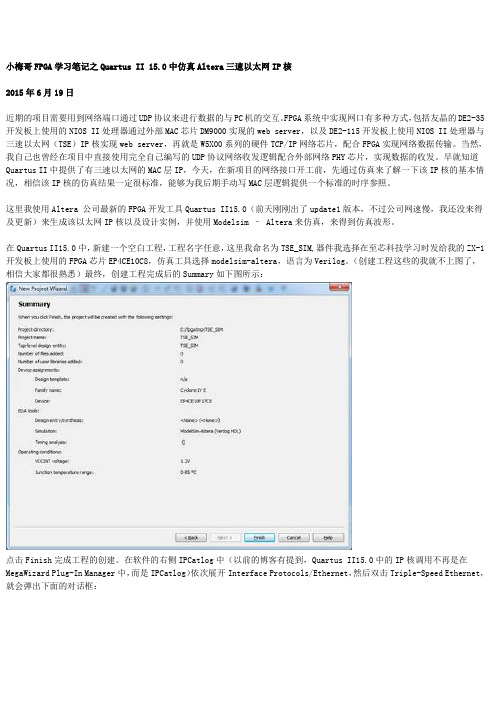

在Quartus II15.0中,新建一个空白工程,工程名字任意,这里我命名为TSE_SIM,器件我选择在至芯科技学习时发给我的ZX-1开发板上使用的FPGA芯片EP4CE10C8,仿真工具选择modelsim-altera,语言为Verilog。

(创建工程这些的我就不上图了,相信大家都很熟悉)最终,创建工程完成后的Summary如下图所示:点击Finish完成工程的创建。

在软件的右侧IPCatlog中(以前的博客有提到,Quartus II15.0中的IP核调用不再是在MegaWizard Plug-In Manager中,而是IPCatlog)依次展开Interface Protocols/Ethernet,然后双击Triple-Speed Ethernet,就会弹出下面的对话框:这里,语言选择Verilog,IP核被我自己命名为TSE,然后点击OK,则开始启动参数配置界面,启动过程很长,从点击OK到最终GUI弹出来大约需要20秒左右的时间,大家要耐心点,不要怀疑是否是软件出了故障。

quartus使用,李绍鹏数电实验2笔记,江苏科技大学

数电实验笔记Quartus II 7.2使用方法谨此献给亲爱的王晶、江洋洋、黄琳同学我相信很多事情只要不懈努力就会有奇妙且温暖的结果你们就是我的榜样数字电路系统设计流程根据设计项目逻辑抽象自动设计流程特点:核心步骤由计算机自动完成1原理图或HDL编辑2自动检测格式,排错3选择器件类型4逻辑综合:生成逻辑电路原理图文件5结构综合:自动生成逻辑电路布线布局图6自动装配:生成硬件构7建文件和时序测试文件8时序仿真和功能仿真9嵌入式逻辑分析仪实时测试硬件系统使用方法Q uartus II 7.2使用方法建立工程1建立工程双击桌面“Quartus II 7.2 (32-Bit)”单击“File”中的“New Project Wizard:Introduction”单击“next>”三行依次填入“D:\自己学号的文件夹”“要做实验的实验名”“与上一个空一致:要做实验的实验名”单击“next>”单击“next>”Family:选择“Cyclone”Available devices:选择“EP1C3T144C8”单击“next>”单击“next>”单击“finish”原理图 或VHDL语言语言2建立文件建立文件 原理图单击“file”中的“New”单击“Device Design Files”单击“Block Diagram/Schematic File”单击“OK”在Block.bdf中鼠标右键单击“insert”中的“symbol”在Libraries中选择要选用的元件或在name中输入所要选用的元件要说明的是:(1)用鼠标选中每个Symbol Properties 鼠标右键Rotate by Degrees 可以进行翻转(2)用鼠标双击每个Symbol Properties 可进行命名(3)多余项用GND谨此献给亲爱的王晶、江洋洋、黄琳同学 1谨此献给亲爱的王晶、江洋洋、黄琳同学 2 (4)输入用Vcc(5)选用的元件支持Ctrl+C 和Ctrl+V单击单击““file file””中的中的““Save as Save as””点击点击““保存保存””取底层文件名取底层文件名(.bdf (.bdf 原理图文件原理图文件))3编译编译单击单击““Processing Processing””中的中的““Start Compilation Start Compilation””单击“Tools”中的“Netlist Viewers”中的“RTL Viewer”4仿真文件仿真文件 导入节点导入节点 建立波形文件建立波形文件 矢量波形矢量波形 保存文件保存文件单击“file”中的“New”中的“Other Files”中的“Vector Waveform File”单击“OK”单击“View”中的“Utility Windows”中的“Node Finder”中的“list”把信号A B …… Y 拖到“name” 中关闭“Node Finder”单击“Edit”中的“End Time”并设置为“10.0ms”单击“OK”5点信号点信号 选一部分信号,单击 “Count Value”中的“Timing”中的“Count every” 并设置为“50.0us”。

QuartusII学习总结

QuartusII学习总结目录一、FPGA简介二、SOPC简介三、Quartus9.1安装过程及破解四、文本编辑五、原理图编辑六、混合编辑(方波应用实例)一、FPGA简介1.1 FPGA的定义FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

1.2 FPGA的现状中国每年对于FPGA设计人才的需求缺口巨大,FPGA设计人才的薪水也是行业内最高的。

目前,美国已有FPGA人才40多万,中国台湾地区也有7万多,而中国内地仅有1万左右,可见中国渴望有更多的FPGA人才涌现出来。

FPGA(现场可编程逻辑器件)产品的应用领域已经从原来的通信扩展到消费电子、汽车电子、工业控制、测试测量等广泛的领域。

而应用的变化也使FPGA产品近几年的演进趋势越来越明显:一方面,FPGA供应商致力于采用当前最先进的工艺来提升产品的性能,降低产品的成本;另一方面,越来越多的通用IP(知识产权)或客户定制IP被引入FPGA中,以满足客户产品快速上市的要求。

此外,FPGA 企业都在大力降低产品的功耗,满足业界越来越苛刻的低功耗需求。

1.3 FPGA的发展趋势分析(1)规模越来越大,集成度越来越高。

早期的FPGA规模只有几千门,2006年5月份,Xilinx公司推出世界上第一个65nm FPGA系列——Virtex-5。

基于65nm三极栅氧化层技术、11层铜布线工艺、低K材料、新型镍硅自对准技术、新型ExpressFabric技术和ASMBL架构,可以提供330 000个逻辑单元(可编程逻辑门约660万门)和1 200个用户I/O。

(2)速度不断提高,性能不断提升。

Xilinx 2006年推出的Virtex-5 LX 性能和利用率都很高,同时功耗大幅度降低。

(笔记)QuartusII9.1完全操作教程

(笔记)Quartus II 与DE2 入门指导(Digital Logic)(DE2)作者:yf.x来源:博客园发布时间:2010-03-04 21:18 阅读:1218 次原文链接[收藏] Version 1.0By yf.x03/03/2010Abstract通过一个简单的实例介绍Quartus II 9.1和DE2基本使用方法。

Introduction典型的计算机辅助设计流程开始新建一个项目(project)Verilog设计输入编译设计管脚分配仿真设计电路规划、配置FPGA器件测试设计的电路一个典型的FPGA计算机辅助设计流程如图1所示。

图1 FPGA CAD设计流程设计流程的步骤:•设计输入(Design Entry)-- 用原理图或者硬件描述语言说明设计的电路。

•综合(Synthesis)-- 将输入的设计综合成由FPGA芯片的逻辑元件(logic elements)组成的电路。

•功能仿真(Functional Simulation)-- 测试、验证综合的电路功能正确与否,不考虑延时。

•适配(Fitting)-- 将工程的逻辑和时序要求与器件的可用资源相匹配。

它将每个逻辑功能分配给最佳逻辑单元位置,进行布线和时序分析,并选定相应的互连路径和引脚分配。

•时序分析(Timing Analysis)-- 通过对适配电路的传播延迟的分析,提供电路的性能指标。

•时序仿真(Timing Simulation)-- 验证电路的功能和时序的正确性。

•编程和下载配置(Programming and Configuration)-- 在FPGA上实现设计的电路。

本文主要介绍Quartus II 的基本特性。

演示如何用Verilog HDL在Quartus II平台设计和实现电路。

包括:•创建一个项目(project)•用Verilog代码设计输入•综合•适配•分配管脚•仿真•编程与下载1 创建一个项目(1)启动Quartus II ,选择File > New Project Wizard,弹出窗口(图2)图2 新建项目向导(2)选择Next,如图3输入项目路径和项目名。

quartus学习笔记

关于quartus的功能学习:总体设计过程是这样的:Step1:创建工程Step2:文本输入Step3:编译包括:1、Analysis&Synthesis:分析和综合2、Fitters:布局布线3、Assembler:编译生成输出文件(sof,pof)4、Timing analyzer:时序分析5、EDA netlist writer:网表写入这五步。

注意编译后会有非常详细的编译报告。

也分别包括是这五步的报告,从硬件角度进行了非常完整的描述,可以通过点击工具栏的compilation report选项来看,包括:(一)compilation report:总体报告1、Flow summary:流程总结:包括最基本的工程信息,包括两个方面,一是工程,包括工程名,软件版本,是否时序分析等。

二是器件,包括器件型号,(1)LE使用率:combination连线使用率,logic register寄存器使用率。

这肯能正是LUT和LATCH结构(2)Pin占用率:(3)Virtual pin 占用率(4)Memory bit占用率(内嵌SRAM单元占用率)(5)Embedded multiplier 内嵌乘法器占用率(6)PLL占用率。

2、一些设置,log(二)Analysis&Synthesis:分析综合报告:(synthesis即为map)1、summary:与上面相同2、settings:非常详尽的综合设置,包括内嵌单元的使用方式,时空权衡,等等。

3、resource使用情况4、messages:警告与错误(三)fitter:布局布线报告:1、summary:同上2、settings:非常详尽的布线设置3、pin out file:固定引脚的分配情况,对引脚说明非常详细4、resource section :更为详尽的resource 使用情况。

以及介绍。

(四)Assembler:输出文件报告:1、generated files:输出文件的名称、位置2、device options:sof的配置,介绍3、device options:pof的配置,介绍(五)Timer analyzer:时间分析报告:1、频率2、建立保持时间等。

quartus&cpld学习报告

Quartus&cpld学习报告一、学习目的:1、掌握cpld基本编程2、熟悉quartus界面及使用方法3、掌握基本代码编写规范二、学习内容:2.1学习cpld代码编写规范希望在cpld入门之初,能够掌握规范的程序编写方法,使代码具有较高的可读性、可修改性、可移植性。

2.1.1命名的习惯:选择有意义的信号和变量名,对设计是很重要的。

命名的一般规则如下:✧使用有意义而有效的名字例如:循环指针通常默认使用I,没有必要使用loop_index作为指针名。

✧使用连贯的缩写长的名字对书写和记忆会带来不便,缩写的例子如下:Addr→address Pntr→pointer Clk→clock✧最右边的字符下划线表示低电平有效,高电平有效的信号不得以下划线表示:Rst_ Trdy_✧大小写原则:名字一般首字符大些,其余小写,两个词之间要用下划线连接。

如:Packet_addr Data_in Mem_wr✧自己定义的常数、类型等用大些标识:如:Parameter CYCLE=100;✧避免使用保留字,如:In,out,x,z等不能够作为变量、端口或者模块名✧一个module一个文件,且文件名能够与module名对应起来。

2.1.2模块设计Verilog设计一般都是层次型设计,也就是在设计中会出现一个或多个模块,模块间的调用在所难免。

✧每一个模块应在开始处注明文件名、功能描述、引用模块、设计者、设计时间及版权信息等。

代码中适当的地方需要添加说明和注释。

另外,必须将每次版本修改的信息按照时间一一详加叙述,以保持版本的可读性与继承性。

例如:/* ========================*\Filename ﹕RX_MUX.vAuthor ﹕Description ﹕Called by ﹕Top moduleRevision History ﹕99-08-01Revision 1.0Email ﹕M@Company ﹕Huawei Technology .IncCopyright(c) 1999, Huawei Technology Inc, All right reserved\* =========================*/✧用一个始终的上升沿或下降沿采样信号,不能一会儿用上升沿,一会儿用下降沿。

(笔记)QuartusII9.1完全操作教程

(笔记)Quartus II 与DE2 入门指导(Digital Logic)(DE2)作者:yf.x来源:博客园发布时间:2010-03-04 21:18 阅读:1218 次原文链接[收藏] Version 1.0By yf.x03/03/2010Abstract通过一个简单的实例介绍Quartus II 9.1和DE2基本使用方法。

Introduction典型的计算机辅助设计流程开始新建一个项目(project)Verilog设计输入编译设计管脚分配仿真设计电路规划、配置FPGA器件测试设计的电路一个典型的FPGA计算机辅助设计流程如图1所示。

图1 FPGA CAD设计流程设计流程的步骤:•设计输入(Design Entry)-- 用原理图或者硬件描述语言说明设计的电路。

•综合(Synthesis)-- 将输入的设计综合成由FPGA芯片的逻辑元件(logic elements)组成的电路。

•功能仿真(Functional Simulation)-- 测试、验证综合的电路功能正确与否,不考虑延时。

•适配(Fitting)-- 将工程的逻辑和时序要求与器件的可用资源相匹配。

它将每个逻辑功能分配给最佳逻辑单元位置,进行布线和时序分析,并选定相应的互连路径和引脚分配。

•时序分析(Timing Analysis)-- 通过对适配电路的传播延迟的分析,提供电路的性能指标。

•时序仿真(Timing Simulation)-- 验证电路的功能和时序的正确性。

•编程和下载配置(Programming and Configuration)-- 在FPGA上实现设计的电路。

本文主要介绍Quartus II 的基本特性。

演示如何用Verilog HDL在Quartus II平台设计和实现电路。

包括:•创建一个项目(project)•用Verilog代码设计输入•综合•适配•分配管脚•仿真•编程与下载1 创建一个项目(1)启动Quartus II ,选择File > New Project Wizard,弹出窗口(图2)图2 新建项目向导(2)选择Next,如图3输入项目路径和项目名。

quartus使用心得

quartus使用心得

我使用Quartus进行FPGA设计的心得体会

Quartus是一款强大的FPGA设计工具,我在使用它的过程中获得了很多经验和收获。

首先,Quartus提供了一个友好的用户界面,使我能够直观地进行设计和调试。

它的图形化界面使我能够快速创建和连接各种硬件模块,而无需编写繁琐的代码。

在Quartus中,我可以轻松地设计各种数字电路,例如逻辑门、寄存器和计数器等。

Quartus提供了丰富的元件库,我只需简单地拖拽和连接这些元件,即可完成复杂的数字电路设计。

这大大提高了我的工作效率。

Quartus还提供了强大的仿真功能,我可以通过仿真来验证我的设计是否正确。

在仿真过程中,我可以输入不同的测试数据,观察输出信号的变化,以确保设计的正确性。

这对于减少硬件调试的时间和工作量非常有帮助。

在使用Quartus的过程中,我还学会了如何使用约束文件来约束我的设计。

约束文件可以帮助我指定时钟频率、输入输出延迟等设计要求,以确保设计在实际硬件中能够正常工作。

通过合理地设置约束,我可以优化设计的性能和功耗,提高系统的整体性能。

总的来说,Quartus是一款功能强大、易于使用的FPGA设计工具。

它提供了丰富的元件库、直观的图形界面和强大的仿真功能,使我

能够快速、高效地进行FPGA设计。

在使用Quartus的过程中,我不仅学到了很多关于数字电路设计的知识,还提高了自己的工作效率。

我相信,在今后的工作中,Quartus将继续发挥重要的作用,帮助我完成更多的FPGA设计任务。

quartus学习笔记

注释无法直接打出中文,用文本编辑器打出后复制到注释处Quartus起名要求总共涉及到的名字有工程名,模块名,具体描述模块的Verilog文件名,原理图文件名。

工程名为A,那么最终需要编译的文件的名字必须和工程名相同。

只能将最终需要编译的原理图命名为A(可能一个工程下不只一个原理图,要将最后仿真需要的总原理图命名为A),而模块名一定不能为A。

在Verilog程序中描述模块时,可以给模块起名为B,程序完成后不需要编译,直接create symbol,在一个Verilog程序中可以定义多个模块,名字均不同,并且可以在一个模块中使用其他的模块,在create symbol时程序中有几个模块就会相应产生几个器件。

这个Verilog程序文件(.v文件)的名字可以为A或不为A。

总之:工程名为A,最终要编译的总原理图名一定要为A,原理图中使用的各模块名一定不能为A,定义这些模块的Verilog文件名可以为A或不为A。

建立相应的文件block diagram/schematic file 建立原理图、表模块文件vector waveform file 建立矢量波形文件,保存后仿真,分为功能仿真与时序仿真,功能仿真忽略了延时,时序仿真加上了延时方法:assignments-----settings,在simulation mode 中选择functional是功能仿真,timeing是时序仿真设置完成后,要生成功能仿真网络表processing--generatefunctional simulation netlist再点击按钮进行仿真规划引脚分布:assignments—pin planner(必须要选定器件才能规划引脚)触发器D:Q*=DJK:Q*=JQ’+K’QT:Q*=T’Q+TQ’SR:Q*=S+R’Q混合编辑自底向上:建立工程,建立2个(或以上)所需的VerilogHDL文件,并输入代码保存。

创建图元:file----creat/update----creat symbol files for current file,生成.bsf格式的图元文件。

第四讲QuartusII使用简介(自学).

用鼠标左键单击Update Symbol or Block,将出现升级向导窗口,引导 用户将原来的宏模块符号和框图升级为修改后的形式。

13

③ View

View菜单的 命令主要是 进行文件视 图操作,原 理图文件视 图菜单如图 所示。

14

◆ Utility Windows:通用窗口。 用鼠标左键单击Utility Windows,将出现下拉菜单。 单在该菜单中 列有Project Navigater(项目管理器)、Node Finder(节点查找器)、Tcl Console(工具命令语言控制器)、Messages(信息管理器)、Status(状 态管理器)、Change Manger(内容更改管理器)。 用鼠标左键单击其中某项,将打开或关闭该项所对应的窗口。 ◆ Full Screen:全屏。 用鼠标左键单击Full Screen,将打开或关闭全屏显示。

12

◆ Insert Symbol:插入符号。 用鼠标左键单击Insert Symbol,将出现插入模块符号窗口,引导用户 在原理图中插入宏模块符号。 ◆ Insert Symbol as Block:插入符号为模块。 用鼠标左键单击Insert Symbol as Block,将出现插入模块符号窗口, 引导用户在原理图中插入宏模块框图。该框图对宏模块进行了详细的 说明,但不能作为电路元器件使用。 ◆ Edit Selected Symbol:编辑所选符号。 选中某宏模块符号后,该功能被激活。用鼠标左键单击Edit Selected Symbol ,将出现宏模块符号编辑窗口。在该窗口中,可以修改宏模块 的外形和文本。 ◆ Update Symbol or Block:升级符号或模块。

19

◆ Generate PowerPlay Early Power Estimator File:创建功 率估算文件。 用鼠标左键单击Generate PowerPlay Early Power Estimator File,将出现对话框,引导用户给项目创建并保存功率估算文 件。 ◆ Locate:定位。 用鼠标左键单击Locate,将出现二级下拉菜单,引导用户实 行定位操作。 ◆ Set as Top-Level Entity:设为项层入口。 在具有多个源文件的项目中,必须有唯一的1个顶层文件。在 项目管理窗口中,选择某文件,再用鼠标左键单击Set as Top-Level Entity,将完成顶层文件的指定。 ◆ Hierarchy:层次。 用鼠标左键单击Hierarchy,可实现多层次文件的上下层次跳 转。

(My)EDA学习笔记

1、QuartusⅡ的存储目录应该是全英文的,出现以汉字命名的文件夹则无法编译。

2、波形文件若是未存储则无法时序分析。

3、.sof用于直接对FPGA进行配置;.pof用于CPLD器件编程或配置专用配置芯片;.bdf 为原理图文件;.bsf为图元文件。

4、添加到工程中的是设计源文件,可能是vhdl文件也可以是原理图文件。

5、Error (10437): VHDL Association List error at shuzizhong.vhd(37): positional associations must be listed before named associations----漏了“>”6、在波形仿真的情况下一定要注意设定合适的进制。

7、信号与变量的区别信号可以在实体、结构体、程序包中说明。

变量则在进程、子程序中说明。

赋值符号不同。

变量赋值立即生效,信号的赋值需经过一定的延时时间后才能得到,因此在顺序语句中如果对同一型号多次赋值只有最后一次赋值有效。

信号在整个结构体内有效,变量只是在所定义的进程或子程序中有效。

如果在进程或子程序之外使用变量的值,需要退出进程或子程序之前将变量的值付给信号。

8、数字电路的工作方式是系统各单元电路同时上电工作,单元电路内部按顺序工作。

9、vhdl综合器理解为不满足条件时,变量的原值保持不变。

10、z对应为高阻态。

11、查看状态机的状态转换图:tool---netlist viewers---state machine viewer。

12、“`”在左上角而不是…13、将欲调用的文件放在同一个工程文件中时不需加include,当存储在其他路径下时则需要。

例如:`include “c:/…/mux.v”14、always @ (1),always @ (*)都是一直循环的意思。

15、{ }是并置的意思。

网上暂未找到相关资料,书上见相关例题。

16、。

quartus学习笔记

Error: Node instance "inst" instantiates undefined最近搞nios一点积累希望对你有用,Error: Node instance "inst" instantiates undefined "b"这里b是个顶层文件,要是b包含的底层文件有些不能编译通过,一样会出现上面的问题,如果b包含的底层文件都能编译通过,最后编译工程出现上面的问题解决办法如下:方法一:在Assignments Settings的Files里指定该文件路径。

就是说把没有实例化的程序b添加进来然后编译工程即可。

方法二:在Assignments Settings的Libraries里指定该文件的存放目录quartus ii 仿真时间间隔怎么设置?end time是1us,间隔是160ns,每间隔中有8小格。

怎么设置啊?在edit中设置不行啊。

谁能告诉我啊end time 是仿真的总时间,而最小的间隔设置是用edit中的grid size进行设置的。

DATAa[7..0]中间两个点quartus ii功能仿真怎么操作在菜单栏下面的processing 中有一个simulaor tool 点开。

出现仿真的选项:simulation mode选成function 即功能仿真。

simulation input找到你自己的波形文件。

然后先点下generated functional simulation netist。

就是产生功能反正对应的网表文件。

最后点下左下方的start 仿真,完成之后,单击report即可查看功能仿真之后的波形了。

仿真时输入数据双击数值处,弹出表格输入数据即可COUT没有进位是没有满足进位要求,可有程序查看不同位的进位状态在波形仿真时Value --count value--中的第一项中设置数据类型,在第二项Timing中设置每一位的宽度,Octal显示三位以上是用Vhdl写的程序,编译后出现的是Warning: Found pins functioning as undefined clocks and/or memory enablesInfo: Assuming node "CLOCK" is an undefined clock没设定全局时钟方法:选择Assignment > Setting命令,在Timing Analysis Settings下选择的Classic Timing Analyzer SettingsDefault required fmax中填入时钟频率,点击下面的Indicidual Clocks按钮点击New点击Applies to node后面的“...”按钮,并在弹出的Node finder 中加入相应的CLK信号填上clock settings name(即为程序中CLK),设置时钟频率和占空比,点击OK然后一路OK下去,再编译的时候这个警告就会没有了。

Quartus 我的学习记录

Quartus 我的学习记录Notebook:[01] 我爱电子Created:2014/6/27 22:32Updated:2014/7/3 14:58 Tags:FPGA, 记录2014/6/251.设为顶层文件(Top-level Entity)2.建立波形文件2014/6/27 20:281.改变仿真时间 增大仿真时间在edit菜单下有个endtime选项 可以设置总体方针时间单个的在在前界面的左边有好多可以选波形的按钮 有一个是可以设定你想要的频率的2.注意级联芯片的翻转数电课设(一)Quartus II 工具介绍1.操作流程2.设备3.4.5.6.7.8.9.10.(二)全加器设计步骤(三)实验室装置介绍1.2.LED控制原理x`x`3.分配引脚4.全编译引脚分配后进行全编译才能在原理图中显示出引脚5. 下载程序6.引脚(1)LED点阵引脚开始设计按键扫描与点阵显示1.功能2.系统框图3. 设计步骤2014/6/30 20:411.利用总线 可以简化连线——————>>2.一定需要一个时钟3.不能忽略warnings,他可以提示有些线是连错的2014/7/3 10:07验收最后一天,紧张调试1.可以接线至LED灯观察按键情况注意LED的ACOM要接,否则不会亮,共阳共阴问题。

2.ROM 的时钟频率要高,1M3.单线使用add[3],这不同于add3--这是指命名为add3,而不是指总线的第三根。

4. 100Hz按键消抖使用一个D触发器,用100Hz频率,1Y输入(有抖) Anjian输出(消抖)5.高低位不一样6.可以用MUX(数据选择器)或 BUSMUX(总线数据选择器)作数据分配器,同一个数据分配给不同引脚比如,按键color选择用红色LED或绿色LED显示数据。

Quartus学习1

Quartus II

软件界面

工具栏

资源管理器

工程工作区 编辑状态显 示窗

信息显示窗

伪随机信号发生器

•

伪随机码是数字通信中重要信码之一,常作为数字通信中的基带信号源;扰码;误码测试; 扩频通信;保密通信等领域。 伪随机码的特性包括四个方面: 1. 由n级移位寄存器产生的伪随机序列,其周期为2n-1; 2. 信码中“0”、“1” 出现次数大致相等,“1”码只比“0”码多一个; 3. 在周期内共有2n-1游程,长度为i的游程出现次数比长度为i+1的游程出现次数多一 倍; τ 0 4. 具有类似白噪声的自相关函数,其自相关函数为: 1

24.下载界面

Thank You!

Quartus II 学习

浙江大学通信实验室 2013.3

Quartus II --- EDA开发软件

Quartus II 软件特点

1. Quartus II 软件是大型的EDA开发软件,支持电路规模达到300万门以上 2. 适合现代数字通信系统物理层开发,例如 全数字化调制解调器、纠错编码与译码、 自适应均衡技术、GSM基站、CDMA基站、宽带无线网络等。 3. 支持 电路图输入、VHDL输入、Verilog输入、AHDL输入和仿真 4. 具有丰富的通信模块:FIR滤波器、IIR滤波器、FFT、数字VCO、数字乘法器、各种 纠错编码与译码、DSP模块、各种RAM和ROM、PCI总线等。 5. DSPBuilder 新功能 ------ 可以将 Matlab做的系统仿真结果,直接转换成VHDL或 Verilog 语言描述的硬件电路 6. SOPCBuilder 新功能 ------ 支持system on chip 设计

7. Nios 新功能 ------ 嵌入式CPU 软核,同一个FPGA内可以同时装入多个CPU。

QuartusII增量编译的个人学习

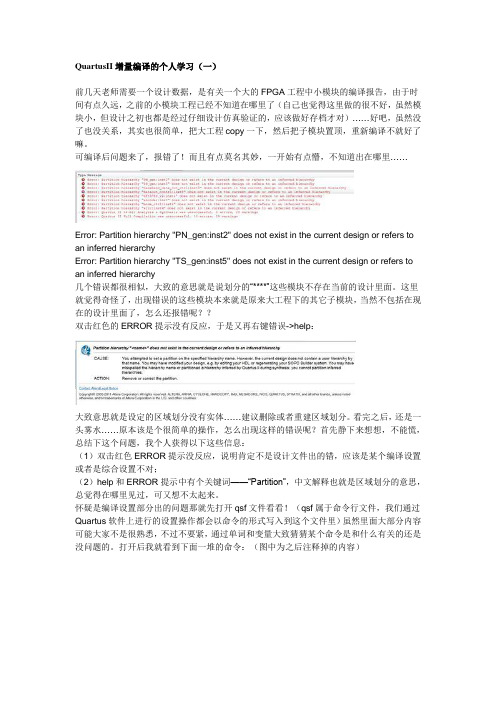

QuartusII增量编译的个人学习(一)前几天老师需要一个设计数据,是有关一个大的FPGA工程中小模块的编译报告,由于时间有点久远,之前的小模块工程已经不知道在哪里了(自己也觉得这里做的很不好,虽然模块小,但设计之初也都是经过仔细设计仿真验证的,应该做好存档才对)……好吧,虽然没了也没关系,其实也很简单,把大工程copy一下,然后把子模块置顶,重新编译不就好了嘛。

可编译后问题来了,报错了!而且有点莫名其妙,一开始有点懵,不知道出在哪里……Error: Partition hierarchy "PN_gen:inst2" does not exist in the current design or refers to an inferred hierarchyError: Partition hierarchy "TS_gen:inst5" does not exist in the current design or refers to an inferred hierarchy几个错误都很相似,大致的意思就是说划分的“****”这些模块不存在当前的设计里面。

这里就觉得奇怪了,出现错误的这些模块本来就是原来大工程下的其它子模块,当然不包括在现在的设计里面了,怎么还报错呢??双击红色的ERROR提示没有反应,于是又再右键错误->help:大致意思就是设定的区域划分没有实体……建议删除或者重建区域划分。

看完之后,还是一头雾水……原本该是个很简单的操作,怎么出现这样的错误呢?首先静下来想想,不能慌,总结下这个问题,我个人获得以下这些信息:(1)双击红色ERROR提示没反应,说明肯定不是设计文件出的错,应该是某个编译设置或者是综合设置不对;(2)help和ERROR提示中有个关键词——“Partition”,中文解释也就是区域划分的意思,总觉得在哪里见过,可又想不太起来。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

注释无法直接打出中文,用文本编辑器打出后复制到注释处Quartus起名要求总共涉及到的名字有工程名,模块名,具体描述模块的Verilog文件名,原理图文件名。

工程名为A,那么最终需要编译的文件的名字必须和工程名相同。

只能将最终需要编译的原理图命名为A(可能一个工程下不只一个原理图,要将最后仿真需要的总原理图命名为A),而模块名一定不能为A。

在Verilog程序中描述模块时,可以给模块起名为B,程序完成后不需要编译,直接create symbol,在一个Verilog程序中可以定义多个模块,名字均不同,并且可以在一个模块中使用其他的模块,在create symbol时程序中有几个模块就会相应产生几个器件。

这个Verilog程序文件(.v文件)的名字可以为A或不为A。

总之:工程名为A,最终要编译的总原理图名一定要为A,原理图中使用的各模块名一定不能为A,定义这些模块的Verilog文件名可以为A或不为A。

建立相应的文件block diagram/schematic file 建立原理图、表模块文件vector waveform file 建立矢量波形文件,保存后仿真,分为功能仿真与时序仿真,功能仿真忽略了延时,时序仿真加上了延时方法:assignments-----settings,在simulation mode 中选择functional是功能仿真,timeing是时序仿真设置完成后,要生成功能仿真网络表processing--generatefunctional simulation netlist再点击按钮进行仿真规划引脚分布:assignments—pin planner(必须要选定器件才能规划引脚)触发器D:Q*=DJK:Q*=JQ’+K’QT:Q*=T’Q+TQ’SR:Q*=S+R’Q混合编辑自底向上:建立工程,建立2个(或以上)所需的VerilogHDL文件,并输入代码保存。

创建图元:file----creat/update----creat symbol files for current file,生成.bsf格式的图元文件。

再新建原理图文件,上述图元文件就可以添加进原理图文件中了。

自顶向下:建立工程,建立原理图文件,放置符号块(block tool),在blockproperties中设置名字、I/O类型等,添加模块引线(node tool/ bus tool等)并设置属性(general选项卡设置I/O类型,mappings设置连线节点名称)。

右击符号块选择create design file form selected block,选择verilogHDL语言,单击OK,在生成的“.v”文件中修改代码VerilogHDL语言都是以module开始以endmodule结束的一段程序Module<模块名>(<端口列表>)<定义><模块条目>endmoduleverilogHDL文件名,模块名要相同才不会报错。

Assign连续赋值语句,一直检测等式左右两端变量,一旦其中一个发生变化,就重新赋值并传给等式左端输出。

在一个VerilogHDL文件中调用子模块:3个方法法一:首先建立工程(eg.lm),再建立VerilogHDL文件(lm),编写完成后将其设置为顶层文件,project --set as top level entiey。

再建立VerilogHDL文件(ll),当做子文件。

即可在lm中调用ll了。

VerilogHDL区分大小写;并且包含102个关键词,关键词必须小写Parameter(小写)进行参数声明,eg:parameter param1=count,BIT=1; 可以声明数字也可以是计算表达式。

预处理命令:见VerilogHDL程序设计与应用P19中的`是键盘左上角1旁边的那个键在英文状态下的输入法二:`include "F:\quartus\exercise\4调用子模块\ll.v"module lm(in1,in2,out);input in1,in2;output out;wire w1;ll ll1(in1,in2,w1);ll ll2(w1,w1,out);endmodule法三:等价于module ll(in1,in2,out);input in1,in2;output out;assign out=~(in1&in2);endmodulemodule lm(in1,in2,out);input in1,in2;output out;wire w1;ll ll1(in1,in2,w1);ll ll2(w1,w1,out);endmoduleO(o)八进制B(b)二进制D(d)十进制H(h)十六进制线网的声明语法:net_kind [msb:lsb] net1;Net_kind是网线类型,[msb:lsb]定义网线宽度,不写默认是1([2:0]宽度为3)net1网线变量的名称具体语句赋值总是从最低位(右侧)开始向最高位进行,任何多余的位都会被截断。

有两种赋值方法:一是“=”阻塞赋值,相当于串行,必须执行完这一句才能完成下一句;二是“<=”非阻塞赋值,看成并行,与下一句可以同时执行;但是只能给寄存器赋值。

If条件语句下没有大括号,用begin----end来代替用if语句最好加上else,用case,最好加上default,防止出现锁存器。

Begin If(……)q=d;end (1)1产生了锁存器,因为在不满足……时无定义,q还要保持原先的值Begin if(……) q=d;else q=0;end(2)2没有锁存器。

在不满足……时,q被赋值为0.顺序语句块Begin------------end并行语句块:并行执行,与书写顺序无关Fork ---------- joinCase语句:多选一Case(判断)A:---------------;B:---------------;Default:-----------;EndcaseCasez语句:条件表达式和分支表达式的值z被认为是无关值。

Casex:x,z被认为无关Casez(Ask)4’b1???:bus*1+=0;//ask第一位为1,忽略其他位,bus[1]赋值04’b01??:bus*0+=0; endcase//ask第2位为1,忽略其他,bus[1]赋值1. Initial语句只执行一次,一个模块可含多个initial,并行执行Always语句只要满足规定的条件,就一直执行;而initial语句整个仿真过程就执行一次。

always @(*) //@后加敏感信号列表,加*是省略Always #5 clk=~clk;时延五秒后再执行并且可以用@控制always语句的发生:always @(A)//语句发生的条件是A发生(有值改变)。

@定义边沿出发事件,有电平跳变就执行。

Wait控制电平敏感事件。

@(negedge A)B=$time;//在A的下降沿执行把当前时间赋给B;//negedge下降沿;posedge上升沿AlwaysWait (……) ----------;end 等待……值为1,向下执行。

屏幕显示display,输出会自动换行$display(‘”---------is %b”,A);//屏幕显示---------is A$write(“---------”)//输出不会自动换行,要加换行符\n循环语句Forever永远执行Repeat(loop_count)语句;loop_count控制循环次数While带条件循环表达式For类似C语言画原理图可以画出如图a的波形将图中的起始值进行更改即可位与和逻辑与&&是逻辑与即判断&&两侧的表达式是否都为真,都为真则此&&表达式值为真;&是按位与即将&两侧的数用二进制展开,每一位都求与运算(二进制与运算,跟逻辑与差不多),最后得到的二进制数即为结果;逻辑与结果只讲真和假,而按位与得出的却是实实在在的一个数数据流描述:采用assign连续赋值语句行为描述:使用always语句或initial语句块中的过程赋值语句结构化描述:实例化已有的功能模块或原语(`include”---.v ”.)四位全加器数据流描述module Full_Add_4b_1( A, B, Cin, Sum, Cout );input[3:0] A;input[3:0] B; input Cin;output[3:0] Sum; output Cout;assign {Cout, Sum} = A + B + Cin;endmodule行为描述module Full_Add_4b_2( A, B, Cin, Sum, Cout );input[3:0] A; input[3:0] B;input Cin;output[3:0] Sum; output Cout;reg [3:0] Sum; reg Cout;always @(A or B or Cin)begin{Cout, Sum} <= A + B + Cin;endendmodule基于时序逻辑的时候就用reg,组合逻辑一般用wire。

always中只能用reg,才能对其赋值。

Always模块内要被赋值的每一个信号都要定义为reg16’b1010_1011_1111_1010 “_”用于每四位数之间,增加程序可读性。

Parameter定义一个标识符代表一个常量。

Parameter A=3.14Memory类型Reg [n-1:0] memory [m-1:0]有m个字节,每个字节宽n位的存储器,名字是memory即定义了n个m位寄存器memory{a,b,c} 拼接运算符,接成几位的都可以Task任务与function函数Task <任务名> function[n-1:0] <函数名> Input ; input*+……;//定义输入端口Output ; begin……endBegin …… end endfunctionEndtask。