EDA第3章-宏功能模块

EDA技术实用教程-VHDL版课后答案

第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL 程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。

EDA技术(山东联盟)智慧树知到答案章节测试2023年泰山学院

绪论单元测试1.电子设计自动化的英文缩写是EDA。

A:错B:对答案:B2.EDA课程学习要求的五个一是指A:一种技术——EDAB:一种语言——HDLC:一套软件——QuartusIID:一套实验系统E:一个设计目标——数字系统F:一种器件——FPGA/CPLD答案:ABCEF3.学好EDA技术课程的标志是最后可以利用EDA方法设计出一个复杂的数字电子系统。

A:对B:错答案:A4.小组合作学习的目的包括A:相互激励克服困难B:通过交流锻炼表达能力C:分工协作以完成复杂任务D:独立工作展现个人魅力E:互帮互学答案:ABCE5.混合式学习的内涵包括A:独立学习与合作学习的混合B:线上线下学习的混合C:老师讲授与学生自学的混合D:理论学习与实践学习的混合答案:ABCD第一章测试1.基于硬件描述语言的数字系统设计目前不太常用的设计方法是()设计法。

A:自顶向下B:层次化C:自底向上D:顶层设计答案:C2.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程。

下面关于综合的描述错误的是A:综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;B:为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;C:综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是不唯一的。

D:综合是纯软件的转换过程,与器件硬件结构无关。

答案:D3.所列哪个流程是基于EDA软件的正确的FPGA / CPLD设计流程A:原理图/HDL文本输入→功能仿真→适配→编程下载→综合→硬件测试B:原理图/HDL文本输入→适配→综合→功能仿真→编程下载→硬件测试C:原理图/HDL文本输入→功能仿真→综合→适配→编程下载→硬件测试D:原理图/HDL文本输入→功能仿真→综合→编程下载→→适配硬件测试答案:C4.IP核在EDA技术和开发中具有十分重要的地位,以版图文件方式提供的IP被称为()。

EDA概述

第一章EDA概述1.1EDA技术的涵义一、EDA技术的涵义EDA(Electronic Design Automation)即电子设计自动化是指利用计算机完成电子系统的设计。

二、 EDA技术的分类EDA技术分:广义的EDA技术和狭义的EDA技术广义的EDA技术是指以计算机和微电子技术为先导,汇集了计算机图形学、数据库管理、图论和拓扑逻辑、编译原理、微电子工艺与结构学和计算数学等多种计算机应用学科最新成果的先进技术。

狭义的EDA技术是指以大规模可编程逻辑器件为载体,以硬件描述语言HDL为系统逻辑的主要表达方式,借助功能强大的计算机,在EDA 工具软件平台上,对用HDL描述完成的设计文件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、逻辑简化、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至对特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片ASIC(Application Specific Integrated Circuits)的一门新技术。

本书中提到的EDA技术指的是狭义的EDA技术。

1.2EDA技术的发展历史EDA技术的发展,大致经历了三个发展阶段:1.计算机辅助设计CAD 2.计算机辅助工程设计CAE 3.电子设计自动化EDA1.3 EDA技术的基本特征EDA技术的基本特征主要包括:1.EDA技术采用自顶向下的设计方法2.EDA技术的设计语言是硬件描述语言3.EDA技术具有逻辑综合和优化的功能4.EDA技术采用开放性和标准化的软件框架1.4 EDA的主要内容EDA技术主要这几方面的内容: 1.可编程逻辑器件2.硬件描述语言3.软件开发工具1.可编程逻辑器件可编程逻辑器件是一种由用户编程以实现某种逻辑功能的新型件。

可编程逻辑器件也称为可编程ASIC,它是EDA技术的物质基础。

2.硬件描述语言HDL语言是EDA技术的重要组成部分,它是一种用于描述硬件电子系统的计算机语言,它用软件编程的方式来描述电子系统的逻辑功能、电路结构和连接形式。

EDA技术3-QUARTUS使用方法

厦门理工学院通信系 刘虹

26

3.4 LPM_ROM宏模块应用

使用Quartus II 的MegeWizard Plug-In Manager中的宏功能模块可以帮助用户完成一些复 杂系统的设计,并可以方便地对现有的设计文件 进行修改。这些宏功能模块包括LPM(Library Parameterized Megafunction)、MegaCore(例 如FFT、FIR等)和AMMP(Altera Megafunction Partners Program,例如PCI、DDS等)。下面以 波形发生器的设计为例,介绍Quartus II宏功能 模块的使用方法。

厦门理工学院通信系 刘虹 2

为了方便电路设计,设计者首先应当在计 算机中建立自己的工程目录(如d:\myeda)。 将自己的全部EDA设计文件放在文件夹中。

注意:工程文件夹的名称不要使用汉字,最好 也不要使用数字。

厦门理工学院通信系 刘虹

3

Quartus II原理图输入的基本操作

编辑原理图

引脚锁定

厦门理工学院通信系 刘虹

24

在设计中嵌入SignalTap Ⅱ逻辑分析

仪有两种方法:第一种方法是建立一个

SignalTap Ⅱ文件(.stp),然后定义STP文

件的详细内容;第二种方法是用

MegaWizard Plug-InManager建立并配臵

STP文件,然后用MegaWizard实例化一个

HDL输出模块。

厦门理工学院通信系 刘虹

29

1. 加入计数器元件 用鼠标双击原理图编辑窗, 在弹出的元件选择窗的 “Libraries”栏目中选择 “arithmetic”的 “lpm_counter”(计数器) LPM元件。LPM是参数化的多功 能库元件,每一种LPM元件都 具有许多端口和参数,通过对 端口的选择与参数的设臵得到 设计需要的元件。

eda技术实用教程-veriloghdl答案

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

SoC设计与EDA工具第3章-SoC设计与EDA工具(1)

版图电路图同一性比较(LVS,Layout Versus Schematic)

用于比较版图和原理图在晶体管级的连接是否正确。

ECO步骤之后需要进行 逻辑等效性检查

P&R

Phy. V.

ECO

Equivalence Checking

静态时序分析(Static Timing Analysis)

静态时序分析工具通过计算路径上延迟的总和,并比较相对于预定义时钟的延迟, 来检查是否满足时序要求。它仅关注时序间的相对关系而不是评估逻辑功能。 不需要测试激励,检查所有路径的时序。 常用工具,如Synopsys公司的Primetime。

快速搭建虚拟原型机

电子系统级(ESL)设计

Electronic System Level(ESL)设计指系统级的设计方法,是从算 法建模演变而来,已经演变为嵌入式系统软硬件设计、验证、调试的 一种补充方法学。

ESL设计以抽象方式来描述SoC硬件系统,给软硬件工程师提供一 个虚拟的硬件原型平台,用以进行硬件系统结构的探测和软件程序的 开发。

设计约束

综合工具按照什么样的原则来综合电路,该电路所要达到的指标是什么。

主要包括时序、面积、功耗、可测性等。

逻辑综合的流程

工艺无关

工艺相关

逻辑综合的举例

RTL描述:

module magnitude_comparator(A, B, clk, rst_b, A_gt_B, A_lt_B, A_eq_B);

BIST的基本结构

边界扫描测试

边界扫描的原理是在核心逻辑电路的I/O都增加一个寄存器,通 过将这些I/O上的寄存器连接起来,可以将数据串行输入被测单 元,并且从相应端口串行读出。也可以并行输入,并行输出。

EDA技术与应用讲义 第3章 原理图输入设计方法 QUARTUS II版本

有了HDL语言后?

硬件设计人员 的工作过程

已经 类似与

软件设计人员,那么

这种模式的好处是?

让我们先看看原来是如何做的->

Compiler Netlist Extractor (编译器网表提取器)

❖ The Compiler module that converts each design file in a project (or each cell of an EDIF Input File) into a separate binary CNF. The filename(s) of the CNF(s) are based on the project name. Example

电路的模块划分

❖ 人工 根据电路功能 进行 模块划分

❖ 合理的模块划分 关系到

1. 电路的性能 2. 实现的难易程度

❖ 根据模块划分和系统功能 确定: PLD芯片型号

模块划分后,就可以进行 具体设计 了

设计输入

一般EDA软件允许3种设计输入:

1. HDL语言 2. 电路图 3. 波形输入

图形设计输入的过程

件电路图设计 5. 综合调试 6. 完成

设计的几个问题

❖ 如何组织多个设计文件的系统?,项目的概 念。

❖ 时钟系统如何设计?

❖ 电路的设计功耗

❖ 高速信号的软件和硬件设计

The end.

以下内容 为 正文的引用,

可不阅读。

常用EDA工具软件

❖ EDA软件方面,大体可以分为两类:

1. PLD器件厂商提供的EDA工具。较著名的如:

❖ 第三方工具软件是对CPLD/FPGA生产厂家开发软件的补 充和优化,如通常认为Max+plus II和Quartus II对 VHDL/Verilog HDL逻辑综合能力不强,如果采用专用的 HDL工具进行逻辑综合,会有效地提高综合质量。

第3章EDA设计流程及其工具

3.5 常用EDA工具软件

一、EDA工具大致可分为如下五个模块: 1、 设计输入编辑器。 2、仿真器。 3、HDL综合器。 4、适配器(或布局布线器)。 5、下载器。

二、 MAX+plusII概述

具有一定的典型性和一般性 MAX+plusII是Altera提供的FPGA/CPLD开发集成 环境,Altera是世界最大可编程逻辑器件供应商 之一。MAX+plusII界面友好,使用便捷,被誉 为业界最易用易学的EDA软件。

四、IP的发展: 1、初级阶段:免费使用,扩大营业

IC生产厂(Foundry) 扩大业务,提供精心设计并经过工 艺验证的标准单元,吸引IC设计公司(Fabless,无生产 线IC公司)成为他的客户,向客户提供相关的数据资料。 IC设计师十分乐于使用成熟、优化的单元完成自己的设 计,可提高效率,又可减少设计风险。一旦完成设计, 自然必须到这家Foundry去做工艺流片,这就使Foundry 达到了的目的。标准单元使用者与Foundry签订标准单 元数据不扩散协议,无须交单元库的使用费,没直接获 取IP的收益,扩大营业间接收到单元库的IP效益。

2、半定制或全定制ASIC 统称为掩模(MASK)ASIC,或直接称ASIC。 特点:用户设计IC,IC 厂家生产 三种级别: A、半导体元件、连线的大小与尺寸,电路全定 制 B、片内晶体管固定,用户设计连线 半定制 C、库内含标准单元,如SSI逻辑块、MSI逻辑 块、数据通道模块、存储器、IP,乃至系统级模 块。用户在EDA工具上进行开发/粘贴。

特点是必须首先关注并致力于解决系统最底层硬件 的可获得性,以及它们的功能特性方面的诸多细 节问题;在整个逐级设计和测试过程中,始终必 须顾及具体目标器件的技术细节。在这个设计过 程中的任一时刻,最底层目标器件的更换,或某 些技术参数不满足总体要求,或缺货,或由于市 场竞争的变化,临时提出降低系统成本,提高运 行速度等等不可预测的外部因素,都将可能使前 面的工作前功尽弃,工作又得重新开始。 结论:是一种低效、低可靠性、费时费力、且成本 高昂的设计方法。

EDA技术实用教程课后习题答案(20210110132612)

第一章1- 1 EDA技术与ASIC设计与FPGA开发有什么关系?答:利用EDA技术进行电子系统设计得最后目标就是完成专用集成电路ASIC得设计与实现;FPGA与CPLD就是实现这一途径得主流器件。

FPGA与CPLD通常也被称为可编程专用IC,或可编程ASIC o FPGA与CPLD得应用就是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)与ASIC设计,以及对自动设计与自动实现最典型得诠释。

1- 2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU得机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU得硬件结构,只能被动地为其特定得硬件电路结构所利用。

综合器将VHDL程序转化得目标就是底层得电路结构网表文件,这种满足VHDL设计程序功能描述得电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达得电路功能转化成具体得电路结构网表过程中,具有明显得能动性与创造性,它不就是机械得一一对应式得“翻译”,而就是根据设计库、工艺库以及预先设置得各类约束条件,选择最优得方式完成电路结构得设计。

1- 3什么就是综合?有哪些类型?综合在电子设计自动化中得地位就是什么?什么就是综合?答:在电子设计领域中综合得概念可以表示为:将用行为与功能层次表达得电子系统转换为低层次得便于具体实现得模块组合装配得过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域得综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)得表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA得配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中得地位就是什么?答:就是核心地位(见图1- 3)。

宏功能模块概述

宏功能模块概述

算术组件 门电路 I/O组件

累加器、加法器、乘法器和LPM算术函数

多路复用器和LPM门函数

时钟数据恢复(CDR)、锁相环(PLL)、双数据速率 (DDR)、千兆位收发器块(GXB)、LVDS接收器和发送器、 PLL重新配置和远程更新宏功能模块

存储器编译器

FIFO Partitioner、RAM和ROM宏功能模块

存储组件

存模块概述

1.1 知识产权核的应用

AMPP程序

MegaCore函数

OpenCore评估功能 OpenCore Plus硬件评估功能

宏功能模块概述

1.2 使用MegaWizard Plug-In Manager

<输出文件>.bsf : Block Editor中使用的宏功能模块的符号(元件)。 • <输出文件>.cmp : 组件申明文件。 • <输出文件>.inc : 宏功能模块包装文件中模块的AHDL包含文件。 • <输出文件>.tdf : 要在AHDL设计中实例化的宏功能模块包装文件。 • <输出文件>.vhd : 要在VHDL设计中实例化的宏功能模块包装文件。 • <输出文件>.v : 要在VerilogHDL设计中实例化的宏功能模块包装文件。 • <输出文件>_bb.v :VerilogHDL设计所用宏功能模块包装文件中模块的空体或

black-box申明,用于在使用EDA 综合工具时指定端口方向。 • <输出文件>_inst.tdf : 宏功能模块包装文件中子设计的AHDL例化示例。 • <输出文件>_inst.vhd : 宏功能模块包装文件中实体的VHDL例化示例。 • <输出文件>_inst.v : 宏功能模块包装文件中模块的VerilogHDL例化示例。

EDA技术实用教程习题答案——潘松_黄继业

EDA技术实用教程潘松黄继业第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点?答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中的地位是什么?答:是核心地位(见图1-3)。

eda芯片功能

8faddb 8位全加器

7480 门控全加器

7482 2位2进制全加器

7483 带快速进位的4位2进制全加器

74183 双进位存储全加器

74283 带快速进位的4位全加器

74385 带清零端的4位加法器/减法器

74824 带三态反相输出的9位总线接口触发器

74824b 带三态反相输出的9位D触发器

74825 带三态反相输出的8位总线接口触发器

74825b 带三态输出的8进制D触发器

74826 带三态反相输出的9位总线接口触发器

74826b 带三态反相输出的8进制D触发器

74376 带公共时钟和公共清零端4JK触发器

74377 带使能端的8进制D触发器

74377b 带使能端的8进制D触发器

74378 带使能端的16进制D触发器

74379 带使能端的4D触发器

74396 8进制存储寄存器

74548 带三态输出的8位两级流水线寄存器

lpm_fifo 参数化单时钟FIFO

lpm_fifo_dc 参数化双时钟FIFO

ROM的设计

lpm_rom

Quartus II开发软件中的宏模块--时序电路宏模块

Quartus II开发软件中的宏模块--时序电路宏模块

触发器

宏模块名称 功能描述

lpm_ff 参数化D或T触发器

unicnt 通用4位加/减计数器,可异步设置、读取、清零和级联的左/右移位寄存器

16cudslr 16位2进制加/减计数器,带异步设置的左/右移位寄存器

16cudsrb 16位2进制加/减计数器,带异步清零和设置的左/右移位寄存器

EDA技术--教学大纲

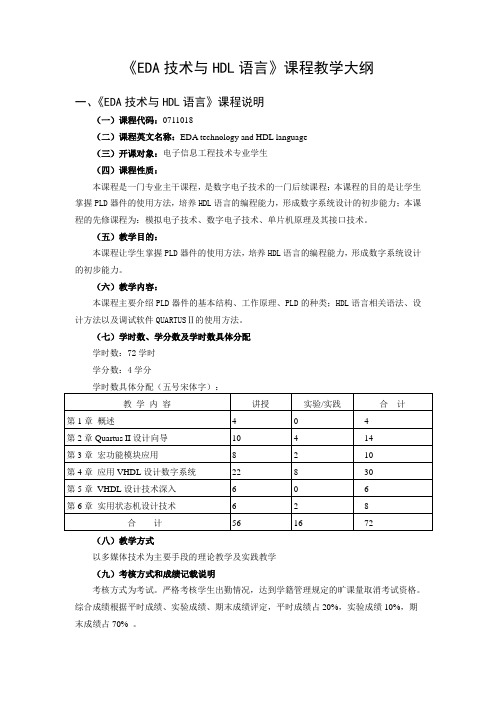

《EDA技术与HDL语言》课程教学大纲一、《EDA技术与HDL语言》课程说明(一)课程代码:0711018(二)课程英文名称:EDA technology and HDL language(三)开课对象:电子信息工程技术专业学生(四)课程性质:本课程是一门专业主干课程,是数字电子技术的一门后续课程;本课程的目的是让学生掌握PLD器件的使用方法,培养HDL语言的编程能力,形成数字系统设计的初步能力;本课程的先修课程为:模拟电子技术、数字电子技术、单片机原理及其接口技术。

(五)教学目的:本课程让学生掌握PLD器件的使用方法,培养HDL语言的编程能力,形成数字系统设计的初步能力。

(六)教学内容:本课程主要介绍PLD器件的基本结构、工作原理、PLD的种类;HDL语言相关语法、设计方法以及调试软件QUARTUSⅡ的使用方法。

(七)学时数、学分数及学时数具体分配学时数:72学时学分数:4学分(八)教学方式以多媒体技术为主要手段的理论教学及实践教学(九)考核方式和成绩记载说明考核方式为考试。

严格考核学生出勤情况,达到学籍管理规定的旷课量取消考试资格。

综合成绩根据平时成绩、实验成绩、期末成绩评定,平时成绩占20%,实验成绩10%,期末成绩占70% 。

二、讲授大纲与各章的基本要求第1章概述教学要点:通过本章的学习,使学生初步了解EDA的基本知识、常用的EDA基本工具使用方法和目标器件的结构原理。

教学时数:4学时教学内容:第一节 EDA技术第二节 EDA技术应用对象第三节 VHDL第四节 EDA的优势第五节面向FPGA的EDA开发流程一设计输入二综合三适配(布线布局)四仿真第六节 PLD一 PLD的分类二 PROM可编程原理三 GAL第七节 CPLD的结构与可编程原理第八节 FPGA的结构与工作原理一查找表逻辑结构二 FPGA的结构与原理第九节硬件测试技术一内部逻辑测试二 JTAG边界扫描测试第十节 FPGA/CPLD产品概述一 Altera公司FPGA和CPLD器件系列二 Lattice公司CPLD器件系列三 Xilinx公司FPGA和CPID器件系列第十一节编程与配置第十二节 FPGA配置器件第十三节 Quartus II2第十四节 IP核第十五节 EDA的发展趋势第2章 Quartus II设计向导教学要点:通过本章的学习,使学生掌握Quartus II软件的基本使用方法,学会图形输入法的EDA 设计过程。

EDA技术习题.

第一章EDA技术概述填空题1.一般把EDA技术的发展分为_______、_______和________三个阶段。

2.在EDA发展的_________阶段,人们只能借助计算机对电路进行模拟、预测,以及辅助进行集成电路版图编辑、印刷电路板(PCB)布局布线等工作。

3.在EDA发展的_______阶段,人们可与将计算机作为单点设计工具,并建立各种设计单元库,开始用计算机将许多单点工具集成在一起使用。

4.EDA设计流程包括_________、__________、__________和_________四个步骤。

5.EDA的设计验证包括________、__________和_________。

6.EDA的设计输入方式主要包括________、________和_________。

7.文本输入是指采用_________进行电路设计的方式。

8.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为_______。

9.时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为________或_______。

10.当前最流行的并成为IEEE标准的硬件描述语言包括_________和________.11.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为_______的设计法。

12.EDA工具大致可以分为________、_______、_______、________以及_____等5个模块。

13.将硬件描述语言转换为硬件电路的重要工具称为_______。

单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( ).①设计输入②设计输出③仿真④综合2.在设计输入完成后,应立即对设计文件进行()①编辑②编译③功能仿真④时序仿真3.在设计处理工程中,可产生器件编程使用的数据文件,对于CPLD来说是产生()①熔丝图②位流数据③图形④仿真4.在设计处理过程中,可产生供器件编程使用的数据文件,对于FPGA来说是生成()①熔丝图②位流数据③图形④仿真5.在C语言的基础上演化而来的硬件描述语言是()①VHDL②Verilog HDL③AHD④CUPL6.基于硬件描述语言HDL的数字系统设计目前最常用的设计法称为()设计法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

22

实验三/作业

4.1 采用Quartus II软件的宏功能模块lpm_counter设计 一个模为60的加法计数器,进行编译和仿真,查看仿真结果。 4.3 先利用LPM_ROM设计8位×8位乘法器,进行编译和仿 真,查看仿真结果。 4.4 用数字锁相环实现分频,假定输入时钟频率为10MHz, 想要得到6MHz的时钟信号,试用altpll宏功能模块实现该电 路。

19

计数器74161设计举例

模10计数器

20

仿真结果

模10计数器仿真波形

21

实验二/作业

4-1 基于Quartus II软件,用D触发器设计一个2分频电路,并做波形 仿真,在此基础上,设计一个4分频和8分频电路,做波形仿真。 4-2 基于Quartus II软件,用7490设计一个能计时(12小时)、计分 (60分)和计秒(60秒)的简单数字钟电路。设计过程如下: (1)先用Quartus II的原理图输入方式,用7490连接成包含进位输出 的模60的计数器,并进行仿真,如果功能正确,则将其生成一个部件; (2)将7490连接成模12的计数器,进行仿真,如果功能正确,也将其 生成一个部件; (3)将以上两个部件连接成为简单的数字钟电路,能计时、计分和计秒, 计满12小时后系统清0重新开始计时。

24

23

实验报告要求

(4) 实验报告: a.简单叙述设计流程(可以用流程图); b.给出各层次的原理图; c.给出各层次的综合报告; d.给出各层次的仿真波形图(包括功能仿真和时序仿真,注 意要把尽可能多的信息放在同一个仿真图里,并且在仿真 图上标注必要的信息,标注不规定标的地方和数量,每人 根据自己的理解标注,越多越好)。 e.给出时序仿真的延时、最大工作频率、建立时间和保持 时间的情况。

第4 章

基于宏功能模块的设计

1

第4章

基于宏功能模块的设计

乘法器模块

内容

计数器模块 锁相环模块 存储器模块 其他模块

2

4.1 乘法器模块

Megafunction库是Altera提供的参数化 模块库。从功能上看,可以把 Megafunction库中的元器件分为: 算术运算模块(arithmetic) 逻辑门模块(gates) 储存模块(storage) IO模块(I/O)

片对锁相环的支持程度不同,但是基本的参数设置大致

相同,下面便举例说明altpll的应用。

8(1)输入altplFra bibliotek宏功能模块选择芯片和设置参考时钟

9

锁相环控制信号设置

10

输入时钟设置

11

(2)编译和仿真

锁相环电路

功能仿真波形

12

4.6 存储器模块

ROM(Read Only Memory,只读存储器)是存储器的 一种,利用FPGA可以实现ROM的功能,但其不是真正意义 上的ROM,因为FPGA器件在掉电后,其内部的所有信息都 会丢失,再次工作时需要重新配置。 Quartus II提供的参数化ROM是lpm_rom,下面用一 个乘法器的例子来说明它的使用方法,这个例子使用 lpm_rom构成一个4位×4位的无符号数乘法器,利用查表 方法完成乘法功能。

13

数据线、地址线宽度设置

14

控制端口设置

15

添加.mif文件

16

如下图所示就是基于ROM实现的4位×4位的无符号 数乘法器电路图,其参数设置为: LPM_WIDTH=8 LPM_WIDTHAD=8 LPM_FILE=mult_rom.mif

17

仿真结果

18

4.7 其他模块

Maxplus2库主要由74系列数字集成电路组成,包括 时序电路宏模块和运算电路宏模块两大类,其中时序电 路宏模块包括触发器、锁存器、计数器、分频器、多路 复用器和移位寄存器,运算电路宏模块包括逻辑预算模 块、加法器、减法器、乘法器、绝对值运算器、数值比 较器、编译码器和奇偶校验器。 对于这些小规模的集成电路,在数字电路课程中有详细 的介绍。他们的调入方法和Megafunction库中的宏模 块是一样的,只是端口和参数无法设置。

3

4.3 计数器模块

计数器输出端口宽度和计数方向设置

4

计数器模和控制端口设置

5

更多控制端口设置

6

lpm_counter计数器功能仿真波形

模24方向可控计数器电路

7

4.5 锁相环模块

参数化锁相环宏模块altpll以输入时钟信号作为参考信

号实现锁相,从而输出若干个同步倍频或者分频的片内 时钟信号。与直接来自片外的时钟相比,片内时钟可以 减少时钟延迟,减小片外干扰,还可改善时钟的建立时 间和保持时间,是系统稳定工作的保证。不同系列的芯