宏功能模块与IP应用分析

第7章 宏功能模块的应用

7.2 存储器设计

7.2.1 ROM设计 设计

lpm_type => "LPM_ROM", lpm_width => 8, lpm_widthad => 6) PORT MAP ( outclock => outclock, address => address, inclock => inclock, q => sub_wire0 ); END SYN;

7.2 存储器设计

7.2.1 ROM设计 设计

图7.2 设置数据

图7.3 数据表

7.2 存储器设计

7.2.1 ROM设计 设计

填入数据后如图7.4所示

图7. 4

填入数据

7.2 存储器设计

7.2.1 ROM设计 设计 用鼠标右键单击窗口边缘的地址栏弹出格式选择窗 口,可以从中选择不同的地址格式和数据格式。表 中任意数据对应的地址为左列数和顶行数之和。 例如,表中任意一个数据87对应的地址为左列 16,顶行3,则地址为16+3=19, 若用 16进制表示为13H,表示存储器地址为13H 内的数据为87。完成数据输入后,保存文件并命 名名为“rom.mif”。

图7.11

7.2 存储器设计

7.2.1 ROM设计 设计

(4) ROM创建完成后,将生成的文件为rom.vhd(既可以用于原理图编 辑也可以用于顶层文件的实例化),将ROM文件夹中的rom.vhd打开, 其代码如例7.1所示。 【例7.1】ROM的VHDL源代码 LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY lpm; USE lpm.all; ENTITY room IS PORT( address : IN STD_LOGIC_VECTOR (5 DOWNTO 0); inclock : IN STD_LOGIC ; outclock : IN STD_LOGIC ; q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)); END room;

EDA技术P10-宏模块和IP使用方法新

什么是IP?

知识产权(IP)是指专利、商标、版权等形式的法律保护下的创意和创新。

宏模块与IP的区别

宏模块是具体的硬件设计,而IP是具备知识产权的创新设计,可以包含宏模块。

宏模块和IP的使用价值

宏模块和IP的使用可以加快电路设计过程、提高设计的可靠性以及降低开发成 本。

EDA技术P10-宏模块和IP 使用方法新

本演示介绍EDA技术中的宏模块和IP的使用方法。探索它们的定义、差异、设 计流程、测试与验证以及应用领域。了解宏模块和IP在电路设计中的重要作用。

EDA技术简介

电子设计自动化(EDA)是使用计算机软件和工具来设计、分析和验证集成电路系统的方法。

什么是宏模块?

如何使用宏模块和IP?

使用宏模块和IP要注意选择适合项目需求的设计,灵活运用标准接口和库。

宏模块的设计流程

1

设计

2

使用EDA工具进行宏模块的设计。

3

需求分析

确定宏模块的功能和特性。

验证

对宏模块进行功能验证和仿真。

IP的设计流程

1

需求分析

确定IP的功能和特性。

设计

2

使用EDA工具进行IP的设计。

3

验证

对IP进行功能验证和仿真。

宏模块的测试与验证

测试和验证宏模块的功能和性能是确保其正确工作的关键步骤。

IP的测试与验证

测试和验证IP的功能和性能是确保其正确工作的关键步骤。

宏模块和IP的维护

定期进行宏模块和IP的维护,包括修复错误、改进性能和支持新的软件和硬件 标准。

常见的宏模块

常见的宏模块包括时钟模块、存储器控制器和通信接口。

第6章 宏模块和LPM函数的应用(CPU)

第6章 宏模块和LPM函数的应用

固核(Firm Core)

固核比软核有更大的设计深度,己完成了门级综合、时序 仿真并经过硬件验证,以门级网表的形式提交使用。 只要用户提供相同的单元库时序参数,一般就可以正确完 成物理设计。

固核的缺点是它与实现工艺的相关性和网表的难读性。前 者限制了固核的使用范围,后者则使得布局布线后发生的 时序问题难以排除。

LPM模块的使用

FPGA-CPLD原理及应用

第6章 宏模块和LPM函数的应用

知识要点

LPM功能模块 LPM: library of Parameterized Modules

参数化的模块库,其模块使用参数和端口信号进 行描述,通过设置参数和端口信号,可以实现不 同的功能。其模块可称之为参数化模块或者LPM模 块或者LPM宏功能块。

(3) 使用端口和参数定义生成宏功能模块

计数器 乘法器 RAM 加法/减法器 乘-累加器和乘-加法器 移位寄存器

FPGA-CPLD原理及应用

第6章 宏模块和LPM函数的应用

6.2 LPM模块应用实例

使用LPM_COUNTER模块实现数控分频器 各端口信号的意义和设置 参数的设置 分频比

软核为后续设计留有比较大的空间,使用者可以通过修 改源码,完成更具新意的结构设计,生成具有自主版权 的新软核。 由于软核的载体HDL与实现工艺无关,使用者要负责从 描述到版图转换的全过程,模块的可预测性低,设计风 险大,使用者在后续设计中仍有发生差错的可能,这是 软核最主要的缺点。

FPGA-CPLD原理及应用

模块设置 参数:设置大小; 端口信号设置:设置使用哪些端口信号和信号属 性等,其中输入端口信号有缺省值,也可以自己 设置。

精品课件-硬件描述语言与FPGA设计技术(肖闽进)-第6章 宏功能模块与IP应用

f sin_o[9..0] f cos_o[9..0]

out_v alid

inst

OUTPUT OUTPUT

FS[9..0] FC[9..0]

嵌入式逻辑分析仪测试波形

6.6 LPM嵌入式锁相环设计

Altera 的FPGA器件CycloneII/III/IV及 StraixII/III/IV等系列中含有高性能的嵌入式模拟锁相 环,其性能远优于普通数字锁相环。这些锁相环PLL可以 与一输入的时钟信号同步,并以其作为参考信号实现锁 相,从而输出一至多个同步倍频或分频的片内时钟,以 供逻辑系统应用。与直接来自外部的时钟相比,这种片 内时钟可以减少时钟延时和时钟变形,减少片外干扰; 还可以改善时钟的建立时间和保持时间,是系统稳定工 作的保证。

aclr

8 bits 128 words

OUTPUT

CLKOUT

OUTPUT OUTPUT

ADDR[6..0] Q[7..0]

sin2_rom

address[6..0]

q[7..0]

inclock

inst2 Block ty pe: AUTO

OUTPUT

COUT

6.6.2锁相环仿真测试和硬件特性 锁相环仿真波形

加入NCO授权文件和Quartus II授权文件。这里设授权文 件位置路径:C:\altera\90\license.DAT。有了授权文 件,在Option对话框的Licensed AMPP/MegaCore functions 栏中可以看到FIR、PCI、NCO等IP的授权码, 这样就可以编译出能够写Flash的SOF文件。也可以先转 变为间接配置编程文件写入EPCS Flash。

6.1 LPM存储器设计 6.1.1 ROM模块设计

【Verilog】第7章 宏功能模块与IP应用

7.10 使用IP Core设计FIR滤波器

7.10 使用IP Core设计FIR滤波器

7.11 8051单片 机IP核应 用

7.11 8051单片机IP核应用

7.11 8051单片机IP核应用

7.12 DDS实现原理与应用

7.12.1 DDS实现原理

7.12 DDS实现原理与应用

7.12.1 DDS实现原理

实验与设计

7-7 4X4阵列键盘键信号检测电路设计

(1)实验原理:

实验与设计

7-7 4X4阵列键盘键信号检测电路设计

(2)实验任务1: (3)实验任务2:

(4)实验任务3: (5)实验任务4: (6)实验任务5: (7)实验任务6: 5E+系统演示示例:/KX_7C5EE+/EXPERIMENTs/EXP31_SCAN_4X4KEY/。

接下页

接上页

7.4.4 Verilog的存储器描述及相关属性

4.文本方式调用存储器LPM模块

7.5 LPM_ROM的定制和使用示例

7.5.1 LPM_ROM的定制调用和测试

7.5 LPM_ROM的定制和使用示例

7.5.1 LPM_ROM的定制调用和测试

7.5 LPM_ROM的定制和使用示例

7.5.1 LPM_ROM的定制调用和测试

7.4 LPM 随机存储器的设置和调用

7.4.1 存储器初始化文件生成 2.建立.hex格式文件

7.4 LPM 随机存储器的设置和调用

7.4.2 LPM_RAM的设置和调用

7.4 LPM 随机存储器的设置和调用

7.4.2 LPM_RAM的设置和调用

7.4 LPM 随机存储器的设置和调用

7.4.2 LPM_RAM的设置和调用

6 宏功能模块与IP应用 [兼容模式]

![6 宏功能模块与IP应用 [兼容模式]](https://img.taocdn.com/s3/m/becd31b1960590c69ec376e8.png)

ARCHITECTURE one OF myadder IS COMPONENT adder12 IS PORT( aclr : IN STD_LOGIC ; clock : IN STD_LOGIC ; dataa : IN STD_LOGIC_VECTOR (11 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (11 DOWNTO 0); result : OUT STD_LOGIC_VECTOR (11 DOWNTO 0) END COMPONENT; SIGNAL qq: STD_LOGIC_VECTOR(11 DOWNTO 0); SIGNAL dreg: STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN

6.3 LPM运算器的设计

阅读:教材6.2和6.3节。

学习目标

了解LPM; 熟悉MegaWizard Plug-in Manager; 掌握LPM计数器、ROM、RAM和运算器的使用;

);

PROCESS(rst, clk) BEGIN IF rst='0' THEN dreg<=(OTHERS=>'0'); ELSIF clk'EVENT AND clk='1' THEN dreg<=din; END IF; END PROCESS; U1: adder12 PORT MAP( aclr=>(not rst), clock=>clk, dataa=> "0000" & dreg, datab=>qq, result=>qq ); dout<=qq; END ARCHITECTURE;

宏功能模块与IP应用2

; ; ; ; ; ; ; ; ; ;

09:00; 19:09; 29:18; 39:27; 49:36; 59:45; 69:54; 79:63; 89:72; 99:81;

首页 上页 下页 末页 结束

6

7.6流水线乘法累加器的混合输入设计

本节通过一个8位流水线乘法累加器的实例介 绍以原理图为工程,VHDL文本描述和宏功能块为 原理图元件的混合输入和设计方法。 【例7-6】 (1)用 VHDL设计16位加法器。作为乘法累加器的 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; 元件之一, 16位加法器可以用VHDL文本表述(如例 USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER16B 7-6所示 )。 IS PORT ( CIN : IN STD_LOGIC; 首先将此加法器输入 Quattus Ⅱ。然后将其转 A,B : IN STD_LOGIC_VECTOR(15 DOWNTO 0); S : OUT STD_LOGIC_VECTOR(15 DOWNTO 0); 换为原理图元件。 COUT : OUT STD_LOGIC );

; ; ; ; ; ; ; ; ; ;

03:00 13:03 23:06 33:09 43:12 53:15 63:18 73:21 83:24 93:27

; ; ; ; ; ; ; ; ; ;

04:00 14:04 24:08 34:12 44:16 54:20 64:24 74:28 84:32 94:36

图7-22 LPM_RAM的仿真波形

首页 上页 下页 末页 结束

2

7.5.2 FIFO定制 先进先出存储器LPM_FIFO的定制与前面介绍 的流程也基本相同。 同样使用MegaWizard Plug-In Manager工具。 在进入图7-6所示窗口后.选择LPM_FIFO+项,选 择Cyclone器件,文件名可取为fif02.vhd。 由图7-23可知,此FIFO的数据位宽度为8,深 度为256。其中data[7 …1]为数据输入口;q[7…0]为 数据输出口;wrreq和rdreq分别为数据写入和读出 请求信号,高电平有效;aclr为异步清零;full为存 储数据溢出指示信号;empty为FIFO空指示信号; usedw[7…0]为当前已使用地址数指示;选择了速度 优化方式。

第7章VHDL宏功能模块与IP核的应用

END;

ARCHITECTURE DACC OF SINGT IS COMPONENT data_rom --调用波形数据存储器LPM_ROM文件:data_rom.vhd声明

PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);--6位地址信号 inclock : IN STD_LOGIC ;--地址锁存时钟

7.0 宏功能模块概述

宏功能模块LPM:是参数可设置模块库的英语缩写 (Library of Parameterized Modules),这些可 以以图形或硬件描述语言模块形式方便调用的宏 功能块,使得基于EDA技术的电子设计的效率和 可靠性有了很大的提高。设计者可以根据实际电 路的设计需要,选择LPM库中的适当模块,并为 其设定适当的参数,就能满足自己设计需要,从 而在自己的项目中十分方便地调用优秀的电子工 程师人员的硬件设计成果。

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SINGT IS

PORT ( CLK : IN STD_LOGIC;

--信号源时钟

DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );--8位波形数据输出

black-box申明,用于在使用EDA 综合工具时指定端口方向。 • <输出文件>_inst.tdf : 宏功能模块包装文件中子设计的AHDL例化示例。 • <输出文件>_inst.vhd : 宏功能模块包装文件中实体的VHDL例化示例。 • <输出文件>_inst.v : 宏功能模块包装文件中模块的VerilogHDL例化示例。

宏功能模块与IP应用

宏功能模块与IP应用6.1宏功能模块概述这里主要介绍LPM宏功能模块,它就是Library of Parameterized Modules(参数可设置模块库)的缩写,Altera提供的可参数化功能模块和LPM函数均基于altera器件的结构作了优化设计。

我认为就是已经设计好的最佳的基本电路模块。

在特定器件结构中发挥出最佳性能。

可以使用这些知识产权的参数化模块减少设计和测试的时间。

这些宏功能模块应用于通信,数字信号处理(DSP),PCI和其他总线界面,以及存储器中的宏功能模块。

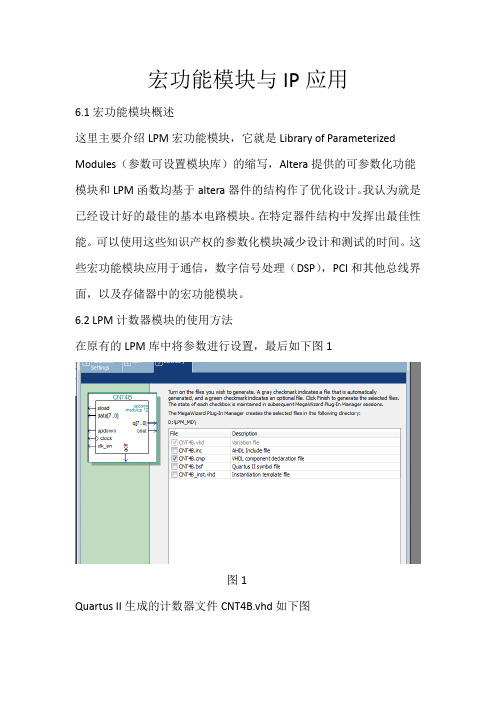

6.2 LPM计数器模块的使用方法在原有的LPM库中将参数进行设置,最后如下图1图1Quartus II生成的计数器文件CNT4B.vhd如下图Lpm_counter是元件名,是可以从lpm库中调用的宏功能模块元件名;而lpm_counter_component则是在此文件中为使用和调用lpm_counter取的例化名,即参数传递语句中的宏功能模块元件的例化名。

6.3 基于LPM的流水线乘法累加器设计LPM加法器模块设计LMP乘法器模块设置调用6.4 LPM随机存储器的设置和调用在涉及RAM和ROM等存储器应用的EDA设计开发中,调用LPM模块类存储器是最方便,最经济,最高效和性能最容易满足设计要求的途径。

Quartus能接受两种格式的文件:MIF和HEX。

建立米饭格式的文件然后就是数据类型的定义语句!如整数类型INTEGER,布尔型boolean,标准逻辑类型std_logic等,此外VHDL还允许用户自行定义新的数据类型。

6.5 LPM_ROM的定制和使用方法6.6 在系统存储器数据读写编辑器应用对于Cyclone系列的FPGA,只要对使用的LPM_ROM或LPM_RAM等存储器模块作适当设置,就能利用Quartus的在系统存储器读写编辑器直接通过JTAG口读取或改写FPGA内处于工作状态的存储器中的数据,读取过程不影响FPGA的正常工作。

EDA 第7讲 宏功能模块与IP应用

7.4 LPM 随机存储器的设置和调用

7.4.5 数据类型定义语句 4. 枚举型子类型数据类型定义

SUBTYPE定义了由TYPE所定义的原型数据类型的一个子集

【例】

7.4 LPM 随机存储器的设置和调用

7.4.6 存储器配置文件属性定义和结构设置 例7-6中,纯VHDL 描述,不做约束,直接综合的RTL:------耗费大量逻辑资源

7.5 LPM_ROM的定制和使用示例

7.5.4 正弦信号发生器硬件实现和测试

第 7讲

宏功能模块与IP应用

7.1 7.2 7.3 7.4 7.5 7.6 7.7 7.8 7.9 7.10 7.11 7.12

宏功能模块概述 LPM计数器模块使用方法 利用属性控制乘法器的构建 LPM 随机存储器的设置和调用 LPM_ROM的定制和使用示例 在系统存储器数据读写编辑器应用 FIFO定制 LPM嵌入式锁相环调用 NCO核数控振荡器使用方法 使用IP Core设计FIR滤波器 8051单片机IP核应用 DDS实现原理与应用

7.4 LPM 随机存储器的设置和调用

1.建立.mif格式文件 (4)专用mif文件生成器

7.4 LPM 随机存储器的设置和调用

7.4.1 存储器初始化文件生成 2.建立.hex格式文件

建立.hex格式文件的两种方法

7.4 LPM 随机存储器的设置和调用

7.4.2 LPM_RAM的设置和调用 •先建原理图文件,建工程。 •菜单:Tools->Mega Wizard Plug-in Manager

7.2 LPM计数器模块使用方法

7.2.1 LPM_COUNTER计数器模块文本文件的调用 (1)打开宏功能块调用管理器 •先建文件夹。

EDA第七章_宏功能模块与IP应用

【例7-2】用其他编辑器(如记事本)产生.mif格式文件 WIDTH = 8; DEPTH = 64; ADDRESS_RADIX = HEX; 正弦波数据可以使用C语言程序来生成 DATA_RADIX = HEX; #include <stdio.h> CONTENT BEGIN #include “math.h” 0 : FF; main() 1 : FE; { 2 : FC; int i; 3 : F9; float s; 4 : F5; for( i=0; i<64; i++ ) …(数据略去) { s = sin(atan(1)*8*i/64); 3D : FC; printf( "%x : %x;\n", i, (int)( (s+1)/2*255) 3E : FE; ); 3F : FF; } END; } 把上述程序编译成可执行文件romgen.exe, 可在DOS命令行下执行: romgen > sin_rom.mif;

(主要用于不支持该Megafunction的第三方EDA工具例化和调用,避免出 现找不到源文件的情况(当然,也就不能实现其功能))

6. 包含仿真波形的html文件:根据用户的配置信息得到的仿真波形,

可供设计者初步评估该定制Megafunction的参数配置是否符合需要。

7.1.3 对Megafunction进行例化

其余宏功能模块在Quartus II上只有其网络链接 使用资料:Help Megafunctions/LPM 利用Megafunction进行项目设计的步骤:

1.利用MegaWizard Plug-In Manager(MegaWizard 插件管理器)建立或修 改包含自定义宏功能模块的设计文件 2.在顶层设计文件中对这些文件进行例化。

第六章_宏功能模块与IP应用

复习

P195~209

预习

第二次实验: 第二次实验:p120_4.5.2 2位十进制数字频率计 位十进制数字频率计 第三次实验: 第三次实验: 必做: 十六进制7段数码显示译码器设计 段数码显示译码器设计( 必做:p140_4-4 十六进制 段数码显示译码器设计(参 考本教材二版p143【例5-21】) 考本教材二版 【 】 选做: 数码扫描显示电路设计( 选做:p141_4-6 数码扫描显示电路设计(参考本教材 二版p144【例5-22】) 二版 【 】 第四次实验: 并行ADC采样控制电路实现和 第四次实验:p264_7-2 并行 采样控制电路实现和 硬件验证 第五/六次实验 设计型实验(自己选题) 六次实验: 第五 六次实验:设计型实验(自己选题)

一、正弦信号发生器结构

由FPGA实现 实现 RST EN CLK Q1 address Inclock q Q

四 个 组 成 部 分

1、7位地址信号发生器 、 位地址信号发生器 2、正弦信号数据存储器 、正弦信号数据存储器ROM 3、VHDL顶层文件 顶层文件SIN_GNT 、 顶层文件 4、8位D/A 、 位

LPM功能模块内容丰富,设计者可根据实际需要,选 功能模块内容丰富,设计者可根据实际需要, 功能模块内容丰富 择LPM库中的适当模块,并为其设定适当的参数,满足自 库中的适当模块,并为其设定适当的参数, 库中的适当模块 己的设计需求。 己的设计需求。

6.5.3 简易正弦信号发生器设计 简易正弦信号发生器设计

三、正弦信号数据存储器ROM的定制 正弦信号数据存储器ROM的定制 ROM

4. 按图示作选择

三、正弦信号数据存储器ROM的定制 正弦信号数据存储器ROM的定制 ROM

5. 按图示作选择

第7章 QuartusⅡ中的宏功能模块及应用

第7章 QuartusⅡ中的宏功能模块及 应用

Altera宏功能模块是复杂或更高级构建模块,可在 QuartusⅡ设计文件中,与逻辑门或触发器等基本单元一起 使用。 QuartusⅡ7.2开发软件提供的各种宏功能模块,如计数 器、乘法器、存储器、寄存器、锁存器等。

8)单击“Finish”按钮,则原理图编辑窗口中出现了 刚才定制的计数器的图形,添加输入输出端口后,如下图 所示。

参数化四位加法计数器原理图

第七章 结束

lpm_counter元件选择窗口

3)弹出宏功能模块定制管理器对话框2: 对lpm_counter元件的各种参数进行选择,定制适合设计需要的 模块,NEXT。

4)弹出定制lpm_counter元件对话框3: 在“How wide should the ‘q’ output bus be?”此处输入“4”位; 并选择“Up only”(为双边沿有效 ),NEXT。

1 宏功能模块与LPM函数

Altera提供的可参数化宏功能模块和LPM函数均为Altera

器件结构做了优化使用宏功能模块能节省时间,不需要用 户对逻辑进行编码,只需调用合适的宏功能模块即可; 使用宏功能模块方便快捷,通过设置参数便可方便地 将宏功能模块伸缩为不同的大小。

使用宏功能模块能优化设计,可参数化宏功能模块和 LPM函数能更有效地对设计文件进行逻辑综合和器件实现。

2 知识产权IP核

IP核是指将一些在数字电路中常用但比较复杂的功 能块,如FIR滤波器,SDRAM控制器,PCI接口等设计 成可修改参数的模块,让其他用户可以直接调用这些模 块。

3 宏功能模块定制管理器

第7章宏模块与IP应用

组成

地址发生器:计数器(6位) VHDL顶层文件

■

输出频率:f = f0 /64

f :输出频率 f0:计数器时钟频率

7.2.1 正弦信号发生器设计

2、正弦信号发生器结构框图

f f0

7.2

宏模块应用实例

7.2.2 设计步骤

第一步:定制初始化数据文件 1、建立mif格式文件方法:

法① : Quartus中利用New-Other-Memory Initialization file 法② :其它编辑器设计 见例7-1 法③ : C语言设计 见例7-2 等等。

完成

7.2.2宏功能块设计步骤

6) LPM_ROM设计完成后所需的设置框

—对大多器件以下设置可以省略,只有采用CycloneⅡ需要以下设置。

注释:

生成的ROM文件可以打开,打开文件方式: 键入:init_file => “文件的目录及名称”或直接从File\open即可。 书上给出了ROM文件内容:P167.[7-3]—自看

(2)顶层原理图文件设计

■ 将LPM乘法器设置为流水线工作方式

其他模块按照顶层设计的电路一一提取,并连接完成,再编译仿真,下载 即完成全部设计。

第 7 章

宏功能模块与IP应用

7.7 LPM嵌入式锁相环调用

7.7.1 建立嵌入式锁相环元件

■ 选择输入参考时钟为20MHz

时钟为20MHz

7.7 LPM嵌入式锁相环调用

(1)建立.mif格式文件 (2)建立.hex格式文件

2.建立.hex格式文件方法:

法①:Quartus中利用 New-Other File-Hexadecimal file 见图7-2 法②:利用8051单片机编辑器设计 见图7-3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Quartus II软件,用74161设计一个模99的计数器,个 位和十位都采用8421BCD码的编码方式设计,分别用置0和置1 两种方法实现,完成原理图设计输入、编译、仿真和下载整个过 程。

3

基于Quartus II软件,用7490设计一个模71计数器,个位和 十位都采用8421BCD码的编码方式设计,完成原理图设计输入、 编译、仿真和下载整个过程。

5

-5 5

my_vector’low

my_vector’length my_vector’range

-5

11 (5 downto -5)

my_vector’reverse_range

(-5 to 5)

习

题

1 基于Quartus II软件,用D触发器设计一个2分频电路,并做波形仿 真,在此基础上,设计一个4分频和8分频电路,做波形仿真。 。 2 基于Quartus II软件,用7490设计一个能计时(12小时)、计分 (60分)和计秒(60秒)的简单数字钟电路。设计过程如下: (1)先用Quartus II的原理图输入方式,用7490连接成包含进位输出 的模60的计数器,并进行仿真,如果功能正确,则将其生成一个部件; (2)将7490连接成模12的计数器,进行仿真,如果功能正确,也将其 生成一个部件; (3)将以上两个部件连接成为简单的数字钟电路,能计时、计分和计秒, 计满12小时后系统清0重新开始计时。 (4)在实现上述功能的基础上可以进一步增加其它功能,比如校时功能, 能随意调整小时、分钟信号,增加整点报时功能等。

TYPE week IS (sun,mon,tue,wed,thu,fri,sat) ; TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ;

SIGNAL present_state,next_state : m_state ;

编码为:st0=“000” ; st1=“001” ; st2=“010” ; st3=“011” ; st4=“100” ;

计数器74161设计举例

模10计数器

仿真结果

三、 Primitives库

缓冲器库

引脚库

存储单元库

逻辑门库

其他模块

例1:利用lpm_counter计数器模块做一个十二进制计数器

方法一:利用画电路图,建立.bdf文件 方法二:利用vhdl语言,建立.vhd文件

例2:利用lpm_ram做一个8位、128深度的ram.

I/O模块库

锁相环模块设计举例

参数化锁相环宏模块altpll以输入时钟信号作为参考信

号实现锁相,从而输出若干个同步倍频或者分频的片内 时钟信号。与直接来自片外的时钟相比,片内时钟可以 减少时钟延迟,减小片外干扰,还可改善时钟的建立时 间和保持时间,是系统稳定工作的保证。不同系列的芯

片对锁相环的支持程度不同,但是基本的参数设置大致

st5=“101”

2.整数类型:

用户定义的整数类型是标准包中整数类型的子范围。

格式:type 类型名称 is interger 整数范围; 例:type my_integer is integer range 0 to 9;

3.数组类型:

数组:同类型元素的集合。VHDL支持多维数组。

多维数组的声明: type byte is array(7 downto 0) of bit; type vector is array(3 downto 0) of byte;

例3:设置一个数字钟. 要求:具有24小时计数功能,可以设置小时和分钟的 值,并具有整点报时和报警功能。

数据类型定义语句

TYPE语句的用法如下: TYPE 或 TYPE 数据类型名 IS 数据类型定义 ; 两种不同的定义方式: TYPE st1 IS ARRAY ( 0 TO 15 ) OF STD_LOGIC ; TYPE week IS (sun,mon,tue,wed,thu,fri,sat) ; 数据类型名 IS 数据类型定义 OF 基本数据类型 ;

状态符号化: TYPE m_state IS ( st0,st1,st2,st3,st4,st5 ) ;

SIGNAL present_state,next_state : m_state ; TYPE BOOLEAN IS (FALSE,TRUE) ;

TYPE my_logic IS

( '1' ,'Z' ,'U' ,'0' ) ;

4

基于Quartus II,用74283(4位二进制全加器)设计实现一 个8位全加器,并进行综合和仿真,查看综合结果和仿真结果。

5

6 采用Quartus II软件的宏功能模块lpm_rom,用查表的 方式设计一个实现两个8位无符号数加法的电路,进行编译 仿真。 7 先用lp一个, 再用VHDL分别设计4bit×4bit和8bit×8bit乘法器,比较 两类乘法器的运行速度和资源好用情况。 8 用数字锁相环实现分频,假定输入时钟频率为10MHz,要 想得到6MHz的时钟信号,使用altpll宏功能模块实现该电路。

可以将此触发器旁路,信号直接输给PIA或输出到I/O

脚。

/

MAX7000系列的内部结构:

这种PLD可分为三块结构:宏单元(Marocell),可编程连线 (PIA)和I/O控制块。 宏单元是PLD的基本结构,由它来实现基本 的逻辑功能。图1中兰色部分是多个宏单元的集合(因为宏单元较 多,没有一一画出)。可编程连线负责信号传递,连接所有的宏 单元。I/O控制块负责输入输出的电气特性控制,比如可以设定集 电极开路输出,摆率控制,三态输出等。 图中 左上的 INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全局

SIGNAL s1 : my_logic ; s1 <= 'Z' ;

SUBTYPE

子类型名 IS 基本数据类型 RANGE 约束范围;

SUBTYPE digits IS INTEGER RANGE 0 to 9 ;

1.枚举类型:

综合器将自动实现枚举类型元素的编码,一般将第一 个枚举量(最左边)编码为0,以后的依次加1。编码 用位矢量表示,位矢量的长度将取所需表达的所有枚 举元素的最小值。

数组属性:

语法如下: 对象‘属性 VHDL为数组预先定义的属性:

left

high length

right

low range

reverse_range

例:variable my_vector:bit_vector(5 downto -5); 各属性如下:

my_vector’left

my_vector’right my_vector’high

相同,下面便举例说明altpll的应用。

(1)输入altpll宏功能模块

选择芯片和设置参考时钟

锁相环控制信号设置

输入时钟设置

(2)编译和仿真

锁相环电路

功能仿真波形

存储模块库

存储器模块设计举例

ROM(Read Only Memory,只读存储器)是存储器的 一种,利用FPGA可以实现ROM的功能,但其不是真正意义 上的ROM,因为FPGA器件在掉电后,其内部的所有信息都 会丢失,再次工作时需要重新配置。 Quartus II提供的参数化ROM是lpm_rom,下面用一 个乘法器的例子来说明它的使用方法,这个例子使用 lpm_rom构成一个4位×4位的无符号数乘法器,利用查表 方法完成乘法功能。

数据线、地址线宽度设置

控制端口设置

添加.mif文件

如下图所示就是基于ROM实现的4位×4位的无符号 数乘法器电路图,其参数设置为: LPM_WIDTH=8 LPM_WIDTHAD=8 LPM_FILE=mult_rom.mif

仿真结果

二、 Maxplus2库

Maxplus2库主要由74系列数字集成电路组成,包括 时序电路宏模块和运算电路宏模块两大类,其中时序电 路宏模块包括触发器、锁存器、计数器、分频器、多路 复用器和移位寄存器,运算电路宏模块包括逻辑预算模 块、加法器、减法器、乘法器、绝对值运算器、数值比 较器、编译码器和奇偶校验器。 对于这些小规模的集成电路,在数字电路课程中有详 细的介绍,其调入方法与Megafunction库中的宏模块 相同,只是端口和参数无法设置。

EDA技术实用教程

宏功能模块与 IP应用

宏功能模块设计

一、 Megafunctions库 二、 Maxplus2库 三、 Primitives库

一、Megafunctions库

Megafunction库是Altera提供的参数 化模块库。从功能上看,可以把 Megafunction库中的元器件分为: 算术运算模块(arithmetic) 逻辑门模块(gates) 储存模块(storage) IO模块(I/O)

时钟,清零和输出使能信号,这几个信号有专用连线与PLD中每

个宏单元相连,信号到每个宏单元的延时相同并且延时最短。

宏单元的具体结构:

左侧是乘积项阵列,实际就是一个与或阵列,每一个 交叉点都是一个可编程熔丝,如果导通就是实现“与” 逻辑。后面的乘积项选择矩阵是一个“或”阵列。两 者一起完成组合逻辑。图右侧是一个可编程D触发器, 它的时钟,清零输入都可以编程选择,可以使用专用 的全局清零和全局时钟,也可以使用内部逻辑(乘积 项阵列)产生的时钟和清零。如果不需要触发器,也

算数运算模块库

lpm_mult

下面以参数化乘法器lpm_mult为例来说明如何在设计中使用宏功 能模块。lpm_mult的基本参数已在下表中给出。

(1)调用lpm_mult

(2)lpm_mult参数设置

输入输出位宽设置

乘法器类型设置

(3)编译仿真