利用simulink实现8线3线编码器的设计仿真

8-3编码器,3-8译码器的verilog实现

8-3编码器,3-8译码器的verilog实现在数字系统中,由于采⽤⼆进制运算处理数据,因此通常将信息变成若⼲位⼆进制代码。

在逻辑电路中,信号都是以⾼,低电平的形式输出。

编码器:实现编码的数字电路,把输⼊的每个⾼低电平信号编成⼀组对应的⼆进制代码。

设计⼀个输⼊为8个⾼电平有效信号,输出代码为原码输出的3位⼆进制编码器。

化简逻辑表达式:由逻辑表达式可以得出,普通的8-3编码器⽤或门即可实现。

对应的verilog程序如下:module mb_83(x,y);input [7:0]x;output [2:0]y;reg [2:0]y;always@(x)begincase (x)8'b00000001:y=3'b000; //当当 x=8 ’b00000001,则则 y 输出为 3 ’b0008'b00000010:y=3'b001; //当当 x=8 ’b00000010,则则 y 输出为 3 ’b0018'b00000100:y=3'b010; //当当 x=8 ’b00000100,则则 y 输出为 3 ’b0108'b00001000:y=3'b011; //当当 x=8 ’b00001000,则则 y 输出为 3 ’b0118'b00010000:y=3'b100; //当当 x=8 ’b00010000,则则 y 输出为 3 ’b1008'b00100000:y=3'b101; //当当 x=8 ’b00100000,则则 y 输出为 3 ’b1018'b01000000:y=3'b110; //当当 x=8 ’b01000000,则则 y 输出为 3 ’b1108'b10000000:y=3'b111; //当当 x=8 ’b10000000,则则 y 输出为 3 ’b111default: y=3'b000;endcaseendendmodule上述编码器有⼀个缺点,即在某⼀个时刻只允许有⼀个有效的输⼊,⽽同时若⼜有两个或两个以上的输⼊信号要求编码,输出端⼀定会发⽣混乱,出现错误。

实验三-quartus-ii的设计处理(3-8译码器设计)

实验三-quartus-ii的设计处理(3-8译码器设计)

《可编程逻辑器件的设计与仿真》

实验报告

实验项目实验三Quartus II的设计处理(3-8译码器设计)

实验目的1.设计一个3-8译码器;

2.学习用VHDL进行逻辑描述。

实验器材PC机,Quartus II

授课形式集中训练任课教师:彭铁牛实验时间:2013-03-17

实验说明本设计实现一个3-8译码器,其逻辑功能如表所示

C B A Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0

0 0 0 1 1 1 1 1 1 1 0

0 0 1 1 1 1 1 1 1 0 1

***********

0 1 1 1 1 1 1 0 1 1 1

1 0 0 1 1 1 0 1 1 1 1

1 0 1 1 1 0 1 1 1 1 1

1 1 0 1 0 1 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1 1

本设计练习用VHDL语言描述仿真译码器。

要求编写3-8译码器的VHDL设计文件。

注意VHDL文件的结构和语法,并掌Quartus II 平台中文本编辑器的使用方法。

实验内容和体会

1

Ⅰ.VHDL源程序Ⅱ.仿真波形Ⅲ.元件符号Ⅳ.实验体会。

Simulink6

• 5)4-16线译码器的搭建 对于两个3-8线译码器,选择任意一个使 能端作为第4个译码输入端。 Ex22_4.mdl

• 3.数据选择器仿真 数据选择器又叫多路 X0 选择器或多路开关。它有 X 1 . m个输入端X0~Xm-1,一 . 个输出端D,n个地址端 . Xm-1 A0~An-1。输入端的个数 m与地址端的位数应满足: 2n=m。在地址码A0~An-1 的控制下,从多个输入中 选择一个,将其送到输出 端。

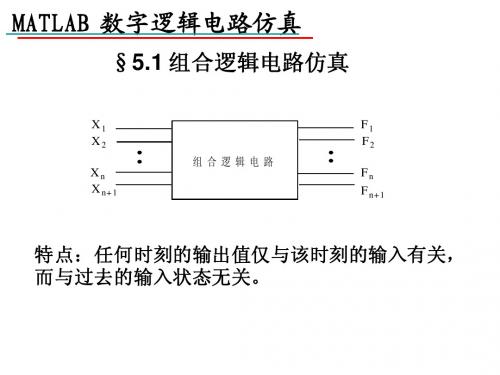

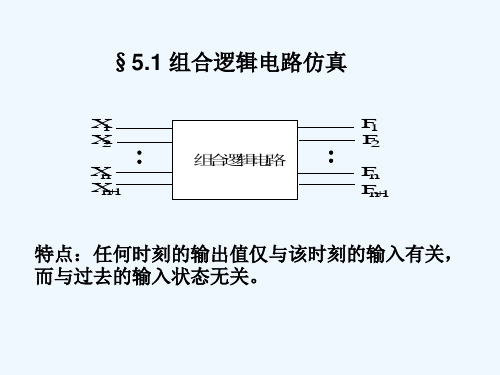

• 2.6.1 组合逻辑电路仿真 • 1.编码器的仿真 编码器是指用选定的一组0、1序列来识别 特定对象的过程。 设编码器有n个输入端X0,X1,…,Xn1,有m个输出端Z0,Z1,…,Zm-1。规 定在任何给定时间内,n个输入端中只有一 个输入出现,其余n-1个输入均不得出现。 为了建立输入输出之间一一对应的关系, 输出的位数应满足 m logn ,m取整数。

X2 X1 X0 Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

1 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0

0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0

0 0 0 0 1 0 0 0

逻辑表达式: Z2=X4+X5+X6+X7 Z1=X2+X3+X6+X7 Z0=X1+X3+X5+X7 • 2)模型搭建 Ex20.mdl

2.译码器的仿真 译码是编码的逆过程,它将被编成0、1序列的 某种代码还原成原来的对象。

例2.21 3-8线译码器的仿真模型 1)模型分析

3-8线译码器真值表

实验三 3-8译码器仿真及实现

实验三3-8译码器仿真及实现一、实验目的和要求本次实验使用Verilog 硬件描述语言在DE1开发平台上设计一个基本组合逻辑电路3-8 译码器,并完成功能仿真和时序仿真。

二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、编写3-8的Verilog程序。

2、构建仿真波形文件,实现QuartusII的功能仿真和时序仿真。

3、下载设计到DE1,观察译码输出。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程目录、工程文件名以及顶层实体名。

自己起名字,例如学号加38等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

不要使用Quartus II的根目录作为工程目录。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

8)培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程的根目录,为了让Quartus II 像Visual Studio 等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果输出路径。

实验三+3-8译码器仿真及实现

实验三3-8译码器仿真及实现姓名:学号:班级:日期:一、实验目的和要求本次实验使用Verilog 硬件描述语言在DE1开发平台上设计一个基本组合逻辑电路3-8 译码器,并完成功能仿真和时序仿真。

二、实验环境1、PC机,Pentium 4 2.0G以上,内存1G以上,硬盘500G以上,1024×768彩显,USB接口,网络接口,串口。

2、友晶DE1开发板和相关配件。

3、软件:Windows XP或者Windows 7操作系统,DE1配套光盘。

三、实验内容1、编写3-8的Verilog程序。

2、构建仿真波形文件,实现QuartusII的功能仿真和时序仿真。

3、下载设计到DE1,观察译码输出。

四、实验步骤1、建立Quartus 工程:1)打开Quartus II 工作环境。

2)点击菜单项File->New Project Wizard 帮助新建工程。

3)输入工程目录、工程文件名以及顶层实体名。

自己起名字,例如学号加38等。

注意:输入的顶层实体名必须与之后设计文件的顶层实体名相同,默认的顶层实体名与工程文件名相同,本类实验均采用这种命名方法以便于管理。

不要使用Quartus II的根目录作为工程目录。

4)添加设计文件。

如果用户之前已经有设计文件(比如.v 文件)。

那么直接添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑新的设计文件。

5)选择设计所用器件。

由于本次实验使用 Altera 公司提供的DE1 开发板,用户必须选择与之相对应的FPGA 器件型号,如下图:6)设置 EDA 工具。

设计中可能会用到的EDA 工具有综合工具、仿真工具以及时序分析工具。

本次实验中不使用这些工具,因此点击Next 直接跳过设置。

7)查看新建工程总结。

在基本设计完成后,Quartus II 会自动生成一个总结让用户核对之前的设计,确认后点击Finish 完成新建。

8)培养良好的文件布局。

Quartus II 默认把所有编译结果放在工程的根目录,为了让Quartus II 像Visual Studio 等IDE 一样把编译结果放在一个单独的目录中,需要指定编译结果输出路径。

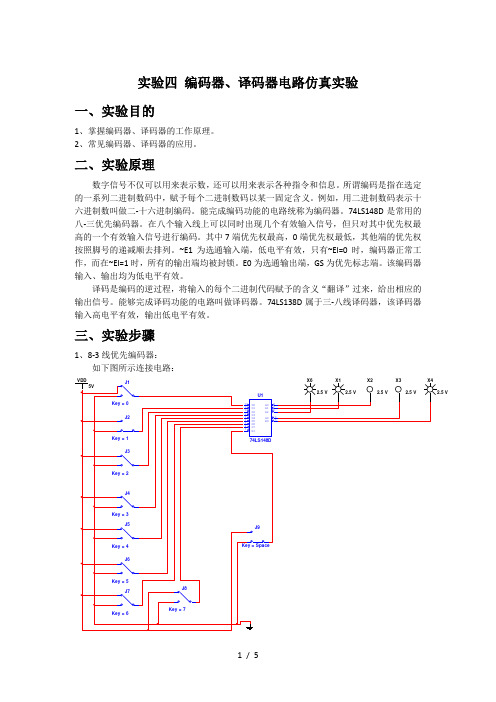

实验四-编码器-和译码器电路仿真实验

实验四编码器、译码器电路仿真实验一、实验目的1、掌握编码器、译码器的工作原理。

2、常见编码器、译码器的应用。

二、实验原理数字信号不仅可以用来表示数,还可以用来表示各种指令和信息。

所谓编码是指在选定的一系列二进制数码中,赋予每个二进制数码以某一固定含义。

例如,用二进制数码表示十六进制数叫做二-十六进制编码。

能完成编码功能的电路统称为编码器。

74LS148D是常用的八-三优先编码器。

在八个输入线上可以同时出现几个有效输入信号,但只对其中优先权最高的一个有效输入信号进行编码。

其中7端优先权最高,0端优先权最低,其他端的优先权按照脚号的递减顺去排列。

~E1为选通输入端,低电平有效,只有~EI=0时,编码器正常工作,而在~EI=1时,所有的输出端均被封锁。

E0为选通输出端,GS为优先标志端。

该编码器输入、输出均为低电平有效。

译码是编码的逆过程,将输入的每个二进制代码赋予的含义“翻译”过来,给出相应的输出信号。

能够完成译码功能的电路叫做译码器。

74LS138D属于三-八线译码器,该译码器输入高电平有效,输出低电平有效。

三、实验步骤1、8-3线优先编码器:如下图所示连接电路:切换9个单刀双掷开关进行仿真实验,将结果记录入下表中,输入端“1”表示高电平,“0”表示低电平,“X”表示高低电平都可以。

输出端中的“1”表示探测器亮,“0”表示探测器灭。

该编码器输入、输出均为低电平有效。

2、3-8线译码器实验步骤如下图所示连接电路切换3个单刀双掷开关进行仿真实验,实验结果记录如下表中。

输入端中的“1”表示接高电平,“0”表示接地电平。

输出端中的“1”表示探测器亮,“0”表示探测器灭。

该译码器输入高电平有效,输出低电平有效。

四、思考题:(1)利用两块8-3线优先编码器74LS148D设计16-4线优先编码电路,然后仿真实验验证16-4线优先编码的逻辑功能。

实验线路如图:真值表如图所示:(2)利用两块3-8线译码器74LS138D设计4-16线译码器,然后仿真验证4-16线译码逻辑功能。

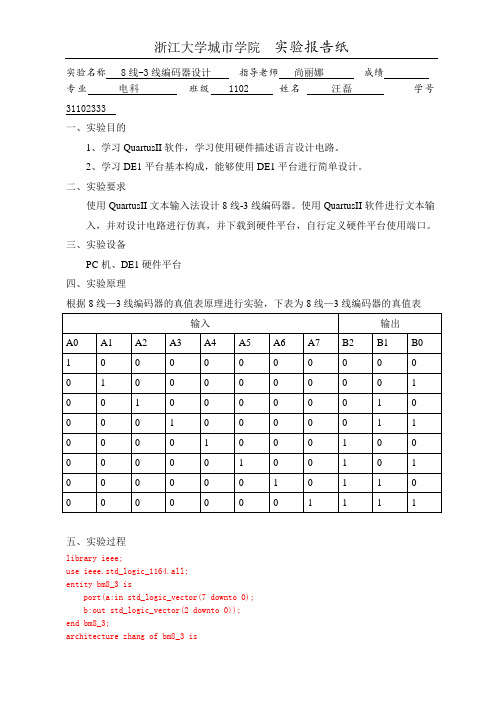

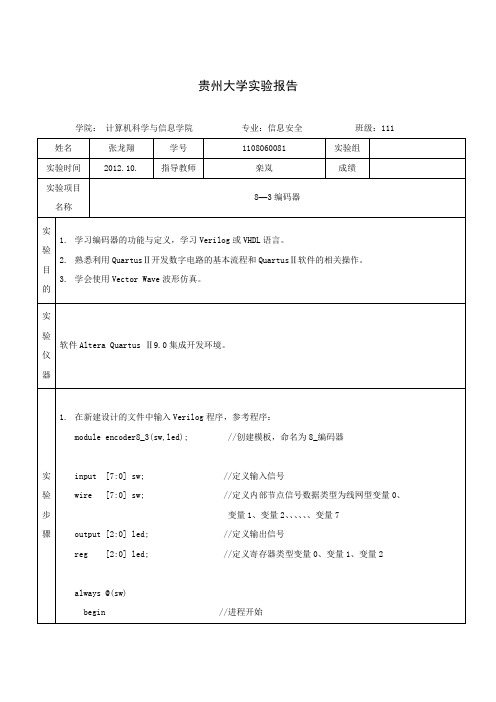

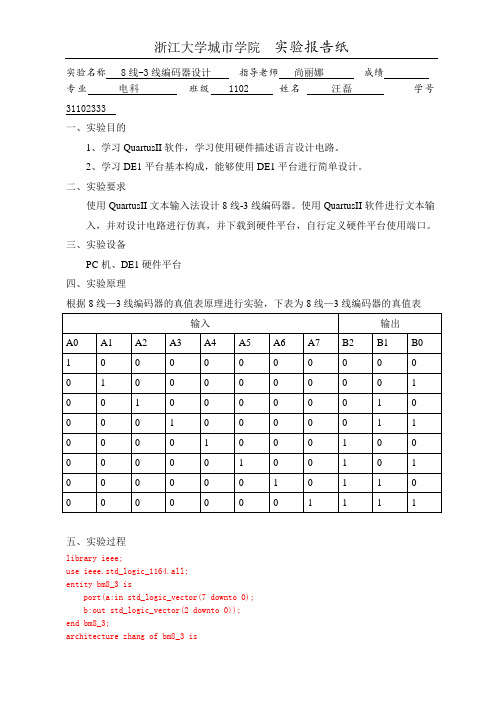

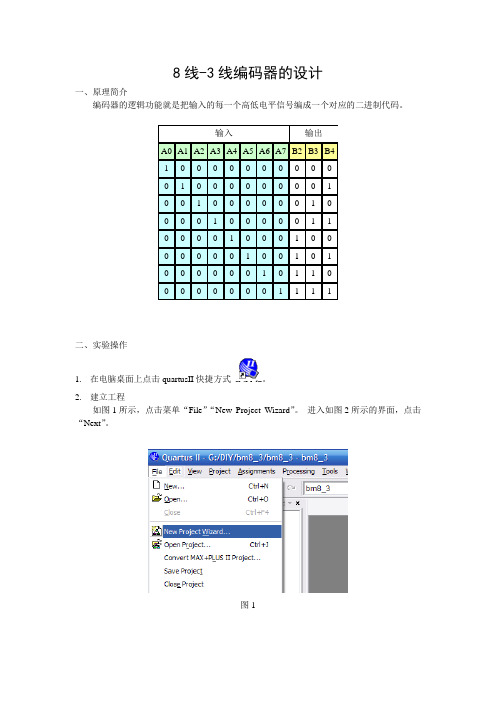

实验二 8线-3线编码器设计

实验名称 8线-3线编码器设计指导老师尚丽娜成绩专业电科班级 1102 姓名汪磊学号31102333一、实验目的1、学习QuartusII软件,学习使用硬件描述语言设计电路。

2、学习DE1平台基本构成,能够使用DE1平台进行简单设计。

二、实验要求使用QuartusII文本输入法设计8线-3线编码器。

使用QuartusII软件进行文本输入,并对设计电路进行仿真,并下载到硬件平台,自行定义硬件平台使用端口。

三、实验设备PC机、DE1硬件平台四、实验原理根据8线—3线编码器的真值表原理进行实验,下表为8线—3线编码器的真值表五、实验过程library ieee;use ieee.std_logic_1164.all;entity bm8_3 isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(2 downto 0));end bm8_3;architecture zhang of bm8_3 isbeginprocess(a)begincase a iswhen"00000001"=>b<="000";when"00000010"=>b<="001";when"00000100"=>b<="010";when"00001000"=>b<="011";when"00010000"=>b<="100";when"00100000"=>b<="101";when"01000000"=>b<="110";when others=>b<="111";end case;end process;end zhang;六、实验结果该程序还存在一些不足,当出现10000000是和非正常输入的时候是一样的输出,所以我们进行了一些修改,修改程序与结果如下:library ieee;use ieee.std_logic_1164.all;entity e isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(3 downto 0));end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;思考题一:思考题二:entity e isport(a:in bit_vector(7 downto 0);b:out bit_vector(3 downto 0)); end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;七、心得体会对操作更加熟练,加深对其的认识。

8-3译码器实验报告

实验报告

学院:专业:班级:

8'b0100_0000:led<=3'b110; //当输入信号是位宽为8位的二进制数据01000000时,输出信号为位宽

为3位的二进制数据110

8'b1000_0000:led<=3'b111; //当输入信号是位宽为8位的二进制数据时,输出信号为位宽为3位的

二进制数据111

default :led<=3'b000; //当输入信号是位宽为8位的二进制数据00000001时,输出信号为位宽

为3位的二进制数据000

endcase //结束分支语句

end //结束循环语句

endmodule //结束模块

实

验

数

据

上图为波形仿真。

如图可知,当输入信号为00000001时,输出信号为000;输入信号为00000010时,输出信号为001;

输入信号为00000100时,输出信号为010;输入信号为00001000时,输出信号为011;输入信号为00010000时,输出信号为100;输入信号为00100000时,输出信号为101;输入信号为01000000时,输出信号为

注:各学院可根据教学需要对以上栏木进行增减。

表格内容可根据内容扩充。

8——3编码器 数电实验报告(完整版)

实验总结

1.由于编译环境是在软件:Altera QuartusⅡ9.0下进行的,而该软件是全英文版,在第一次做的时候总是多一个字母少一个字母的,所以为了适应该软件在课下要做好实验预习,同时也应该认真听老师讲课。

2.在选择工程路径和工程名以及顶层文件实体名时,要注意工程名必须与顶层实体名相同,而工程目录可以随便设置,但必须是英文的目录,工程名跟顶层实体名必须也是英文字母开头。

8'b0000_0010 : led <= 3'b001;//如果sw为8’b0000_0010,则led被赋值为3’b001;

8'b0000_0100 : led <= 3'b010;//如果sw为8’b0000_0100,则led被赋值为3’b010;

8'b0000_1000 : led <= 3'b011;//如果sw为8’b0000_1000,则led被赋值为3’b011;

8'b1000_0000 : led <= 3'b111;//如果sw为8’b1000_0000,则led被赋值为3’b111;

default : led <= 3'b000;//如果sw不是上面的值,则led被赋值为3’b000;

endcase//进程结束

end//实体结束

endmodule//结束模块

实验内容

编写8—3编码器的Verilog代码并仿真

实验数据

(图一)

(图二)

对实验结果的分析:

1.在设定sw的参数后,任意操作sw1——sw7,例如操作sw[4],则led被赋值为二进制的3’b100,然后回到源程序“output [2:0] led;”则被三位输出。

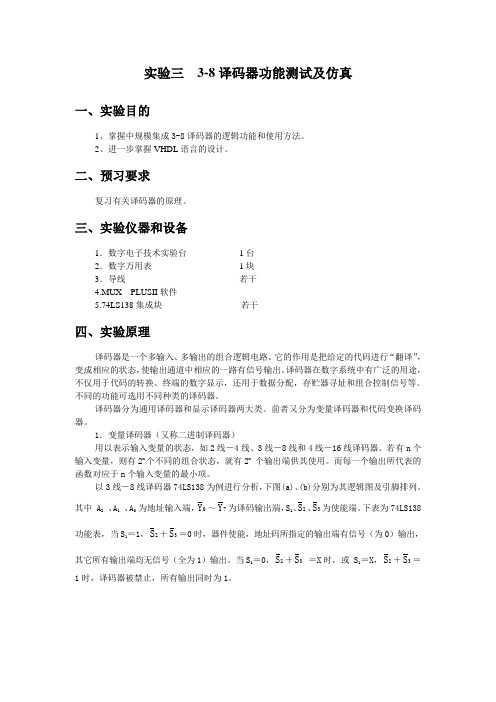

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

实验二 8线-3线编码器设计

实验名称 8线-3线编码器设计指导老师尚丽娜成绩专业电科班级 1102 姓名汪磊学号31102333一、实验目的1、学习QuartusII软件,学习使用硬件描述语言设计电路。

2、学习DE1平台基本构成,能够使用DE1平台进行简单设计。

二、实验要求使用QuartusII文本输入法设计8线-3线编码器。

使用QuartusII软件进行文本输入,并对设计电路进行仿真,并下载到硬件平台,自行定义硬件平台使用端口。

三、实验设备PC机、DE1硬件平台四、实验原理根据8线—3线编码器的真值表原理进行实验,下表为8线—3线编码器的真值表五、实验过程library ieee;use ieee.std_logic_1164.all;entity bm8_3 isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(2 downto 0));end bm8_3;architecture zhang of bm8_3 isbeginprocess(a)begincase a iswhen"00000001"=>b<="000";when"00000010"=>b<="001";when"00000100"=>b<="010";when"00001000"=>b<="011";when"00010000"=>b<="100";when"00100000"=>b<="101";when"01000000"=>b<="110";when others=>b<="111";end case;end process;end zhang;六、实验结果该程序还存在一些不足,当出现10000000是和非正常输入的时候是一样的输出,所以我们进行了一些修改,修改程序与结果如下:library ieee;use ieee.std_logic_1164.all;entity e isport(a:in std_logic_vector(7 downto 0);b:out std_logic_vector(3 downto 0));end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;思考题一:思考题二:entity e isport(a:in bit_vector(7 downto 0);b:out bit_vector(3 downto 0)); end e;architecture zhang of e isbeginprocess(a)begincase a iswhen"00000001"=>b<="0000";when"00000010"=>b<="0001";when"00000100"=>b<="0010";when"00001000"=>b<="0011";when"00010000"=>b<="0100";when"00100000"=>b<="0101";when"01000000"=>b<="0110";when"10000000"=>b<="0111";when others=>b<="1111";end case;end process;end zhang;七、心得体会对操作更加熟练,加深对其的认识。

利用simulink实现8线3线编码器的设计仿真

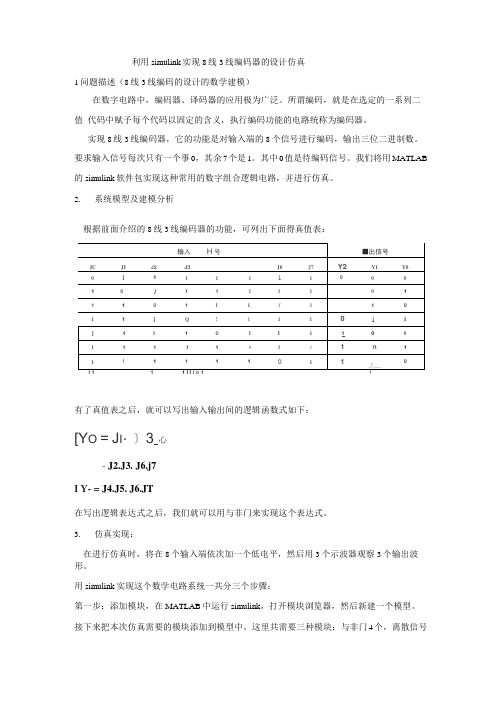

利用simulink实现8线3线编码器的设计仿真1问题描述(8线3线编码的设计的数学建模)在数字电路中,编码器、译码器的应用极为广泛。

所谓编码,就是在选定的一系列二值代码中赋予每个代码以固定的含义,执行编码功能的电路统称为编码器。

实现8线3线编码器,它的功能是对输入端的8个信号进行编码,输出三位二进制数。

要求输入信号每次只有一个事0,其余7个是1。

其中0值是待编码信号。

我们将用MATLAB 的simulink软件包实现这种常用的数字组合逻辑电路,并进行仿真。

2.系统模型及建模分析根据前面介绍的8线3线编码器的功能,可列出下面得真值表:有了真值表之后,就可以写出输入输出间的逻辑函数式如下:[Y O =J I・〕3心- J2.J3. J6.j7I Y- = J4.J5. J6.JT在写出逻辑表达式之后,我们就可以用与非门来实现这个表达式。

3.仿真实现;在进行仿真时,将在8个输入端依次加一个低电平,然后用3个示波器观察3个输出波形。

用simulink实现这个数学电路系统一共分三个步骤:第一步:添加模块,在MATLAB中运行simulink,打开模块浏览器,然后新建一个模型。

接下来把本次仿真需要的模块添加到模型中。

这里共需要三种模块:与非门4个,离散信号脉冲源8个,示波器3个。

与非门位于simulink模块库中的logocal operater,离散信号源脉冲位于simulink—sources—pulse generator, 示波器位于simulink—sinks—scope。

将这三种模块到拖到一个模型中。

点击与非门模块的名称,即写着Logical Operator的区域,将名称改为Y0,接着点击选中与非门模块不要松开鼠标,按住Ctrl键拖动这个模块到另一个位置,就会复制一个新的Y1模块。

用同样的方法得到Y2,类似地将离散信号脉冲源模块名字改为J0,同样得到J0,J1...J7。

最后将示波器复制三个。

应用matlab数字逻辑电路仿真

创建模型如下:

MATLAB 数字逻辑电路仿真

MATLAB 数字逻辑电路仿真

注意pulse generator模块的参数设置

模块名称 X2 X1 X0

Pulse type sample based sample based sample based

amplitud e 1 1 1

period 2 2 2

3线—8线二进制译码器真值表

X2 X1 X0 Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

0

0 0 0 1 1

0

0 1 1 0 0

0

1 0 1 0 1

1

0 0 0 0 0

0

1 0 0 0 0

0

0 1 0 0 0

0

0 0 1 0 0

0

0 0 0 1 0

0

0 0 0 0 1

0

0 0 0 0 0

0

0 0 0 0 0

MATLAB 数字逻辑电路仿真

A=0101,B=0111实现A+B

MATLAB 数字逻辑电路仿真

§5.2 时序逻辑电路仿真

X1 Xn Z1

组 合 逻 辑 电 路

Zn

触 发 器

MATLAB 数字逻辑电路仿真

基本触发器模块: 1、RS触发器

MATLAB 数字逻辑电路仿真

RS触发器真值表

S 0 0 0 0 R 0 0 1 1 Qn 0 1 0 1 Qn+1 0 1 0 0

注意事项:

对于Pulse Generator的 属性中设置,选用 Sample based、 Amplitude=1、Period=8、 pulse width=1、 phase delay=0,1,2,3, 4,5,6,7、 sample time=1

8-3线编码器1

port( a:in std_logic_vector(7 downto 0);

b:out std_logic_vector(2 downto 0));

End bm8_3;

Architecture one of bm8_3 is

begin

process(a)

begin

case a is

when"01000000"=>b<="110";

when others=>b<="111";

end case;

end process ;

end one;

图7

图8

4.编译文件

在项目导航栏“Project Negatior”中选择文件,点击鼠标右键,选“Set as Top-Level Entity”。

如图9所示,点击编译按钮 。图10为编译成功提示。

图9

图10

5.引脚设置

点击菜单 的 ,如图22所示。

图22

进入如图23所示界面,在 栏中设置引脚,如图23所示。

图23

引脚设置如下:

a[7]PIN_7

a[6]PIN_8

a[5]PIN_9

a[4]PIN_10

a[3]PIN_11

a[2]PIN_12

a[1]PIN_13

0

1

0

1

1

0

0

0

0

0

0

0

0

1

1

1

1

二、实验操作

1.在电脑桌面上点击quartusII快捷方式 。

2.建立工程

如图1所示,点击菜单“File”“New Project Wizard”。进入如图2所示的界面,点击“Next”。

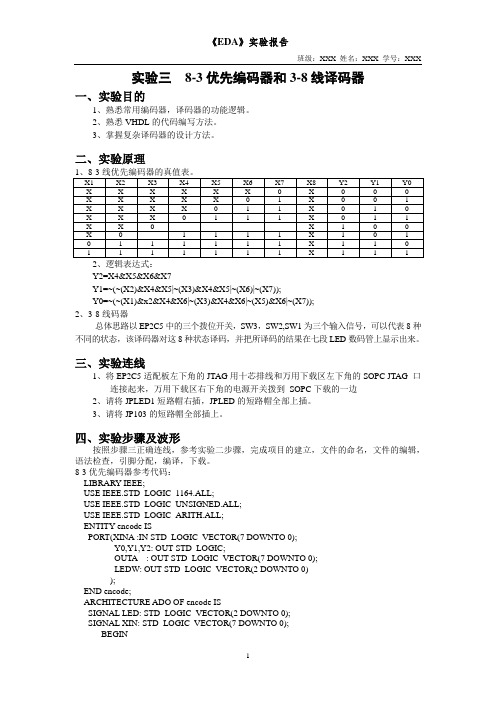

实验三 8-3优先编码器和3-8线译码器

实验三8-3优先编码器和3-8线译码器一、实验目的1、熟悉常用编码器,译码器的功能逻辑。

2、熟悉VHDL的代码编写方法。

3、掌握复杂译码器的设计方法。

二、实验原理2、逻辑表达式:Y2=X4&X5&X6&X7Y1=~(~(X2)&X4&X5|~(X3)&X4&X5|~(X6)|~(X7));Y0=~(~(X1)&x2&X4&X6|~(X3)&X4&X6|~(X5)&X6|~(X7));2、3-8线码器总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

三、实验连线1、将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到SOPC下载的一边2、请将JPLED1短路帽右插,JPLED的短路帽全部上插。

3、请将JP103的短路帽全部插上。

四、实验步骤及波形按照步骤三正确连线,参考实验二步骤,完成项目的建立,文件的命名,文件的编辑,语法检查,引脚分配,编译,下载。

8-3优先编码器参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY encode ISPORT(XINA :IN STD_LOGIC_VECTOR(7 DOWNTO 0);Y0,Y1,Y2: OUT STD_LOGIC;OUTA : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END encode;ARCHITECTURE ADO OF encode ISSIGNAL LED: STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL XIN: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINXIN<=XINA;LEDW<="000";PROCESS (XIN)BEGINCASE XIN ISWHEN x"00" => OUTA<=x"3F";WHEN x"01" => OUTA<=x"06";WHEN x"02" => OUTA<=x"5B";WHEN x"04" => OUTA<=x"4F";WHEN x"08" => OUTA<=x"66";WHEN x"10" => OUTA<=x"6D";WHEN x"20" => OUTA<=x"7D";WHEN x"40" => OUTA<=x"07";WHEN x"80" => OUTA<=x"3F";WHEN OTHERS => OUTA<=x"3F";END CASE;END PROCESS;PROCESS (XIN)BEGINCASE XIN ISWHEN x"01" => LED<="001";WHEN x"02" => LED<="010";WHEN x"04" => LED<="011";WHEN x"08" => LED<="100";WHEN x"10" => LED<="101";WHEN x"20" => LED<="110";WHEN x"40" => LED<="111";WHEN x"80" => LED<="000";WHEN OTHERS => LED<="000";END CASE;END PROCESS;Y2<=LED(2);Y1<=LED(1);Y0<=LED(0);END ADO;3-8译码器参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)V ARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DA TA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;五、实验仿真8-3编码器引脚锁定如图:图5-1图5-2仿真波形如图:3-8译码器引脚锁定如图:图5-3波形如图:图5-4六、实验现象调试ok的EP2C5文件在文件夹decode中,可以直接调用。

应用matlab数字逻辑电路仿真

1

0 1 0 1 0

0

0

0

0

0

0

0

1

1

1

1

由真值表可知逻辑表达式为:

Z X X X X 2 4 5 6 7

Z X X X X 1 2 3 6 7

Z X X X X 0 1 3 5 7

创建模型如下:

注意事项:

对于Pulse Generator的 属性中设置,选用 Sample based、 Amplitude=1、Period=8、 pulse width=1、 phase delay=0,1,2,3, 4,5,6,7、 sample time=1

Sample time 4 2 1

子系统

4线-6线译码器的仿真模型,p119,例5-3

• 注意: 要设置系统的仿真时间为20秒,才能达到图 5-16的效果。

三、全加器 实现4位二进制运算

1、建立全加器子模块

由全加器真值表可知全加器的逻辑表达式为:

SA B C DAB BC AC

创建模型如下:

注意pulse generator模块的参数设置

模块名称 X2 X1 X0

Pulse type sample based sample based sample based

amplitud e 1 1 1

period 2 2 2

Pulse width 1 1 1

Phase delay 1 1 1

二、译码器仿真 利用SIMULINK模块搭建一个3线—8线二进制译码器

3线—8线二进制译码器真值表

X2 X1 X0 Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

0

0 0 0 1 1

电子设计自动化EDA技术实验三报告模板-8线-3线优先编码器设计

2. 器件及管脚逻分配图

管脚分配情况如图,所选器件为 EPM7032AELCC44-4

3. 仿真波形 8 线-3 线优先编码器的仿真波形如下图,从波形可以得出,输入输出 满足前文真值表,电路功能达到设计要求

4. 时序分析图

上述时间分析可以得到,输出信号存在最大 4.5ቤተ መጻሕፍቲ ባይዱ时间延迟,它主要与器件速

度、表达逻辑的合理性有关,选用速度更高器件、优化设计可以使该值降低。 七、结论 采用图形编程法实现了 8 线-3 线优先编码器的设计,并完成了电路的 设计编译、综合、逻辑仿真、时间分析,结果表明采用 ALTRA 的 CPLD 器件 设计的 8 线-3 线优先编码器,时间延迟为不超过 4.5ns 八、思考题 8 线-3 线优先编码器的设计方法还可以通过什么方式实现? 利用 VHDL 实现 8 线 -3 线优先编码器方法多样,还可以通过诸如 case-when 等其他结构实现…..

Y : OUT STD_LOGIC_VECTOR(2 DOWNTO 0); YS,YEX : INOUT STD_LOGIC); END ENCODER; ARCHITECTURE sample OF ENCODER IS BEGIN P1:PROCESS(I,SEL) BEGIN if SEL='1' then Y <="111"; YS <='1'; YEX<='1'; elsif I(7)='0' then Y <="000"; YS <='1'; YEX<='0'; elsif I(6)='0' then Y<="001"; YS <='1'; YEX<='0'; elsif I(5)='0' then Y<="010"; YS <='1'; YEX<='0'; elsif I(4)='0' then Y<="011"; YS <='1'; YEX<='0'; elsif I(3)='0' then Y<="100"; YS <='1'; YEX<='0'; elsif I(2)='0' then Y<="101"; YS <='1'; YEX<='0';

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

利用simulink实现8线3线编码器的设计仿真

1 问题描述(8线3线编码的设计的数学建模)

在数字电路中,编码器、译码器的应用极为广泛。

所谓编码,就是在选定的一系列二值代码中赋予每个代码以固定的含义,执行编码功能的电路统称为编码器。

实现8线3线编码器,它的功能是对输入端的8个信号进行编码,输出三位二进制数。

要求输入信号每次只有一个事0,其余7个是1。

其中0值是待编码信号。

我们将用MATLAB 的simulink软件包实现这种常用的数字组合逻辑电路,并进行仿真。

2. 系统模型及建模分析

根据前面介绍的8线3线编码器的功能,可列出下面得真值表:

有了真值表之后,就可以写出输入输出间的逻辑函数式如下:

在写出逻辑表达式之后,我们就可以用与非门来实现这个表达式。

3. 仿真实现;

在进行仿真时,将在8个输入端依次加一个低电平,然后用3个示波器观察3个输出波形。

用simulink实现这个数学电路系统一共分三个步骤:

第一步:添加模块,在MATLAB中运行simulink,打开模块浏览器,然后新建一个模型。

接下来把本次仿真需要的模块添加到模型中。

这里共需要三种模块:与非门4个,离散信号脉

冲源8个,示波器3个。

与非门位于simulink模块库中的logocal operater,离散信号源脉冲位于simulink—sources—pulse generator,示波器位于simulink—sinks—scope。

将这三种模块到拖到一个模型中。

点击与非门模块的名称,即写着Logical Operator 的区域,将名称改为Y0,接着点击选中与非门模块不要松开鼠标,按住Ctrl 键拖动这个模块到另一个位置,就会复制一个新的Y1模块。

用同样的方法得到Y2,类似地将离散信号脉冲源模块名字改为J0,同样得到J0,J1…J7。

最后将示波器复制三个。

这样一来就将所有模块添加到模型中了。

第二步:修改模块参数

首先双击Y0,打开属性对话框,将操作(Operator)修改为“NAND”,输入节点数改为4,然后点击OK确定。

Y1,Y2也做同样修改。

然后,通过双击示波器模块Scope,得到一个图形界面,在其工具栏上单击打印图标右边的Parameters图标,打开示波器属性设置对话框,将坐标轴改为3,同样地,将示波器Scope1,Scope2的坐标轴数改为4。

最后修改脉冲源的属性。

双击离散脉冲源J0,将看到关于它的属性对话框,可以从对话框中看到5个参数设置,分别为:

Amolititude:方波信号的幅度;

Period:方波信号的周期;

Pulse width: 脉冲宽度;

Sample Time:采样时间长度,以秒为单位。

针对这个例子中的要求,我们需要J0到J7依次为低电平,所以将J0到J7的周期调整为8,脉冲宽度设为7,相位延迟为-7到0,幅度和采样时间用默认值。

这样在零时刻,J0为低电平,其余输入为高电平;过一个采样时间,J1变为低电平。

这样下去,到第七个采样时间,J7变为低电平。

从而实现了设计要求。

第三步:联系及仿真

现在将各模块之间的连线上。

根据输入输出的逻辑表达式,将J1、J3、J5、J7接到Y0的输入,将J2、J3、J6、J7接到Y1的输入,将J4、J5、J6、J7接到Y2 的输入。

然后用示波器Scope监测Y2、Y1、Y0的输出,Scope1 用来监视J0到J3这4个波形,Scope2 用来监视J4到J7这4个波形。

这样我们就完成了连线、

在最后进行仿真之前,先保存结果到自己的工作目录里。

仿真结束后,可以从示波器Scope1,Scope2 上看到编码器的8个输入端的波形,在示

波器Scope中看到编码器输出波形。

4. 实验过程中遇到的问题;

在初建立simulink模型时,我找不到simulink模块浏览器与题相匹配的仿真模块,开始以为是机房MATLAB版本太低,准备要放弃这个课题。

后来通过对相似模块的研究发现,原题中需要的Discrete Pulse Generator 可以通过Pulse Generator 改变time 为Sample **就可以实现。

在设置离散脉冲源信号的时候,没有依次将Phase dalay(相位延迟)设置为-7—0,只是随便设定了一个数字,后来波形出现混乱,无法出现预期效果。

通过对8线3线编码器的研究和其逻辑功能的实现,我明白了其中的不妥,从而做出了改正。

由于对Simulink开始的不熟悉,造成了在连线过程中出现很多阻挠,比如,改变输入输出端口数目的操作,改变输入输出端口方向的操作,设定示波器时间的操作,这样使我开始在连线时,将整个仿真图连得很乱,没有清晰地方向,不能一目了然,通过同学的帮助,和对相关书籍的学习,我基本掌握了Simulink中的基本操作。

在建模过程中,开始也是毫无头绪,虽然有了课题,但是还是无从下手,但是通过研究,结果并没有我想象中那么复杂,只是利用最基本的仿真模块就可以达到预期效果,这让我对Simulink这门技术产生了好感。

5. 仿真结果分析

8线3线编码器仿真后,当输入J0到J7依次以1为单位的相移变化时,示波器的波形跟着变化,如果J0为低电平,则的输出波形为低电平,表示0的二进制数,J4为低电平时,则Y0为低电平,Y1,Y2为高电平,表示4的二进制数,从而实现了编码的功能。

6. 总结

通过对具体模型的建立和利用Simulink的仿真实现,我体会到了实践的重要性,通常一个

模型的建立在开始的时候都是看似很难的,其实,在仔细研究过后,才发现只要认真分析其中的每个细节都能个个攻破,最后达到预想结果,当然,我的这个模型只是具体实际应用中的一个小环节,没有用到太多高功能的技术,但是,我想只要对实际问题认真分析,就能建立一个有利于各种现实问题的解决。

通过对Simulink的学习,我对这门技术产生了兴趣,它能帮助我们更好的解决更多在现实中不可实现的仿真。