分立元件逻辑门共44页

电子课件电子技术基础第六版第六章门电路及组合逻辑电路可编辑全文

逻辑函数除可以用逻辑函数表达式(逻辑表达式)表示以 外,还可以用相应的真值表以及逻辑电路图来表示。真值表 与前述基本逻辑关系的真值表类似,就是将各个变量取真值 (0 和 1)的各种可能组合列写出来,得到对应逻辑函数的真 值(0 或 1)。逻辑电路图(逻辑图)是指由基本逻辑门或复 合逻辑门等逻辑符号及它们之间的连线构成的图形。

TTL 集成“与非”门的外形和引脚排列 a)外形 bOS 集成门电路以绝缘栅场效应管为基本元件组成, MOS 场效应管有 PMOS 和NMOS 两类。CMOS 集成门电路 是由 PMOS 和 NMOS 组 成的互补对称型逻辑门电路。它具 有集成度更高、功耗更低、抗干扰能力更强、扇出系数更大 等优点。

三、其他类型集成门电路

1. 集电极开路与非门(OC 门) 在这种类型的电路内部,输出三极管的集电极是开路的, 故称集电极开路与非门,也称集电极开路门,简称 OC 门。

OC 门 a)逻辑符号 b)外接上拉电阻

74LS01 是一种常用的 OC 门,其外形和引脚排列如图所 示。

74LS01 的外形和引脚排列 a)外形 b)引脚排列

2. 主要参数 TTL 集成“与非”门的主要参数反映了电路的工作速度、抗 干扰能力和驱动能力等。

TTL 集成“与非”门的主要参数

TTL 集成“与非”门具有广泛的用途,利用它可以组成很多 不同逻辑功能的电路,其外形和引脚排列如图所示。如 TTL“ 异或”门就是在 TTL“与非”门的基础上适当地改动和组合而成 的;此外,后面讨论的编码器、译码器、触发器、计数器等 逻辑电路也都可以由它来组成。

实验一分立元件(由二极管三极管组成的)逻辑门电路

实验一分立元件(由二极管三极管组成的)逻辑门电路一、实验目的1.熟悉并掌握由二极管、三极管组成的逻辑门电路。

2.掌握数字电路实验装置及示波器的使用方法。

二、实验仪器与器材1.数字电路实验装置2.双踪示波器三、预习要求1.复习二极管、三极管的开关特性。

2.了解双踪示波器的使用方法。

四、实验内容与步骤(一)二极管与门电路实验步骤:1、按图-1所示连接电路2、检查无误后,按表-1所列的真值表设置开关K、2K的状态,1开关闭合表示为“0”,开关断开或发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=AB。

(注:K=A,2K=B,Y代表发光二极管。

下同)13、根据真值表和逻辑关系式Y=AB,总结二极管与门电路的功能为“全高则高,有低则低”。

图-1 二极管与门电路表-1 真值表(二)二极管或门电路 实验步骤:1、按图-2所示连接电路。

2、检查无误后,按表-2所列的真值表设置开关1K 、2K 的状态,开关闭合表示为“1”,开关断开表示为“0”,发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=A+B 。

图-2 二极管或门电路 表-2 真值表3、根据真值表和逻辑关系式Y=A+B ,总结二极管或门电路的功能为“全低则低,有高则高”。

(三)三极管非门电路实验步骤:1、按图-3所示连接电路2、检查无误后,按表-3所列的真值表设置开关K 的状态,开关闭合表示为“1”, 开关断开表示为“0”,发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-3中,应符合逻辑关系式Y=A 。

3、根据真值表和逻辑关系式Y=A ,总结三极管非门电路的功能相当于反相器“是低则高,是高则低”。

(注:K=A )图-3 三极管非门电路 表-3 真值表(四)三极管与非门电路实验步骤:1、按图-4所示连接电路2、检查无误后,按表-4所列的真值表设置开关1K 、2K 的状态,开关闭合表示为“0”,开关断开或发光二极管亮表示为“1”,然后检测每次的输出端的状态填入表-1中,应符合逻辑关系式Y=AB 。

分立元件逻辑门的级联

分立元件逻辑门的级联在数字电路设计中,分立元件逻辑门的级联是一种常见的组合逻辑方法。

分立元件逻辑门包括与门、或门、非门等基本逻辑门,通过合理地连接这些逻辑门,可以实现复杂的数字逻辑电路。

级联是将多个逻辑门按照一定的方式相互连接,以实现更丰富的功能。

首先,我们来了解一下分立元件逻辑门的原理及应用:1. 与门:与门(AND gate)接收两个或多个输入信号,当所有输入信号都为高电平(通常表示为1)时,输出为高电平;否则,输出为低电平(通常表示为0)。

与门广泛应用于组合逻辑电路的设计中。

2. 或门:或门(OR gate)接收两个或多个输入信号,当任意一个输入信号为高电平时,输出为高电平;只有当所有输入信号都为低电平时,输出才为低电平。

或门常用于构建多路选择器、编码器等电路。

3.非门:非门(NOT gate)只接收一个输入信号,输出信号与输入信号相反。

非门常用于信号反相、时序控制等场合。

在了解了基本逻辑门的工作原理后,我们可以将它们级联以实现更复杂的逻辑功能。

以下是一个分立元件逻辑门级联的例子:假设我们有一个输入信号A和两个输出信号Y和Z。

我们可以通过以下逻辑电路实现输出Z与输入A的反相(即Z= NOT A):1. 将输入信号A接入非门(NOT gate)的输入端,得到输出信号B(B= NOT A)。

2. 将输出信号B与输入信号A接入与门(AND gate),得到输出信号C(C= A·B)。

3. 将输出信号C接入非门(NOT gate),得到输出信号Z(Z= NOT C = NOT(A·B))。

通过这个级联电路,我们实现了输出信号Z与输入信号A的反相。

此外,我们还可以通过调整逻辑门的连接方式,实现其他复杂的逻辑功能。

分立元件逻辑门的级联在数字电路设计中具有重要意义。

掌握这种方法,有助于我们更好地理解数字逻辑电路的工作原理,并灵活地设计出满足实际需求的数字电路系统。

同时,分立元件逻辑门的级联也是学习现代数字电子技术的基础,对于深入理解计算机原理、嵌入式系统等领域具有重要意义。

分立元件逻辑门

(2-18)

§2.3

TTL与非门 TTL与非门

二、输入、输出负载特性 输入、

1. 扇出系数 扇出系数: &

与非门电路输出能驱动同类门的个数。 与非门电路输出能驱动同类门的个数。

?

&

分两种情况讨论: 分两种情况讨论:

(1)前级输出为 高电平时 ) (2)前级输出为 低电平时 )

(2-9)

§2.3

TTL与非门 TTL与非门

+5V

R1 R2 T3 R5 T5 R4

A B C

T1

T2

T4

F

T1 —多发射极晶 多发射极晶 体管:实现“ 体管:实现“与” R3 运算。 运算。

输入级

中间级

输出级

(2-10)

§2.3

TTL与非门 TTL与非门

+5V

R1 R2 T3 R5 T5 R3 R4 复合管形式 A B C

OC门可以实现“线与”功能。 门可以实现“线与”功能。 门可以实现 UCC & F1 & F2 & F3 分析: 任一导通, 分析:F1、F2、F3任一导通,则F=0。 。 F1、F2、F3全截止,则F=1 。 全截止, RL F

UCC RL T5 T5 T5

T1

T2

T4

F

“与” 与

“非” 非

输出级

与非门

(2-11)

二、工作原理 1. 任一输入为低电平(0.3V)时 任一输入为低电平( )

不足以让 T2、T5导通 、 R1 3k 0.7V b1 R2 750Ω Ω T2 T3 3k R5

§2.3

TTL与非门 TTL与非门

分立器件逻辑门电路PPT模板

uY=uA+ =uB+ =(0+0.7)V=0.7V ② uA=0V、uB=3V,看起来这两个二极管都应导通,因为它们的正极都通 过R0接到了+VCC。但是,由于uA、uB电平不同,当D1导通后,使uY=uA+ =(0+0.7)V=0.7V,导致 =uY-uB=(0.7-3)V=-2.3V,即二极管D2承受的是反向电压, 故截止。通常二极管导通之后,如果其负极电位不变,那么它的正极电位就 固定在比负极高0.7V的电位上,如果其正极电位不变,那么它的负极电位就 固定在比正极低0.7V的电位上,导通二极管的这种作用称为钳位。

① uA=uB=0V时,D1、D2均导通,uY=(0-0.7)V=-0.7V。 ② uA=0V、uB=3V时,D2导通,D1反向偏置截止,uY=(3-0.7)V=2.3V。 ③ uA=3V、uB=0V时,D1导通,D2反向偏置截止,uY=(3-0.7)V=2.3V。 ④ uA=uB=3V时,D1、D2均导通,uY=(3-0.7)V=2.3V。

2)设定变量、状态赋值、列真值表 ① 设定变量:用A、B、Y分别表示uA、uB、uY。 ② 状态赋值:用0表示低电平,用1表示高电平。 ③ 列真值表:根据设定的变量和状态赋值情况,由上表即可列出如下表所 示的与门的逻辑真值表。

与门的逻辑真值表 由上表可以看出输入信号A、B与输出信号Y之间的关系满足与逻辑关系, 即Y=AB,所以图6-1(a)所示电路确实实现了与的逻辑功能,是一个二极管与 门电路。

③ uA=3V、uB=0V,情况与②中是类似的,只不过此时导通的是D2,截止的 是D1而已。D2导通后就把uY钳位在0.7V,即

7.分立元件门电路ppt课件

5 0.7 iB 4.3 mA 1mA

1 0

YA

14

三、动态开关特性

uI UIH

UIL O iC 0.9IC(sat)

0.1IC(sat) O uO VCC

IC(sat)

ton

toff

uI正跳变到iC上升到 0.9IC(sat)所需的时间ton称 为三极管开通时间。

uI负跳变到iC下降到

t

0.1IC(sat)所需的时间toff称 为三极管关断时间。

6

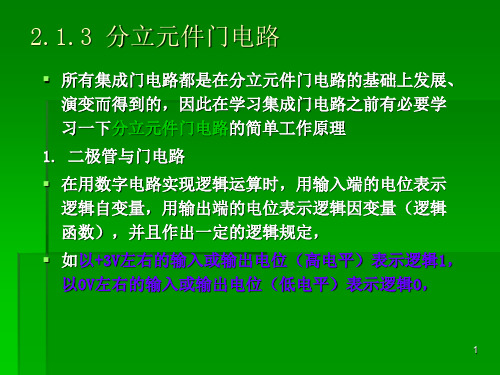

3.2 分立元件门电路

主要要求:

理解二极管的开关特性。 理解三极管的开关特性、工作条件

7

一、二极管的开关特性

iD(mA)

IF

UBR

uD(V)

0

0.5 0.7

D

+ ui=0V -

+

RL uo -

D

+

+

ui

RL uo

-

-

开关电路

D

+ +-

+

ui=5V 0.7V RL uo

-

-

ui=0V时,二极管截止,如 同开关断开,uo=0V。

A BC

A B& C

& &Y

2

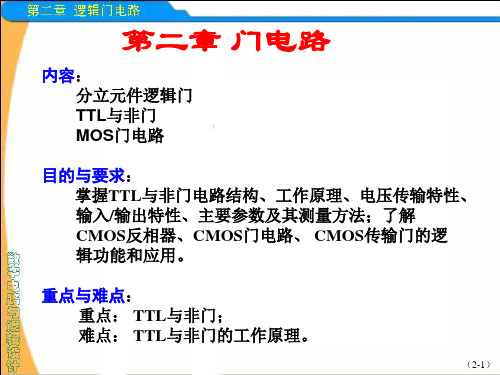

第3章 集成逻辑门电路

分立元器件门电路 TTL集成门电路 CMOS集成门电路 本章小结

3

3.1 概 述

主要要求:

了解逻辑门电路的作用和常用类型。 理解高电平信号和低电平信号的含义。

4

一、门电路的作用和常用类型

门电路(Gate Circuit)

指用以实现基本逻辑关系和 常用复合逻辑关系的电子电路。

课题五-分立元件门电路及TTL集成门电路PPT

•

R2

T2

饱和

•

uF=0.3V

结论2:输入全高时,输出为低

R3

+5V

T5饱和, Vce5=0.3V

F

T5

饱和

工作原理小结: 1. 输入有低电平(0.3V)时

VF=3.6V

2. 输入全为高电平(3.6V)时 VF=0.3V

3. 逻辑功能 FABC

T1深饱和

T2截止

T3微饱和

T4放大 T5截止

T1:倒置 T2:饱和 T3:放大 T4:截止 T5:饱和

+5V

A

B C

R1 3k

b1 c1 T1

• E2

T输T实的CR212与现和入2R5运了基级T算输极由3。入电多中级和的发变组发••间 ,R集射3量TR射R级由电极组144A极组是T极E成RV、c22晶成c、可放C,(B2体R以,大5T和、VF22)管它C

•A

输出F级:A由TB3、CT4、T5和R4、R5

集

晶体三极管----晶体三极管逻辑门 (TTL)

成 双极型 射极耦合逻辑门 (ECL)

逻

集成注入逻辑门电路 ( I 2 L)

辑

N沟道MOS门 (NMOS)

门 单极型(MOS型) P 沟道MOS门 (PMOS)

互补MOS门 (CMOS)

集成:把晶体管、电阻、和导线等封装在一个芯片上。

3.1 电路

•

•

V1

阻的增加,反向电流逐渐减小,直至

漏电流Is。

反向恢复时间 tre

ID

电流I由 2VR2 0.1I2,所需的时间。 I1

说明: ⑴转换时间:截止→导通 较小

导通→截止较大

⑵V故i的D最的高开频关率时以间1以0 ttrree来来衡取量值。。

数字逻辑课件——分立元件门电路

6 0.7 VO 5 5 5 0.7 3.35V

当用万用表测B点电压时,D2导通, VB应为

VB VO VD

3.35 0.7 2.65V

20

例2.3 反相器原理分析

▪ 三极管T构成的反相器电路如图所示。已知三极管T的VBE = 0.7V, = 30,T饱和时的管压降VCES 0V 。试计算: (1) 当VI为何值时,

uY = 0V + 0.7V = 0.7V ≈ 0V。VD1截止。 4. uA = uB = 3V。

二极管VD1和VD2都导通,

uY = 3 V+ 0.7V = 3.7V ≈ 3V。

4

输出电位与输入电位uA ,uB的关系示于下面左表中,按正

逻辑规定,即高电位代表逻辑1,低电位代表逻辑0,可得

下面右表所示真值表,说明电路实现的是“与”逻辑关系,

(3) 在电路输出为高电平时,由于钳位电路的存 在,VOH 值应为VOH = EQ + VD = 2.9 + 0.7 =3.6V

这时,电路允许的外拉电流ILH应满足

I LH

VCC VOH RC

9 3.6 5.4mA 1

当外拉电流超过5.4mA时, VOH将随ILH的进一步增大 而下降。

24

VB (VBB ) VCC VCES

R2

RC

代入已知参数

VI 0.7 0.7 (9) 9 0

2

20 301

解得 VI 2.27V

当VI大于2.27V时,三 极管T进入饱和状态。

22

(2) 在VI = 3.0V时,可求得三极管基极偏置电流

IB

逻辑门电路PPT课件

IC(Integrated Circuits):将元、器件制作在同一硅片上, 以实现电路的某些功能。 SSI(Small-Scale Integration): 10个门电路。 MSI(Medium-Scale Integration):10~100个门电路。 LSI(Large-Scale Integration):1000~10000个门电路。 VLSI(Very Large-Scale Integration): 10000个门电路。

VT5

集成门电路——TTL与非门电路

可以线与的TTL门电路

TSL门电路除正常输入端A、B,输出端F外,增加了控制端口C,

C=1,电路完成正常与非功能;C=0时,输出端对地呈现高阻状态。

将C称为控制端或使能端。三态门的基本用途是在数字系统中构成

总线(Bus)。

a.单向总线。

b.双向总线。

G1

G1

总线

单极型集成逻辑门电路:集成逻辑门是以单极型晶体管(只有一 种极性的载流子:电子或空穴)为基础的。目前应用得最广泛的 是金属—氧化物—半导体场效应管逻辑电路(Metal Oxide Semiconductor, MOS)。

集成门电路——概 述

衡量门电路的性能指标

1.传输延迟时间(Transmission Delay Time) 2.功耗(Power Dissipation) 3.逻辑电平(Logic Level) 4.阈值电压(Threshold Voltage) 5.噪声容限(Noise Margin) 6.扇入(Fan—In),扇出(Fan—Out) 7.工作温度范围(Operating Temperature Range)

集成门电路——TTL与非门电路

半导体器件开关特性及分立元器件门电路

分立元件基本逻辑门电路

分立元件基本逻辑门电路1、二极管与门电路图1(a)所示是二极管与门电路,它有两个输入端A和B,一个输出端Y。

也可以认为A和B是它的两个输入信号或称输入变量,Y是输出信号或称输出变量。

图1(b)和(c)所示分别为与门电路的规律符号和波形图。

(a)电路(b)规律符号(c)波形图图1 二极管与门电路当输入变量A和B全为1时(设两个输入端的电位均为3V),电源+5V 的正端经电阻R向两个输入端流通电流(电源的负端接“地”,图中未标出),和两管都导通,输出端Y的电位略高于3V(因二极管的正向电压降有零点几伏),因此输出变量Y为1。

当输入变量不全为1,而有一个或两个全为0时,即该输入端的电位在0V四周。

例如A为0,B为1,则优先导通。

这时输入端Y的电位也在0V四周,因此Y为0。

因承受反向电压而截止。

只有当输入变量全为1时,输出变量Y才为1,这合乎与门的要求。

与规律关系式为(1)图1(a)有两个输入端,输入信号有1和0两种状态,共有四种组合,因此可用表1完整地列出四种输入、输出规律状态。

它可和图12.2(c)的波形图相对比。

表1 与门规律状态表ABY000010100111 2、二极管或门电路图2(a)所示是二极管或门电路。

比较一下图1(a)和图2(a)就可看出,后者二极管的极性与前者接得相反,其阴极相连经电阻R接“地”。

(a)电路(b)规律符号(c)波形图图2 二极管或门电路当输入变量只要有一个为1时,输出就为1。

例如A为1,B为0,则优先导通,输出变量Y也为1。

因承受反向电压而截止。

只有当输入变量全为0时,输出变量Y才为0,此时两只二极管都截止。

或规律关系式为(2)表2是或门的输入、输出规律状态表,它可和图2(c)的波形图相对比。

图2(b)是或门电路的规律符号。

表2 或门规律状态表ABY000011101111 3、晶体管非门电路图3(a)所示是晶体管非门电路。

晶体管非门电路不同于放大电路,管子的工作状态或从截止转为饱和,或从饱和转为截止。