逻辑门电路- 【PPT课件】

合集下载

《逻辑门电路》PPT课件

b

电子,形成电流ICN R b

P N I E N I E P

VC C

➢另外,集电结区的少 V B B

数载流子形成漂移电流

e IE

ICBO

两种载流子参与导电——双极性晶体管Bipolar Junction Transistor

2021-09-22

中国科学技术大学 快电子 刘树彬

17

BJT的开关工作状态

《逻辑门电路》PPT课件

本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢! 本课件PPT仅供大家学习使用 学习完请自行删除,谢谢!

第三章 逻辑门电路

3.1 MOS逻辑门电路 3.2 TTL逻辑门电路 3.3 射极耦合门电路 3.5 逻辑描述中的几个问题 3.6 逻辑门电路使用中的几个实际问题

7

N型半导体

在本征半导体中掺入五价杂质元素,如磷、砷等

硅原子 + 4

多余电子

+4

磷原子

+4

+4

+4

电子空穴对 自由电子

N型半导体

+5 +4

++ + + ++ + +

+3;

2021-09-22

多数载流子——自由电子 少数载流子—— 空穴

中国科学技术大学 快电子 刘树彬

施主离子

8

PN结

2021-09-22

中国科学技术大学 快电子 刘树彬

t1

t

IFVFR LVDV RF L

0.1IR t

数字逻辑课件——门电路概述

其中,i为流过二极管的电流;u为加到二极

管两端的电压;UT

kT q

k为玻耳兹曼常数,T为热力学温度,q为电子电荷, 在常温下(即结温为27℃,T = 300K),VT ≈26mV; IS为反相饱和电流。

它和二极管的材料、工艺和尺寸有关,但对每只二 极管而言,它是一个定值。

9

i

二极管的特性也可用图 2-1-4的伏安特性曲线描 述。

5

2.1.2 半导体器件的开关特性

▪ 1. 半导体二极管的开关特性

因为半导体二极管具有单向导

电性,即外加正电压时导通,

+VCC

外加反电压时截止,所以它相

当于一个受外加电压极性控制

D

R

的开关,

uI

uO

S

如果用它取代图2-1-1中的S, 图2-1-3 二极管开关电路 就得到了图2-1-3所示的二极

管开关电路。

•以图2-1-10为例,设图中MOS管为

N沟道增强型,它的开启电压为UTN , 则当uI = uGS < UTN时,MOS管工作

在截止区,D-S之间没有形成导电 沟道,沟道间电阻为109~1010Ω, 呈高阻状态,因此D-S间的状态就

像开关断开一样。

图2-1-10 MOS管的 开关电路

20

当uI = uGS > UTN时,且uGD > UTN,则

当uI ≤ 0时,uBE ≤ 0,三极管工

作在截止区,其工作特点是基极电

流iB ≈ 0,集电极电流iC = ICE

≈ 0,因此三极管的集-射极之间 相当于一个断开的开关。

输出电压为uo = UOH ≈ VCC 。

图2-1-7 双极型三 极管开关电路

16

门电路及组合逻辑电路ppt课件.ppt

二-十进制代码:用4位二进制数b3b2b1b0来表示十进 制数中的 0 ~ 9 十个数码。简称BCD码。

用四位自然二进制码中的前十个码字来表示十进制数码, 因各位的权值依次为8、4、2、1,故称8421码。

2421码的权值依次为2、4、2、1;余3码由8421码加0011 得到;格雷码是一种循环码,其特点是任何相邻的两个码字, 仅有一位代码不同,其它位相同。

即:(5555)10=5×103 +5×102+5×101+5×100 又如:(209.04)10= 2×102 +0×101+9×100+0×10-1+4 ×10-2

(1)数制:二进制

数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2-2

A

&

B

≥1 &

C

&

D

(a) 与或非门的构成

A

FB C

& ≥1 F

D

(b) 与或非门的符号

F AB CD

4、异或

异或是一种二变量逻辑运算,当两个变量取值相同时, 逻辑函数值为0;当两个变量取值不同时,逻辑函数值为1。

异或的逻辑表达式为: L A B

“异或”真值

表 输入

输出

A

B

L

A

=1

0

0

0

0

常用 BCD 码

十进制数 8421 码 余 3 码 格雷码 2421 码

0

0000 0011 0000 0000

1

0001 0100 0001 0001

2

0010 0101 0011 0010

用四位自然二进制码中的前十个码字来表示十进制数码, 因各位的权值依次为8、4、2、1,故称8421码。

2421码的权值依次为2、4、2、1;余3码由8421码加0011 得到;格雷码是一种循环码,其特点是任何相邻的两个码字, 仅有一位代码不同,其它位相同。

即:(5555)10=5×103 +5×102+5×101+5×100 又如:(209.04)10= 2×102 +0×101+9×100+0×10-1+4 ×10-2

(1)数制:二进制

数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2-2

A

&

B

≥1 &

C

&

D

(a) 与或非门的构成

A

FB C

& ≥1 F

D

(b) 与或非门的符号

F AB CD

4、异或

异或是一种二变量逻辑运算,当两个变量取值相同时, 逻辑函数值为0;当两个变量取值不同时,逻辑函数值为1。

异或的逻辑表达式为: L A B

“异或”真值

表 输入

输出

A

B

L

A

=1

0

0

0

0

常用 BCD 码

十进制数 8421 码 余 3 码 格雷码 2421 码

0

0000 0011 0000 0000

1

0001 0100 0001 0001

2

0010 0101 0011 0010

数字电子技术逻辑门电路课件

F 1 0

数字电子技术-逻辑门电路

二极管与门/或门电路的缺点

(1)在多个门串接使用时,会出现低电平偏离标准数值 的情况。 (2)负载能力差。

+VCC(+5V)

R 3kΩ

D1

0V

D2

5V

D1

p

5V

D2

0.7V

+VCC(+5V) R 3kΩ

L

RL

1.4V

数字电子技术-逻辑门电路

解决办法:

将二极管与门(或门)电路和三极管非门电路组 合起来。

1

3

2T 3

Hale Waihona Puke R e21kΩ输入级

中间级

输出级

数字电子技术-逻辑门电路

TTL与非门的逻辑关系分析

1、输入全为高电平3.6V时。

T2、T3饱和导通, 由于T2饱和导通,VC2=1V。

由于T3饱和导通,输出电压为: VO=VCES3≈0.3V

T4和二极管D都截止。

实现了与非门的逻 辑功能之一: 输入全为高电平时, 输出为低电平。 A

管相当于一个闭合的开关。

D

K

V

F

IF

RL

V

F

IF

RL

数字电子技术-逻辑门电路

半导体二极管的理想开关特性

(2)加反向电压VR时,二极管截止,反向电流IS可忽略。二

极管相当于一个断开的开关。

D

K

V

R

IS

RL

V

R

RL

iD

理想二极管 伏安特性

uD

0V

数字电子技术-逻辑门电路

半导体二极管的实际开关特性

实际的硅二极管正向导通时,存在 一个0.7V的门槛电压(锗二极管为 0.3V),其伏安特性曲线为:

数字电子技术-逻辑门电路

二极管与门/或门电路的缺点

(1)在多个门串接使用时,会出现低电平偏离标准数值 的情况。 (2)负载能力差。

+VCC(+5V)

R 3kΩ

D1

0V

D2

5V

D1

p

5V

D2

0.7V

+VCC(+5V) R 3kΩ

L

RL

1.4V

数字电子技术-逻辑门电路

解决办法:

将二极管与门(或门)电路和三极管非门电路组 合起来。

1

3

2T 3

Hale Waihona Puke R e21kΩ输入级

中间级

输出级

数字电子技术-逻辑门电路

TTL与非门的逻辑关系分析

1、输入全为高电平3.6V时。

T2、T3饱和导通, 由于T2饱和导通,VC2=1V。

由于T3饱和导通,输出电压为: VO=VCES3≈0.3V

T4和二极管D都截止。

实现了与非门的逻 辑功能之一: 输入全为高电平时, 输出为低电平。 A

管相当于一个闭合的开关。

D

K

V

F

IF

RL

V

F

IF

RL

数字电子技术-逻辑门电路

半导体二极管的理想开关特性

(2)加反向电压VR时,二极管截止,反向电流IS可忽略。二

极管相当于一个断开的开关。

D

K

V

R

IS

RL

V

R

RL

iD

理想二极管 伏安特性

uD

0V

数字电子技术-逻辑门电路

半导体二极管的实际开关特性

实际的硅二极管正向导通时,存在 一个0.7V的门槛电压(锗二极管为 0.3V),其伏安特性曲线为:

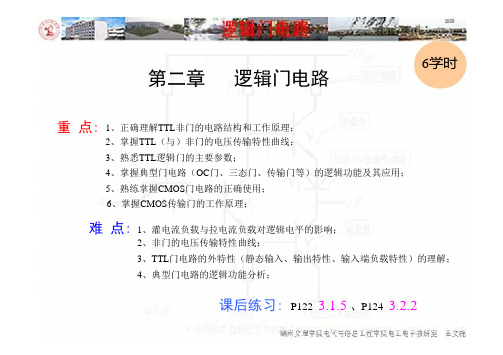

第2章-逻辑门电路

类似74HC,可直接与TTL接口

高速,可代替74HC

高速,可代替74HCT

2.4.1.MOS反相器

2. MOS反相器

(1)电阻负载MOS电路:

如图2-37(a)所示,在这种反相器 中,输入器件是增强型MOS管,负载是线性 电阻。这种反相器在集成电路中很少采用。

(2)E/E MOS(Enhancement/Enhancement MOS) 反相器:

2.三态输出门电路(TSL门) 图227 三态门

三态输出门电路简称三态门,用 TSL(Three Sate Logic)表示,TSL电路的 主要特点是输出共有3种状态,即逻辑高电 平、逻辑低电平和高阻态。

图2-27所示为三态门电路及逻辑符号。 图中EN为三态使能端,A、B为输入逻辑变 量,Y为电路输出。

74F

速度比标准系列快近5倍, 功耗低于标准系列

2.2.1.TTL与非门的典型电路 及工作原理

1. 电路结构

电路由输入级、中间级和输出级三部 分组成。

2. 基本工作原理

(1)TTL工作在关态(截止态)

当输入信号A、B、C中少一个为低电 位(0.3V)时:

VO = VOH = VCC – VR2 – VBE3 – VD4 =5V-0.7V-0.7V =3.6V

实现了输出高电平,此时TTL工作在关 态,也称截止态。

(2)TTL工作在开态(饱和态)

输出电压Vo为

VO = VOL = VCES4 = 0.3V 实现了输出低电平,此时TTL工作在开 态,也称饱和态。

通过以上分析可知,当输入信号中至 少一个为低电位,即VI=ABC= VIL时,输出 高电平,即VO = VOH ;当输入信号全部为 高电位时,即VI=ABC= VIH时,输出低电平, 即VO = VOL。说明电路实现了与非门的逻辑 关系,即

高速,可代替74HC

高速,可代替74HCT

2.4.1.MOS反相器

2. MOS反相器

(1)电阻负载MOS电路:

如图2-37(a)所示,在这种反相器 中,输入器件是增强型MOS管,负载是线性 电阻。这种反相器在集成电路中很少采用。

(2)E/E MOS(Enhancement/Enhancement MOS) 反相器:

2.三态输出门电路(TSL门) 图227 三态门

三态输出门电路简称三态门,用 TSL(Three Sate Logic)表示,TSL电路的 主要特点是输出共有3种状态,即逻辑高电 平、逻辑低电平和高阻态。

图2-27所示为三态门电路及逻辑符号。 图中EN为三态使能端,A、B为输入逻辑变 量,Y为电路输出。

74F

速度比标准系列快近5倍, 功耗低于标准系列

2.2.1.TTL与非门的典型电路 及工作原理

1. 电路结构

电路由输入级、中间级和输出级三部 分组成。

2. 基本工作原理

(1)TTL工作在关态(截止态)

当输入信号A、B、C中少一个为低电 位(0.3V)时:

VO = VOH = VCC – VR2 – VBE3 – VD4 =5V-0.7V-0.7V =3.6V

实现了输出高电平,此时TTL工作在关 态,也称截止态。

(2)TTL工作在开态(饱和态)

输出电压Vo为

VO = VOL = VCES4 = 0.3V 实现了输出低电平,此时TTL工作在开 态,也称饱和态。

通过以上分析可知,当输入信号中至 少一个为低电位,即VI=ABC= VIL时,输出 高电平,即VO = VOH ;当输入信号全部为 高电位时,即VI=ABC= VIH时,输出低电平, 即VO = VOL。说明电路实现了与非门的逻辑 关系,即

电子技术基础数字部分第二章逻辑门电路经典课件

V5

A

V1

V2

F 输出管

V3

R2

输入级

中间级 (推拉式)输出级

(中间放大且驱动互补输出)

(1)A=1时,V1管处于发射结与集电结倒置使用放大状态,V2、V3导通,V4截止,有F=0;

VCC

+2.5V

高电平箝位电路提高输出的正向抗干扰能 力;(低电平输入时正向波动导致V导通,

但只要仍有IQ的存在即VZ导通,仍可以保证 高电平输出)

加速电容

A

提高低电平输入的 正向抗干扰能力

IRC RC

VZ

IQ

Cb

F

Rb

V

R' VCC

饱和的深度提高高电平输入时的负向抗干扰能力; 但饱和深度又降低了开关速度,增加了电路损耗;

1、逻辑非:某件事物发生的条件与结果相反的逻辑关系。 2、非门:实现逻辑非运算,且单端输入单端输出的电路。

3、BJT非逻辑电路基本结构及工作原理

VCC

Rb

A

RC

V

F

电位表

VA VF V 0V 5V 止 5V 0.3V 通

4、非门符号

1

A

F

实现了非 逻辑功能

真值表

AF 01 10

5、BJT非逻辑电路改进

CMOS负载

V OH(min)/V TTL负载

CMOS负载

V OL(max)/V TTL负载

VDD/VCC/V tpd/ns PD/mW NO VNH/V VNL/V

CMOS

74HC 74HCT

0.001 -0.001 -0.02

-4

0.001 -0.001 -0.02

-4

0.02

第6部分逻辑门电路-

PMOS电路。由P沟道MOS管构成,制造工 艺简单,但工作速度较低。

NMOS电路。由N沟道MOS管构成,制造工 艺复杂,但工作速度优于PMOS电路。

33

2019/10/26

CMOS电路。由PMOS管和NMOS管构成的互补对称型 MOS电路,优点是静态功耗低、抗干扰能力强、工作 稳定性好、开关速度较高。虽然制作工艺相对复杂、成 本偏高,但由于其优点突出,是现在发展最快、应用广 泛的一种集成电路。

34

2019/10/26

6.3.1 常见CMOS门电路

1. CMOS与非门 高速CMOS集成电路54/74HC00为四2输入与非门,

即内部集成了四个2输入与非门,

35

2019/10/26

36

2019/10/26

2. CMOS或非门 高速CMOS集成电路54/74HC02为2输入四或非门。

37

2019/10/26

砷、锑等)。 杂质原子的五个价电子与周围硅原子组成共价键时,

多出一个价电子,使晶体产生一个自由电子。 根据掺入杂质的多少,可以控制自由电子的数量。

由于自由电子的数量远远大于空穴的数量,这种半导体 导电以自由电子导电为主。将自由电子称为多数载流子, 简称多子;空穴称为少数载流子,简称少子。

9

2019/10/26

(1)电源规则 电源极性不能接反,否则将会造成集成电路的

永久损坏。另外,电源电压应保持在最大极限电压范 围之内。电源电压越高,电路抗干扰能力就越强,允 许的工作频率就越高,但功耗会相应增大。

43

2019/10/26

(2)输入规则 与TTL门电路不同,CMOS门电路的多余输入端禁

止悬空,而应采取如下措施: ①多余的与输入端接VDD或高电平。 ②多余的或输入端接VSS或低电平,也可以通过电

NMOS电路。由N沟道MOS管构成,制造工 艺复杂,但工作速度优于PMOS电路。

33

2019/10/26

CMOS电路。由PMOS管和NMOS管构成的互补对称型 MOS电路,优点是静态功耗低、抗干扰能力强、工作 稳定性好、开关速度较高。虽然制作工艺相对复杂、成 本偏高,但由于其优点突出,是现在发展最快、应用广 泛的一种集成电路。

34

2019/10/26

6.3.1 常见CMOS门电路

1. CMOS与非门 高速CMOS集成电路54/74HC00为四2输入与非门,

即内部集成了四个2输入与非门,

35

2019/10/26

36

2019/10/26

2. CMOS或非门 高速CMOS集成电路54/74HC02为2输入四或非门。

37

2019/10/26

砷、锑等)。 杂质原子的五个价电子与周围硅原子组成共价键时,

多出一个价电子,使晶体产生一个自由电子。 根据掺入杂质的多少,可以控制自由电子的数量。

由于自由电子的数量远远大于空穴的数量,这种半导体 导电以自由电子导电为主。将自由电子称为多数载流子, 简称多子;空穴称为少数载流子,简称少子。

9

2019/10/26

(1)电源规则 电源极性不能接反,否则将会造成集成电路的

永久损坏。另外,电源电压应保持在最大极限电压范 围之内。电源电压越高,电路抗干扰能力就越强,允 许的工作频率就越高,但功耗会相应增大。

43

2019/10/26

(2)输入规则 与TTL门电路不同,CMOS门电路的多余输入端禁

止悬空,而应采取如下措施: ①多余的与输入端接VDD或高电平。 ②多余的或输入端接VSS或低电平,也可以通过电

数字电子技术-逻辑门电路PPT课件

在电路中的应用。

或非门(NOR Gate)

逻辑符号与真值表

描述或非门的逻辑符号,列出其对应的真值表, 解释不同输入下的输出结果。

逻辑表达式

给出或非门的逻辑表达式,解释其含义和运算规 则。

逻辑功能

阐述或非门实现逻辑或操作后再进行逻辑非的功 能,举例说明其在电路中的应用。

异或门(XOR Gate)

逻辑符号与真值表

01

02

03

Байду номын сангаас

04

1. 根据实验要求搭建逻辑门 电路实验板,并连接好电源和

地。

2. 使用示波器或逻辑分析仪 对输入信号进行测试,记录输

入信号的波形和参数。

3. 将输入信号接入逻辑门电 路的输入端,观察并记录输出

信号的波形和参数。

4. 改变输入信号的参数(如频 率、幅度等),重复步骤3, 观察并记录输出信号的变化情

THANKS

感谢观看

低功耗设计有助于提高电路效率和延长设 备使用寿命,而良好的噪声容限则可以提 高电路的抗干扰能力和稳定性。

扇入扇出系数

扇入系数

指门电路允许同时输入的最多 信号数。

扇出系数

指一个门电路的输出端最多可 以驱动的同类型门电路的输入 端数目。

影响因素

门电路的输入/输出电阻、驱动 能力等。

重要性

扇入扇出系数反映了门电路的驱动 能力和带负载能力,对于复杂数字 系统的设计和分析具有重要意义。

实际应用

举例说明非门在数字电路中的应用, 如反相器、振荡器等。

03

复合逻辑门电路

与非门(NAND Gate)

逻辑符号与真值表

描述与非门的逻辑符号,列出其 对应的真值表,解释不同输入下

或非门(NOR Gate)

逻辑符号与真值表

描述或非门的逻辑符号,列出其对应的真值表, 解释不同输入下的输出结果。

逻辑表达式

给出或非门的逻辑表达式,解释其含义和运算规 则。

逻辑功能

阐述或非门实现逻辑或操作后再进行逻辑非的功 能,举例说明其在电路中的应用。

异或门(XOR Gate)

逻辑符号与真值表

01

02

03

Байду номын сангаас

04

1. 根据实验要求搭建逻辑门 电路实验板,并连接好电源和

地。

2. 使用示波器或逻辑分析仪 对输入信号进行测试,记录输

入信号的波形和参数。

3. 将输入信号接入逻辑门电 路的输入端,观察并记录输出

信号的波形和参数。

4. 改变输入信号的参数(如频 率、幅度等),重复步骤3, 观察并记录输出信号的变化情

THANKS

感谢观看

低功耗设计有助于提高电路效率和延长设 备使用寿命,而良好的噪声容限则可以提 高电路的抗干扰能力和稳定性。

扇入扇出系数

扇入系数

指门电路允许同时输入的最多 信号数。

扇出系数

指一个门电路的输出端最多可 以驱动的同类型门电路的输入 端数目。

影响因素

门电路的输入/输出电阻、驱动 能力等。

重要性

扇入扇出系数反映了门电路的驱动 能力和带负载能力,对于复杂数字 系统的设计和分析具有重要意义。

实际应用

举例说明非门在数字电路中的应用, 如反相器、振荡器等。

03

复合逻辑门电路

与非门(NAND Gate)

逻辑符号与真值表

描述与非门的逻辑符号,列出其 对应的真值表,解释不同输入下

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3、输出级形式(二)

达林顿结构; 输出电阻减小,速度增快; 静态功耗增加。

(二) 几种典型的TTL集成门电路 一、 TTL反相器

A

A

A

A

二、 TTL集成与非门

悬空?

AB

AB AB

AB

三、 其它逻辑功能的TTL门电路

1、几种复合门电路

或非门

A+B A

A+B

B

A+B

AB+CD AB

AB+CD CD

二、四输入ECL或/或非门电路介绍:

-1.3V

图2.4.12 ECL或/或非门的电路及逻辑符号

三、ECL门电路的主要特点:

优点: 1)由于三极管导通时为非饱和状态,电路中电阻取值较小,

逻辑电平摆幅小(0.8V),所以其工作速度是各种集成门电路中最高 的一种。

2)或/或非互补输出,使用方便、灵活。 3)输出采用射随器,所以输出阻抗低、带负载能力强。 4)由于在开关工作状态下的电源电流基本不变,所以电 路内部的开关噪声很低。

图2.1.2 获得高、低电平的基本原理

§2.2 半导体器件的开关特性

一、半导体二极管的开关特性:

二、半导体三极管的开关特性: 1、三极管的特点:

模电和数电 的区别?

图2.2.2 双极型三极管的输出特性曲线

2、三极管开关电路分析:

图2.2.3 双极型三极管的动态开关特性

三、MOS管的开关特性: 1、MOS管的结构:

逻辑门电路

Chapter 2 Logic Gate Circuit

本章主要内容

第一节 概述 第二节 半导体器件的开关特性 第三节 分立元件门电路 第四节 双极型集成门电路 第五节 MOS型门电路 第六节 使用数字集成电路的注意事项

缺陷?

VCC

输 入 VI 信 号

S1

输

VO

出 信

号

S2

(a)

(b)

• 集成电路的优点:体积小、重量轻、可靠性高、 寿命长、功耗小、成本低、工作速度高。

• 通常把一个封装内含有等效逻辑门的个数或元 器件的个数定义为集成度。

图2.4.1 集成电路图例

• 数字集成电路按集成度分可分为:

小规模(SSI:Small Scale Integration): 1~10门/片或10~100个元件/片

图2.2.4 MOS管的结构和符号

2、MOS管的输入特性和输出特性: 可变电 阻区

恒流区

截止区

图2.2.5 MOS管共源接法和输出特性曲线 (a)共源接法 (b)输出特性曲线

3、MOS管的基本开关电路:

图2.2.6 MOS管的基本开关电路

4、MOS管的四种类型(列表):

§2.3 分立元件门电路

与或非门

AB+CD

AB A+B

异或门 A⊕B

2、集电极开路(OC)与非门

图2.4.6 推拉式输出级并联的情况

图2.4.7 OC门输出并联的接法和逻辑图

3、三态输出门

使T4也截止,输出 呈高阻态

使T4也截止,输出 呈高阻态

图2.4.8 三态与非门的电路结构和逻辑符号

(a)高电平有效三态门(b)低电平有效三态门

一、二极管与门

二、二极管或门

三、三极管非门(反相器)

VB

四、其它电路

图2.3.4 与非门电路

图2.3.5 或非门电路

思考:如何用分立元件画出与或非门、异或门和同或门 的电路图?

§2.4 双极型集成门电路

§2.4.1 集成电路概述

• 目前,数字电路中,集成电路已几乎取代了分立元 件电路。

• 所谓集成电路,即把电路中的半导体器件、电阻、 电容及连线等制作在一个半导体基片上,构成一个 完整的电路,并封装在一个管壳内。

中规模(MSI:Medium Scale Integration): 10~100门/片或100~1000个元件/片

大规模(LSI: Large Scale Integration): >100门/片或>1000个元件/片

超大规模(VLSI:Very Large Scale Integration): >10万个元件/片

缺点:1)抗干扰能力差( V0.6V); 2)开关速度较慢(饱和型电路, tp d:20~30ns)。

目前,IIL电路主要用于制作大规模集成电路的内部逻辑电路。

§2.5 MOS型门电路 §2.5.1 CMOS门电路

CMOS电路具有低功耗、抗干扰能力强等特点,但其工

缺点: 1)噪声容限低。

2)电路功耗大。 3)输出电平的稳定性较差。

目前,ECL电路的产品只有中、小规模的集成电路,主要用在 高速、超高速的数字系统和设备当中。

§2.4.4 IIL门电路

一、I 2L(Integrated Injection Logic)电路简介: I L2 电路的基本单元是由一只NPN多集电极三极管构成的反

相器,反相器的偏流由另一只PNP三极管提供。

图2.4.13 IIL电路的基本逻辑单元

二、I 2L电路的主要特点:

优点:1)电路结构简单,这样节省了硅片面积又降低了功耗;

2)各逻辑单元之间无需隔离,这样简化了工艺,省了片上的隔 离槽,使集成度大大提高;

3)IIL电路能够在低电压、微电流下工作。 正因为此,IIL是目前双极型电路中功耗最低的一种,且其集成 度可相当大。另外,IIL还可以与TTL电平相兼容,工艺也兼容。

• 数字集成电路按 输出结构分可分为:

• 数字集成电路按制造工艺不同可分为:

双极型: * TTL——常用之一,速度较快,功率较大; * HTL——抗干扰强,速度低; * ECL——速度快,功耗大; * IIL ——集成度很大,功耗最低,抗干扰差, 速度低;

MOS型:* CMOS——常用之一,低功耗,抗干扰能力强; * NMOS * PMOS

Bi-CMOS型:功率小,输出阻抗小。

§2.4.2 TTL集成门电路

(一) TTL集成门电路的结构

图2.4.2 TTL集成门电路结构图

1、输入级形式(一)

1、输入级形式(二)

2、中间级 形式

3、输出级形式(一)

输出电平可变; 驱动能力增强; 可“线与”。

输出电阻很低; 输出高低电平固定; 驱动能力较弱。

图2.4.9 用三态输出门接 成总线结构

图2.4.10 用三态输出门实 现数据的双向传输

§2.4.3 ECL门电路

一、ECL(Emitter Coupled Logic)门电路的基本单元:

VIH 0.8V VIL 1.6V

T1、T3均工作在非 饱和状态

图2.4.11Hale Waihona Puke ECL门电路的基本单元(差动放大器)