高密度封装基板设计技术介绍

高密度高可靠电子封装关键技术及成套工艺

高密度高可靠电子封装关键技术及成套工艺

高密度高可靠电子封装技术及成套工艺是电子封装行业的发展重要内容之一,

也是实现电子产品小型化、高密集度和高可靠性等目标的重要支撑技术。

高密度高可靠电子封装技术和成套工艺综合利用了精密机加工、计算機设计、

数码技术、微机控制、光学技术、焊接等技术,满足了电子产品的复杂封装需求。

在高密度高可靠电子封装技术和成套工艺密切结合的基础上,研究工程师不断优化了电子封装的制程工艺、分析实验开发,以及封装设计结构、较少的连接点等技术改进。

首先,研究工程师采用了最新的精密机械加工技术,强化了电子封装精度,优

化了封装物料的精度,使封装物料更加精密,特别是对复杂的多层封装,精密机械加工技术的应用使电子封装物料的精度大大提高,有效的改善以往的封装质量缺陷。

其次,结合CAD/CAM系统,研究工程师可以快速准确地提取机要封装原件的可拆件图,将最新的封装设计方案设计计算机,采用Ipads/CAM系统实现封装技术,实现封装质量自动检测,使电子封装产品具有较高的可靠性。

此外研究工程师还着重改进电子封装物料上采用新型精密切削技术提高电子封

装产品的可靠性,同时通过良好的焊接技术,增强了元器件的可靠性,使电子封装技术的可靠性进一步提高。

这些先进的高密度高可靠电子封装技术及成套工艺,为电子封装行业的发展提

供了强有力的技术支撑,改善了电子封装物料的可靠性和可靠性,使电子产品实现小型化、高密集度和高可靠性等目标。

面向fc-bga的增层胶膜封装基板镀铜工艺

面向FC-BGA的增层胶膜封装基板镀铜工艺在电子产品的制造过程中,封装基板是至关重要的一环。

封装基板不仅可以保护电子元器件,还可以实现电路连接和信号传输。

而面向FC-BGA(Fine-pitch Ball Grid Array)的增层胶膜封装基板镀铜工艺,更是在高密度、高性能电子产品中得到广泛应用。

本文将从工艺流程、关键技术及优势等方面对这一工艺进行深入探讨。

一、工艺流程1. 回流焊:在封装基板制作的初始阶段,需要进行回流焊工艺,即将预先涂布在基板上的焊膏通过热加热到一定温度,形成均匀的焊点,以保证后续的焊接工艺。

2. 钻孔与防蚀工艺:在回流焊完成后,需要进行钻孔工艺,将基板表面的焊盘连接到下层连接电路。

然后进行防蚀工艺,即在基板的金属层上镀一层保护膜,以防止铜层暴露在空气中而氧化。

3. 绝缘子与导体形成工艺:之后是绝缘子与导体形成工艺,通过光刻技术,在基板表面形成导体线路,并在导体线路上覆盖绝缘层,以隔离导体线路。

4. 镀铜工艺:最关键的工艺环节之一,镀铜工艺需要将基板表面的连接电路和孔壁进行镀铜,以保证良好的导电性和连接性。

5. 热压工艺:最后一个工艺环节是热压工艺,即将已经完成镀铜的基板与电子元器件进行压合,形成最终的封装基板。

二、关键技术1. 镀铜层厚度控制:在增层胶膜封装基板镀铜工艺中,镀铜层的厚度控制是十分关键的。

太薄的镀铜层会导致连接电路的导通性差,太厚则会增加制造成本。

精确控制镀铜层的厚度是提升工艺质量的关键。

2. 镀铜均匀性:镀铜层的均匀性直接影响到连接电路的性能。

如果镀铜层的厚薄不均匀,将会造成连接电路的电阻不一致,影响整体性能。

如何保证镀铜层的均匀性也是关键技术之一。

3. 成本控制:增层胶膜封装基板镀铜工艺需要耗费大量的材料和能源。

如何在保证质量的前提下降低生产成本,也是制约技术发展的一个重要因素。

三、优势1. 高密度:增层胶膜封装基板镀铜工艺可以实现更高密度的连接电路,适用于高性能电子产品的制造。

封装基板技术的发展

封装基板技术的发展封装基板技术是电子元器件制造的关键环节之一,它旨在将电子元器件连接到电路板上,并提供物理支撑和电气连接。

随着电子产品的不断发展和智能化需求的增加,封装基板技术也在不断发展。

以下是封装基板技术的发展所经历的几个重要阶段:1.初期阶段(1960年代-1980年代)封装基板技术起源于20世纪60年代,这个阶段主要采用双面贴片和通孔技术。

双面贴片技术通过在电路板的两面安装元器件,并进行焊接连接来实现电气连接。

通孔技术则是通过铜箔覆盖的孔洞,在两个电路层之间传导信号。

这个时期,封装基板技术主要使用单层板或双层板,功能也相对简单,并且生产周期较长。

2.高密度阶段(1990年代)进入20世纪80年代,随着电子器件越来越小型化,封装基板技术也逐渐发展为多层板和高密度连接技术。

多层板技术允许多个电路层叠放在一起,通过通过通孔或盲孔进行连接。

高密度连接技术则用于增加连接器端子的数目,提高连接器的密度。

这一阶段的封装基板技术大幅提高了电子器件的集成度和性能。

3.超高密度阶段(2000年代)进入21世纪,随着电子产品对小型、高性能、高可靠性的要求日益严格,封装基板技术发展到了超高密度阶段。

这一阶段的关键技术是微细线路、微细通孔和微阵列连接器等。

微细线路技术通过减小线路宽度和间距来实现更高的线路密度。

微细通孔技术则通过缩小通孔径向直径,增加通孔数量来提高连接密度。

微阵列连接器技术则可以实现大量信号和功率的高速连接。

这些技术的应用大大推动了封装基板技术的进一步发展。

4.3D封装阶段(2024年代至今)近年来,随着电子产品对体积更小、性能更强的需求增加,封装基板技术也逐渐发展到3D封装阶段。

3D封装技术通过垂直堆叠多个芯片,提高器件的集成度,并通过封装互连技术实现芯片和封装基板之间更高密度的互连。

目前的主要的3D封装技术有通过硅通孔封装(TSV)和硅基互连(SIP)两种。

这些技术将推动封装基板技术向更高集成度和更高性能的方向发展。

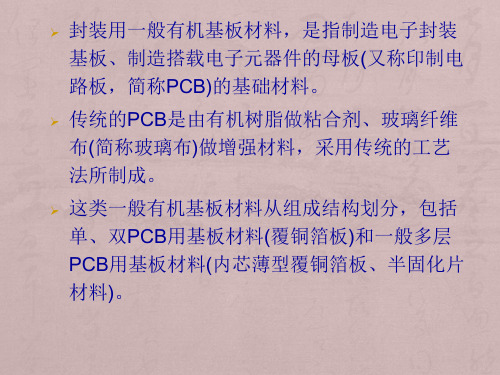

第三讲---封装有机基板简介

➢ 这类一般有机基板材料从组成结构划分,包括 单、双PCB用基板材料(覆铜箔板)和一般多层 PCB用基板材料(内芯薄型覆铜箔板、半固化片 材料)。

有机封装基板用基材,在整个封装印制电路板上, 主要担负着导电、绝缘和支撑三大方面的功能。 ➢导电----主要是以基板材料所含有的铜箔来实现; ➢绝缘----主要是由所含的有机树脂来实现; ➢支撑----由所含的树脂、补强材料或填充料来实现。 封装及其基板(印制电路板)的性能、可靠性、制造中 的加工性、制造成本、制造水平以及新技术在封装 中的实现等,在很大程度上,取决于基板材料。

4、具有低介电常数特性

有机封装基板用基材,一般具有较低的介电常数(εr), 与陶瓷基材相比,更适用于高频信号的传输,因此更适应 电路信号高速化的发展趋势。尽管如此,随着高速电路封 装技术的发展,以及封装体内信号传输速度的提高,对降 低有机封装基板用基材的介电常数,提出更高的要求。

OMPAC型塑料封装的发展

图 (c)所示结构的封装(薄型PKG),更强调要求在微组装时的工艺性良 好。如基板材料要具有较高的高温弹性模量,薄型化绝缘基材,在它 的耐湿性,保证导通孔可靠性方面,对基板材料也有更严的要求。

三、有机封装基板用基板材料的分类

从总体上按状态划分为刚性与挠性两大类。 ➢ 刚性基材又分为含有纤维增强的一般型PCB用基材、积 层多层板用基材、复合化多层板用基材。 ➢ 挠性基材主要作为带载型封装用有机基材。它主要有薄 膜类(聚酞亚胺树脂薄膜、其他特殊性树脂薄膜)和玻璃布/ 环氧树脂卷状薄型覆铜板等。

不同类型封装对基板材料性能需求的侧重点

图 ( a)所示结构的封装(OMPAC型PKG):基材在高温条件下的硬度保 持不下降,以保证高的金属丝焊接的可靠性。同时要求高温下弹性模 量高。这样在再流焊时,基板的翘曲度会小。

MIP封装工艺

MIP封装工艺

MIP封装工艺是一种高效、可靠的集成电路封装技术。

它采用了先进的微影技术,能够在一个芯片上集成多个功能模块,从而实现芯片的高度集成和多功能化。

MIP封装工艺的主要特点包括:高密度、高可靠性、高集成度、低成本、高性能等。

其中,高密度是指MIP封装工艺可以在一个芯片上集成大量的功能模块,从而实现芯片的高度集成;高可靠性是指MIP封装工艺的焊点可靠性非常高,能够保证芯片在长期使用过程中不会出现失效问题;高集成度是指MIP封装工艺可以将多个芯片的功能集成在一个芯片上,从而实现芯片的多功能化;低成本是指MIP封装工艺比传统封装工艺更加节省成本;高性能是指MIP封装工艺可以实现高速传输、高带宽、低功耗等优秀的性能表现。

在MIP封装工艺中,最关键的是微影工艺。

通过微影工艺,可以将多个功能模块集成在一个芯片上,并且实现高密度的焊点布局。

同时,MIP封装工艺还采用了金属化技术和电子束焊接技术等先进技术,实现了焊点的高可靠性和高精度。

此外,MIP封装工艺还可以实现多层封装,从而进一步提高芯片的集成度和可靠性。

总之,MIP封装工艺是一种先进、高效、可靠的封装技术。

在集成电路领域,MIP封装工艺正在得到越来越广泛的应用。

- 1 -。

高密度互连积层板研发制造方案(二)

高密度互连积层板研发制造方案一、实施背景随着科技的飞速发展,电子设备正朝着更轻、更薄、更高效的方向发展。

高密度互连积层板(HDI)作为PCB(Printed Circuit Board,印刷电路板)的一种,因其高集成度、高可靠性、低重量等优点,已成为航空航天、医疗设备、智能手机、汽车电子等领域的关键组件。

当前,HDI市场主要由日本、韩国和中国台湾等少数企业主导,国内企业在高端市场上的竞争力较弱。

因此,开展高密度互连积层板的研发制造,对于提升国内企业在该领域的竞争力,具有重要意义。

二、工作原理HDI是一种多层板,其制造过程主要包括以下几个步骤:1.基材制备:采用高导热、低膨胀系数、高耐腐蚀性的材料作为基材。

2.线路制作:在基材上采用激光切割或化学腐蚀等方式制作线路。

3.绝缘层制作:在制作好的线路层之间添加绝缘材料。

4.孔金属化:通过电镀或化学镀的方式在需要的孔内形成金属化层。

5.焊接:通过焊接将各层线路连接起来。

其中,孔金属化是HDI制造的关键技术之一。

由于孔径小、孔深,且需满足不同导电层之间的连接,因此对孔金属化的制备工艺和技术要求极高。

三、实施计划步骤1.技术研究:开展HDI制造关键技术的研发,包括孔金属化技术、多层板制作技术等。

2.设备选型与采购:根据技术研发需要,采购相应的制造设备和检测设备。

3.工艺流程设计:根据HDI的制造特点,设计合理的工艺流程。

4.中试生产:在实验室条件下进行小批量生产,验证工艺流程的可行性。

5.批量生产:根据中试结果,调整工艺参数,进行批量生产。

6.产品检测与认证:对生产的产品进行性能检测和认证。

7.市场推广:将产品推向市场,与需求方建立合作关系。

四、适用范围HDI适用于以下领域:1.航空航天:HDI的高可靠性、低重量特性使其成为航空航天领域的首选组件。

2.医疗设备:HDI的精密线路制作能力使其成为医疗设备的重要组件。

3.智能手机:HDI的高集成度使其成为智能手机主板的首选材料。

高密度封装覆铜板的阻抗控制方法及应用

高密度封装覆铜板的阻抗控制方法及应用随着电子元件的不断发展和封装技术的不断提升,高密度封装覆铜板作为一种常见的电路板材料,广泛应用于各类电子产品中。

在高密度封装覆铜板制造过程中,阻抗控制是一个十分关键的环节,它对于保证电路板稳定性和性能的提升至关重要。

本文将介绍高密度封装覆铜板的阻抗控制方法以及其在电子产品中的应用。

高密度封装覆铜板的阻抗控制方法主要包括以下几个方面:材料选择、层间距离、板厚、板质以及线宽和环境温度等。

首先,材料选择是影响阻抗控制的关键因素之一。

在选择覆铜板材料时,应考虑其介电常数和损耗因子等参数,以确保所选材料在特定频率范围内能够提供所需的阻抗值。

常见的覆铜板材料包括FR-4、Rogers、PTFE等,它们各自具有不同的介电常数和损耗因子,可以根据具体要求进行选择。

其次,层间距离也对阻抗控制起着重要作用。

层间距离是指在多层电路板中,相邻两层的距离。

较大的层间距离可以降低电磁干扰的可能性,进而提高阻抗的稳定性。

因此,在设计高密度封装覆铜板时,应合理选择层间距离,避免不必要的电磁相互作用。

此外,板厚和板质也对阻抗控制产生影响。

较薄的覆铜板厚度能够提高信号的传输速度,但可能导致阻抗变化较大。

因此,在选择板厚时,需要综合考虑阻抗和机械强度之间的平衡。

同样,不同的板质也会对阻抗产生不同的影响。

高精度的阻抗控制通常会选择具有较高玻璃转移温度(Tg)的板材,以确保在高温环境下仍能保持良好的阻抗稳定性。

最后,线宽和环境温度也需要考虑在阻抗控制的过程中。

较细的线宽可以提高电路的集成度,但也会引入更多的阻抗变化。

因此,在设计线宽时,需要根据具体需求和制造工艺的限制进行合理选择。

另外,环境温度对高密度封装覆铜板的阻抗控制同样具有重要影响,温度的变化可能导致介质的性能变化,从而引起阻抗的波动。

高密度封装覆铜板在各类电子产品中具有广泛的应用。

例如,它被广泛用于通信设备、计算机、医疗仪器、高速电子线路等领域。

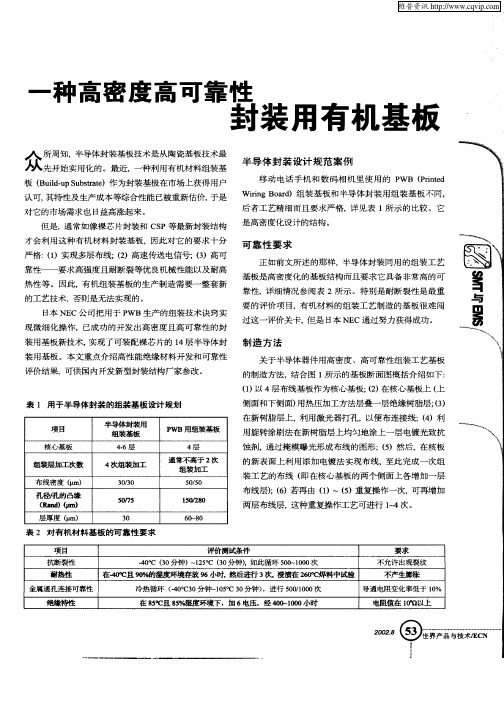

一种高密度高可靠性封装用有机基板

在研究树脂设计的基础上, 对有关 的 4种树脂进行

当选定评价 时也采用 以下方法进 行综 日本 N C公司通过返复改进 P E WB生产中行之有效 选定评价 。然而 ,

的激光加工 敷有铜箔 的树脂 R C ( ei C a dC p e) C R s ot o pr n e 工艺方法, 终于成功地开发出具有高可靠性的基板材料 。 在改进该工艺 的过程 中, 通过 采用热应 力模拟方法, 图 试 缩短研究与开发周期 。

4次绸 咖 工

3/ 00 3

通 常不 高于 2次 组 装加工

5 /0 05

孔 径 吼 的 凸缘

( 皿)

n s

3 0

l02o 5,8

6~ 0 O 8

层厚 度 ( ) o e r

表 2 对有机材料基板的可 靠性 要求

维普资讯

维普资讯

一

种密高靠 装 有 基 高度可簧 用 机 板

所周知, 半导体封装基板技术是从陶瓷基板技术最

入 先开始实用化的 。最近, 一种利用有机材料组装基

板 ( ul.p u s a )作为封装基极在市场上获得用户 B i u bt t d S re

中以下各点的研究与开发: 1 高强 度特性——基板材料在机械性能上, . 应具备强

韧性 ,例如 ,在温度循环实验 10 00次以上时,仍不出现 端 头处阻止继续漫延扩 展, 其应 力通过 无机填 料作用分

裂纹 : . 2 可靠 隆— 高热环境下表现 出高耐热 『 , 生 能 保 散 开来 。当选择无机填料时, 需要细 心考虑 , 诸如无机 持金属连接通 口的可靠I,阻抗可控耕 陛和绝缘材料不劣 生

质, 也可使它高 T 点化; g 但是, 树脂 固化后变成很 瞻、易 碎。有热可塑 幽 对 旨 月 配合, 不仅是寻求高 T g点而且提高

fowlp概念

fowlp概念FOWLP(Fan-Out Wafer-Level Packaging)•概念:FOWLP(Fan-Out Wafer-Level Packaging)是一种新型的封装技术,它通过将IC芯片、封装基板和封装材料进行三维堆叠,实现半导体器件的封装和互联。

FOWLP的主要特点是具备高密度、低成本、小尺寸和高性能等优势,被广泛应用于智能手机、芯片封装和其他高端电子设备中。

FOWLP的特点•高密度:FOWLP采用面积小、特殊设计的封装基板,可以实现芯片的高度集成和高密度连接,大大提升了器件的集成度。

•低成本:FOWLP采用了高度集成的工艺,减少了额外的封装材料和成本,相比传统封装技术具有较低的成本优势。

•小尺寸:FOWLP的封装基板可以进行芯片的堆叠和紧凑布局,使得整体封装尺寸更小,适用于轻薄、小型化的电子设备。

•高性能:FOWLP的封装方式可以提供更短的互联长度和更小的电阻、电感,从而提高信号传输速度和性能。

FOWLP的应用1.智能手机芯片封装:FOWLP在智能手机中得到广泛应用,可以实现高集成度的封装和多芯片堆叠,提升手机性能和功能。

2.高端电子设备:FOWLP适用于各种高端电子设备的封装,如平板电脑、可穿戴设备等,可以降低设备尺寸和重量,提高功耗和性能。

3.大数据中心:FOWLP可以用于大数据中心服务器的高密度封装,提供更高的计算能力和数据传输速度。

FOWLP的未来发展•随着半导体封装技术的不断发展,FOWLP作为一种创新的封装方式,将在未来继续得到广泛应用和发展。

•未来FOWLP将更加注重高集成度、低功耗和高性能的需求,进一步提升封装密度和互联性能。

•同时,FOWLP还将面临一些挑战,如封装工艺的复杂性、可靠性和成本控制等,需要不断的技术创新和改进。

以上就是FOWLP的概念及相关内容的简述,希望能对您有所帮助。

BGA封装技术介绍

CCGA技术特点

CCGA承受封装体和PCB基板材料之间热失配应 力的能力较好,因此其可靠性要优于CBGA器件,特 别是大器件尺寸应用领域,此外清洗也较容易。

CCGA焊料柱直径约0.508mm,高度约1.8mm, 间距约1.27mm,由于焊柱高度太大,目前应用的 较少。

TBGA技术

载带球栅阵列(TBGA)又称阵列载带自动键合,是 一种相对较新颖的BGA封装形式,采用的基板类型为PI 多层布线基板,焊料球材料为高熔点焊料合金,焊接时 采用低熔点焊料合金。

塑料封装BGA采用塑料材料和塑封工艺制作,是最常

用的BGA封装形式。

PBGA采用的基板类型为PCB基板材料(BT树脂/玻 璃层压板),裸芯片经过粘结和WB技术连接到基板顶 部及引脚框架后采用注塑成型(环氧模塑混合物)方法 实现整体塑模。

焊球材料为低熔点共晶焊料合金63Sn37Pb,直径约1mm ,间距范围1.27-2.54mm,焊球与封装体底部的连接不需要 另外使用焊料。组装时焊球熔融,与PCB表面焊盘接合在一 起,呈现桶状。

基板。HITCE-high thermal coefficient of expansion

②封装工艺流程

圆片凸点的制备→圆片切割→芯片倒装及回流焊→ 底部填充→导热脂、密封焊料的分配→封盖→装配 焊料球→回流焊→打标→分离→最终检查→测试→ 包装

• 倒装焊接

特点:倒装焊技术克服了引线键合焊盘中心距极限的问题; 在芯片的电源/地线分布设计上提供了更多的便利; 为高频率、大功率器件提供更完善的信号。

真空吸盘

真空吸球

滴助焊剂

放球

N2气中回流

助焊剂滴涂和置球机 氮气再流焊炉 助焊剂清洗、分离、打标机

BGA植球工艺流程

mip和cob封装工艺

MIP和COB封装工艺1. 简介MIP(Molded Interconnect Package)和COB(Chip-on-board)是两种常见的封装工艺,用于集成电路的封装和连接。

它们在电子产品制造中起到关键作用,能够提高产品的性能和可靠性。

本文将详细介绍MIP和COB封装工艺的原理、特点、应用以及制造过程。

2. MIP封装工艺2.1 原理MIP封装工艺是一种将集成电路芯片和封装基板结合在一起的封装技术。

其原理是通过将芯片和基板分别制造,然后将芯片嵌入基板中,最后通过热压等工艺将芯片与基板连接在一起。

MIP封装工艺可以实现高密度封装和多功能集成,具有良好的电气性能和可靠性。

2.2 特点•高集成度:MIP封装工艺可以实现芯片和基板的紧密结合,从而实现高集成度的电路设计。

•尺寸小:MIP封装工艺可以实现小型化设计,适用于微型电子产品的制造。

•低功耗:MIP封装工艺采用多层结构,可以减少电路的功耗。

•高可靠性:MIP封装工艺可以减少引脚数量和连接点,从而提高了电路的可靠性。

2.3 应用MIP封装工艺广泛应用于手机、平板电脑、智能穿戴设备等消费电子产品中。

由于其尺寸小、功耗低、可靠性高的特点,MIP封装工艺能够满足现代电子产品对于高性能和高可靠性的要求。

3. COB封装工艺3.1 原理COB封装工艺是一种将芯片直接粘贴在基板上的封装技术。

其原理是将芯片裸露的金属焊盘与基板上的金属焊盘通过焊接连接在一起,然后用环氧树脂等材料进行封装。

COB封装工艺可以实现高密度封装和高可靠性连接。

3.2 特点•高密度封装:COB封装工艺可以实现芯片与基板的直接连接,从而实现高密度封装。

•高可靠性:COB封装工艺采用焊接连接,可以提高电路的可靠性。

•良好的散热性能:COB封装工艺将芯片直接粘贴在基板上,可以提高散热性能,减少芯片温度。

3.3 应用COB封装工艺广泛应用于LED灯、汽车电子、医疗器械等领域。

由于其高密度封装、高可靠性和良好的散热性能,COB封装工艺能够满足这些领域对于高性能和高可靠性的要求。

bga基板全制程简介

检测误差的原因主要包括检测设备的精度问题、检测方法的 不当、检测人员的技能水平不足等。为了解决检测误差问题 ,可以采取多种措施,如提高检测设备的精度、优化检测方 法、进行检测人员的技能培训等。

05 bga基板全制程发展趋势与挑战

制程技术进步趋势

01 02

精细化制造

随着电子产品向更小、更轻薄方向发展,BGA基板的焊球间距不断缩小 ,对制程技术的要求也越来越高。为了实现更精细的制造,需要采用更 高精度的模具和更严格的制程控制。

对基板表面进行研磨、抛光等 处理,以提高焊接性能和电气 性能。

芯片贴装

芯片选择

根据产品要求选择合适的 芯片,确保功能和性能符 合要求。

芯片贴装设计

依据基板结构和芯片尺寸 ,进行芯片贴装设计,制 定合理的布局和间距。

芯片贴装工艺

将芯片按照设计要求贴装 到基板上,采用适当的粘 结剂和焊接技术。

焊接

焊接材料选择

其他辅助材料

如焊锡、胶水、标记材料 等。

基板制造

制作模具

根据设计图纸制作模具,用于 后续基板制作。

纤维编织

将混合好的材料放入模具中, 进行纤维编织,形成基板的框 架结构。

设计和制图

依据产品要求进行基板设计, 并制作成工程图纸。

配料与搅拌

将树脂、玻璃纤维等材料按照 一定比例混合,并搅拌均匀。

表面处理

汽车电子领域

由于BGA基板具有高可靠性和耐高 温性能,因此在汽车电子领域也有 广泛应用,如发动机控制芯片、安 全气囊控制芯片等。

02 bga基板全制程工艺流程

原材料采购

01

02

03

基板材料

包括树脂、玻璃纤维、铜 箔等,需根据产品要求选 择合适的材料。

plcc封装基板的制造工艺流程

plcc封装基板的制造工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!PLCC封装基板的制造工艺流程详解PLCC,全称为塑料-leaded chip carrier,即塑封有引脚的芯片载体,是集成电路封装技术中常见的一种。

ic封装基板工艺

ic封装基板工艺IC封装基板工艺是一种将集成电路封装在基板上的技术,它在电子产品制造中起到了至关重要的作用。

本文将从工艺流程、封装类型和制造要求等方面,对IC封装基板工艺进行详细介绍。

一、工艺流程IC封装基板工艺的流程一般包括以下几个环节:设计、制造、组装和测试。

首先,设计人员根据产品的需求和规格要求进行IC封装设计,确定封装类型、引脚布局和线路连接等。

然后,制造工艺师根据设计要求选择合适的材料,并采用PCB制造技术进行基板的制造,包括电镀、切割、钻孔等工艺步骤。

接下来,组装工艺师将已封装好的IC芯片焊接在基板上,并进行线路连接和封装密封等工作。

最后,进行测试验证,确保封装的IC基板符合产品的功能和性能要求。

二、封装类型IC封装基板的封装类型多种多样,常见的有DIP、SOP、QFP、BGA等。

DIP(Dual In-line Package)是最早的封装类型,引脚呈直线排列,适合手工焊接。

SOP(Small Outline Package)是一种小型封装,适用于高密度集成电路。

QFP(Quad Flat Package)是一种方形封装,引脚呈四边形排列,适用于高速信号传输。

BGA (Ball Grid Array)是一种球阵列封装,引脚以球形排列在底部,具有良好的散热性能和电性能。

三、制造要求IC封装基板的制造要求非常严格,主要包括以下几个方面:材料选用、尺寸控制、焊接工艺和封装密封。

首先,材料的选用要符合产品的性能要求,如基板材料要具有良好的导电性和绝缘性。

其次,尺寸的控制要精确,保证基板的尺寸和引脚的间距符合设计要求。

焊接工艺对于封装质量至关重要,要保证焊接的牢固性和可靠性。

最后,封装密封要做好,以保护IC芯片不受外界环境的影响。

IC封装基板工艺的发展与电子产品的需求密切相关。

随着电子产品的不断更新换代,对IC封装基板的要求也越来越高。

目前,一些先进的封装技术如CSP(Chip Scale Package)和WLP(Wafer Level Package)已经逐渐应用到IC封装基板制造中,以实现更小型化、更高性能和更低功耗的产品。

封装基板技术

封装基板是一种用于承载芯片的线路板,属于PCB的一个技术分支,也是核心的半导体封测材料。

它具有高密度、高精度、高性能、小型化及轻薄化的特点,可为芯片提供支撑、散热和保护的作用,同时也可为芯片与PCB母板之间提供电气连接及物理支撑。

封装基板的产品工艺不断地随着封装形式演进,而且在高阶封装领域替代原有的引线框架、环氧模塑料、键合金丝等传统材料。

随着电子产品向更小、更轻、更短、更薄的方向发展,封装基板技术也持续进行技术迭代,向着更细、更小的线宽/线距发展,提升封装基板的附加值。

封装基板技术的进步是推动IC封装基板领域增长的关键动力。

以上信息仅供参考,如有需要,建议您查阅专业书籍或咨询专业人士。

IC封装基板技术简介

IC封装基板技术简介IC封装基板技术随着电子产品微小型化、多功能化和信号传输高频高速数字化,要求PCB迅速走向高密度化、高性能化和高可靠性发展。

为了适应这个要求,不仅PCB迅速走向HDIBUM板、嵌入(集成)元件PCB等,而且IC封装基板已经迅速由无机基板(陶瓷基板)走向有机基板(PCB板)。

有机IC封装基板是在HDI/BUM板的基础上继续‘深化(高密度化)’而发展起来的,或者说IC封装基板是具更高密度化的HDI/BUM板。

1 封装基板的提出及其类型1.1 有机封装基板的提出封装基板是用于把多个一级(可用二级)封装IC组件再封(组)装形成更大密度与容量的一种基板。

由于这类基板的封装密度很高,因此,其尺寸都不大,大多数为≤50*70mm2。

过去主要是采用陶瓷基板,现在迅速走向高密度PCB封装基板。

(1)陶瓷封装基板。

陶瓷封装基板的应用已有几十年的历史了,基优点是CTE较小,导热率较高。

但是,随着高密度化、特别是信号传输高频高速数字化的发展,陶瓷封装基板遇到了严厉的挑战。

①介电常数εr大(6∽8)。

信号传输速度V是由来介电常数εr决定的,如下式可得知。

V=k·C/(εr)1/2其中:k——为常数;C——光速。

这就是说,采用较小的介电常数εr,就可以得到较高的信号传输速度。

还有特性阻抗值等问题。

②密度低。

L/S≥O.1mm,加上厚度厚、孔径大,不能满足IC高集成度的要求。

③电阻大。

大多采用钼形成的导线,其电阻率(烧结后)比铜大三倍多或更大,发热量大和影响电气性能。

④基板尺寸不能大,影响密度和容量提高。

由于陶瓷基板的脆性大,不仅尺寸不能大,而且生产、组装和应用等都要格外小心。

⑤薄型化困难。

厚度较厚,大多数为1mm以上。

⑥成本高。

(2)有机(PCB)基板。

有机(PCB)基板,刚好与陶瓷封装基板相反。

①介电常数εr小(可选择性大,大多用3∽4的材料)。

②高密度化好。

L/S可达到20∽50μm,介质层薄,孔径小。

高密度集成电路设计与优化

高密度集成电路设计与优化在信息技术飞速发展的时代,高密度集成电路设计与优化发挥着极为重要的作用。

随着科技的不断进步,人们对电子产品的功能和性能需求也越来越高,这就对高密度集成电路设计与优化提出了更高的要求。

本文将从高密度集成电路设计的基本概念、优化方法和应用领域等方面进行阐述。

首先,高密度集成电路设计是指在有限的芯片面积内,将更多的功能集成在一块芯片上。

这是电子技术发展的必然趋势之一。

高密度集成电路设计的核心任务是在保证电路功能完整性的前提下,通过优化布局和布线,实现尽可能小的面积占用,并提高集成度。

其中,CAD软件在高密度集成电路设计中扮演着重要的角色,它能够自动化地生成、分析和优化电路布局与布线,大大提高了设计的效率和准确性。

其次,高密度集成电路设计优化的方法有很多种,常见的包括逻辑综合、布局优化和布线优化等。

逻辑综合是将逻辑电路描述转化为等价的、能够实现指定功能的综合电路的过程。

布局优化是在给定的芯片尺寸和资源限制下,通过优化电路元件的摆放位置,实现最小的面积占用和最短的信号传输路径。

布线优化是在逻辑综合和布局优化的基础上,通过合理的布线规划,减少信号延迟和功耗,提高电路的性能。

而对于复杂的高密度集成电路设计,还可以采用分层设计和逻辑重构等方法进行优化,从而进一步提高集成电路的可靠性和性能。

高密度集成电路设计与优化在多个领域都有广泛的应用。

首先,它在消费电子产品中发挥着重要作用。

如今,智能手机、平板电脑等便携式设备越来越流行,而这些设备通常需要在有限的空间内集成众多的功能模块。

高密度集成电路设计与优化使得这些设备在小巧的体积内实现了强大的功能,为用户带来更好的体验。

其次,高密度集成电路设计优化也在通信领域得到广泛应用。

高速通信和数据传输对电路速度和功耗有极高的要求,而高密度集成电路设计可以提高电路的速度和功耗效率,满足通信需求。

另外,在医疗、汽车和航空等领域,高密度集成电路的应用也越来越广泛,为这些领域的发展带来了巨大的推动力。

fbga封装流程

fbga封装流程FBGA封装流程FBGA(Fine Ball Grid Array)是一种常见的芯片封装技术,其具有高集成度、高密度、高可靠性等优点,被广泛应用于电子产品中。

本文将介绍FBGA封装的流程和步骤,以帮助读者更好地了解这一技术。

一、准备工作在进行FBGA封装之前,需要做一些准备工作。

首先,需要准备好FBGA芯片、封装基板和焊接设备。

其次,需要确定封装的芯片型号和规格,并根据其要求设计封装基板。

最后,需要检查焊接设备的状态,确保其正常运行。

二、PCB设计PCB(Printed Circuit Board)的设计是FBGA封装的重要环节。

在设计过程中,应根据芯片的布局和尺寸要求,合理布置芯片和引脚,并设置适当的焊盘和焊盘间距。

此外,还需要考虑电源分配、信号线路布线、地线规划等因素,以确保封装后的电路性能稳定。

三、焊盘制作焊盘是FBGA芯片与封装基板之间的连接介质,其制作需要经过一系列步骤。

首先,需要在封装基板上涂覆焊膏,以形成焊盘。

然后,使用精密的光刻技术,将焊盘的位置和形状进行精确定位和制作。

最后,经过烘烤等工艺,使焊盘达到适当的硬度和耐用性。

四、芯片安装在进行FBGA芯片安装之前,需要先检查芯片和封装基板的质量。

然后,将芯片轻轻放置在封装基板上,并确保芯片的正面与封装基板的焊盘对齐。

接下来,使用专用的热压设备,对芯片进行热压,以确保芯片与焊盘之间的良好连接。

五、焊接工艺焊接是FBGA封装的关键步骤之一。

在焊接过程中,需要控制好焊接温度、焊接时间和焊接压力。

一般情况下,使用热风或红外线等加热方式,将焊盘加热至足够温度,使焊膏熔化并与芯片引脚连接。

同时,通过适当的焊接压力,确保焊接质量和稳定性。

六、封装测试完成焊接后,需要对封装芯片进行测试。

测试内容包括外观检查、尺寸测量、焊接质量检验等。

外观检查主要是查看封装是否完整、焊盘是否正常,尺寸测量主要是检查封装尺寸是否符合要求,焊接质量检验主要是通过电子显微镜等设备,对焊盘进行显微观察,以确保焊盘的质量和焊接效果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

System level PCB level Package level Chip level

以互联为核心,从成熟业务PCB拓展到电子装联、封装基板两项新业务,形成公司 的三项业务,并不断提升各项业务的技术地位;以客户价值为核心,通过开展设计、封 装等服务打造高效快速的“产品+服务”的一站式商业新模式,为客户提供持续增值服 务,实现产业升级和转型

4

深南电路基板业务布局

5

主要内容

1 2 3

深南电路有限公司介绍 高密度封装基板设计与制造 系统级设计封装一站式业务

6

电子产品的发展背景

•计算/网络 •数字音频 •数码影像/DV •通信/无线 •GPS/卫星导航 •传感器

高密度、小型化、多功能集成

7

电子产品的发展背景

小型化 多功能化 高频高速传输

Motorola 3200

体积:334×67×43mm 功能:语音通话 传输频率:800MHZ 重量:520g

埋入式

EC EC&ER

被动器件埋入

主动器件埋入

Discrete Embedded

IC Embedded

倒装芯片

FCCSP(Array) FCCSP(Perimeter ) FC-POP Coreless

引线键合

MEMS

PBGA

CSP

Cavum Microphone Cavity Substrate

Camera Module

互连密度

PCB + Embedded thin film 2009

SUB + WB + SMT Embedded active PCB + SMT SUB + Embedded thin film SUB + WB Rigid-Flex

Embedded passives

2010

2012

2015

封装基板产品路线

40 nF/in2 22 0.010 3 μm 31 (x,y,z)

20

埋入式分立器件高密度封装基板

埋入分立器件的种类 种类

0402电容(普通) 0402电阻(普通) 0402电容(GRU153) 0402电容(GRU15Y) 0201电容(普通) 0201电阻(普通) 0201电容(GRU03Y)

Perimeter Discrete Embedded

1995

2000

2005

2010

2015

11

高密度封装基板应用领域

手机 GPU/BB/RF ……

台式/笔记本 CPU/GPU Chipset

微机电 MEMS 游戏机 CPU/GPU

消费类电子 驱动IC

封装基板

平板电脑 CPU/GPU Flash…… 逻辑器件 FPGA/PLD

29

系统级封装一站式服务模式

Order Wafer 流片时间 2 months Delivery

5-6 Weeks

SiP Design 1Week Substrate Manufacture 2-3 Weeks SMT Assembly 1 week

特殊服务: 小批量、快交付 支持MPW、Sample、LVM 支持BGA、LGA、QFN、FC

埋入式设计

Character

Capacitance /area Dielectric Constant (1 kHz) Dissipation Factor (1 kHz) Dielectric Thickness CTE (ppm/C) Dielectric loss @ 1GHz Resin system Dielectric Strength Copper Thickness

苹果iPhone5 S(土豪金)

体积:123.8×58.6×7.6mm 功能:视频电话,800万像素,Wi-Fi, 多媒 体,GPS,64位架构、多种感应器。。。 重量:112g

电子产品的小型化发展驱动要素

随着电子技术的飞速发展及电子产品朝着微型化,轻便化,多功能,高集成, 高可靠方向发展,半导体器件封装也向多引脚细间距化飞速发展,相应的搭载半 导体部件的封装基板也朝着小型轻量化和高密度的发展;驱动产品多功能集成化 和小型化发展的要素主要有:

Memory 记忆体

网络通讯

12

高密度封装基板市场状况

2012年全球有机封装基板市场规模约100.4亿美元,其中倒装芯片基板为54.07亿美元。预 计2015年,全球有机封装基板市场规模约112.04亿美元。 2011年全球前11大基板厂产值合计75.5亿美元,占比85%,集中度较高。

12000 10000 8000 6000 4000 2000 0 2007 2008 2009 2010 2011 2015

电极宽(L2&L3)

0.1min 0.15-0.3 0.15-0.3 0.23-0.33 0.13-0.23 0.15-0.25 0.115-0.185

普通电容侧面图

GRU15Y电容侧面图

21

埋入式分立器件工艺路线(1)

22

埋入式分立器件工艺路线(2)

23

系统集成---埋入式芯片介绍

HIDING DIES (High-density Integration of Dies into Electronics Substrates)

倒装芯片基板核心术技术图

封装基板生产技术能力

Board Tks. / Core/PP Trace Pitch Finger Pitch 2L,130/60 4L,230/60/30 L/S 35/35 90 180 75/175 100/230 SM Reg.±35 SM Flatness±7 2L,110/50 4L,210/50/30 L/S 30/30 80 150 75/160 100/210 SM Reg.±30 SM Flatness±5 L/S 20/20 70 150 65/150 2L,100/40 4L,190/40/30 L/S 15/15 60 130 60/130 75/180 SM Reg.±15

SAC305/OSP IC Embedded

2013 HVM

2013 LVM

2015

18

埋入式器件高密度封装基板

埋入技术分类

平面埋入 埋入电容 埋入电感 埋入电阻

分立器件埋入 埋入分立电容 埋入分立电阻

埋入芯片

19

平面埋入式电容、电阻高密度封装基板

传统设计 优势: -减少表面元件的安装面积。 -可以实现电子产品的小型、薄型化 -导线长度缩减,提高电子特性(可 对应高频)。 -焊点减少,提高焊接可靠性。 -旁路电容的配置的合理化,提高抗 电磁干扰能力。 -减少小型元件的安装不良,提高装 配效率。 -减少管理成本。 Value

6.4 nF/in2 16 0.005 14 μm 32 (x,y,z) 10 nF/in2 22 0.010 12 μm 31 (x,y,z) 20 nF/in2 22 0.010 6 μm 31 (x,y,z) 0.03 Epoxy, ceramic filler ~130V/μm 35 μm (1.4 mil) 30 nF/in2 22 0.010 4 μm 31 (x,y,z)

贴片

真空层压 IC芯片埋入(10x10 cm²) 激光成盲孔

金属化微盲孔 Cross section 24

实际应用案例

平面埋入基板产品,应用于MEMS封装 普通的功率芯片通过埋入线路板内 部,可以实现器件的集成及体积的缩 小。

CMMB模组埋入分立式电容

25

小型化模块发展

IPD SUB + FC + Embedded SUB + FC

G

H

150

15

高密度封装基板设计(特殊SiP设计结构)

Cavity down基板设计示意图

器件埋入式基板设计图

热 分 析

Embedded Capacitor

FR4

16

高密度封装基板关键技术

新型积层工艺

通孔填孔技术

高精度阻焊

细密金属凸点

高精度阻焊技术

表面涂覆

通孔填孔

无芯基板技术

精细线路

薄芯板&无芯

长(L1)

1.0±0.05 1.0±0.05 1.0±0.05 1.0±0.05 0.6±0.03 0.6±0.1 0.6±0.03

宽(W)

0.5±0.05 0.5±0.05 0.5±0.05 0.5±0.05 0.3±0.03 0.3±0.05 0.3±0.03

高(T)

0.5±0.05 0.32±0.05 0.33max 0.15max 0.33 0.25±0.05 0.15max

产品高密度、小型化驱动: WB基板

销售额 (百万美元 )

资料来源:Prismark 2011 Report

FC基板

13

业务模式

14

高密度封装基板设计(多芯片封装设 计)

单芯片封装

多芯片堆叠封装1

小型化

多芯片堆叠封装2

Item A B C D

多芯片堆叠封装3(FC+WB)

Description Bond Finger Edge to Die Edge Bond Finger Edge to Package Edge Film Die Edge to Package Edge Epoxy Bond Finger Edge to Bond Finger Edge Film E Die Edge to Die Edge Epoxy Bond Finger Edge to SMT Pad Edge Die Edge to SMT Pad Edge Forward SSB Film Epoxy 500 200 250 150 250 150 200 400 100 200 150 250 HVM >150 100 AVM