PCIe总线基本概念,高速串行总线取代传统并行总线是一个大的趋势

pci术概念 -回复

pci术概念-回复PCI(Peripheral Component Interconnect)是一种计算机总线标准,用于连接计算机主板上的外部设备。

它是一种通用的、高带宽的、并行的总线,并且被广泛应用于电脑或服务器系统中。

本文将逐步回答有关PCI 术语和概念的问题。

第一节:PCI的背景和起源PCI的概念最早起源于1987年,由Intel、Digital Equipment Corporation(DEC)、IBM和NCR共同提出。

他们旨在开发一种用于连接计算机主板上的外部设备的标准,以替代旧的ISA(Industry Standard Architecture)总线。

于是,PCI总线被设计出来,并在1992年正式发布。

第二节:PCI的结构和工作原理PCI总线的结构包括主板上的插槽、扩展插槽和总线控制器等组件。

每个PCI插槽都可以支持一个PCI扩展卡。

PCI总线采用的是多总线主板结构,因此可以同时支持多个PCI设备。

总线控制器负责协调和管理这些设备之间的数据传输。

第三节:PCI的版本和规格PCI标准经历了多个版本的更新和改进,每个版本都引入了新的特性和功能。

主要的PCI版本包括:PCI 1.0、PCI 2.0、PCI 2.1、PCI 2.2、PCI-X、PCI Express和PCIe 2.0等。

每个版本都有自己的规格和性能参数,如带宽、时钟频率和信号电压等。

第四节:PCIe和PCI的比较PCIe(Peripheral Component Interconnect Express)是最新的PCI版本,它与传统的PCI总线相比具有更高的性能和更先进的特性。

PCIe采用了一种全新的串行通信协议,而不是并行通信。

这使得PCIe具备了更高的带宽和更低的延迟。

此外,PCIe还引入了独立的通道概念,允许多个设备同时进行数据传输。

第五节:PCIe的拓扑结构PCIe拓扑结构指的是PCIe设备之间的连接方式。

PCIe支持多种拓扑结构,包括点对点、星型、链状和多层。

pci-e总线基本传输机制

pci-e总线基本传输机制1.引言1.1 概述概述部分的内容可以写成以下内容:PCI-E(Peripheral Component Interconnect Express)总线是一种计算机扩展插槽标准,旨在提供高速、高性能的数据传输能力。

它广泛应用于各种计算机设备,如显卡、网络卡、存储卡等,使它们能够与主板进行有效的通信和数据传输。

PCI-E总线采用了一套全新的传输机制,以取代之前的PCI (Peripheral Component Interconnect)总线。

与传统的PCI总线相比,PCI-E总线在带宽、速度和可扩展性等方面有了巨大的提升。

它能够提供更高的数据传输速度和更大的带宽,满足现代计算机对于高性能、高速度数据传输的需求。

PCI-E总线的传输机制是基于高速串行通信的。

传统的PCI总线采用的是并行传输,每次传输数据的位数较多,而PCI-E总线则采用了串行传输的方式,减少了数据线的数量,提高了信号传输的速度和质量。

同时,PCI-E总线还采用了差分传输技术,通过正负两个信号线来传输数据,有效地减少了信号的干扰和噪声,提高了信号的稳定性和可靠性。

除此之外,PCI-E总线还采用了分层的架构设计。

它将总线分为物理层、数据链路层和传输层,每一层都有相应的协议和规范,用于确保数据的正确传输和处理。

这种分层的设计使得PCI-E总线具有较高的灵活性和可扩展性,能够适应不同设备和不同需求的应用。

综上所述,PCI-E总线作为一种高速、高性能的数据传输接口,已经成为现代计算机系统中不可或缺的一部分。

它的概念和特点将在接下来的文章中进一步介绍和探讨。

1.2文章结构文章结构是指整篇文章的组织结构和内容安排。

一个清晰、合理的文章结构能够使读者更好地理解文章主题,并能够有条理地获取所需信息。

本文的结构如下:1. 引言1.1 概述:介绍PCI-E总线的重要性和应用背景,引出本文的主题。

1.2 文章结构:概述本文的组织结构并列举各部分的内容大纲。

pcie规范

pcie规范PCIe(Peripheral Component Interconnect Express)是一种高速串行总线规范,用于在计算机系统中连接各种外部设备和扩展卡。

PCIe是一种基于总线结构的互联技术,它提供了更高的带宽和更快的数据传输速度,以满足现代计算需求日益增长的需求。

本文将详细介绍PCIe规范,包括其历史、特点、工作原理以及应用领域。

PCIe的历史可以追溯到1992年,当时英特尔、IBM和康柏就开始开发PCI(Peripheral Component Interconnect)总线规范,用于取代传统的ISA和VLB总线。

PCI总线规范在1993年发布,迅速成为标准计算机接口,并在20世纪90年代普及开来。

然而,随着计算机性能的不断提升和多媒体、网络等应用的广泛应用,PCI总线的带宽和性能已经无法满足需求。

为了提供更高的带宽和更快的数据传输速度,PCI-SIG(PCI Special Interest Group)于2004年发布了PCI Express规范,即PCIe 1.0版本。

PCIe采用了全新的串行总线结构,以替代传统的并行总线。

相较于PCI总线,PCIe具有更高的数据传输速度、更低的延迟、更高的带宽和更好的可伸缩性。

PCIe的特点主要体现在以下几个方面:1. 高速传输:PCIe提供了多个版本,每个版本都有不同的数据传输速率。

当前最常见的PCIe 3.0版本,具有每条通道8 Gbps的传输速度,每条通道相当于一个全双工的高速通道。

2. 可伸缩性:PCIe采用点对点连接的拓扑结构,每个设备都有一个独立的通道,与其他设备无冲突。

这种可伸缩性使得PCIe可以支持大量的设备以及更复杂的系统架构。

3. 低延迟:由于PCIe采用了串行传输,相较于并行总线具有更低的延迟,能够更快地处理数据。

4. 热插拔支持:PCIe支持热插拔特性,即可以在计算机运行时插入或拔出设备,而不需要重启计算机。

PCIe总线架构深入剖析

PCIe总线架构深入剖析PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,被广泛用于连接扩展卡和主板之间的通信。

它是替代传统PCI(Peripheral Component Interconnect)总线的一种新一代高速总线架构。

本文将深入剖析PCIe总线架构,探讨其工作原理、主要特性和应用领域。

首先,让我们了解PCIe总线的工作原理。

PCIe总线使用了串行数据传输,相较于传统的并行数据传输,串行传输更具优势。

PCIe总线将数据分为多个数据包,通过不同的数据通道同时传输,使得数据传输更加稳定和高效。

PCIe总线采用了差分信号传输,即发送方将数据编码为正负两个相等幅度但相反的点对点差分信号,接收方通过比较两个信号的幅度大小来恢复原始数据,这种差分信号传输方式可以有效抵抗干扰和噪声。

PCIe总线的主要特性之一是其高速性能。

PCIe 3.0是当前最常用的版本,其理论带宽达到了8个Gbit/s或986.67Mbyte/s。

PCIe 4.0和PCIe 5.0则更进一步提升了传输速度,分别达到了16 Gbit/s和32 Gbit/s,这使得PCIe总线成为现代计算机系统中的重要组成部分,支持高速数据传输和处理需求。

另一个重要的特性是PCIe总线架构的可扩展性。

PCIe总线可以通过添加更多的插槽和扩展卡来扩展系统的功能和性能。

每个PCIe插槽都有自己的数据通道,这意味着可以同时连接多个高速设备而不会互相干扰。

此外,PCIe总线还支持热插拔功能,用户可以在计算机工作的过程中插入或拔出PCIe扩展卡,而无需重新启动系统,这大大提高了计算机系统的可用性和灵活性。

PCIe总线还具有优秀的可靠性和稳定性。

由于采用了差分信号传输,PCIe总线的抗干扰能力较强,能够在高速数据传输中保持稳定的连接。

此外,PCIe总线还支持错误检测和重新发送机制,确保数据的完整性和准确性。

PCIe协议相关资料要点

PCIe协议相关资料要点PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接计算机系统的外部设备。

它在现代计算机中广泛应用于图形卡、存储卡和扩展卡等设备的连接。

下面是PCIe协议的相关资料要点。

一、PCIe协议概述PCIe协议是一种高速串行通信协议,用于在计算机系统中传输数据。

它取代了传统的PCI总线,提供更高的带宽和更可靠的性能。

PCIe协议具有以下特点:1. 高速性能:PCIe协议支持多个通道和多个数据传输通路,并且每个通道都可以达到多Gbps的传输速度。

2. 点对点连接:PCIe协议采用点对点连接方式,每个设备都直接连接到主机,并且不会与其他设备共享带宽。

3. 热插拔支持:PCIe协议支持热插拔功能,可以在计算机运行时插入或拔出设备,而无需重新启动系统。

4. 多功率状态支持:PCIe协议支持多功率状态,可以有效地管理设备的能耗。

二、PCIe协议架构PCIe协议的架构包括物理层、数据链路层和传输层。

每个层级都有不同的功能和责任。

1. 物理层(Physical Layer):物理层负责在发送和接收设备之间传输数据。

它定义了数据传输的电气特性、传输速度和功耗等参数。

2. 数据链路层(Data Link Layer):数据链路层负责在发送和接收设备之间建立可靠的数据传输连接。

它通过发送和接收数据包来确保数据的完整性和可靠性。

3. 传输层(Transport Layer):传输层负责数据的路由和传输。

它根据设备的地址和标识符来确定数据的发送和接收。

三、PCIe协议数据传输PCIe协议的数据传输分为读取和写入两种方式。

1. 读取(Read):读取是指从PCIe设备读取数据到主机内存。

读取传输由主机启动,并且主机提供要读取的目标地址。

读取过程中,设备将数据传输到主机内存中的指定地址。

2. 写入(Write):写入是指将数据从主机内存写入到PCIe设备。

pcie基本原理

pcie基本原理PCIe基本原理PCIe(Peripheral Component Interconnect Express)是一种高速、点对点的串行总线标准,用于连接计算机内部的外部设备。

它是目前最流行的计算机总线标准之一,被广泛用于连接各种设备,如显卡、网卡、存储控制器等。

本文将介绍PCIe的基本原理,以帮助读者更好地理解这一技术。

PCIe采用串行传输方式,相比传统的并行总线,具有更高的带宽和更低的延迟。

它采用差分信号传输,即同时传输正负两路信号,以减少信号干扰和提高传输速度。

PCIe总线的带宽通常用“xN”来表示,其中“x”表示总线的通道数,而“N”表示每个通道的数据传输速率。

例如,PCIe 3.0 x16表示具有16个通道,每个通道的传输速率为PCIe 3.0规范下的速率。

PCIe总线采用多通道的方式来提高数据传输速度。

每个通道都有自己的发送和接收端口,可以同时进行数据传输。

此外,PCIe还支持多路复用技术,即将多个数据流通过同一物理通道传输,以提高总线的利用率。

这种设计使PCIe具有更高的带宽和更好的扩展性,可以满足不同设备对数据传输速度的需求。

PCIe总线还采用了“插槽”和“连接器”的设计,以便用户可以方便地连接和更换设备。

每个PCIe插槽都有一定数量的针脚,用于传输数据、电源和地线。

连接器则负责将插槽与设备连接起来,保证信号传输的可靠性和稳定性。

PCIe插槽通常分为不同的规格,如PCIe x1、PCIe x4、PCIe x8和PCIe x16等,以适应不同设备的需求。

PCIe总线还具有“热插拔”和“热插拔”功能,用户可以在计算机运行时插入或拔出设备,而无需重新启动计算机。

这使得设备的更换和升级变得更加方便快捷。

此外,PCIe还支持“链路层发现”和“链路层训练”功能,用于自动检测和优化总线的性能,以提高数据传输的稳定性和可靠性。

总的来说,PCIe是一种高速、灵活、可靠的计算机总线标准,被广泛应用于各种设备之间的连接。

第1章 PCI总线的基本知识

PCI(Peripheral Component Interconnect)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关。

在处理器体系结构中,PCI总线属于局部总线(Local Bus)。

局部总线作为系统总线的延伸,主要功能是为了连接外部设备。

处理器主频的不断提升,要求速度更快,带宽更高的局部总线。

起初PC使用8位的XT总线作为局部总线,并很快升级到16位的ISA(Industry Standard Architecture)总线,逐步发展到32位的EISA(Extended Industry Standard Architecture)、VESA(Video Electronics Standards Association)和MCA(Micro Channel Architecture)总线。

PCI总线规范在上世纪九十年代提出。

这条总线推出之后,很快得到了各大主流半导体厂商的认同,迅速统一了当时并存的各类局部总线。

EISA、VESA等其他32位总线很快就被PCI总线淘汰了。

从那时起,PCI总线一直在处理器体系结构中占有重要地位。

在此后相当长的一段时间里,PC处理器系统的大多数外部设备都是直接或者间接地与PCI总线相连。

即使目前PCI Express总线逐步取代了PCI总线成为PC局部总线的主流,也不能掩盖PCI总线的光芒。

从软件层面上看,PCI Express总线与PCI总线基本兼容;从硬件层面上看,PCI Express总线在很大程度上继承了PCI总线的设计思路。

因此PCI总线依然是软硬件工程师在进行处理器系统的开发与设计时,必须要掌握的一条局部总线。

PCI总线V1.0规范仅针对在一个PCB(Printed Circuit Board)环境内的,器件之间的互连,而1993年4月30日发布的V2.0规范增加了对PCI插槽的支持。

1995年6月1日,PCI V2.1总线规范发布,这个规范具有里程碑意义。

PCIe总线基本概念,高速串行总线取代传统并行总线是一个大的趋势

PCIe总线基本概念,高速串行总线取代传统并行总线是一个大的趋势PCIe总线- - -PCIe总线的提出可以算是代表着传统并行总线向高速串行总线发展的时代的到来。

实际上,不仅是PCI总线到PCIe总线,高速串行总线取代传统并行总线是一个大的趋势。

如ATA到SATA,SCSI到USB等……不过,为了兼容之前的PCI总线设备,虽然PCIe是一种串行总线,无法再物理层上兼容PCI总线,但是在软件层上面却是兼容PCI总线的。

和很多的串行总线一样,PCIe采用了全双工的传输设计,即允许在同一时刻,同时进行发送和接收数据。

如下图所示,设备A和设备B之间通过双向的Link相连接,每个Link 支持1到32个通道(Lane)。

由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。

与绝大部分的高速连接一样,PCIe采用了差分对进行收发,以提高总线的性能。

一个PCIe Lane的例子如下图所示:除了差分总线,PCIe还引入了嵌入式时钟的技术(Embedded Clock),即发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据Lane中恢复出时钟。

一个简单的时钟恢复电路模型如下图所示:注:PCie Gen3以及之后的版本采用了128b/130b的编码方式。

PCIe相对于PCI总线的另一个大的优势是其的Scalable Performance,即可以根据应用的需要来调整PCIe设备的带宽。

如需要很高的带宽,则采用多个Lane(比如显卡);如果并不需要特别高的带宽,则只需要一个Lane就可以了(比如说网卡等)。

和PCI-X总线一样,由于非常高的传输速度,PCIe是一种点对点连接的总线,而不像PCI 那样的共享总线。

但是PCIe总线系统可以通过Switch连接多个PCIe设备,也可以通过PCIe桥连接传统的PCI和PCI-X设备。

一个简单的PCIe总线系统的拓扑结构图如下所示:注:这里的Switch实际上包含了多个类似于PCI总线中桥的概念。

描述pci总线基本概念

描述pci总线基本概念

PCI总线是一种计算机内部的系统总线,用于连接计算机中的各种硬件设备。

PCI总线被广泛应用于PC机和服务器系统中,是一种高速、可靠、灵活的系统总线。

PCI总线采用并行传输方式,数据传输率高达133MB/s,远远高于ISA总线和VESA总线。

PCI总线支持热插拔,即可以在不关闭计算机的情况下更换硬件设备。

PCI总线采用基于插槽的设计,每个插槽对应一个PCI设备。

PCI 设备可以是网卡、声卡、显卡、磁盘控制器等各种硬件设备。

每个PCI设备都有一个唯一的设备ID,可以通过设备ID来识别PCI设备。

PCI总线是一种多主机设备,可以支持多个CPU同时访问同一PCI 设备。

PCI总线通过总线控制器来实现设备间的通信,总线控制器负责控制总线上的数据传输和设备访问。

总的来说,PCI总线是一种高速、可靠、灵活的系统总线,被广泛应用于PC机和服务器系统中,为计算机硬件设备的连接和通信提供了强大的支持。

- 1 -。

pcie协议

pcie协议

PCIe协议是一种计算机总线标准,用于连接主板和外设,旨在取代老旧的PCI总线。

PCIe协议采用串行传输,具有高速、高扩展性、可靠性强等优点,已成为现代计算机中最常用的总线之一。

PCIe协议分为基本协议、物理层协议和传输层协议。

其

中基本协议定义了总线操作的控制流程,如传输格式、数据流、延迟等。

物理层协议定义了硬件接口形式、传输速率、信号幅度等。

传输层协议则对应用软件层提供了一些服务和接口。

PCIe协议支持多级拓扑结构,可以在主板和外设之间增

加多个USB和扩展卡以满足系统扩展的需求。

同时,PCIe协

议也支持热插拔,外设在未关机的情况下,可以在不影响系统正常工作的情况下进行更换。

PCIe协议的传输速率越来越高,现在最新版的PCIe4.0

协议传输速率已经达到了16 GT/s,相比较PCIe 3.0协议的8 GT/s速率提升了两倍。

并且PCIe 4.0协议允许在同一时刻进

行多次传输,大大提升了数据的传输效率,使计算机性能得到全面提升。

总之,PCIe协议是一种高效、高速、可靠的计算机总线

标准,广泛应用于现代计算机中的各类外设连接和数据传输。

随着技术的不断发展,PCIe协议的传输速率和性能将会进一

步提升,相信未来会有更多的应用场景出现。

PCIE基础知识

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋.与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备.这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端.PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe总线使用的层次结构与网络协议栈较为类似.1。

1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成.高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

【博文连载】PCIe扫盲——PCI总线基本概念

【博文连载】PCIe扫盲——PCI总线基本概念PCI总线PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,它曾经是个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽。

目前该总线已经逐渐被PCI Express总线所取代。

PCI即Peripheral Component Interconnect,中文意思是“外围器件互联”,是由PCISIG (PCI Special Interest Group)推出的一种局部并行总线标准。

PCI总线是由ISA(Industy Standard Architecture)总线发展而来的,是一种同步的独立于处理器的32位或64位局部总线。

从结构上看,PCI是在CPU的供应商和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。

从1992年创立规范到如今,PCI总线已成为了计算机的一种标准总线,广泛用于当前高档微机、工作站,以及便携式微机。

主要用于连接显示卡、网卡、声卡。

注:ISA并行总线有8位和16位两种模式,时钟频率为8MHz,工作频率为33MHz/66MHz。

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。

PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备(同一时刻),其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。

注:这并不意味着所有的读写操作都需要通过北桥中转,因为PCI总线上的主设备和从设备属性是可以变化的。

比如Ethernet和SCSI需要传输数据,可以通过一种叫做Peer-to-Peer的方式来完成,此时Ethernet或者SCSI则作为主机,其它的设备则为从机。

具体会在后面的博文中详细介绍。

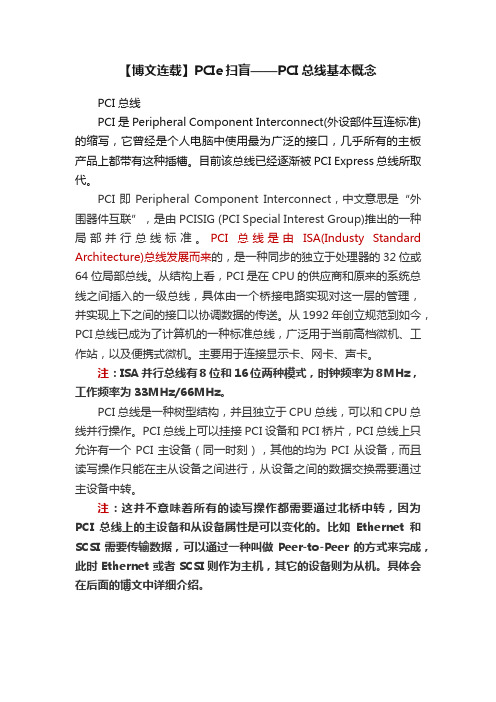

一个典型的33MHz的PCI总线系统如上图所示,处理器通过FSB 与北桥相连接,北桥上挂载着图形加速器(显卡)、SDRAM(内存)和PCI总线。

PCIE接口介绍-修改

PCIe接口介绍PCIe接口简介PCIe(Peripheral Component Interconnect Express)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Group,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe 的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)。

PCI总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe总线(在2001年发布,采用点对点串行连接)替代。

目前PCIe的主流应用是3.0,4.0还没正式推出,但标准已经制定的差不多了。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

实际使用中,PCIe无法一直维持在峰值传输状态,因为编码方式、链路管理消耗、存储时间延迟等原因,一般只有50%~60%的效率。

PCIe接口原理连接方式PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图一。

6PCI总线的基本含义

1 A/D卡设计1.1 基于PCI总线的A/D卡1、PCI总线的含义PCI是由Intel公司1991年推出的一种局部总线。

从结构上看,PCI是在CPU 和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。

管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能,它为显卡、声卡、网卡、MODEM 等设备提供了连接接口,它的工作频率为33MHz/66MHz。

PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,它是目前个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽。

PCI 插槽也是主板带有最多数量的插槽类型,在目前流行的台式机主板上,ATX结构的主板一般带有5~6个PCI插槽,而小一点的MATX主板也都带有2~3个PCI 插槽,可见其应用的广泛性。

PCI总线是一种不依附于某个具体处理器的局部总线。

管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能。

PCI总线也支持总线主控技术,允许智能设备在需要时取得总线控制权,以加速数据传送。

图1.1 典型的PCI系统总线构成2、PCI总线的基本含义不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。

这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。

在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI 设备做目标(从设备,Target或Slave)。

总线上的所有时序的产生与控制,都由Master来发起。

PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。

高速串行总线设计基础__概述及解释说明

高速串行总线设计基础概述及解释说明1. 引言1.1 概述在当前信息技术飞速发展的背景下,高速串行总线作为一种重要的数据传输方式,在各个领域都得到了广泛的应用。

它已经取代了传统的并行总线,并带来了更快、更稳定的数据传输速度。

本文将对高速串行总线的设计基础进行详细阐述,包括其概念、优势以及应用领域。

1.2 文章结构为了使读者能够系统地了解高速串行总线的设计基础,本文将分为五个主要部分来讲解相关内容。

首先,在引言部分将介绍本文的概述和结构,然后进入正文部分。

第二部分将详细讨论什么是高速串行总线以及它所具备的优势。

接着,第三部分将深入探讨高速串行总线的工作原理,包括数据传输模式、时钟和同步机制以及数据编码和解码方法等内容。

第四部分将对目前较为常见的几种高速串行总线协议标准进行比较与分析,主要涉及PCI Express(PCIe)协议标准、USB协议标准和Thunderbolt协议标准。

最后,第五部分将讨论高速串行总线设计中的关键要点与挑战,包括时钟和信号完整性管理、噪声抑制与电磁兼容(EMC)设计技术以及延迟和功耗优化方法等。

1.3 目的本文的主要目的是为读者提供高速串行总线设计的基础知识,以便更好地理解其原理和应用。

通过对高速串行总线概念、工作原理和协议标准的讲解,读者可以更加全面地了解这一领域。

同时,本文也旨在帮助读者认识到高速串行总线设计中可能遇到的关键问题和挑战,并为其提供相应的解决方法和技巧。

希望通过阅读本文,读者能够深入研究和探索高速串行总线设计,并能够在实际应用中取得更好的效果。

2. 高速串行总线设计基础:2.1 什么是高速串行总线:高速串行总线是一种数据传输技术,用于在计算机系统中连接各种设备和组件。

与传统的并行总线相比,高速串行总线使用较少的物理引脚,并通过将数据位逐位地传输来提供更高的传输速度。

它可以有效地支持更快的数据传输率,并能同时处理多个信号。

2.2 高速串行总线的优势:高速串行总线具有以下优势:- 传输速度快:由于采用逐位传输方式,高速串行总线能够实现更快的数据传输速度。

国产化软件无线电平台设计与实现

国产化软件无线电平台设计与实现[摘要]在基于国产FPGA+DSP进行软件无线电平台研制并成功实现的技术基础上,通过全面总结分析说明了系统板、业务板和接口板的研制及实现,为今后研制软件无线电平台或国产化嵌入式系统提供技术借鉴。

[关键词]VPX、软件无线电、国产化。

1.引言:软件无线电是一种新的无线电系统体系结构,是一种现代无线电工程的设计方法、设计理念,其基本思想是将开放性、可扩展、简化的硬件作为通用平台,尽可能多地利用可重配置、可扩展组件实现无线电功能的软件。

但在软件无线电平台大量采用国外软硬件产品,给我国信息安全带来很大的隐患,因此研究支持自主可控的国产化软件无线电平台软硬件关键技术,提高信息安全防护能力成为当前迫切的需求。

随着国产处理器芯片、国产操作系统等部件技术的不断发展和成熟稳定,基于国产部件研制国产自主可控软件无线电平台已经具备研制条件。

本文就一款基于国产化FPGA+DSP、操作系统部件完全自主研制的软件无线电平台进行技术经验总结,分析说明了系统板、业务板和接口板的研制及实现,为今后研制软件无线电平台或国产化嵌入式系统提供技术借鉴。

2.总线技术经过多年的研究发展,软件无线电平台现阶段的硬件体系结构有三种,分别为流水式、工作站式和总线式。

流水式硬件结构的特点就是信号流向为流水式单线,一个平台可以是一个单板, FPGA、DSP和GPP(通用处理器)为其核心器件,FPGA用于并行的高速协处理,基带信号由FPGA和DSP负责,而和用户相关的应用层由GPP处理。

流水式软件无线电结构存在独立程度不高,没有统一并开放的接口标准,使得系统的通用性和伸缩性很差,所以这种结构仅适用于某些特定的通信系统中,不能满足复杂软件无线电系统的要求。

工作站式硬件结构特点是:通过以太网或PCI-Express使PC工作站和前端处理卡互联,处理卡完成AD/DA转换、上下变频、速率转换等功能。

无线信号的处理通过PC工作站的GPU或CPU进行。

PCI总线基本概念详解

PCI 总线基本概念详解

PCI 总线

PCI 是Peripheral Component Interconnect(外设部件互连标准)的缩写,它曾经是个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插

槽。

目前该总线已经逐渐被PCI Express 总线所取代。

PCI 即Peripheral Component Interconnect,中文意思是“外围器件互联”,是由PCISIG (PCI Special Interest Group)推出的一种局部并行总线标准。

PCI 总线是由ISA(Industy Standard Architecture)总线发展而来的,是一种同步的独立于处理器的32 位或64 位局部总线。

从结构上看,PCI 是在CPU 的供应商

和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层

的管理,并实现上下之间的接口以协调数据的传送。

从1992 年创立规范到如今,PCI 总线已成为了计算机的一种标准总线,广泛用于当前高档微机、工

作站,以及便携式微机。

主要用于连接显示卡、网卡、声卡。

注:ISA 并行总线有8 位和16 位两种模式,时钟频率为8MHz,工作频

率为33MHz/66MHz。

PCI-Express总线简介

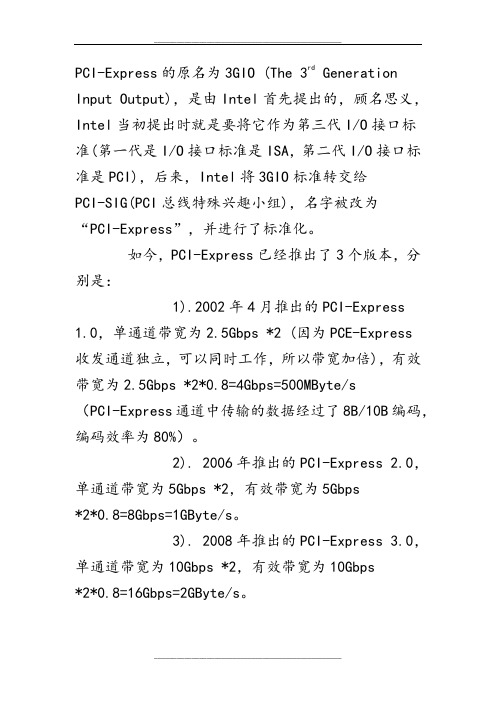

PCI-Express的原名为3GIO (The 3rd Generation Input Output),是由Intel首先提出的,顾名思义,Intel当初提出时就是要将它作为第三代I/O接口标准(第一代是I/O接口标准是ISA,第二代I/O接口标准是PCI),后来,Intel将3GIO标准转交给PCI-SIG(PCI总线特殊兴趣小组),名字被改为“PCI-Express”,并进行了标准化。

如今,PCI-Express已经推出了3个版本,分别是:1).2002年4月推出的PCI-Express 1.0,单通道带宽为2.5Gbps *2 (因为PCE-Express收发通道独立,可以同时工作,所以带宽加倍),有效带宽为2.5Gbps *2*0.8=4Gbps=500MByte/s(PCI-Express通道中传输的数据经过了8B/10B编码,编码效率为80%)。

2). 2006年推出的PCI-Express 2.0,单通道带宽为5Gbps *2,有效带宽为5Gbps*2*0.8=8Gbps=1GByte/s。

3). 2008年推出的PCI-Express 3.0,单通道带宽为10Gbps *2,有效带宽为10Gbps*2*0.8=16Gbps=2GByte/s。

PCI-Express总线的基本架构包括根组件(Root Complex)、交换器(Switch)和各种终端设备(Endpoint)。

根组件可以集成在北桥芯片中,用于处理器和内存子系统与I/O之间的连接;交换器的功能通常以软件的形式提供,包括多个逻辑PCI到PCI 的桥连接,以及与传统PCI设备的兼容性,在PCI-Express架构中出现的新设备是交换器,主要用来为I/O总线提供输出端,它也支持在不同终端设备间进行对等数据传输。

PCI-Express总线的拓扑结构如下图所示。

PCI总线特点:1).双单工,点对点传输,每个Lane包含4根线,2收2发,使用LVDS差分信号,最小差模电压175mV,共模电压3.5V,最长可传输3m。

pcie总线原理

PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于连接外部设备和计算机主板上的扩展卡。

它取代了较旧的PCI、PCI-X和AGP标准,提供了

更高的数据传输速度和更强大的性能。

PCIe总线原理涉及以下几个重要方面:

1. 数据传输:PCIe使用高速串行连接,通过多条差分信号对来实现数据传输。

这种串

行连接方式使得PCIe可以提供比传统并行总线更高的带宽和更快的数据传输速度。

2. 通道和速率:PCIe通过在主板和设备之间建立多个“通道”(lanes)来实现数据传输。

每个通道都能够以不同的速率进行传输,常见的包括x1, x4, x8, 和 x16。

这些数字表示

通道中传输的数据位数,例如,x1表示单通道,x16表示16个通道。

3. 数据包:PCIe使用数据包来传输信息,而不是简单的电平信号。

这种数据包的方式

更有效地利用了总线带宽,并提供了更好的可靠性和错误检测能力。

4. 点对点连接:每个PCIe设备都直接连接到主板上的PCIe控制器,这种点对点连接

方式避免了总线冲突和竞争,提高了系统的稳定性和可扩展性。

5. 多版本和兼容性:PCIe标准不断更新,引入了新的技术以提高性能和功能。

同时,PCIe也保持向后兼容性,因此较老的PCIe设备可以在新的PCIe插槽上运行,尽管可

能会受限于低速或其他方面的性能。

通过使用这些原理,PCIe总线能够提供高性能、低延迟和灵活的外部设备连接,成为

现代计算机系统中极为重要的一部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCIe 总线基本概念,高速串行总线取代传统并行总线

是一个大的趋势

PCIe 总线- - -

PCIe 总线的提出可以算是代表着传统并行总线向高速串行总线发展的时代的到来。

实际上,不仅是PCI 总线到PCIe 总线,高速串行总线取代传统并行总线是一个大的趋势。

如ATA 到SATA,SCSI 到USB 等……

不过,为了兼容之前的PCI 总线设备,虽然PCIe 是一种串行总线,无法再物理层上兼容PCI 总线,但是在软件层上面却是兼容PCI 总线的。

和很多的串行总线一样,PCIe 采用了全双工的传输设计,即允许在同一时刻,同时进行发送和接收数据。

如下图所示,设备A 和设备B 之间通过双向的Link 相连接,每个Link 支持1 到32 个通道(Lane)。

由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。

与绝大部分的高速连接一样,PCIe 采用了差分对进行收发,以提高总线的性能。

一个PCIe Lane 的例子如下图所示:。