通信系统仿真

通信系统仿真(精)

一、物理层仿真实验1、实验目的:初步掌握数字通信系统的仿真方法。

完成一个通信系统的搭建,并仿真得到相应的BER-Eb/No性能曲线,完成系统性能的分析。

2、实验原理通信系统仿真就是要通过计算机产生各种随机信号,并对这些信号做相应的处理以获得期望的结果,但是要求计算机产生完全随机的数据时不可能的,只能算是伪随机数。

从预测的角度看,周期数据是完全可以预测的,但当周期趋于无穷大时,可以认为该数据具有伪随机特性。

产生伪随机数的算法通常有:Wishmann-Hill算法产生均匀分布随机变量该算法是通过将3个周期相近的随机数发生器产生的数据序列进行相加,进而得到更大周期的数据序列。

定义三个随机数发生器:Xi+1=(171xi)mod(30269)Yi+1=(170yi)mod(30307)Zi+1=(172zi)mod(30323)以上三式中均需要设定一初始值(x0,y0,z0),这三个初始值一般称为种子。

产生的三个序列的周期分别是:30269、30307、30323。

将这三个序列组合相加即可得到一个周期更大的均匀分布随机序列:Ui=(Xi/30269+Yi/30307+Zi/30323)mod(1)逆变换法产生Rayleigh分布随机变量逆变换法的基本思想是:将一个不相关均匀分布的随机序列U映射到一个具有概率分布函数Fx(x)的不相关序列随机序列X,条件是要产生的随机变量的分布函数具有闭合表达式。

R=sqrt(-2σ2 ln(u))根据上式即可将均匀分布的随机变量映射为Rayleigh分布的随机变量。

根据Rayleigh分布随机变量产生Gussian分布随机变量通信系统中的噪声通常建模为白高斯噪声,其含义是功率谱是白的,信号分布是满足高斯的。

基于Rayleigh随机变量,可以方便的产生Gussian分布的随机变量。

关系如下:X=R*COS(2πu1)Y=R*SIN(2πu2)其中U1和U2分别是两个均匀分布的随机变量,产生的X和Y均为高斯随机变量。

通信系统仿真实验报告

通信系统仿真实验报告摘要:本篇文章主要介绍了针对通信系统的仿真实验,通过建立系统模型和仿真场景,对系统性能进行分析和评估,得出了一些有意义的结果并进行了详细讨论。

一、引言通信系统是指用于信息传输的各种系统,例如电话、电报、电视、互联网等。

通信系统的性能和可靠性是非常重要的,为了测试和评估系统的性能,需进行一系列的试验和仿真。

本实验主要针对某通信系统的部分功能进行了仿真和性能评估。

二、实验设计本实验中,我们以MATLAB软件为基础,使用Simulink工具箱建立了一个通信系统模型。

该模型包含了一个信源(source)、调制器(modulator)、信道、解调器(demodulator)和接收器(receiver)。

在模型中,信号流经无线信道,受到了衰落等影响。

在实验过程中,我们不断调整系统模型的参数,例如信道的衰落因子以及接收机的灵敏度等。

同时,我们还模拟了不同的噪声干扰场景和信道状况,以测试系统的鲁棒性和容错性。

三、实验结果通过实验以及仿真,我们得出了一些有意义的成果。

首先,我们发现在噪声干扰场景中,系统性能并没有明显下降,这说明了系统具有很好的鲁棒性。

其次,我们还测试了系统在不同的信道条件下的性能,例如信道的衰落和干扰情况。

测试结果表明,系统的性能明显下降,而信道干扰和衰落程度越大,系统则表现得越不稳定。

最后,我们还评估了系统的传输速率和误码率等性能指标。

通过对多组测试数据的分析和对比,我们得出了一些有价值的结论,并进行了讨论。

四、总结通过本次实验,我们充分理解了通信系统的相关知识,并掌握了MATLAB软件和Simulink工具箱的使用方法,可以进行多种仿真。

同时,我们还得出了一些有意义的结论和数据,并对其进行了分析和讨论。

这对于提高通信系统性能以及设计更加鲁棒的系统具有一定的参考价值。

通信系统仿真的作用及应用前景

4 通信系统仿真问题的研究价值

通信系 统仿真实质上就是把硬件实验搬

进了计算机 ,可以把它看成是一种软件实 验. 与硬件实验相比, 软件实验具有如下一 些优点 : ( 1 ) 软件实验具有广泛的适应性和极好 的灵活性. 在硬件实验中改变系统参数也许 意味着要重做硬件,而在软件实验中则是改

电 子科技大学出 版社, 0 . 象,分层建模,模型定义,仿真自 动生成等特征。

3 通信系统仿真的作用

通信系统仿真应用到了通信系统工程设 计的各个阶段,无论是从早期的概念设计, 还是实现、测试、使用等各个阶段。在概 念定义阶段,通信系统仿真获得顶层指标。 在接下来的设计和研发中,通信系统仿真确 定硬件研发的指标 ,检验己完成子系统对整 个系统性能的影响。在运行阶段,通信系统 仿真可以用来确定解决问题的方法。通信系 统仿真还可以预测系统的使用寿命。现代计 算机软硬件技术的快速发展, 新一代的可视 化的仿真软件的使用使得通信系统仿真的设 计和分析过程变得相对直观和便捷,推动了 通信系统仿真的快速发展。 随着通信和信号处理系统的复杂程度的 提高,同时出现了一系列新的技术,如用干 数字信号处理的价格不高但速度很快的硬 件、光纤光学器件、集成光学设备和单片微 波集成电路, 这些对通信系统的实现均有重 要影响。通信系统复杂度的提高使得用来分 析和设计系统的时间和精力也相应提高了, 然而在商用产品中引 人新技术要求设计能做 到短时、高效、省力,而这些要求只有通 过使用强大的计算机辅助分析和设计工具才

4 结束语

作为一种前沿科技, F I D 正引起国内 参考文献 R IB 智能建筑与城市信息,2004 ,11) : ( 外许多企业、零售商、院校、科研单位的 川 Rao ,K . V. 5 . An over view of 7 2 一7 6 关注和兴趣,纷纷开展实际性的研发工作。 back以 t re r d o fr阂uency ldentl一 泊 d a i e 4 随着RF ID 标准的不断成熟,技术的发展演 ficat ion system(RFID) . Microwave t 』中国RFID 产业如何稳中求快. 中国电 子报,2004一 12一 30. 进,以及成本的降低,R F ID 将更加融入我 Con fe r en ce , 1999 As ia P ac ific , ] 5 ID 们的日 常生活,渗透到社会的方方面面。展 Volume : 3 , 1999 ,Page(5) : 746一 749 【 钱恒. 关于我国RF一 发展的几点思 考. w、 . 讨 r 迁 o m.c , X抖,1 . 刀 ldi 0.c w n 2( 2 yol .3。 望未来,不仅RF D 本身将形成一个规模巨 I 大的产业,由R FID 所形成的物联网对社会 [ Mawh 加 ey D, c r wave t g identl一 ] 2 叮 Mi o a i f ca tion s外tems . R CA R ev ,1983, 月 的影响更是不可估量。

《通信系统仿真》实验改革的探索与体会

《通信系统仿真》实验改革的探索与体会通信系统仿真实验为计算机科学与技术专业的学生提供了一个可以全面掌握通信系统仿真原理和技能的机会。

近年来,随着社会科学研究的不断发展,我们通信系统仿真实验也经历了一次重大的改革。

本文通过对改革实施和实施效果的分析,探讨了通信系统仿真实验改革的探索和体会。

首先,对通信系统仿真实验进行改革的目的是提高学生的实践能力和实践素养。

为了达到这一目标,我们在实验内容和实验形式上做了一些改革。

首先,我们将实验的内容由传统的理论知识转向实践性的实验内容,通过实验的做法来实现理论知识的运用,从而更好地培养学生的实践素养和实践能力。

其次,我们在实验形式上也作出了一些改变。

将传统的小组讨论方式改为学生更加自主的实验形式,让学生亲自动手实践,进一步增强实践素养和实践能力。

改革后的通信系统仿真实验给学生带来了显著的实践能力和实践素养的提高,但也存在一些问题,如学生的态度不够认真或缺乏实践的技能。

为了解决这些问题,我们针对学生的不同问题,在教学过程中更加细致入微,采用更加灵活多变的方式,指导学生进行实践。

例如,在实践前,教师要讲解实验原理及实验流程,让学生明白实验的目的及对实验结果的重要性;在实验过程中,教师还要详细的讲解相关技术,以及步骤的演示,帮助学生完成实验,得出正确的结论;在实验结束后,还要结合实验结果,进行实验结论的总结,以此让学生更好的掌握实验所涉及的知识,增强自己实践能力和实践素养。

通过实施上述改革,我们在提高学生实践能力和实践素养方面取得了明显的效果。

学生在实验中更加灵活地运用自己所学的知识和技能,明白实验的目的及实验结果的重要性,并根据实验结果作出正确的结论,这说明实践能力和实践素养已经初步提高。

总之,通过对通信系统仿真实验的改革,我们发现了一些新的发现,提出了一些新的观点,并在提高学生实践能力和实践素养方面取得了显著的成效。

今后,根据实际情况进行相应的调整和完善,努力实现学生实践能力和实践素养的最佳提升。

通信系统的仿真实验资料

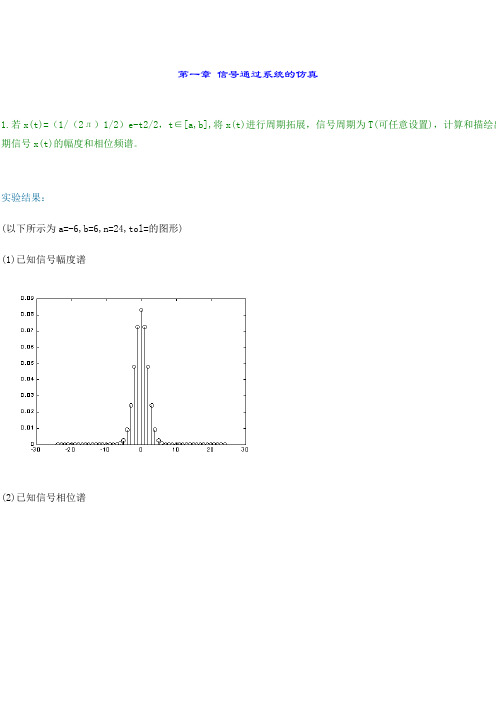

第一章信号通过系统的仿真1.若x(t)=(1/(2л)1/2)e-t2/2,t∈[a,b],将x(t)进行周期拓展,信号周期为T(可任意设置),计算和描绘出期信号x(t)的幅度和相位频谱。

实验结果:(以下所示为a=-6,b=6,n=24,tol=的图形)(1)已知信号幅度谱(2)已知信号相位谱2.信号定义为x(t)= cos(2л*47t)+cos(2л*219t), 0≤t≤100, 其它假设信号以1000抽样/秒进行抽样。

用MATLAB设计一个低通Butterworth滤波器。

确定并绘出输出的功率谱和输入功率谱比较(滤波器的阶数及截频可自行确定)。

实验结果:(以下为阶数=4,截频=100Hz的图形)(1)输入信号功率谱密度(2)输出信号功率谱密度第二章随机过程仿真1.从下式的递归关系中产生一个高斯马尔可夫过程的1000个(等间距)样本的序列Xn=+ωn n=1,2,…1000,式中X0=0,ωn是一个零均值,方差为1,独立的随机变量序列。

绘出序列{ Xn,1≤n≤1000}与时序n的关系及相关函数N-mRx(m)=1/(N-m)ΣXn Xn+m m=0,1,…50 式中N=1000.n-1实验结果:(1)高斯——马尔可夫过程(2)高斯马尔可夫过程的自相关函数2.假设一个具有抽样序列{X(n)}的白噪声过程通过一个脉冲响应如下所示的线性滤波器nh(n)= ,n≥00, n<0求输出过程{Y(n)}的功率谱和自相关函数Ry(τ)。

实验结果:(1)输出的功率谱(2)输出的自相关第三章模拟调制仿真1.用MATLAB软件仿真AM调制。

被调信号为1, (t0/3)>t>0;m(t)=-2, (t0/3)≤t≤(2*t0/3);0, 其它;利用AM 调制方式调制载波。

假设t0=,fc=250hz;调制系数a=。

实验结果:1)调制信号、载波、已调信号的时域波形2)已调信号的频域波形2.被调信号为1, t0/3>t>0;m(t)=-2, t0/3<= t<2*t0/3;0, 其它;采用频率调制方案。

通信系统建模与仿真重点

(1)模型的分类模型分为两大类:一类是物理模型,就是采用一定比例尺按照真实系统的“样子”制作;另一类是数学模型,就是用数学表达式来描述系统的内在规律。

(2)通信系统仿真的方法三种1.公式计算法;2.硬件样机测试研究法;3.波形仿真法(3)仿真在通信系统中所起的作用?仿真在通信系统的设计过程中起着重要作用:在概念定义阶段,仿真给出了顶层的技术要求;在设计进程和开发过程中,仿真与硬件开发一起确定最后的技术条件,并检查子系统对整个系统性能的影响;在运行情况下,仿真可以做检修故障的工具,并且预计系统的EOL性能。

(4)通信仿真系统的建模结构分为哪几种?通信仿真系统的建模结构分成系统建模、设备建模和过程建模三种。

(5)过程建模主要有几种,各自作用?过程建模分为三种:信源、噪声和干扰随机过程建模,随机信道建模,等价随机过程建模。

作用:在系统的设计和检测中,信源经常被用作测试信号,信道建模实际上也是随机过程建模,等价随机过程模型可以减少运动量。

(6)泊松过程的特性?1.X(0)=0,即零初值性;2.对任意的s≥t≥0,∆t≥0,增量X(s+∆t)−X(t+∆t)与X(s)−X(t)具有相同的分布函数,即增量平稳性或齐次性;3.对任意的正整数n,以及任意的非负实数0≤t0≤t1≤⋯≤t n,增量X(t1)−X(t0), X(t2)−X(t1),⋯ , X(t n)−X(t n−1),相互独立,即增量独立性;4.对于足够小的时间∆t,有P[X(∆t)=1]=λ∆t+O(∆t)P[X(∆t)=0]=1−λ∆t+O(∆t)P[X(∆t)≥2]=O(∆t)即称{X(t),t≥0}是强度为λ的泊松方程。

(7)平稳随机过程?所谓平稳随机过程,是指它的任何n维分布函数或概率密度函数与时间起点无关。

(8)试求功率谱密度为P n =n 0/2的白噪声通过理想低通滤波器后的功率谱密度、自相关函数及噪声功率N 。

解:理想低通滤波器特性可由下式表示H (ω)={k 0e −jωtd ,|ω|≤ωH 0 , 其它ω可见|H (ω)|2=K 02,|ω|≤ωH计算输出功率谱密度为P Y (ω)=|H (ω)|2P n (ω)=K 02n 02,|ω|≤ωH 而自相关函数R Y (τ)为R Y (τ)=12π∫P Y (ω)e jωπdω∞−∞ =K 02n 04π∫e jωπωH −ωH dω =K 02n 0f H sin ωH τωH τ, f H =ωH 2π于是,输出噪声功率N 为R Y (0),即 N=R Y (0)= K 02n 0f H可见,输出的噪声功率与K 02、n 0及f H 成正比。

通信系统的模拟仿真技术应用

通信系统的模拟仿真技术应用随着现代科技的不断发展,通信系统作为人类社会中最为重要的信息传递方式之一,已经成为现代社会不可或缺的基础设施。

而通信系统的复杂性和高效性又使其变得十分难以理解和掌握。

为了更好地理解和应用通信系统,模拟仿真技术应运而生,并得到了广泛的应用。

一、通信系统的模拟仿真技术通信系统的模拟仿真技术是指运用计算机等数学模型,对通信系统进行各种形式的仿真,以提供对通信系统的性能和行为的评估和分析。

通信系统的模拟仿真技术可以在设计和实现通信系统的过程中提供可靠的支持,以确保通信系统的可靠性和效率。

通信系统的模拟仿真技术可以分为三类基本方法:数学模型仿真、电路仿真和物理仿真。

其中数学模型仿真是最常见的方法,通常使用MATLAB等数学仿真软件实现。

数学模型仿真基于通信系统的数学模型来模拟通信系统的性能和行为。

数学模型是指将通信系统的各种物理特性转化成数学方程或算法,以便用计算机进行模拟仿真。

通信系统的数学模型通常包括信道特性模型、信号生成模型、信号传播模型、信号检测模型等。

电路仿真是指通过计算机对通信系统电路进行仿真。

通信系统的电路仿真通常使用SPICE、ADS等电路仿真软件实现。

通过电路仿真,可以对通信系统电路的性能和行为进行模拟分析,从而优化通信系统的设计和实现。

物理仿真是指在实验室环境下对通信系统进行仿真实验。

通信系统的物理仿真通常使用各种测量仪器,如示波器、信号分析器、频谱分析仪等。

物理仿真可以对通信系统的行为进行更加准确的分析,但是实验成本较高。

二、通信系统的模拟仿真应用通信系统的模拟仿真技术在通信领域的应用非常广泛,主要包括以下几个方面。

1. 通信系统设计通信系统设计是通信领域中最重要的应用之一。

通信系统的设计主要包括系统结构设计、信号处理算法设计、信号传输方案设计等。

通信系统的模拟仿真技术可以对设计方案进行各种形式的仿真实验,帮助系统设计人员理解系统的性能和行为。

2. 通信系统性能分析通信系统的性能分析是了解通信系统性能表现的重要手段。

通信系统仿真报告

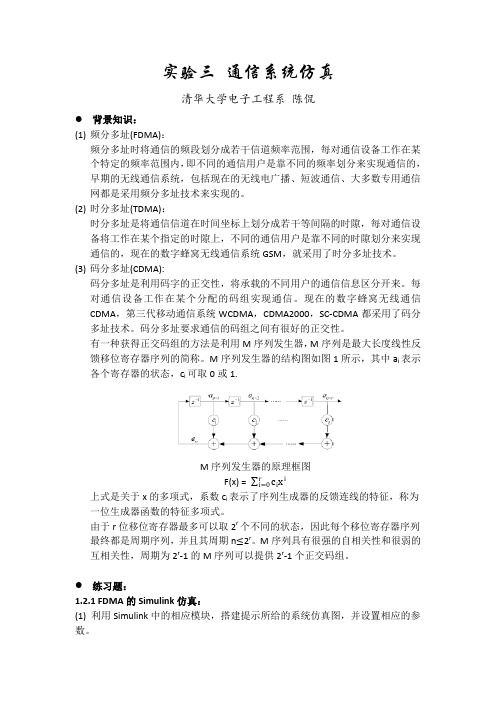

实验三 通信系统仿真清华大学电子工程系 陈侃● 背景知识:(1) 频分多址(FDMA):频分多址时将通信的频段划分成若干信道频率范围,每对通信设备工作在某个特定的频率范围内,即不同的通信用户是靠不同的频率划分来实现通信的,早期的无线通信系统,包括现在的无线电广播、短波通信、大多数专用通信网都是采用频分多址技术来实现的。

(2) 时分多址(TDMA):时分多址是将通信信道在时间坐标上划分成若干等间隔的时隙,每对通信设备将工作在某个指定的时隙上,不同的通信用户是靠不同的时隙划分来实现通信的,现在的数字蜂窝无线通信系统GSM ,就采用了时分多址技术。

(3) 码分多址(CDMA):码分多址是利用码字的正交性,将承载的不同用户的通信信息区分开来。

每对通信设备工作在某个分配的码组实现通信。

现在的数字蜂窝无线通信CDMA ,第三代移动通信系统WCDMA ,CDMA2000,SC-CDMA 都采用了码分多址技术。

码分多址要求通信的码组之间有很好的正交性。

有一种获得正交码组的方法是利用M 序列发生器,M 序列是最大长度线性反馈移位寄存器序列的简称。

M 序列发生器的结构图如图1所示,其中a i 表示各个寄存器的状态,c i 可取0或1.M 序列发生器的原理框图F(x) = c i x ir i=0上式是关于x 的多项式,系数c i 表示了序列生成器的反馈连线的特征,称为一位生成器函数的特征多项式。

由于r 位移位寄存器最多可以取2r 个不同的状态,因此每个移位寄存器序列最终都是周期序列,并且其周期n ≤2r 。

M 序列具有很强的自相关性和很弱的互相关性,周期为2r -1的M 序列可以提供2r -1个正交码组。

● 练习题:1.2.1 FDMA 的Simulink 仿真:(1) 利用Simulink 中的相应模块,搭建提示所给的系统仿真图,并设置相应的参数。

答:按照提示所给的模型图以及相应模块的参数,我设计出的FDMA 系统仿真图如下所示:(2) 上图中的六个Analog Filter Design 滤波器的作用分别是什么?根据已知的参数设置它们的参数,然后进行系统仿真,记录下三个Scope 上显示的波形。

通信系统仿真课程设计

通信系统仿真课程设计1. 引言通信系统是现代社会不可或缺的一部分,它在无线通信、互联网、电视、手机、卫星通信等方面都有广泛应用。

为了能够更好地理解和分析通信系统的性能,在通信工程领域中,仿真技术被广泛应用。

本课程设计将介绍通信系统仿真的相关概念、方法和工具,以及如何根据具体问题进行通信系统的仿真。

2. 通信系统仿真的目的和意义通信系统仿真是通过计算机模拟通信系统的运行和性能,以达到理解系统特性、优化设计和解决问题的目的。

它在通信工程领域有着重要的意义和广泛的应用。

通信系统仿真的目的主要有以下几点:•理解系统特性:通过仿真可以深入了解通信系统的各个组成部分,包括信源、信道、调制解调器、信道编码和解码等,从而更好地理解系统的工作原理和性能特点。

•优化设计:通过仿真可以评估不同的系统设计方案,找到最佳的参数配置和算法,从而提高系统的性能,降低成本。

•解决问题:通过仿真可以模拟通信系统在不同情况下的性能表现,从而分析和解决实际问题,比如干扰问题、误码率改善等。

3. 通信系统仿真的基本原理通信系统仿真的基本原理是模拟和计算。

通信系统仿真通常涉及到以下几个方面的模拟和计算:•信源:通过模拟产生各种类型的信号,比如正弦波、随机信号等。

•信道:通过模拟产生不同的信道特性,比如传输损耗、多路径效应、噪声等。

可以通过添加白噪声、多径信道模型等方式来模拟实际信道的特性。

•调制解调器:通过模拟调制解调过程,将数字信号转换为模拟信号或者将模拟信号转换为数字信号。

•信道编码和解码:通过模拟编码和解码过程,对信号进行编码和解码,提高抗干扰性能。

•误码分析:通过模拟接收端信号的误码情况,分析误码率和误差传播等指标。

通信系统仿真的计算过程需要使用编程语言和相关工具,比如MATLAB、Python等,以及通信系统仿真平台,比如NS-3、OPNET等。

4. 通信系统仿真的步骤通信系统仿真通常包括以下几个步骤:1.确定仿真目标:明确仿真的目标,包括仿真对象、仿真精度和仿真场景等。

通信系统仿真教案(信道和调制解调)

信道

传输信号的媒介,如无线电波、 光纤等。

信宿

接收并使用信息,如收音机、 电视机等。

通信系统的分类

有线通信系统

利用电缆、光缆等物理介质传输信号。

模拟通信系统

传输连续的模拟信号,如调频广播。

无线通信系统

利用电磁波传输信号,如手机、卫星通信等。

数字通信系统

传输离散的数字信号,如数字电视、计算机 网络等。

04

解调技术

解调的基本概念

01

解调是将已调信号从载波中提取出来以便进一步处理的过程。

02

解调是调制的逆过程,其作用是将已调信号还原成原始基带信

号。

解调方式分为线性解调和非线性解调两种。

03

常见的解调方式

相干解调

相干解调也称为同步解调,它需要使用已调信号的相位信息进行解调。相干解调的优点是解调性能较好,但需要 同步信号,因此在实际应用中受到一定限制。

通信系统仿真教案(信道和调 制解调)

目录

• 通信系统概述 • 信道特性 • 调制技术 • 解调技术 • 通信系统仿真

01

通信系统概述

通信系统的基本组成

发送器

将信源产生的信息转换为适合 传输的信号,如调频、调相、 调幅等。

接收器

接收信道传输的信号,并将其 还原为原始信息。

信源

产生需要传输的信息,如声音、 图像、文字等。

信道容量

信道容量表示信道传输信息的最大速率,是衡量信道性能的 重要指标。

信道编码

为了提高通信系统的可靠性和传输效率,需要对信号进行编 码处理,包括纠错编码和加密编码等。

03

调制技术

调制的基本概念

调制的基本概念

调制是将低频信号(基带信号)附加到高频载波 信号上,以便于传输的过程。

通信系统仿真课程设计c语言

通信系统仿真课程设计c语言一、教学目标本课程的教学目标是使学生掌握通信系统仿真的基本原理和方法,能够运用C语言进行通信系统的仿真分析。

具体目标如下:1.理解通信系统的基本原理和仿真方法。

2.掌握C语言的基本语法和编程技巧。

3.熟悉通信系统仿真实验的流程和技巧。

4.能够运用C语言编写简单的通信系统仿真程序。

5.能够分析仿真结果,对通信系统进行性能评估。

6.能够独立完成通信系统仿真实验,并撰写实验报告。

情感态度价值观目标:1.培养学生的创新意识和团队合作精神。

2.增强学生对通信技术的兴趣和热情。

3.培养学生的科学思维和解决问题的能力。

二、教学内容本课程的教学内容主要包括以下几个部分:1.通信系统的基本原理:介绍通信系统的基本概念、信号处理方法、调制解调技术等。

2.通信系统仿真方法:讲解通信系统仿真的基本方法,包括系统模型建立、仿真算法选择等。

3.C语言编程基础:介绍C语言的基本语法、数据类型、运算符、控制结构等。

4.通信系统仿真实验:进行一系列的通信系统仿真实验,让学生动手实践,掌握仿真技巧。

三、教学方法本课程采用多种教学方法,以激发学生的学习兴趣和主动性:1.讲授法:讲解通信系统的基本原理和仿真方法,让学生理解理论知识。

2.讨论法:学生进行小组讨论,培养学生的团队合作精神和创新意识。

3.案例分析法:分析典型的通信系统仿真案例,让学生掌握仿真技巧。

4.实验法:进行通信系统仿真实验,让学生动手实践,提高操作能力。

四、教学资源本课程的教学资源包括以下几个方面:1.教材:选用合适的教材,为学生提供系统的理论知识学习。

2.参考书:提供相关的参考书籍,丰富学生的知识视野。

3.多媒体资料:制作课件、实验视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:提供计算机、通信设备等实验设备,保障学生能够进行实际操作。

五、教学评估本课程的教学评估主要包括以下几个方面:1.平时表现:评估学生在课堂上的参与程度、提问回答情况等,以考察学生的学习态度和积极性。

通信系统设计仿真软件

通信系统设计仿真软件通信系统设计仿真软件是指一种通过计算机模拟通信系统性能的工具。

它可以模拟整个通信系统,包括信源、信道、接收机等,并支持各种不同类型的信号,例如模拟信号、数字信号、频带受限信号等。

这种软件通常用于设计和优化新型通信系统,并且在通信工程师的日常工作中也扮演着重要的角色。

首先,通信系统设计仿真软件在通信系统设计方面具有重要作用。

通过使用这种软件,工程师可以快速创建并评估各种通信系统的性能,包括信噪比、误码率、带宽利用率、传输速度等等。

这能够大大缩短设计周期,避免在实际测试中浪费时间和资源。

另外,通过对仿真数据的分析,工程师可以更好地理解信道特性,从而做出更明智的决策。

其次,通信系统设计仿真软件对于新型通信技术的开发和测试也非常有用。

随着通信技术的不断进步,越来越多的新型技术被开发出来,其中一部分需要在高噪声环境下进行测试。

这时,使用通信系统设计仿真软件可以模拟各种不同的环境,包括高噪声、高速移动等等,从而评估新技术的性能。

通过这种方法,工程师可以快速找到新技术的优势和缺点,并对其进行进一步的改进。

第三,通信系统设计仿真软件也非常有用在通信系统故障诊断和维护方面。

经常出现在通信系统中的故障,例如误码率过高、信号丢失等等问题,通常是由于系统中某个部件的故障或拓扑结构错误所引起。

通过使用仿真软件,工程师可以快速定位故障,并推断出可能的原因。

这种方法可以大大缩短通信系统故障排除时间,并避免在实际测试中浪费时间和资源。

最后,通信系统设计仿真软件也用于教育和培训。

通信系统是复杂的,设计仿真软件的使用需要深入的理解和技巧。

因此,越来越多的通信工程师和学生使用仿真软件进行培训和学习。

这种仿真软件在教学中的优点包括:提供一个安全、低成本和可重复的实验平台,支持实时数据采集和分析,并提供可视化的数据展示和实验结果。

总之,通信系统设计仿真软件在通信系统设计、新技术开发、故障排查和教育培训等方面都有着广泛的应用和优势。

通信系统级仿真流程

通信系统级仿真流程

一、确定仿真目标

1.确定系统级仿真的目标

(1)确定仿真的具体问题或需求

(2)明确仿真的范围和目的

二、收集系统参数

1.收集通信系统的参数

(1)收集系统组成部分的参数

(2)获取通信信道的特性参数

三、建立仿真模型

1.选择仿真工具

(1)选择合适的仿真软件或工具

(2)确保工具能够支持系统级仿真需求2.建立系统模型

(1)构建系统各组成部分的模型

(2)建立信道模型和传输模型

四、运行仿真

1.设定仿真参数

(1)设定仿真的时间范围和步长(2)确定仿真条件和初始状态2.运行仿真模型

(1)启动仿真软件进行仿真(2)监控仿真过程中的输出结果

五、仿真结果分析

1.分析仿真数据

(1)对仿真结果进行数据分析(2)检查系统性能和指标

2.优化系统设计

(1)根据仿真结果优化系统设计(2)提出改进建议和调整方案。

通信工程中的通信系统仿真与性能评估

通信工程中的通信系统仿真与性能评估在当今信息高速传递的时代,通信工程如同构建起信息世界的桥梁,让人们能够便捷、迅速地交流与获取信息。

而在通信工程领域中,通信系统仿真是一项至关重要的技术手段,它能够帮助我们深入理解通信系统的工作原理,预测系统性能,并为优化和改进提供有力的依据。

同时,对通信系统性能的准确评估也是确保通信质量和用户体验的关键环节。

通信系统仿真,简单来说,就是通过建立数学模型和使用计算机软件,模拟真实通信系统的运行情况。

这就好比在虚拟的世界中搭建一个通信网络,然后观察数据如何在这个网络中传输、处理和接收。

为什么要进行通信系统仿真呢?首先,实际构建一个完整的通信系统需要巨大的成本和时间投入。

在系统正式建设之前,通过仿真可以提前发现潜在的问题和缺陷,从而节省资源并降低风险。

其次,仿真能够让我们在不同的条件和场景下对系统进行测试,比如改变信号强度、噪声水平、用户数量等,以了解系统在各种复杂环境下的性能表现。

那么,通信系统仿真又是如何实现的呢?通常,它包括以下几个主要步骤。

第一步是系统建模,这就需要我们对通信系统的各个组成部分,如发射机、信道、接收机等,进行数学描述,确定它们的工作原理和参数。

第二步是选择合适的仿真工具和算法。

市面上有许多专业的通信仿真软件,它们具备强大的功能和丰富的库函数,可以帮助我们快速搭建仿真环境。

第三步是设置仿真参数,这包括输入信号的特征、信道特性、噪声类型和强度等。

第四步就是运行仿真,并对结果进行分析和处理。

在通信系统仿真中,模型的准确性和有效性是至关重要的。

如果模型过于简单,可能无法反映真实系统的复杂特性;而如果模型过于复杂,又会导致计算量过大,仿真时间过长。

因此,在建模过程中,需要在模型的准确性和计算效率之间找到一个平衡点。

同时,还需要对模型进行验证和校准,确保其能够准确地预测系统的性能。

说完通信系统仿真,我们再来谈谈通信系统的性能评估。

性能评估的目的是衡量通信系统在不同条件下满足用户需求的能力。

通信系统仿真课程设计

通信系统仿真课程设计一、课程设计概述通信系统仿真课程设计是通信工程专业的重要课程之一,旨在通过实践操作,让学生掌握通信系统仿真的基本原理、方法和技能。

本课程设计涉及到多个学科领域,如数字信号处理、模拟电路设计、通信原理等。

二、课程设计目标1.了解通信系统仿真的基本原理和方法;2.掌握Matlab软件的使用;3.熟悉数字信号处理和模拟电路设计;4.能够运用所学知识,完成一个简单的通信系统仿真实验。

三、课程设计内容1.数字信号处理(1)采样定理(2)离散傅里叶变换(3)数字滤波器设计2.模拟电路设计(1)放大器电路(2)滤波器电路(3)混频器电路3.通信原理(1)调制与解调技术(2)误码率分析(3)传输链路建立与维护4.Matlab软件使用(1)Matlab基础语法(2)Matlab图像绘制(3)Matlab数据处理与分析四、课程设计步骤1.确定仿真系统的需求和设计目标;2.搜集相关资料,了解仿真系统的基本原理和方法;3.进行仿真系统的设计和实现,包括数字信号处理、模拟电路设计、通信原理等方面;4.对仿真结果进行分析和评估,得出结论;5.撰写课程设计报告。

五、课程设计案例以一个简单的调制解调系统为例,介绍通信系统仿真课程设计的具体步骤。

1.需求分析设计一个基于QPSK调制解调技术的通信系统,要求实现以下功能:(1)产生随机比特序列并进行QPSK调制;(2)添加高斯白噪声并计算误码率;(3)对接收信号进行QPSK解调,并恢复原始比特序列。

2.搜集资料了解QPSK调制解调技术的基本原理和方法,学习Matlab软件的使用方法。

3.系统设计(1)产生随机比特序列并进行QPSK调制利用Matlab软件生成随机比特序列,并将其转换为QPSK符号。

通过画图工具绘制星座图,观察符号分布情况。

(2)添加高斯白噪声并计算误码率在发送信号中添加高斯白噪声,模拟信道的干扰。

通过误码率分析工具计算误码率。

(3)对接收信号进行QPSK解调,并恢复原始比特序列利用Matlab软件对接收信号进行QPSK解调,得到恢复后的比特序列。

通信系统仿真实验

实验一:模拟调制系统设计分析振幅调制系统(常规AM)1.实验要求根据设计要求应用软件搭建模拟调制、解调(相干)系统,运行系统观察各点波形并分析频谱,改变参数研究其抗噪特性。

2.实验原理(1)AM信号的表达式、频谱及带宽在图1-1中,若假设滤波器为全通网络(=1),调制信号叠加直流后再与载波相乘,则输出的信号就是常规双边带条幅信号。

AM调制器模型如图3-2所示。

图1-1 AM调制器模型AM信号的时域和频域表达式分别为:式中,为外加的直流分量;可以是确知信号也可以是随机信号。

AM信号的典型波形和频谱分别如图1-2(a)、(b)所示,图中假定调制信号的上限频率为。

显然,调制信号的带宽为图1-2 AM波形和频谱由图1-2(a)可见,AM信号波形的包络与输入基带信号成正比,故用包络检波的方法很容易恢复原始调制信号。

但为了保证包络检波时不发生失真,必须满足,否则会出现过调幅而失真。

AM信号的频谱是由载频分量和上、下两个边带组成(通常称频谱中画斜线的部分为上边带,不画斜线的部分为下边带)。

上边带的频谱与原调制信号的频谱结构相同,下边带是上边带的镜像。

显然,无论是上边带还是下边带,都含有原调制信号的完整信息。

故AM信号是带有载波的双边带信号,它的带宽为基带信号带宽的两倍,即:式中,为调制信号的带宽,为调制信号的最高频率。

(2)AM信号的解调调制过程的逆过程叫做解调。

AM信号的解调是把接收到的已调信号还原为调制信号。

AM信号的解调方法有两种:相干解调和包络检波解调。

在这里我们采用的是想干解调。

由AM信号的频谱可知,如果将已调信号的频谱搬回到原点位置,即可得到原始的调制信号频谱,从而恢复出原始信号。

解调中的频谱搬移同样可用调制时的相乘运算来实现。

相干解调的原理框图如图1-3所示图1-3 相干解调原理图将已调信号乘上一个与调制器同频同相的载波,得由上式可知,只要用一个低通滤波器,就可以将第1项与第2项分离,无失真的恢复出原始的调制信号3.实验内容与分析(1)实验图如下所示:加法器20以及其上面部分为AM调制,23为信号源1KHZ,幅度2伏;09为载波15KHZ,幅度5伏。

通信电子中的系统仿真技术

通信电子中的系统仿真技术随着科技的发展,通信电子领域的发展也越来越迅速。

在通信电子领域,系统仿真技术在产品设计和开发中起着非常重要的作用。

系统仿真技术允许我们在计算机上对整个系统进行实时运行,预测系统的性能,发现潜在的问题,并最终优化设计。

本文将探讨通信电子中系统仿真技术的应用和意义。

一、系统仿真技术的概述仿真是一种使用计算机模型模仿真实系统行为的方法。

它可以帮助我们设计和开发各种产品,以及提供更好的测试和分析策略。

仿真技术广泛应用于如航空航天、医疗、物流、自动化、能源和通信等领域。

而在通信电子中,仿真技术则更加重要。

因为通信电子涉及的技术、系统和设备都非常复杂,光从理论角度理解是不够的。

在实践中,模拟实验也有很多困难。

因此,仿真技术为我们提供了更为便捷和经济的实验方法,以确保产品和系统的准确性和稳定性,根据实际情况进行模型改进。

二、通信电子中的系统仿真技术应用(一)通信系统仿真通信系统仿真允许我们评估通信系统性能,比如带宽、振幅、信噪比、误码率等。

使用仿真技术可以模拟系统中的各个组件 (例如反射器, 滤波器, 放大器, 电缆等) 的特性,以确保其符合实际应用的需求。

通信系统仿真可以帮助我们评估不同的系统设计选项,指导系统优化。

仿真时,我们可以测试涉及的各种因素和因素的组合,以生成系统模型,从而得出最合适的解决方案。

另外,我们也可以评估某个特定系统的容错性,并应用故障模拟技术,确保系统设计的可靠性。

(二)天线系统仿真天线系统仿真是为了评估天线特性的模拟,比如增益、辐射图案、以及电磁波辐射效应等。

将仿真结果与实验结果进行比较,可以进一步优化天线系统设计,提高其性能。

仿真技术可以帮助我们设计各种类型的天线,比如:方向性天线、扫描天线、多波束系统等等。

(三)整合和验证在仿真系统和硬件之间进行整合和验证是不可或缺的一环。

这个过程允许我们评估系统和硬件之间的所有相互作用和接口问题,并证明系统和硬件是按照设计要求运行的。

通信中的系统级仿真

以六边形的左下角的点为左边原点,建立直角坐标系,设小区的半径为R, 则在改造的长方形中,横坐标x和纵坐标 y 的取值范围分别为[-0.5R,2.5R] 和[0,0.866R]。令用户数目为N,生成在长方形内均匀分布的用户:

C = = k arg max ( t ) , i 1, 2, , K I i

K为总用户数,C/I为用户的载干比,k为所调度的用户。 最大载干比配合自适应编码调制,可以很好的利用信道的反馈信息,实现 系统的吞吐量最大化,而且实现算法简单。但是它完全没有考虑用户之间 的公平性,当某个用户的信道条件一直不好时将不会被调度,会出现用户 “饿死”的现象。因此,从占用资源的角度讲,最大载干比调度是最不公 平的,它是吞吐量性能的上界和公平性的下界。

20

调度模型

轮询调度(RR): 轮询调度又称为循环调度算法,被认为是最公平的调度算法。这种算法中, 每个用户被循环的调度来使用系统资源,从概率意义上讲,每个用户以同 等的概率使用系统资源,如时隙和功率。 假设有两个用户UE1 和UE2,两个用户都有足够多的数据要传输,轮询调 度可以用下图表示。

B=30-25log10(地面建筑物覆盖率) a(hr)=(1.1log10f-0.7)hr-(1.56log10f-0.8)hr CCIR模型和Hata模型的适应条件: 150 MHz≤f≤1500 MHz 1 km≤d≤20 km 30 m≤ht≤200 m 1 m≤hr≤10 m CCIR和Hata模型适用的天线高度和终端高度适 合小型城市、乡镇区域的 地物情况,因此常用于小型城市及乡镇区域1.5G以下的无线网络规划。

基于MATLAB通信系统的设计仿真

基于MATLAB通信系统的设计仿真概述:通信系统是实现信息传输的关键技术,其中设计和仿真是通信系统的重要环节。

本文将介绍如何基于MATLAB进行通信系统的设计和仿真,并以调制和解调为例进行说明。

通信系统的设计和仿真步骤:1.确定系统需求:首先确定通信系统的需求,包括传输速率、距离、信噪比等参数。

2.选择调制方式:根据系统需求和传输介质的特性,选择合适的调制方式,如BPSK、QPSK、16-QAM等。

3.生成基带信号:根据调制方式和传输要求,使用MATLAB生成相应的基带信号。

4.添加调制信号:将基带信号进行调制,生成调制信号,如使用频率调制、相位调制等技术。

5.添加噪声:为了模拟真实通信环境,需要在调制信号中加入噪声信号,可以使用MATLAB提供的噪声函数。

6.解调信号:使用相应的解调技术对接收到的信号进行解调,恢复原始基带信号。

7.评估系统性能:比较解调后的基带信号与原始信号,评估系统的性能,如误码率、误符号率等。

调制与解调的MATLAB实例:以BPSK调制为例,假设系统需求为传输速率2Mbps,信噪比为20dB。

1.生成基带信号:```matlabfs = 10e6; % 采样率N=1000;%生成1000个符号bits = randi([0 1],1,N); % 生成随机的二进制信号Ts = 1/fs; % 采样周期t=0:Ts:(N-1)*Ts;%时间序列baseband_signal = bits.*2-1; % 将0或1转换为-1或1```2.添加调制信号:```matlabfc = 1e6; % 载波频率modulated_signal = baseband_signal .* cos(2*pi*fc*t); % 调制信号```3.添加噪声:```matlabEbNo=10^(20/10);%信噪比,20dB转为线性值N0=1/(2*EbNo);%噪声功率,信噪比为能量比noise = sqrt(N0/2) * randn(size(t)); % 产生高斯白噪声received_signal = modulated_signal + noise; % 加噪声```4.解调信号:```matlabdemodulated_signal = received_signal .* cos(2*pi*fc*t); % 解调信号```5.评估系统性能:```matlabest_baseband_signal = sum(demodulated_signal) > 0; % 判断信号正负,得到解调后的二进制信号error_bits = sum(bits ~= est_baseband_signal); % 计算误码个数BER = error_bits / N; % 误码率```通过调整系统参数,可以进行更详细的仿真和性能评估。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

大学本科实验报告课程名称:通信系统仿真实践学院(系):电子信息与电气工程学部专业:电子信息工程班级:学号:学生姓名:2011年11 月29日实验项目列表大学实验报告学院(系):专业:电子信息工程班级:姓名:学号:组:___实验时间:2011.10.17 实验室:C223 实验台:指导教师签字:成绩:实验一简单基带传输系统一、实验目的和要求掌握观察系统时域波形,特别是眼图的操作方法。

二、实验原理和内容【实验原理】简单的基带传输系统原理框图如图1所示,该系统并不是无码间干扰设计的,为使基带信号能量更为集中,形成滤波器采用高斯滤波器。

图1. 简单基带传输系统组成框图【实验内容】构造一个简单示意性基带传输系统。

以双极性 PN 码发生器模拟一个数据信源,码速率为100bit/s,低通型信道噪声为加性高斯噪声(标准差=0.3v)。

要求:观测接收输入和滤波输出的时域波形;观测接收滤波器输出的眼图。

三、主要仪器设备PC机四、实验步骤与操作方法第1 步:进入SystemView 系统视窗,设置“时间窗”参数如下:①运行时间:Start Time: 0 秒; Stop Time: 0.5 秒;②采样频率:Sample Rate:10000Hz。

第2 步:调用图符块创建如图1 所示的仿真分析系统:图1. 创建的简单基带传输仿真分析系统其中,Token1 为高斯脉冲形成滤波器;Token4 为高斯噪声产生器,设标准偏差StdDeviation=0.3v,均值Mean=0v;Token5 为模拟低通滤波器,来自选操作库中的“LinearSys”图符按钮,在设置参数时,将出现一个设置对话框,在“Design”栏中单击Analog…按钮,进一步单击“Filter PassBand”栏中Lowpass 按钮,选择Butterworth 型滤波器,设置滤波器极点数目:No.of Poles=5(5 阶),设置滤波器截止频率:LoCuttoff=200 Hz。

第3 步:单击运行按钮,运算结束后按“分析窗”按钮,进入分析窗后,单击“绘制新图”按钮,则Sink10~Sink13 显示活动窗口分别显示出“PN 码输出”、“信道输入”、“信道输出”和“判决比较输出”时域波形,如图1 所示:第 4 步:观察信源PN 码和波形形成输出的功率谱。

通过两个信号的功率谱可以看出,波形形成后的信号功率谱主要集中在低频端,能量相对集中,而PN 码的功率谱主瓣外的分量较大。

在分析窗下,单击信宿计算器按钮,在出现的“System Sink Calculator”对话框中单击Spectrum 按钮,分别得到Sink10 和Sink11 的功率谱窗口后,可将这两个功率谱合成在同一个窗口中进行对比,具体操作为:在“System Sink Calculator”对话框中单击Operators 按钮和Overlay Plots 按钮,在右侧窗口内压住左键选中“w4:PowerSpectrum of Sink10”和“w5:Power Spectrum of Sink11”信息条,使之变成反白显示,最后单击OK 按钮即可显示出对比功率谱,如图2 所示。

图2. PN 码和波形形成器输出功率谱对比第5 步:观察信道输入和输出信号眼图。

眼图是衡量基带传输系统性能的重要实验手段。

当屏幕上出现波形显示活动窗口(w1:Sink11 和w2:Sink12)后,单击“System SinkCalculator”对话框中的Style 和Time Slice 按钮,设置好“Start Time[sec]”和“Length[sec]”栏内参数后单击该对话框内的OK 按钮即可,两个眼图如图3 所示。

图3. 信道输入和输出信号眼图从上述眼图可以看出,经高斯滤波器形成处理后的基带信号远比PN 码信号平滑,信号能量主要集中于10 倍码率以内,经低通型信道后信号能量损失相对小一些。

由于信道的不理想和叠加噪声的影响,信道输出眼图将比输入的差些,改变信道特性和噪声强度,眼图会发生明显变化,甚至产生明显的接收误码。

五、实验数据记录和处理六、实验结果与分析高斯噪声:0.3V时,分析结果为:高斯噪声:0.5V时,分析结果为:七、讨论、建议、质疑本次实验中主要掌握systemview软件的使用方法,虽然简单,但是分析很准确,但是如果对系统不了解,也会无从下手。

在掌握了所要仿真系统的结构和工作原理再进行系统仿真才会事半功倍。

实验二差分编码、译码器一、实验目的和要求通过分析理解差分编码/译码的基本工作原理。

二、实验原理和内容【实验原理】二进制差分编码器和译码器组成如图1 所示,其中:{an}为二进制绝对码序列,{dn}为差分编码序列,D 触发器用于将序列延迟一个码元间隔,在SystemView 中此延迟环节一般可不使用D 触发器,而是使用操作库中的“延迟图符块”。

图1. 差分编码、译码器框图【实验内容】创建一对二进制差分编码/译码器,以 PN 码作为二进制绝对码,码速率Rb=100bit/s。

分别观测绝对码序列、差分编码序列、差分译码序列,并观察差分编码是如何克服绝对码全部反相的,以便为分析2DPSK 原理做铺垫。

三、主要仪器设备PC机四、实验步骤与操作方法第1 步:进入SystemView 系统视窗,设置“时间窗”参数如下:①运行时间:Sta1rt Time: 0 秒;Stop Time: 0.3 秒;②采样频率:Sample Rate=10000Hz。

第2 步:首先创建如图1 所示的仿真分析系统,主要图符块参数如便笺所示。

其中,Token1 和Token2都是来自操作库的“数字采样延迟块”,由于系统的采样频率为10000Hz,绝对码时钟频率为100Hz,故延迟一个码元间隔需100 个系统采样时钟。

图1. 差分编码/译码器仿真分析系统第3 步:观察编、译码结果。

在分析窗下,差分编码器输入(绝对码)、差分编码输出及差分译码输出序列分别由Sink3、4、9 给出。

第4 步:得到仿真结果后,将差分编码器与差分译码器之间插入一个非门(NOT),再看仿真结果。

仿真分析系统如图2所示。

可以观察到,差分编码和译码方式可以克服编码输出序列的全反相,差分译码序列与不反相的相同。

充分理解了这一原理,就能很快理解2DPSK 是如何解决载波180°相位模糊问题,同时将有助于读者自行创建包含差分编码与译码的2DPSK 系统。

图2. 差分编码/译码器插入非门的仿真分析系统五、实验数据记录和处理图1的仿真结果如下图所示。

三个窗口分别是差分编码器输入(绝对码)、差分编码输出及差分译码输出序列。

六、实验结果与分析由分析结果可知:Sink3—输入为二进制的绝对码,码速率为100bit/s。

101101000110100010010100100011Sink4—差分编码输出110110000100111100011000111101Sink9—差分译码输出,可见译码结果与输入绝对码相同将差分编码器与差分译码器之间插入一个非门(NOT),再仿真得到下图所示仿真结果。

差分编码和差分译码之间插入一个非门,由结果可见,差分编码和差分译码方式可以克服编码输出序列的全反相,搽粉译码序列与不反相的相同。

可以解决2dpsk的载波180度相位模糊问题。

Sink9—差分译码输出,可见译码结果与输入绝对码相同。

七、讨论、建议、质疑本次实验比实验一简单一些,由于只是仿真出时域的波形,所以做起来要快一些,但是这次实验中要将各个token的功能弄明白也是需要好好预习的,这样做实验时才会比较顺利。

由于本实验可以根据结果快速判断实验是否正确,所以对电路进行修改和仿真都很方便。

实验三二进制相移键控系统一、实验目的和要求分析二进制移相键控系统的工作原理,特别注意2DPSK 系统是如何解决同步载波180°相位模糊问题的。

一、实验原理和内容【实验原理】相干接收 2PSK 系统组成如图1 所示:图1. 2PSK 系统组成对2PSK 信号相干接收的前提是首先进行载波提取,可采用平方环或科斯塔斯环来实现。

为分析方便起见,在本实验中可直接在收端设置一个与发送端同步的本地载波源。

另外,本实验中暂不考虑位同步提取问题。

2DPSK 系统组成原理如图2 所示,系统中差分编、译码器是用来克服2PSK 系统中接收提取载波的180°相位模糊度。

图2. 2DPSK 系统组成【实验内容】创建2PSK 和2DPSK 系统。

三、主要仪器设备PC机四、实验步骤与操作方法相干接收2PSK 系统1、创建仿真系统如图1所示。

图1. 2PSK 仿真系统设置系统运行时间:0-0.3 秒;采样频率10000Hz。

PN 码速率为100Hz,载波频率为1000Hz;收、发正弦载波源的相位均为0。

其中,Token13 为双极性PN 码源; Token2 和Token4是彼此同步的载波源;Token10 为过零比较器a>b 模式);Token11 是幅度和频率均为0 的正弦源,作为过零门限电平(比较器b 输入);Token9 为3 阶100Hz 截止频率的低通滤波器(比较器a 输入)。

2、分析内容要求①观察Token1、6、12、14 处的时域波形,看解调是否正确?观察Token11 处的功率谱;②在2PSK 系统中,接收提取的载波存在180°相位模糊度,这是载波提取电路存在的固有问题,一旦接收端提取的载波与发送端调制载波倒相,解调出的码序列将全部倒相。

重新设置接收载波源的参数,将其中的相位设为180°,运行后再观察解调的结果。

差分相干接收2PSK 系统1、创建仿真系统如图2所示。

图2. 2DPSK 系统的仿真系统方案其中,Token15、16、18 组成差分编码器,Token23、24、25 为差分译码器,设置系统运行时间:0-0.3 秒、采样速率为10000Hz。

其中,Token13为单极性PN 码源;Token15、23 为采样器(采样速率为100Hz);Token19、26为保持器;Token16为放大器(Gain=1)、Token19 为数字延迟器(延迟1 个Sample);Token21、10、27 为比较器(a>b 模式), Token22、28 设为0V 直流电平(Token4 的输入b),Token25设为0V 直流电平(Token24 的输入b)。

Token4、17 输出为双极性码、Token21 输出为单极性码;Token3、8 为彼此同步的载波源(Amp=1V、Freq=1000Hz、Phase = 0°);Token5、7 组成加性高斯噪声信道;Token1、20、6、12、14、29 为信宿接收分析器。