清华模拟IC集成电路设计实践第十二讲

电子设计中的模拟IC设计

电子设计中的模拟IC设计在电子设计中,模拟集成电路设计是一个非常重要的领域,它涉及到模拟信号的处理和传输,通常用于处理声音、图像和其他形式的连续信号。

模拟IC设计的目标是设计出性能稳定、功耗低、成本合理的集成电路。

模拟IC设计的第一步是确定设计参数和规格。

在开始设计之前,需要明确信号的频率范围、幅度范围、输出电流和电压要求等。

这些参数将直接影响到后续设计的方向和结果。

接下来是电路拓扑设计。

根据设计参数和规格,选择合适的电路结构和拓扑。

常用的模拟IC电路包括放大器、滤波器、混频器等。

在确定了电路拓扑之后,可以开始进行具体的电路设计。

在模拟IC设计过程中,模拟电路设计工程师通常会使用一些仿真工具来验证电路设计的性能。

通过仿真可以有效的评估电路的稳定性、频率响应、阻抗匹配等重要指标,从而及时发现问题并进行调整优化。

另一个重要的环节是布局与布线设计。

良好的电路布局和布线对于模拟IC的性能至关重要。

合理的布局可以减小信号传输路径,降低电路的噪声和干扰。

同时,优秀的布局还能有效减小电路的面积和功耗,提高集成度和整体性能。

模拟IC设计的最后一步是验证和调试。

设计完成后,需要进行严格的验证测试,确保电路能够满足设计要求。

如果出现问题,需要及时调试和优化。

通过不断地验证和调试,最终设计出符合需求的模拟IC电路。

总的来说,模拟IC设计是一个复杂而精密的过程,需要设计工程师具备深厚的电路知识和丰富的实践经验。

只有通过不懈的努力和精心的设计,才能设计出性能稳定、高效能的模拟集成电路。

希望以上内容能帮助您更好地了解电子设计中的模拟IC设计。

《集成电路设计实践》第一讲_A

课程进度安排(续二)

第9周:Cell-based设计方法及工具 3.1 Cell-based设计流程介绍 3.2 Verilog简介 第10周: 3.3 电路综合 第11周: 3.4 布局布线 3.5 DRC与LVS

课程进度安排(续三)

第12周:项目设计——CYCLIC ADC的设计 4.1 CYCLIC ADC原理 4.2 CYCLIC ADC电路设计 4.3 版图设计考虑 4.4 ADC性能仿真 4.5 设计报告要求 第13周:深亚微米工艺下的集成电路设计方法 5.1 按比例缩小原理 5.2 短沟道效应 5.3 深亚微米工艺下的设计讨论 5.4 SOC设计 第14~16周:项目设计与辅导

课程进度安排(续一)

第5周:Full-custom设计方法及工具 2.1 Full-custom设计流程介绍 2.2 原理图输入与电路网表导出 第6周: 2.3 HSPICE电路仿真 第7周: 2.4 版图编辑 第8周: 2.5 设计规则检查(DRC)与版图电路比对(LVS) 2.6 版图参数提取和后仿真 2.7 分层设计讨论

一. 集成电路设计基础

1.2 版图的基本概念

版图结构

集成电路加工的平面工艺

制 版 加 工

芯片的剖面结构

从平面工艺到立体结 构,需多层掩膜版,故 构,需多层掩膜版,故 版图是分层次的,由多 层图形叠加而成!

一个简单的例子

Vdd 版 图 in metal1

N+ 剖 N-阱 面 N-阱 图 P-substrate N+ P+

逆向电路提取 逆向电路提取

解剖照相 拼图 电路提取 分析与仿真

集成电路分类

集 成 电 路 按用途 数 字 集 成 电 路 模 拟 集 成 电 路 数 模 混 合 集 成 电 路 按集成规模 ULSI ULSI GLSI GLSI 大 规 模 超 大 规 模 集 成 电 路 按制作工艺 GaAs GaAs MOS MOS Bipolar Bipolar 集 成 电 路 集 成 电 路 按生产形式 标 专 准 用 通 集 用 成 集 电 成 路 电 路 ASIC ASIC

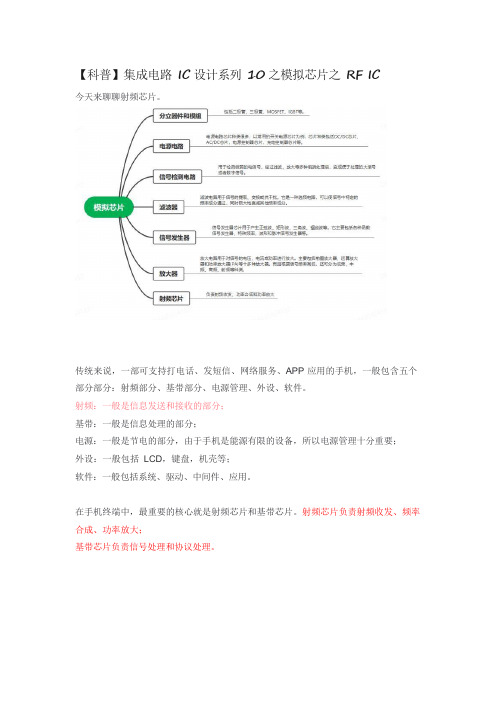

【科普】集成电路IC设计系列10之模拟芯片之RF IC

【科普】集成电路IC 设计系列10 之模拟芯片之RF IC今天来聊聊射频芯片。

传统来说,一部可支持打电话、发短信、网络服务、APP 应用的手机,一般包含五个部分部分:射频部分、基带部分、电源管理、外设、软件。

射频:一般是信息发送和接收的部分;基带:一般是信息处理的部分;电源:一般是节电的部分,由于手机是能源有限的设备,所以电源管理十分重要;外设:一般包括LCD,键盘,机壳等;软件:一般包括系统、驱动、中间件、应用。

在手机终端中,最重要的核心就是射频芯片和基带芯片。

射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。

RF 是Radio Frequency 的缩写,指无线电频率。

频率范围在300KHz~300GHz 之间。

RF 最早的应用是Radio—无线电广播(FM /AM)。

而射频芯片是将无线电信号通信转换成一定的无线电信号波形,通过天线谐振发送出去的电子元件。

在整个射频芯片赛道中,射频前端行业规模巨大,市场增速较快。

射频前端(Radio Frequency Front-End)在通讯系统中天线和基带电路之间的部分,包括发射通路和接收通路,一般由射频功率放大器、射频滤波器、双工器、射频开关、射频低噪声放大器等共同组成。

射频前端行业是我国集成电路行业中对外依存度较高的细分领域之一,特别是在5G、高集成度射频前端模组等前沿市场,据Yole 的数据,2022 年全球射频前端市场由Broadcom(19%)、Qualcomm(17%)、Qorvo(15%)、Skyworks (15%)和村田(14%)等美系和日系厂商占据主导地位,这些射频巨头通过不断地收购整合,不断补强射频前端技术能力。

这五大射频前端厂商合计占据市场约80%的份额,也占据我国大部分的市场份额。

射频前端结构射频前端是无线通信系统构架四大部分(天线、射频前端、射频收发模块以及基带信号)之一,主要功能是将数字信号向无线射频信号转化。

《模拟集成电路设计》教学大纲

《模拟集成电路设计》课程教学大纲一、课程基本信息1、课程编码:2、课程名称(中/英文):模拟集成电路设计/ Design of Analog integrated Circuits3、学时/学分:56学时/3.5学分4、先修课程:电路基础、信号与系统、半导体物理与器件、微电子制造工艺5、开课单位:微电子学院6、开课学期(春/秋/春、秋):秋7、课程类别:专业核心课程8、课程简介(中/英文):本课程为微电子专业的必修课,专业核心课程,是集成电路设计方向最核心的专业课程之一。

本课程主要介绍典型模拟CMOS集成电路的工作原理、设计方法和设计流程、仿真分析方法,以及模拟CMOS集成电路的最新研发动态。

通过该课程的学习,将为学生今后从事集成电路设计奠定坚实的理论基础。

9、教材及教学参考书:教材:《模拟集成电路设计》,魏廷存,等编著教学参考书:1)《模拟CMOS集成电路设计》(第2版).2)《CMOS模拟集成电路设计》二、课程教学目标本课程为微电子专业的必修课,专业核心课程,是集成电路设计方向最核心的专业课程之一。

通过该课程的学习,将为学生今后从事集成电路设计奠定坚实的理论基础。

本课程主要介绍典型模拟CMOS集成电路的工作原理、设计方法和设计流程、仿真分析方法,以及模拟CMOS模拟集成电路的最新研发动态。

主要内容有:1)模拟CMOS集成电路的发展历史及趋势、功能及应用领域、设计流程以及仿真分析方法;2)CMOS元器件的工作原理及其各种等效数学模型(低频、高频、噪声等);3)针对典型模拟电路模块,包括电流镜、各种单级放大器、运算放大器、比较器、基准电压与电流产生电路、时钟信号产生电路、ADC与DAC电路等,重点介绍其工作原理、性能分析(直流/交流/瞬态/噪声/鲁棒性等特性分析)和仿真方法以及电路设计方法;4)介绍模拟CMOS集成电路设计领域的最新研究成果,包括低功耗、低噪声、低电压模拟CMOS集成电路设计技术。

集成电路版图设计基础第五章:模拟IC版图

电源分布是版图设计中非常重要 的一个环节,它涉及到如何合理 地分布电源网络,以保证电路的

稳定性和性能。

常用的电源分布技术包括电源网 格、电源岛和电源总线等,这些 技术可以有效减小电源网络的阻

抗和减小电压降。

热设计

在模拟IC版图设计中,热设计 是一个不可忽视的环节,它涉 及到如何有效地散热和防止热 失效。

验证与测试

功能验证

通过仿真测试或实际测试,验证版图实现的电路功能是 否正确。

时序验证

检查电路时序是否满足设计要求,确保电路正常工作。

ABCD

性能测试

对版图实现的电路进行性能测试,包括参数、频率、功 耗等方面的测试。

可测性、可维护性和可靠性测试

对版图进行测试,验证其在测试、维修和可靠性方面的 表现是否符合要求。

02

模拟IC版图设计流程

电路设计

确定设计目标

根据项目需求,明确电路 的功能、性能指标和限制 条件。

选择合适的工艺

根据电路需求,选择合适 的工艺制程,确保电路性 能和可靠性。

电路原理图设计

使用电路设计软件,根据 电路功能和性能要求,设 计电路原理图。

参数提取与仿真验证

对电路原理图进行仿真验 证,提取关键参数,确保 电路性能满足设计要求。

版图布局

确定版图布局方案

模块划分与放置

根据电路原理图和工艺制程要求,确定合 理的版图布局方案。

将电路原理图划分为若干个模块,合理放 置在版图上,确保模块间的连接关系清晰 、简洁。

电源与地线设计

考虑可测性、可维护性和可靠性

合理规划电源和地线的分布,降低电源和 地线阻抗,提高电路性能。

在版图布局时,应考虑测试、维修和可靠 性等方面的需求。

清华模电华成英PPT课件

清华大学 华成英

.

1

华成英 hchya@

绪论

一、电子技术的发展 二、模拟信号与模拟电路 三、电子信息系统的组成 四、模拟电子技术基础课的特点 五、如何学习这门课程 六、课程的目的 七、考查方法

.

2

华成英 hchya@

一、电子技术的发展

结电容: Cj Cb Cd

结电容不是常量!若PN结外加电压频率高到一定程度, 则失去单向导电性!

.

24

华成英 hchya@

问题

• 为什么将自然界导电性能中等的半导体材料制 成本征半导体,导电性能极差,又将其掺杂, 改善导电性能?

• 为什么半导体器件的温度稳定性差?是多子还 是少子是影响温度稳定性的主要因素?

PN 结的单向导电性

PN结加正向电压导通: 耗尽层变窄,扩散运动加

剧,由于外电源的作用,形 成扩散电流,PN结处于导通 状态。

P必N要结吗加?反向电压截止:

耗尽层变宽,阻止扩散运动,

有利于漂移运动,形成漂移电

流。由于电流很小,故可近似

认为其截止。

.

23

华成英 hchya@

1. 单向导电性

正向特性为 指数曲线

u

i IS(eUT 1)

u

若正u 向 U 电 T,压 i则 ISeUT

若反向 u电 UT, 压i则 IS

2. 伏安特性受温度影响 反向特性为横轴的平行线

T(℃)↑→在电流不变情况下管压降u↓ →反向饱和电流IS↑,U(BR) ↓ 增大1倍/10℃

T(℃)↑→正向特性左移. ,反向特性下移

PN 结的形成

由于扩散运动使P区与N区的交界面缺少多数载流子,形成内 电场,从而阻止扩散运动的进行。内电场使空穴从N区向P区、 自由电子从P区向N 区运动。

现代模拟集成电路设计

《现代模拟集成电路设计》是2024年清华大学出版社出版的图书,作者是孙楠、刘佳欣、揭路。

本书围绕先进工艺节点,基于跨导效率的设计方法介绍现代模拟集成电路的分析与设计方法。

全书大体上分为三部分: 第一部分(第1~7章)对模拟集成电路中的基本元件晶体管,以及基本的分析与设计方法进行介绍,包括晶体管的长沟道模型与小信号模型、晶体管的基本电路结构、晶体管的性能指标、基于跨导效率的模拟电路设计方法、模拟电路的带宽分析方法、模拟电路中的噪声等。

第二部分(第8~10章)介绍模拟电路设计中常见的一些问题与设计技巧,如器件偏差、差分结构、负反馈技术等,并引入模拟电路中最常见的电路结构,即运算放大器与开关电容电路。

第三部分(第11~14章)详细介绍了运算放大器的分析与设计方法,并提供完整的运算放大器设计实例作为参考。

此外,第15章和第16章还介绍了基准源电路以及集成电路的工艺演进。

清华大学《数字集成电路设计》周润德 第1章(课件)绪论

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第1章第3页

评分规则(Grading Policy)

(1)作业: 20%

第 4 周起,每周一次,一周完成,上课时交,迟交无效

(2)期中考试:20%

100

P6 Pentium ® proc

10

8086 286

486

386

8085

1

8080

8008

4004

0.1 1971

1974

1978 1985 年

1992

最先进微处理器的功耗持续增长

2000

资料来源: Intel

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 21 页

2004-9-15

清华大学微电子所《数字大规模集成电路》 周润德

第 1 章 第 17 页

微处理器单个芯片尺寸的增长趋势

100

单个芯片尺寸 (mm)

P6

10

486 Pentium ® proc 386

8080

286 8086

8085

8008

4004

资料来源: Intel

1 1970

1980

1990 年

每1.96年翻一倍!

Pentium® III

Pentium® II

Pentium® Pro

Pentium® i486

i386

80286

10

1 1975

8086

1980

1985 1990

1995

2000

资料来源: Intel

《模拟集成电路设计》实验指导2

3

copy right @mwy;

Email: mwy@

一些操作 Tips: 可以将输入输出曲线分开进行对比。横向拉开,从而得到更细致的图形。

②可以放置 marker 获得某一点的坐标。方法是点击 marker->place->trace marker (vert marker, horiz marker)。然后点击图形上的某一点,便可显示该点的坐标。 7、静态工作点参数的查看。 DC 分析之后,在 ADE 窗口选择 Tools-Results Browser(这是结果浏览窗口),弹出直流分 析结果的窗口。依次选择 psf-dcOpInfo-info-M0(M0 的静态工作点)。可以找到 M0 各个参数 值。选中某一项参数点击右键,选择 Tab,可以查看此项参数值。其他管子的参数亦同样查 看。 例如,①在本例中,我们可以查看 M2 管(NMOS)的静态跨导 gm,漏源间的跨导 gds(输出 电阻 ro=1/gds), 以及 M0 管(PMOS)的漏源跨导 gds, 从而能够手动计算增益。 例如, 当 W=2μm, -4 -5 -5 L=0.18μm 时,可以查看得 gmN=7.33*10 ;gdsN=2.124*10 ;gdsP=1.844*10 。根据增益公式

9、利用计算器(或结合 outputs->setup)获得自己想要的参数值。 计算器功能非常强大,也是我们常用的工具。在 ADE 窗口点击 tools->calculator,可以 调出计算器。也可以在某个波形显示页面用相同的办法调出。计算器显示页面如下: 选择一种分析模式,可以计算的数 据类型会跟随改变。主要的数据类型有:

2 copy right @mwy; Email: mwy@

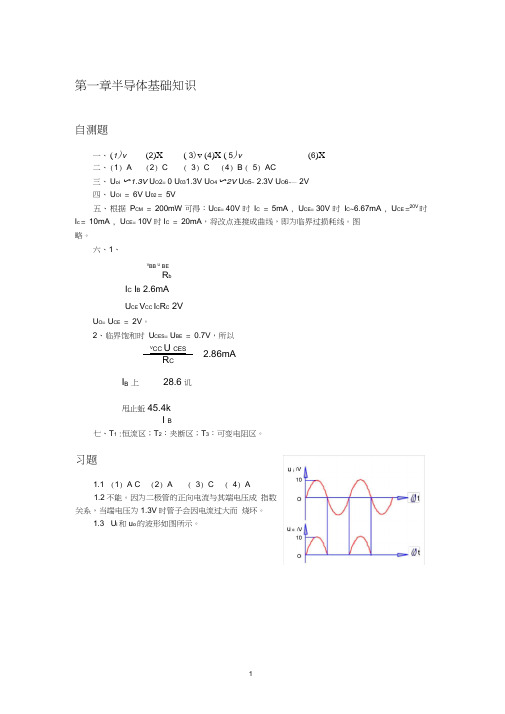

清华大学《模拟电子技术基础》习题解答与答案

第一章半导体基础知识自测题一、 (1)v (2)X( 3)v (4)X ( 5)v(6)X二、 (1) A(2) C( 3) C(4) B ( 5) AC三、 U oi 〜1.3V U O 2= 0 U 031.3V U O4〜2V U O 5~ 2.3V U O 6~— 2V 四、 U OI = 6V U 02 = 5V五、 根据 P CM = 200mW 可得:U CE = 40V 时 I C = 5mA , U CE = 30V 时 I C ~6.67mA , U CE =20V 时I c = 10mA , U CE = 10V 时I C = 20mA ,将改点连接成曲线,即为临界过损耗线。

图 略。

六、1、VBB U BER bI C I B 2.6mAU CE V CC I C R C 2VU O = U CE = 2V 。

2、临界饱和时 U CES = U BE = 0.7V ,所以I B 上28.6讥甩止蚯45.4kI B七、T 1 :恒流区;T 2:夹断区;T 3:可变电阻区。

习题1.1 (1) A C(2) A( 3) C( 4) A1.2不能。

因为二极管的正向电流与其端电压成 指数关系,当端电压为1.3V 时管子会因电流过大而 烧坏。

1.3 U i 和u o 的波形如图所示。

V CCU CESC 2.86mA1.4 u i 和u o 的波形如图所示。

1.5 U o 的波形如图所示。

1.6 I D =( V — U D ) /R =2.6mA ,U T /I D = 10Q, l d = U i /r D ~ 1mA 。

1.7 (1 )两只稳压管串联时可得1.4V 、6.7V 、8.7V 和14V 等四种稳压值。

(2)两只稳压管并联时可得0.7V 和6V 等两种稳压值。

1.8 I ZM = P ZM /U Z = 25mA , R = U Z /I DZ = 0.24 〜1.2k Q o1.9(1 )当U I = 10V 时,若U O = U Z = 6V ,则稳压管的电流为 4mA ,小于其最小稳定 电流,所以稳压管未击穿。

1.2基本门电路设计-版图绘制

集成电路设计实习Integrated Circuits Design LabsI t t d Ci it D i L b单元实验一(第二次课)基本门电路设计--版图设计2006-2007 Institute of Microelectronics Peking University实验目的及时间安排z内容一:z掌握基本门电路的版图设计z熟悉Cadence版图设计、版图验证工具的使用z内容二:z完成2与非门的设计,包括原理图输入、电路仿真、版图设计、版图验证Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page21. 版图图层z本课程中使用CSMC双硅三铝混合信号工艺,主要的设计层包括z TB:tub,n阱,作为pmos器件衬底z TO:Thin Oxide,有源区,作为mos的源漏区Thin Oxidez GT:gate,多晶硅1,作为mos栅极z SP:P+注入区z SN:N+注入区z W1:接触孔,金属1到多晶硅和有源区的接触孔z A1:铝1,第一层金属z W2:通孔1,金属1和金属2的接触孔z A2:铝2,第二层金属z W3:通孔2,金属2和金属3的接触孔z CP:bond pad,pad开孔z IM:第二层多晶硅电阻阻挡层z PC:poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅l Cz PT:p tub,p阱,作为nmos器件衬底z详细的工艺信息请参考设计规则(在CSMC05MS/docs目录下)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page32. 由电路图产生初始版图z VirtuosoXL为cadence的连接关系驱动定制版图设计工具z启动Virtuoso XLz第一步:打开inv的schematic viewz第二步:Schematic窗口:Tools->Design Synthesis->Layout XLz Create Newz OKz OK,弹出Virtuoso XL窗口Vi t XLz在Virtuoso XL窗口中,Design->GenFrom Source Layout,弹出yGeneration Options对话框(下页)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page4z Layout Generation部分z选中I/O Pins,Instances,Transistor Chaining,TransistorTransistor Chaining TransistorFoldingz I/O Pins部分z DefaultsD f lz Layer/Master选择A1层z选中Createz Applyz Pin Label Shapez点击Pin Label Options,在弹出的对话框中选中Layer Name后面的SameLayer Name SameAs Pinz点击OK后出现下页图,按照前面的设计要求进行版图设计Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page5Inv的版图设计z在此基础上添加电源线vdd,地线gnd(可参考下页快捷键)z按照电路图用相应的层把mos管的各端连线画出来z把vdd和N阱相连(用CSMC05MS库中的ntap),把gnd和衬底相连(用tCSMC05MS库中的ptap )z按照标准单元的画法,单元有统一的高度(这里是24um),统一的vdd和gnd走线宽度(2um)和位置(vdd走线在单元的最上端,gnd在最下端)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page6Virtuoso Layout Editor常用操作z Instance(添加元件,快捷键i)g(画矩形,快捷键),yg(画多边形,快捷键z Rectangle r PolygonP),Path(画长连线,快捷键p)pyz Copy(c),Move(m),Stretch(s)z Merge(把多个相互重叠的图形合并成一块,M)Create Ruler Clear All Rulersz Create Ruler(添加标尺,快捷键k),Clear All Rulers(K)z Descend(X),Return(B)z Zoom in by 2(^z),Zoom out by 2(Z),Fit(f)z Option->Display(e)中可以设置一些参数z在命令过程中可以利用F3键打开该命令相关的选项,帮助我们调整命令参数(很有帮助!)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page73. 版图的验证DRCz在Layout窗口中,Verify->DRCz在Rules File一项中,填入divaDRC.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OKz在CIW中可以看到DRC的结果,按说明改掉图中的error,直到Total errors found为0Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page84. 版图的器件提取和LVS检查z在做LVS之前,要把版图中的管子信息和pin的信息提取出来,这就是Extractz在Layout窗口中,Verify->Extractz Rules File一项中,填入在Rules FiledivaEXT.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OK在中可以看到是否成z CIW Extract功,一般情况下Total errorsfound都为0z执行的结果是cell inv产生了一个extracted viewInstitute of Microelectronics, Peking University集成电路设计实习-单元实验一Page9LVSz在Layout窗口中,Verify->LVSz Library和Cell中分别填入库名字design03和单元名字inv,View中对应于schematic的填入schematic,对应于extracted的填入extracted(这些信息也可以通过Browse或者BSel by Cursor得到)在一项中,填入z Rules FiledivaLVS.rul,若该文件不在启动目录下,还应写上路径z点击Run,运行几秒后会出现“Analysis Job Succeeded”的提示z点击Output,观看结果。

清华大学 集成电路设计实践 ic1-background

集成电路的进展内容简介 集成电路的应用领域 集成电路的制造过程 制 从CPU的发展看IC的进展 从行业的发展看IC C的进展 从ISSCC SSCC看IC C的发展方向2010-3-2清华大学微电子学研究所2集成电路的应用领域Communications Computer & Storage gWireless Cellular Basestations Wireless LANNetworking Switches RoutersWireline Optical Metro AccessComputer Servers Mainframe WorkstationsStorage RAID SANOffice AutomationCopiers Printers MFPConsumerIndustrialEntertainment Broadband Audio/Video Video DisplayBroadcast Studio Satellite BroadcastingInstrumentation st u e tat o Medical Test Equipment ManufacturingSecurity/ Energy M E Mgmt. tAuto Navigation EntertainmentMilitary ta y Secure Comm. Radar Guidance & ControlCard Readers Control Systems ATM3中国大陆地区2008 年集成电路设计产 业的有关情况根据商务部统计信息: 2007年集成电路及微电子组件进口金 额高达1277亿美元;是原油进口额的1.6 倍2008年1-10月 集成电路进口:1119亿美元 集成电路进 成品油:278亿美元 原油:1167亿美元 特殊时间:石油价格飞涨2008年大陆地区集成电路设计全行 业销售总额为345亿元,同比增长 23.5%需求大、本地企业小、不断发展集成电路的制造过程-晶圆Single dieWafer6” (15cm) 17000 mm2 8” (20cm) 31000 mm2 12” (30cm) 70000 mm2From 2010-3-2 清华大学微电子学研究所 5集成电路的制造过程-封装Wire BondingSubstrate Die PadLead Frame2010-3-2清华大学微电子学研究所6集成电路的制造过程-芯片2010-3-2清华大学微电子学研究所7集成电路的制造过程-成本 NRE(NonRecurring Engineering) Cost is Increasing0.35um 40k$ 0.25um 80k$ 0.18um 160K$ 0.13um 250K$ 90nm 900K$2010-3-2 清华大学微电子学研究所 8内容简介 集成电路的应用领域 集成电路的制造过程 从CPU的发展看IC的进展 从行业的发展看IC的进展 从ISSCC看IC的发展方向2010-3-2清华大学微电子学研究所9摩尔定律Intel的创始人戈登摩尔(Gordon Moore) •“集成电路所包含的晶体管每18个月就会翻一番” 个月就会翻 番”2010-3-2清华大学微电子学研究所10PDP1(1960)PDP-1(1960)The PDP-1 sold for $120,000.MIT wrote the firstvideo game, Spaceg pWar! for it.A total of 50 wereA total of50werebuilt.INTEL CPUINTEL CPU的发展i4004 1971年11月15日,成立3年的Intel公司推出了世界上第一个微处理器(4004CPU),4位微处理器,10微米的工艺,16针DIP封装,尺寸为3*4mm,共有2300个晶体工艺封装尺寸为3*4共有管,工作频率为108KHz,每秒运算6万次。

清华大学李福乐老师_集成电路设计_SAR ADC

集成电路设计方法三、电路设计-SAR ADC李福乐清华大学微电子所提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验SAR ADC Principle •以D/A来实现A/D, 逐次逼近•需要N次D/A和比较实现1次N位A/D转换•精度主要由DAC决定•无运放,低电压、低功耗•深亚微米CMOS工艺下很有发展潜艺下很有发展潜力的结构•超低功耗,高速转换是研究热点–异步时序控制可实现性能8~16 bitTime‐interleavedxk~ x00M S/s9‐b, 50MS/s, 65fJ/conv.9‐b, 40MS/s, 54fJ/conv.10‐ 10MS/s, 11fJ/conv.0b,0MS/s,fJ/conv.No Time‐interleaved!SAR的功耗优势实际上在中低分辨率上异步SAR结构主要N i t 的速度已逼近Pipeline结构Nyquist结构ADC的比较Ref: Shuo‐Wei Michael Chen. JSSC 2006.12提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验DAC topologies二进制电流型电压型电压改进型电流型R2R阻容混合型电荷型匹配好;低功耗单转差方案1单转差方案¾电荷型DAC特点:¾集成T/H 电路¾与输入相连的开关较多¾输入电容较大¾采用分段结构可减少电容数目¾电容大小是精度与面积功耗的权衡,可通过mento ‐carlo 仿真确定¾对高精度转换,输入开关键点底板采样关Ron 线性须保证bootstrap !¾高位电容可采用单元温度码控制,以减小输入端毛刺,避免电荷泄漏;以及确保单调性¾高位电容可采用DEM 技术进一步提高精度¾版图关键点:t t¾DAC output整体电路Ref: 叶亚飞实践课汇报PPT一个8bit SAR ADC整体结构与信号关系顶板采样10提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验典型的两段分段电容结构X dV u a C 2)11u C kC 幅度VR的阶跃,其对DAC输出Vo的改变量分别为其中:Lt C X +保持正确权重,确保ADC线性=LL u k k C ⋅−=2别为:确保ADC线性,必须有:(a C C k +L Lt k C 2由以上公式可见,要令输入kC结论:1ADC的增益误差只取决于总采样电容与接到参考的总电容之比,MSB段接地的Cd1或寄生不会改变增益误差;2MSB段增加Cd1=kCu Cd1Cd1kC段不参与输入采样,降低ADC输入电容,且不会导致增益误差C 这里:①和②点的权重误差:dV dV =(Lt C C +根据前面的线性化设计结果有:在实际设计中,通常有:LtC <<<<在实际设计中常有为电容上极板寄生电容值与电容本身值之比寄生电容设计考虑•LSB段的寄生Cp2带来权重误差,导致非线性S C2带来权重误差导致非线性–权重误差比例固定为β,因此降低LSB端位数L,可降低非线性–LSB段所用电容、Ca,采用上极板共接•的上下极板间寄生Cp3直接影响权重,导致非线Ca直接影响权重导致非线性–版图布线要特别注意最小化Cp3•MSB段的寄生Cp1不会带来非线性问题和ADC增益误差,但作为DAC时,会带来约Cp1/CMt的增益误差但作为时会带来约p/的增–MSB段所有电容,采用上极板共接,此为底板采样需要better?Which is•从噪声和匹配考虑,MSB段的电容不能太小从声和考虑可取–k>1•从优化电容面积考虑,可采用多段结构–对于中低分辨率ADC,优化面积和输入电容C优化面积和输入电容–对于失配,可采用校准技术提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验由此可计算出元件匹配要求然后根()Nuu E E 221ασ≤由此可计算出元件匹配要求,然后根据工艺参数可确定元件尺度10%50%977%97.7%Ref: Anne Van Den Bosch, …, “An Accurate Statistical Yield Model for CMOS Current ‐Steering D/A Converters”, 2001电容取值:蒙特卡洛仿真法除了计算之外还可对除了计算之外,还可对SAR 结构建模,采用蒙特卡洛仿真法来设计电容尺度根据工艺厂商系统级模型提供的数据设定容值和失配Mento ‐Carlo 分析调整10u*10u: 0.11%若由噪声决定:满足要求?容值N10u*10u 的分析结果满足12bit 要求分段结构设计对于分段结构:1分段结构与CDAC 非线性)从匹配角度,分段结构不能降低电容值2)从噪声角度,分段结构也不能降低电容值3)分段结构可提高最小单元电容值,使其免受工单元电容值,使其免受艺最小尺度的限制4)若指标不受失配限制,分段结构可降低总电容值和ADC 输入电容(中低分辨率or 采用校准)Ref: Stefan Haenzsche, etc. “Modelling of Capacitor Mismatch and Non ‐Linearity Effects in …”, MIXDES 2010分段结构电容设计:可按照不分段的方法先设计Csample 值,而后截取高M 位为段选择合适的设计MSB 段,选择合适的Cu, k ,设计Ca 和LSB 段电容电容失配校准PrinciplelOffsetMeas.MeaslinearityMeasMeas.Ref: Y. Kuramochi, et, al. A 0.05‐mm2 110‐uW10‐b Self‐Calibrating Successive ApproximationADC Core in018um CMOS ASSC20070.18‐ CMOS,分段结构结合校准技术带来电容缩小Main DAC+CAL_DAC校准模式与转换模式Calibration Mode Conversion Model b d dRef: Y. Kuramochi, ASSC 2007非线性效应实际电容表达式:()()()⎥⎥⎦⎤⎢⎢⎣⎡−+−+=22101nom nom V V V V C V C αα电容电压系数致使电容值与输入电压有关,导致ADC 全局渐变的非线性,影响INL ;通常对12bit 以上分辨率的需要考虑电容电压系ADC ,需要考虑电容电压系数的影响差分结构不受1影响会好a1影响,会好一些MOM 电容?提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验Requirements On Comparator?amp amp amp amp 1234•High Speed–Offset 不影响总体线性度,但考虑到Latch 尺寸小,但导致offset 分布扩大–前置放大器的带宽;Latch 的速度•Low offset–影体线性度但考虑到转换精度,以及latch 迟滞效应、噪声和分辨力,其前置放大器增益需足够放大器级数要根据延时、增益、功耗来权衡选择Ref: JOEYDOERNBERG 前置放大器的增益–Offset Cancellation•Low Noise–主要是第一级放大器DOERNBERG, JSSC 1989主要是第级放大器amp1(1/f, thermal noise)•Low kickback noise–Latch 设计要合理(for example: Cascode, cap at input)–(especially at latch on ‐to ‐off)时序设计控制(p y )•Low Power–比较器是构成SAR ADC 功耗的主要单元Trade ‐offM1M2M1采用交叉耦合构成负阻,用于提高增益:Av=gmi/(gm2‐gm1)W2>W1W2W1:放大器W2<W1:带迟滞效应的比较器缺点:有静态功耗!问题:如何优化Latch的速度???低功耗动态比较器预放大器增益~ 2,电流1mA PMOS 负载工作在线性区输出共模逼近VDD ,这样latch 比较时会更快速度快:<100ps for 65nm LL processp Ref: Chun C. Lee, A SAR ‐Assisted Two ‐Stage Pipeline ADC. JSSC 2011.4Latch 无静态功耗动态pre ‐amp + ,无静态功耗~100ps for 90nmRef: 17.7 ISSCC2007Ref: 12.4 ISSCC2008提纲•引言•DAC设计–DAC类型–CDAC分段结构–CDAC电容失配与校准•比较器设计–比较器类型–比较器失调与噪声•SAR逻辑设计–同步逻辑–异步逻辑•实验cancellationComparator offset calibration在preamp输出加入电流可以矫正offset,但同时引入寄生,会降低速度;yield冗余设计也是提高y的办法Ref: S. Park, et, al. A 4GS/s 4b flash ADCin 0.18um CMOS. ISSCC 2006通过衬偏效应来调整输入管VT,以此来校准offsetRef:Alpman, Erkan. A 7‐BIT 2.5GS/sec TIME‐INTERLEAVEDC‐2C SAR ADC FOR 60GHz MULTI‐BAND OFDM‐BASEDRECEIVERS. PHD ThesisComparator offset calibration在动态比较器中,通过调整输入差分对或差分对负载来校准offsetRef: Masaya Miyahara, etc. A Low ‐Noise Self ‐Calibrating Dynamic Comparator for high ‐speed ADCs或通过调整输出点的差a)调整输入分负载电容来校准offset可编程电容阵列差分对b))调整差分负载Ref: 13.5 ISSCC2007Ref: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4Comparator noisepre ‐amp + Latch:静态p p 输入等效噪声可按照传统的放大器噪声分析方法来进行,即先各管产生的声在输先对各导通管产生的噪声在输出节点功率求和,然后再除以增益平方来求得输入等效噪声222222w +⎞⎛总输出噪声电流密度:()141312131211di di w di di di o +⎟⎟⎠⎜⎜⎝⋅+=di r di v 222211⋅=⋅⋅⋅=π总输出噪声电压:o o o no C g C r 422πtCLKΔV动态pre ‐amp :增益和输出噪声与积分m tg 1=的增益:C A 时刻tTime ‐Domain noise analysis model基本RC 并联电路的时域噪声分析假设:①R 为无噪声电阻②in 为高斯分布噪声电路,其等效噪声电阻为Rn T 0时均值的高斯变量方差为③T=0时,vc 为0均值的高斯变量,方差为σ0那么,在时刻t 时,vc 仍为0均值高斯变量,且其方差为:dfR kT di nn42=()RCt RC t n t e e CR kTR 220221−−+−=σσt<<RC 的情况下,上式可简化为:f l l f 在情况式简化为Ref: Pierluigi Nuzzo, Noise Analysis ofLowz降低输入过驱动Vov1 z降低输入共模z延长有效积分时间tdLow noise dynamic comparator增加了:增加了:Co1, td, gm2gm1, td,A2第二级通过M6,M7向ti+, ti ‐放电,M1M2两级动态结构:在第一级增益不够高的情况下,增加第二级增益也能有效地降低噪声噪声Vni(σ)的对比(比对的两者具有相同的size )21mV 066mV 延长了M1,M2饱和区工作时间td ;第一级差分电流通过M6,M7,带来第二级的电压增益A2增加第二级增益,也能有效地降低噪声2.1mV 0.66mV0.41mV0.2mV @ΔSTR=60psRef: Chi ‐Hang Chan, etc. ASSCC 2011 9‐4。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0.25u-0.11u

物理 综合 流程 布局 布线

深亚微米下的设计流程

• 例:中科院EDA中心的参考流程(参见 附件)

– 深亚微米全定制集成电路设计参考流程 – 深亚微米超大规模集成电路设计参考流程 – 深亚微米混合信号系统芯片设计参考流程

片上系统(SOC)

• 什么是SOC

漏电流提前饱和

跨导的降低

速度饱和(续)

• 在饱和区反映速度饱和的解析式:

ID = W 1 μ 0Cox L 2

(VGS − VTH )

2

⎛ μ0 ⎞ 1+ ⎜ ⎜ 2v L + θ ⎟(VGS − VTH ) ⎟ ⎝ sat ⎠

• 上式中μ0/(2vsatL)和θ分别代表横向和垂直电 场引起的迁移率的退化

输出电阻随VDS的变化

深亚微米器件小结

• 目标:用按比例缩小原理获得更低电压下工作 的小尺寸器件,实现更快的工作速度和更低的 功耗 • 当器件尺寸缩小时,电源电压也必须减小 • 阈电压不能与电源电压成比例下降 • 可以在同一芯片上采用多阈值电压器件来实现 兼顾性能和功耗 • 晶体管特性偏离了长沟道的平方率关系,高阶 项的作用增强,但在电路设计中,基本的平方 率关系还是具有指导意义

短沟道效应

• 短沟道效应具体表现在:

– – – – 阈值电压的变化 垂直电场引起迁移率下降 水平电场引起的速度饱和 热载流子效应

– 漏源电压引起的输出阻抗的变化

阈值电压的变化

• 阈值电压存在一个下限值,其减小的速 度偏离按比例缩小原理 • 阈值电压的下限取决于以下几个因素:

– – – – 亚阈值特性 随温度和工艺的变化 与沟道长度的依赖关系 漏致势垒降低(DIBL)

时钟电压自举技术

• 原理:增大关键开关的驱动电压 • 缺点:可能会影响器件寿命

例:时钟电压增大

开关运放技术

• 原理:消除那些工作在中间电压的开关,最好 都用接电源或地的开关来代替它们

例:1.5b全差分 开关运放MDAC

开关运放技术

• 开关运放:

例:全差分开关运放

开关电流技术

• 在电流域处理信号 • 不依赖浮地线性电容,可与数字CMOS 工艺完全兼容 • 固有的低电压摆幅特性,有利于低电压 和高速设计 • 问题:

⎛ Cd ⎞ ⎜1 + ⎟ ⎜ C ⎟VT ox ⎠ ⎝

• 要保持足够低的“关断电流”, VTH有一个下限

温度、工艺变化与沟道长度

• VTH的温度系数约为-1mV/ºK,导致其在工作温 度范围内有几十mV的变化 • 工艺引起的VTH变化约为50mV • 同一晶片上不同沟道长度的晶体管,VTH随L的 减小而变小,而制造过程中沟道长度不能精确 控制

动态范围

• 信号的最大摆幅(swing)缩小α倍 • 热噪声限制的动态范围缩小α倍 • 若要保持热噪声限制的动态范围不变:

– 将gm增大α2倍,即晶体管宽度W/α αW – 电流增为αID,按比例缩小前后功耗不变 – 器件电容增加: (αW )(L α )(αCox ) = αWLCox

器件电容

– 电流镜的匹配问题 – 较大的kT/C底部噪声问题

互连延迟问题

Percentage of Delay

1.0u

0.5u 0.25u 0.18u Silicon Technology

Wire

Gate

物理综合(Physical Synthesis)

0.8u

逻辑 综合 布局 布线

0.5u to 0.35u

0.5u

0.25u 0.35u

10GHz

0.8u

0.6u

3GHz 1GHz

GaAs

1.5u 2u

1u

Bipolar 3u CMOS

75 77 79 81 83 85 87 89 91 93 95 97 99

现在的多工艺射频收发器(例)

RF LNA/Mixer/VCO

Receiver

IF Mixer ADC 90 I

2 ⎝ L α ⎠⎝ α

α ⎠

=

1 1 W μ nCox (VGS − VTH )2 2 L α

• 晶体管处于线性区时电流也缩小α倍

理想的晶体管按比例缩小

• 电路设计关心的参量变化

– – – – – 跨导 增益 动态范围 器件电容 功耗

跨导

• 按比例缩小后的晶体管跨导:

g m , scaled W α VGS − VTH = μ (αCox ) Lα α

(αCox ) = WLCox • 沟道电容: Cch,scaled = α α α • 漏源极结电容: W E ⎛W E ⎞

W L 1

CS / D , scaled =

α α

(αC ) + 2⎜

j

⎝α

+

• 器件电容缩小α倍

= WEC j + 2(W + E )C jsw

[

⎟(C jsw ) α⎠ 1

漏-源电压引起的输出阻抗的变化

• 在饱和区,VDS增大会使得夹断点向源区向源区移动, 同时沟道调制作用也减弱,输出阻抗增大 • 对于短沟道器件,随着VDS进一步增大,漏致势垒降低 (DIBL)变得显著,导致阈值电压减小,漏电流增大, 这将引起输出阻抗的减小,基本抵消了第一种原因所 导致的增长 • 在足够高的漏电压下,漏区附近碰撞电离产生漏-衬电 流,降低了输出阻抗

phone

Logic

Accelerators (bit level)

RTOS book

Keypad, Display

Control

ARQ

A D

FSM

FFT

uC core

Filters

(ARM)

analog

Dedicated Logic digital

Coders

DSP cores

SOC设计

• SOC的复杂性决定了其设计不可能每次都从零 开始 • 基于IP核的SOC设计是集成电路设计的方向

]α

S/D结电容的按比例缩小

门延时和功耗

• CMOS反相器的延时可近似为:

Td , scaled = C α VDD 1 ⎛ C ⎞ = ⎜ VDD ⎟ α⎝I Iα α ⎠

• 功耗可近似为:

2 Pscaled = f (C α )(VDD α ) = fCVDD α 3 2

CMOS反相器

短沟道效应

– 共模抑制比会下降,对共模反馈电路的要求 会有所提高

SC电路中的LV设计技术

• 问题:

VTH不随电源按比例缩小, LV将导致开关导通不良!

SC电路中的LV设计技术

• 解决办法:

– 采用低阈值器件

• 需采用特殊工艺 • 漏电流增大,对保持电荷不利

– 采用时钟电压自举技术 – 采用开关运放设计技术(switched-opamp) – 采用开关电流技术

W = μCox (VGS − VTH ) L

• 可见跨导保持不变!

增益

• 由于漏极周围的耗尽区也缩小α倍,故ΔL/L 保持不变,沟道调制系数λ=(ΔL/L)/VDS,增 大α倍 1 1 r = • 输出电阻的变化:O , scaled = I λI

αλ

• 增益gmrO保持不变

α

D

D

夹断的按比例缩小效应

– 实现复杂系统功能的超大规模集成电路 – 采用超深亚微米工艺技术 – 使用一个或数个嵌入式CPU或数字信号处理 器 – 具备外部对芯片进行编程的功能 – 主要采用第三方的IP核进行设计

典型的SOC芯片例子

Analog Baseband and RF Circuits Communication Algorithms Protocols

• 恒电场按比例缩小(constant-field scaling) • 缩小速度遵循摩尔定律

理想的晶体管按比例缩小

• 晶体管的W, L, tox, VDD, VTH, 源漏结的深度和 周长均缩小α倍 • 按比例缩小后的饱和漏极电流 2 ⎛ w α ⎞⎛ VGS VTH ⎞ 1 ⎟⎜ I D , scaled = μ n (αCox )⎜ − ⎟ ⎜ ⎟

热载流子效应

• 漏源电压足够大时,短沟MOSFET会有很强的 横向电场,虽然载流子平均速度达到饱和,但 其瞬时速度会不断增大,尤其是其加速向漏极 运动时,这些载流子被称为“热”电子 • 在漏区附近,热载流子“撞击”硅原子发生碰撞 电离,产生新的电子-空穴对,电子流向漏区, 空穴流向衬底,这样产生有限的漏-衬电流 • 如果载流子获得足够高的能量,则有可能注入 栅氧,甚至流出栅极,产生栅电流

第十二讲

深亚微米工艺下的电路设计 (讨论)

李福乐 lifule@

Outline

• • • • 按比例缩小原理 短沟道效应 深亚微米工艺下的设计讨论 SOC设计

按比例缩小原理

• 理想的晶体管按比例缩小

– 纵向和横向尺寸均缩小α倍(α>1) – 电源电压和晶体管阈值电压降低α倍 – 所有掺杂浓度增大α倍

单片CMOS实现(例)

• 单片、可变工艺尺寸 CMOS 或BiCMOS • 最少的外围器件

低电压工作电路技术

• 重要单元(运放)的低电压设计 • 采样处理电路的低电压设计

运放的低电压设计

• • • • 采用多级结构 采用背栅驱动 Rail-to-rail设计 对于全差分运放,可采用伪差分(pseudodifferential)设计

VCO Tank Channel Select PLL

IF, AGC ADC IF PLL Tank

Q

DAC

I

Discrete GaAS Bipolar Si CMOS Si

Power Amplifier