PADS中元件引脚类型的解释

PADS元件封装制作规范

PADS元件封装制作规范 PADS元件封装分为5个库:表面贴装(surface)、插入式(through)、连接器(connect)、孔和焊盘(padstacks)及other库(包括管脚、二维线、原理图模板等)。

在以后设计中如遇到库中没有的元件封装,应按以下规范制作,在试用通过后归入相应的元件库中。

一、CAE元件封装制作规则1、CAE元件命名规则常用元件的CAE命名按照表1命名。

特殊元件可用元件名称(元件在ERP中的名称)命名。

表1 常用CAE元件封装命名原理图元件需要具备REF和Value两个属性,REF属性代表元件在原理图中的编号,Value属性对于电阻、电容、电感表示这些元件的标称值,对于其余元件表示为其名称。

REF 和Value属性采用默认值(字体大小100mil,线宽10mil)。

圆点放在元件封装中心。

设计栅格需设为100,具体参数见下图。

这4处的设计值均设置为100二、PCB封装库规则元件PCB封装需具备Name和Value两个属性,分别与原理图封装中REF和Value两个属性对应。

元件PCB封装包括三个部分:封装名称、丝印、焊盘,下面以此分为三部分详述PCB封装库规则。

1、PCB封装库命名规则PCB封装库命名总体上遵守以下规则:一、通用分立元件命名:元件类型简称+元件英制代号(mil)\公制代号(mm)(1mm=39.37mil,1inch=1000mil=25.4mm);二、小外型贴装晶体管命名:元件封装代号;三、集成芯片及接插件命名:元件封装类型+元件参数(包括元件实体尺寸、管脚数、管脚间距、列间距等)。

为方便起见,在元件PCB命名时,元件参数默认采用英制,若采用公制命名,应进行相应的注释;元件管脚间距、列间距采用中心对中心的取值规则;元件实体尺寸表示为元件在PCB板上的占地面积,如右图,元件实体尺寸为16×16mm而不是14×14mm。

特殊元件的PCB封装按PART命名;各元件PCB封装命名详见表2和表3:1)、表面贴装元件(SMD)的命名方法:表2 SMD分立元件的命名方法元件类型简称标准图示命名贴片电阻R 命名方法:元件类型简称+元件英制代号命名举例:R0402,R0603,R0805,R1206, R1210, R2010,R2512。

PADS Logic元器件库管理

PADS Logic元器件库管理本章重点:◆PADS Logic元器件类型(Part Type)◆创建引脚封装(Pin Decal)◆创建CAE封装(CAE Pecal)◆创建新的元器件类型(Part Type)一、PADS Logic元器件类型在将元器件添加到原理图之前,它必须是PADS库中的一个已经存在的元器件类型。

元器件类型由以下3部分组成:➢CAE封装(CAE Decal),又称为逻辑符号➢PCB封装(PCB Decal),如DIP14➢电参数,如引脚号码和门的分配等以7404为例说明:⏹元器件类型名字:7404⏹CAE封装:INV⏹PCB封装:DIP14⏹电参数:6个逻辑门(A到F),使用14个引脚中的12个引脚,另有一个电源和地引脚二、创建引脚封装1.建立引脚封装引脚封装是一个二维线(2D Line)符号,它代表引脚的逻辑功能。

执行菜单命令【Tool】——【Part Editor】,进入元器件编辑器界面。

再执行菜单【File】——【New】,弹出元器件编辑项目选择类对话框,如下图所示:PNAME:引脚或功能的名字,如A00、D01或VCCNETNAME:在原理图中显示时的网络名字标志#E:指引脚号码TYP:引脚类型(Pin Type)SWF:门交换值(Gate Swap Values)提示:引脚类型和门可交换值仅显示在CAE封装编辑器中,在原理图中不显示。

2.定义引脚封装定义一个简单的引脚封装(Pin Decal),它由一个横线和一个圆组成。

具体方法如下:◆工具栏单击封装编辑(◆找到建立绘制二维线(Create 2D Line)图标◆单击鼠标右键,3.保存引脚封装保存引脚封装到库中的操作步骤:◆封装编辑工具栏封装编辑图标退出编辑状态说明:二维线绘图时,单击鼠标右键打开弹出菜单的补充:Complete: 完整的Add Corner: 添加拐角Del Corner: 删除拐角Add Arc: 添加圆角Width: 设置二维线宽度Polygon: 绘制多边形Circle: 绘制圆形Rectangle: 绘制矩形Path: 绘制线段Orthogonal: 绘制水平线或垂直线Diagonal: 绘制水平线、垂直线或45度线Any Angle: 绘制任意角度线Cancel: 取消在需要的时候,要进行的设置,主要是为了控制绘图的大小(还记得这项设置在什么菜单的什么命令中吗?OK ,在【Tools】菜单的【Options】命令中设置)。

Pads2007 logic元器件建库

Pads2007 logic元器件建库作者:fedorayang@eda365一、目标用pads logic 2007自带的ti:74LS14为例讲解建立原理图元件库的过程.Ti库中,和74LS14属于同一个元件族的元件如下:ti: 54HC1454HCT1454LS1474HC1474HCT1474LS14先理解4个感念: 元件族,逻辑族,前缀,后缀.逻辑族: 上述54HC,74LS就是逻辑族.元件族: 上述列举的14就是代表某一功能的元件族.前缀: 用来表示逻辑族;54HC,74HC就是前缀,这两个等于 ?4HC,系统会自动把?代替为5和7. 后缀: 14就是后缀,写成\14.上述概念理解不了也没有关系,做完试验就会理解了.我们的目标是在新库中建立上述器件,为了正确理解概念,我们再多建立3个器件:54147414NS74LS14二、概念建立器件之前需要理解3个概念:Part, CAE decal, PCB decal.Part:可以看成引用CAE decal和PCB decal,再包含一些配置信息。

Part可以被看作这样的一个对象。

CAE decal:在原理图中显示。

包括2D图形,器件的边框,有些表示功能(例如逻辑门);终端,在part中被配置成具体引脚。

PCB decal:在PCB中显示.2D图形,器件的丝印边框;器件的引脚。

CAE decal和PCB decal除了概念描述的内容之外还有label,最常用的label有器件编号和器件类型,例如器件编号U1,器件类型54HC14.Part, CAE decal, PCB decal三个概念在看完这个资料回头想想是否完全明白。

三、准备1.进入part editorÆ tools Æ part editorlogicPads2.建立新库newÆ Library… Æ Create New Lib…File这两步简单,写不写都无所谓!四、操作1.建立CAE decalFileÆnew打开工具栏设计出CAE decal如下:怎样设计请参考其他书籍,这方面资料较多,也比较简单。

PADS2007原理图中加元件规则

PADS2007原理图中加元件规则一、CONN:针座:(S:为180度,R为90度)1121S-XP:脚心距为P=3.96mm2001S(R)-XP:脚心距为P=2.54mm201S(R)-XP脚心距为:P=2.54mm 单排黑色插针201S(R)-1*XP脚心距为:P=2.54mm 双排黑色插针203S(R)-XP脚心距为:P=2.54mm 单排黑色插槽203S( R )- 1*XP脚心距为:P=2.54mm 双排黑色插槽301S( R )-XP 脚心距为:P=2.54mm 双排方PIN 黑色牛角302NS ( R )-XP 脚心距为:P=2.54mm 双排方PIN 黑色TEST:测试点红色,千代UHTWSZ-4Pin:PCB固定端子 4PIN M4螺孔直脚 8*8*11mm T1.0mm 镀锡铜UHTWSZ-6Pin: PCB 铜条、、、二、RES-DIP:插件电阻J:金属膜阻,点击需要的阻值JUMP:跳线K-:可调电阻MOV:压敏电阻NTC:热敏电阻S:水泥电阻T:碳膜电阻Y:线绕电阻三、RES-SMD(贴片电阻)四、CAP-DIP:插件电容电解电容:直接选取需求容量C:瓷片电容CBB: CBB电容D:独石电容DL:涤沦电容钽电容:2904-X2:X2电容Y2:Y2电容五、CAP-SMD(贴片电容)六、DIODE(开尖二极管,发光二极管、稳压二极管,三极管,MOS管、、、) DIO-整流二极管IGBT-IGBTK-快恢复二极管LED:发光二极管MOS-MOS管TRA-三极管W-稳压二极管、、、七、Rly丝、保险座、整流桥、、FUSEB:玻璃保险管(KA:快断带引脚,KB:快断加保险座,MA:慢断带张脚,MB:慢断加保险座)GUB-桥堆RLY-继电器八、IC:九、TX:CT-CTL-电感TX-变压器十二:OTHERBAT-电池BZ-蜂鸣器HS-散热器XL-晶振。

PADS软件基础知识大汇总(元件封装、Logic原理图、Layout)

PADS软件基础知识大汇总(元件封装、Logic原理图、Layout)PADS Logic 窗口介绍1、工具栏中有两个常用的工具栏:① 选择工具栏② 原理图编辑工具栏2、在工具栏最右侧有一个打开/关闭项目浏览器(工作窗口左侧的 Project Explorer)按钮,在项目浏览器中可以浏览和选择① 原理图页② 元器件列表③ 元件类型④ 网络⑤ CAE封装列表⑥ PCB 封装列表PADS 元件类型在将元件添加到原理图之前,它必须是PADS 库中的一个已经存在的元件类型(Part Type),一个完整的元件类型应该由以下三种元素组成:● 在 PADS Logic 中,被称为逻辑符号或 CAE 封装(CAE Decal)展开剩余94%● PCB 封装(PCB Decal),如 DIP14● 电参数,如管脚号码和门的分配下面是一个 7404 的 PADS 元件类型元件类型名字:7404CAE 封装:INVPCB 封装:DIP14电参数:6 个逻辑门(A 到 F)使用 14 个管脚中的 12 个管脚,另有一个电源和地管脚元件类型可以在 PADS Logic 或 PADS Layout 中建立,CAE 封装仅可以在 PADS Logic 中建立,PCB 封装仅可以在 PADS Layout 中建立。

元件 CAE 封装标识进入 CAE 封装后,会有几个字符标识REF:是一个参考编号,如:U1、U2…PART-TYPE:是一个元件类型,如 RK3399、RK1108…Free Label 1:是显示元件类型的第一个属性Free Label 2:是显示元件类型的第二个属性...管脚 CAE 封装标识PNAME:放在这里指示管脚或功能的名字,如A00、D01或VCCNETNAME:放在这里指示在原理图中显示时的网络名字标记“#E:放在这里指示管脚号码TYP 和SWP:放在这里指示管脚类型(Type Pin)和门交换值(Gate Swap Values)注意:管脚类型、门交换值仅仅显示在 CAE 封装编辑器中,在原理图中不显示PADS 中引脚类型引脚类型一般用于原理图仿真或 DRC 检查中(PADS Logic 中没有DRC 检查功能),例如Open Collection 没有接上拉电阻,DRC 检查就会报错或仿真不正常① Bidirectional 双向引脚,即 GPIO 口,具有输入输出功能② Ground 地③ Load 负载引脚,input,接受信号④ Open Collector 开集电极引脚,三极管集电极没有上拉(未搞懂)⑤ Or-tieable Source 或可连接的源引脚,可以或方式连接在一起的输出信号源(未搞懂)⑥ Power 电源正⑦ Source 信号源引脚,也就是 output,输出引脚⑧ Terminator 信号终端引脚,传输线信号端接(未搞懂)⑨ Tristate 三态信号引脚⑩ undefined 无定义类型PADS 设计常用单位1 mil(密耳)= 0.0254 mm/1mm=40mil1 inch(英寸)= 2.54 cm0402对应的封装为1005(长1mm,宽0.5mm)对 Sheet 进行编辑1、编辑Sheet Border(页边、板边)划线部分使用的是“原理图编辑工具栏”里的“画 2D 线”2、保存编辑后的 sheet 或者其他设计者的 sheet 样式,要全部选中绘图项,合并,保存到库中。

PADS高级技巧之元件的拷贝与修改

PADS高级技巧之元件的拷贝与修改操作系统:windows7PADS版本:9.2一、基本概念:1、part、gate与decal关系示意图:2、说明:原理图库中的元件称为part,每个part由一个或多个gate(可以理解为功能单元)构成。

比如常用的双运放LM358通常设计成3个gate:gate A和gate B分别为第1~3脚和第5~7脚组成的两个运放单元;gate C为第4脚和第8脚组成的电源单元。

基本的功能单元称为decal。

修改元件库时,可以根据功能需要在库中新建一个decal,也可以为part中的gate从库中任意指定一个decal以实现对应的功能。

二、引脚的增减(以3脚的LDO改为4脚为例):1、目的:修改原理图库中的元件(比如添加或删除引脚等),并对原理图中的相关元件进行更新。

2、操作步骤:a)单击原理图中待修改的元件b)点击右键并选择“Edit Part”菜单。

c)选择菜单栏下的“Edit Graphic”图标d)选择要修改的gate并单击“ok”按钮,或者从“AltenativeDecals”栏中重新指定一个Decal。

e)修改Decal内容,比如添加一个引脚。

f)选择菜单“File->Return to Part”,然后点击确认按钮,返回主界面g)点击存盘图标并确认保存,至此,对Decal所作的修改已保存到库中。

h)接着,屏幕上提示是否更新图中已有元件,点击“是”予以更新。

3、常见问题:当给part中的gate单元增加引脚时,上述操作步骤进行顺利,但若是减少引脚(由4脚改回3脚),最后一步却出现如下错误提示:4、问题原因:出现上述错误提示时,库中的元件已经修改成功(引脚数减为3),但此时原理图中的LDO元件引脚数为4,因此软件拒绝对其更新,甚至拒绝添加新的LDO元件,除非先将原理图中4个引脚的LDO元件全部删除。

看来PADS软件在引脚数目的关联上的确很纠结。

5、解决办法:添加新的3脚的LDO元件前,先将原理图中的所有4脚的LDO元件删除掉。

PADS logic

3.添加管脚 4.建立元件

• 5.分配自己做的CAE给元件

元件信息的填写

• 同时勾选三个复选框

CAE库的创建

• • • • • 1、利用向导创建(以JTAG插座为例创建) 2、利用非向导创建(以三极管为例) 3、多门集成芯片创建(以74ls00为例) 4、分立器件的创建(以贴片电阻为例) 5、电源的创建(以3.3V电源为例)

第一步 进入logic封装创建界面

• 单击封装编辑工具栏按钮,展开工具栏

“管脚”标签

用于将逻辑封装和PCB封装管脚对应

• tips:若引脚非常多,可以在excel编辑好导入

“属性”标签

• 用于设置 元件类型 的制造商、 价格等说 明信息

第四步 检查元件

• 单击检查元件,提示错误和警告信息

(本例不用理会,JTAG本来就有两个GND引脚)

确定后发现,引脚顺序和实际不符

• 单击CAE封装向导

第二步 建立logic封装

• 设置CAE封装向导参数

保存,弹出的对话框输入新的名称

第三步 建立元件类型

• 单击“编辑电参数”按钮

“常规标签”

• 逻辑系列:电容CAP 电阻RES 连接器CON。。。

“PCB封装”标签

“门”标签 用于设置门封装,即CAE封装

分配之前建立完成的Logic封装

库文件名.pd9

库名称

用途

lib目录下对应的名 称

CAE库

是Logic中的逻辑封装CAE Decal库。必 须与Part Type建立对应关系

库文件名.ld9

库名称

用途

lib目录下对应的名 称

Parts库

将Part Type与Part Decal以及CAE Decal 结合后就具有完整的Part信息,保存 到该库中。在Layout与Logic中 都需要, 库文件名.pt9 而且对于同一个元件在上述两个系统 中必须是同一个Part Type名!

PADS逻辑类型说明

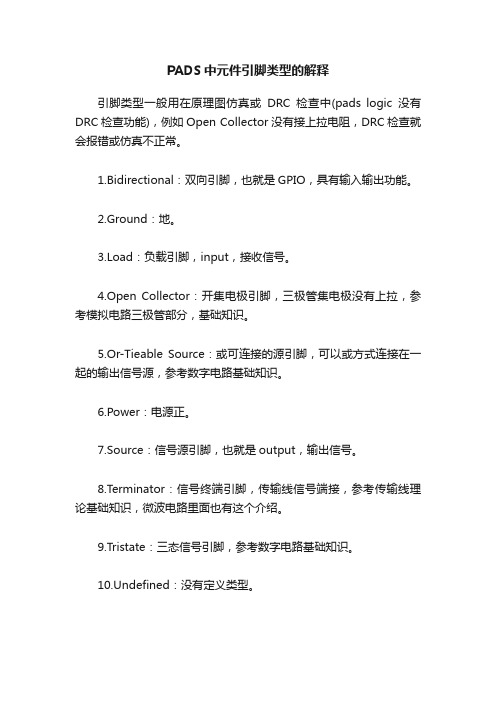

中英文大意ANA BGA ball grid array 球栅阵列封装BPF BQF CAP CAPACITOR 电容器CFP CFP 陶瓷扁平封装CLC CMO CON CONIN 连接器CQF DIO DIODE 二极管DIP Dual In-line Package 双列直插式组件ECL EDG FUS FUSE 保险丝HMO HOL IND INDUCTANCE电感LCC Leadless chip carrier无引脚片式载体MOS Metal Oxide Semiconductor金属氧化物半导体OSC Open Source Commerce振荡器PFP PGA butt joint pin grid array 碰焊(pin grid array) PLC POT POTENTIOMETER可变电阻器PQF PSO QFJ CLCC(ceramic leaded chip carrier)也称QFJ,QFJ-G QFP quad flat package 四侧引脚扁平封装QSO RES Resistor电阻器RLY RLY继电器SCR Silicon Controlled Rectifier可控硅SKT SOI small out-line I-leaded package I形引脚小外型封装SOJ Small Out-Line J-Leaded Package (J形引脚小外型封装)SOP small Out-Line package (小外形封装)SSO SWI SWITCH开关TQF TRX Transistor (三极管TSO TTL Transistor-Transistor Logic (BJT-BJT逻辑门VSO XFR XFMR 变压器Z EN ZENER齐纳二极管UND 增加SIP single in-line package 直插式组件photoelectric coupler (光电耦合器LED Light Emitting Diode 发光二极管TVS Transient Voltage Suppressor (瞬态电压抑制二极管)FB Ferrite bead (磁珠)TP TEST POINT (测试点MIC MICROPHONE (麦克风)BQFP BQFP(quad flat package with bumper) 带缓冲垫的四侧引脚扁平封装CLCC ceramic leaded chip carrier (带引脚的陶瓷芯片载体)COB chip on board (板上芯片封装)DFP dual flat package (双侧引脚扁平封装)(是SOP 的别称)FP flat package (扁平封装)FQFP fine pitch quad flat package (小引脚中心距QFP)CQFP quad fiat package with guard ring (带保护环的四侧引脚扁平封装)HSOP H-(with heat sink)HSOP 表示带散热器的SOP LQFP low profile quad flat package (薄型QFP)SMD surface mount devices (表面贴装器件)CPGA Ceramic Pin Grid Array ZIP Zig-Zag Inline Package 之字型直插式封装TSOP Thin Small Outline Package TSSOP TSOP II Thin Shrink Outline Package。

PADS中元件引脚类型的解释

PADS中元件引脚类型的解释引脚类型一般用在原理图仿真或DRC检查中(pads logic没有DRC检查功能),例如Open Collector没有接上拉电阻,DRC检查就会报错或仿真不正常。

1.Bidirectional:双向引脚,也就是GPIO,具有输入输出功能。

2.Ground:地。

3.Load:负载引脚,input,接收信号。

4.Open Collector:开集电极引脚,三极管集电极没有上拉,参考模拟电路三极管部分,基础知识。

5.Or-Tieable Source:或可连接的源引脚,可以或方式连接在一起的输出信号源,参考数字电路基础知识。

6.Power:电源正。

7.Source:信号源引脚,也就是output,输出信号。

8.Terminator:信号终端引脚,传输线信号端接,参考传输线理论基础知识,微波电路里面也有这个介绍。

9.Tristate:三态信号引脚,参考数字电路基础知识。

10.Undefined:没有定义类型。

Pin type is generally used in schematic simulation or DRC check (PAD logic does not have DRC check function). For example, if open collector is not connected with pull-up resistance, DRC check will report error or abnormal simulation.1. Bidirectional: bidirectional pin, i.e. GPIO, has the function of input and output.2. Ground: ground.3. Load: load pin, input, receive signal.4. Open collector: Open Collector Pin, no pull-up of triode collector, refer to the triode part of analog circuit, basic knowledge.5. Or tieable source: or the connectable source pin, or the output signal source that can be connected together, refer to the basic knowledge of digital circuit.6. Power: positive power supply.7. Source: signal source pin, that is, output, output signal.8. Terminator: signal terminal pin, signal termination of transmission line, refer to the theoretical basis of transmission line, which is also introduced in microwave circuit.9. Tristate: three state signal pin, refer to basic knowledge of digital circuit.10. Undefined: no type defined.。

PADS介绍文档

编辑本段PADS 各层的意义PADS各层用途如下:TOP 顶层 - 用来走线和摆元器件BOTTOM 底层 - 用来走线和摆元器件LAYER-3至LAYER-20 一般层,不是电气层,可以用来扩展电气层,也可以用来做一些标示,比如出gerber做阻抗线的指示solder mask top 顶层露铜层,就是没有绿油覆盖paste mask bottom 底层钢网,你查下钢网就知道了paste mask top顶层钢网drill drawing 孔位层silkscreen top顶层丝印,丝印就是在电路板上面印标示的数据assembly drawing top顶层装配图solder mask bottom底层露铜silksceen bottom底层丝印assembly drawing bottom底层装配图LAYER-25 是插装的器件才有的,只是在出负片的时候才有用,一般只有当电源层定义为CAM Plane的时候geber文件才会出负片(split/Mixe 也是出的正片),如果不加这一层,在出负片的时候这一层的管脚容易短路。

第25层包含了地电信息,主要指电层的焊盘要比正常的焊盘大20mil 左右的安全距离,保证金属化过孔之后,不会有信号与地电相连。

这就需要每个焊盘都包含有第25层的信息。

编辑本段PADS的基本操作PCB封装:即光绘图上的描述焊盘、过孔位置及丝印的封装(DIP40) CAE封装:即原理图上描述该芯片外形的封装(如矩形边框,左右各20个脚)LOGIC封装:即该芯片各引脚作用的封装(如第20个脚是VCC、40个脚是GND)以上三种单独存在时只能在库中管理和打开PART封装则是针对某一种芯片的完整描述,以上三种类型的组合封装,也是PADS LOGIC、LAYOUT调用元件封装的唯一方式.PADS使用技巧1.用filter选择要删除的东东,然后框选,delete即可或者:无模下右键Select Net-Select All-Delete2.在Filter中只选Lable,在板图上框选整个电路板,将选中所有的元件标号,选择Property,可以同时修改所有元件标号的大小、字体的粗细等。

PADS中常用的元器件英文对照表

Fanily(逻辑族) 中英文大意Prefix(前缀)ANAUBGAball grid array(球栅阵列封装)U球栅阵列封装BPFUBQFUCAPCAPACITOR(电容器)C电容CFPCFP(陶瓷扁平封装)U陶瓷扁平封装CLCUCMOUCONCONIN(连接器)JCON接口CQFUDIODIODE(二极管)D二极管DIPDual In-line Package(双列直插式组件)U双列直插形式封装的集成电路芯片ECLUEDGPFUSFUSE(保险丝)F保险丝HMOUHOLXINDINDUCTANCE(电感)L电感LCCLeadless chip carrier(无引脚片式载体)U无引脚片式载体MOSMetal Oxide Semiconductor(金属氧化物半导体)UMOS管OSCOpen Source Commerce(振荡器)Y振荡器PFPUPGAbutt joint pin grid array碰焊 (pin grid array)U表面贴装型PGA ,底面陈列插装型封装PLCphotoelectric coupler(光电耦合器)UPOTPOTENTIOMETER(可变电阻器)P电位器PQFUPSOUQFJCLCC(ceramic leaded chip carrier)也称QFJ,QFJ-GU带引脚的陶瓷芯片载体QFPquad flat package(四侧引脚扁平封装)U四侧引脚扁平封装QSOURESResistor(电阻器)R电阻RLYRLY(继电器)K继电器SCRSilicon Controlled Rectifier(可控硅)SC可控硅SKTUSOIsmall out-line I-leaded package(I形引脚小外型封装)UI形引脚小外型封装SOJSmall Out-Line J-Leaded Package(J形引脚小外型封装)UJ形引脚小外型封装,塑料J形线封装SOPsmall Out-Line package(小外形封装)U小外形外壳封装SSOUSWISWITCH(开关)S开关TQFUTRXTransistor(三极管)Q三极管TSOUTTLTransistor-Transistor Logic(BJT-BJT逻辑门)U逻辑门电路(74系列IC)VSOUXFRXFMR(变压器)T变压器ZENZENER(齐纳二极管)Z稳压二极管UNDUndefined(不明确) U通用增加SIPsingle in-line package(直插式组件)U单列直插式组件PLCphotoelectric coupler(光电耦合器)U/N光电耦合器LEDLight Emitting Diode(发光二极管)LED发光二极管TVSTransient Voltage Suppressor(瞬态电压抑制二极管)TVS瞬态电压抑制二极管FBFerrite bead(磁珠)FB磁珠TPTEST POINT(测试点)TP测试点MICMICROPHONE (麦克风) MIC麦克风BQFPBQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封UCLCCceramic leaded chip carrier(带引脚的陶瓷芯片载体)UCOBchip on board(板上芯片封装) UDFPdual flat package(双侧引脚扁平封装)(是SOP 的别称)UFPflat package(扁平封装) UFQFPfine pitch quad flat package(小引脚中心距QFP) UCQFPquad fiat package with guard ring(带保护环的四侧引脚扁平封装UHSOPH-(with heat sink)HSOP 表示带散热器的SOPULQFPlow profile quad flat package(薄型QFP)USMDsurface mount devices(表面贴装器件)CPGA Ceramic Pin Grid Array UZIPZig-Zag Inline Package (之字型直插式封装)UTSOPThin Small Outline PackageUTSSOP TSOP II thin Shrink Outline Package U。

元器件封装及基本管脚定义说明(精)

元器件封装及基本管脚定义说明以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4II. 贴片式 [0201 0402 0603 0805 1206]贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5III. 整合式 [0402 0603 4合一或8合一排阻]IIII. 可调式[VR1~VR5]2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II. 有极性电容分两种:电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种]钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25VD TYPE (7343 35V]3. 电感: I.DIP型电感II.SMD 型电感4. 晶体管: I.二极管[1N4148 (小功率 1N4007(大功率发光二极管 (都分为SMD DIP两大类]II. 三极管 [SOT23 SOT223 SOT252 SOT263]常见的to-18(普通三极管)to-22 (大功率三极管to-3 (大功率达林顿管5. 端口: I.输入输出端口[AUDIO KB/MS(组合与分立 LAN COM(DB-9RGB(DB-15 LPT DVI USB(常规, 微型 TUNER(高频头 GAME 1394 SATA POWER_JACK等]II. 排针[单排双排 (分不同间距, 不同针脚类型, 不同角度过 IDE FDD, 与其它各类连接排线.III. 插槽 [DDR (DDR分为SMD 与DIP 两类 CPU座 PCIE PCI CNR SD MD CF AGP PCMCIA]6. 开关:I.按键式II. 点按式III. 拔动式IIII. 其它类型7. 晶振: I. 有源晶振 (分为DIP 与SMD 两种包装,一個電源PIN ,一個GND PIN,一個訊號PINII.无源晶振(分为四种包装, 只有接兩個訊號PIN ,另有外売接GND )8. 集成电路IC:I.DIP (Dual In-line Package):双列直插封装。

PADS元件封装制作规范

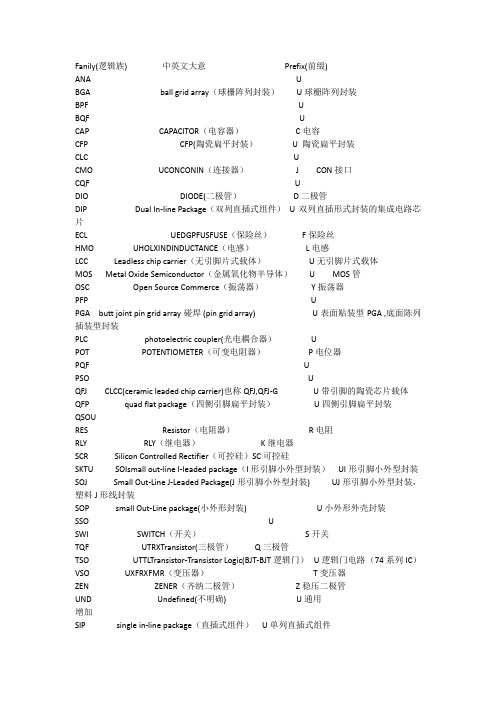

PADS元件封装制作规范1.封装定义元件封装是指为了在PADS电路设计软件中使用,根据元件的实际物理尺寸和引脚数目,制作并定义一个与之匹配的封装。

封装定义必须准确、清晰、规范,以确保在PCB设计过程中元件的正确布局和连接。

2.封装制作流程封装制作的流程一般包括尺寸定义、引脚定义、3D模型制作和封装确认。

2.1尺寸定义尺寸定义是指根据元件的实际物理尺寸,在PADS软件中据此进行封装布局。

尺寸定义需要准确无误,可以通过手动测量或参考元件的数据手册来确定。

2.2引脚定义引脚定义是指根据元件的引脚数目和配置,在PADS软件中定义每个引脚的位置、名称和功能。

引脚定义必须与元件的实际布局一致,并按照标准的命名规范进行命名。

2.33D模型制作3D模型制作是指根据元件的实际物理形状和尺寸,使用CAD软件制作对应的3D模型。

3D模型必须准确无误,并与元件的尺寸定义一致。

在制作时,应考虑元件的所有外部特征,如引脚、引脚间距、体积等。

2.4封装确认封装确认是指将制作好的封装与元件进行比对确认,确保封装的准确性和完整性。

在封装确认过程中,应检查封装的尺寸、引脚定义和3D模型与元件的实际情况是否一致,并进行必要的修正。

3.尺寸规范3.1封装整体尺寸封装的整体尺寸必须与元件的实际尺寸一致,且应考虑到元件的外部特征,如引脚、引脚间距、体积等。

3.2引脚尺寸引脚的尺寸必须与元件的实际引脚尺寸一致,且应考虑到引脚之间的间距和排列方式。

3.3引脚命名引脚的命名应符合标准的命名规范,如1A、2A、1B、2B等。

同时,引脚的方向也需要明确标识,如GND引脚应加以特殊标识。

4.引脚定义规范4.1引脚位置引脚的位置应与元件的实际引脚位置一致,且应按照标准的引脚排列方式进行布局。

4.2引脚功能引脚的功能定义应与元件的实际引脚功能一致,并标注到引脚上。

4.3引脚电性引脚的电性定义应根据元件的实际电性进行标注,如输入、输出、电源、地等。

5.3D模型规范5.13D模型准确性3D模型必须准确无误,并与元件的尺寸定义一致。

pads9元件库建库说明

BAT PARTS BAT

DECALS BEEP

LOGIC

BAT

LINES

BEEP

CAP CONN

BEEP

CAP CAP DB,USB,DIM_SIM_DIM_SCS I_RIM,HD,HDM,IDC,pfb_2m connecotrs m,PHM_2mm,PWC_PMR,PZD ,RJ,SED,SHD,SIP,SMA

物名引脚数_形状+引脚间 距+直径+高度_孔径(单 电池2220座 位) 物名引脚数_形状+长+宽+ 高度_孔径(单位) 物名X2_形状+长+宽+高 度_孔径 MARK TP

ESD

sheetA4_besti sheetA4_syno

说明

battery 电池 buzzer_speaker 蜂鸣器 扬声器 capacitors电容 钽 电解 铝电解 连接器 diodes二极管 有极性的管子 稳压管 TVS bridge 桥 led dpy_seg 数码管 液晶接口 filter 滤波器 fuse 保险丝 ics_module 芯片单个元件 ics_composite 芯片复合元件 inducors 磁珠 电感 MARK_MOUNT_HOLE_MISC 安装孔 定位 孔 光绘点 ESD mesfet 场效应管 audion 三极管 MIC 接口 MOTO 马达接口 triac 可控硅 power_module 电源模块 RES resistors 电阻 RN排阻 DRT电 位器 vsr压敏电阻 shield 屏蔽罩 sence 传感器 SW_DSW 开关 按键 变压器 xtal 晶振类 电路模块 图纸库 LOGO 图标 条形码 天线图 电源符号 引脚 连接符号

PADS元件封装制作规范

PADS元件封装制作规范 PADS元件封装分为5个库:表面贴装(surface)、插入式(through)、连接器(connect)、孔和焊盘(padstacks)及other库(包括管脚、二维线、原理图模板等)。

在以后设计中如遇到库中没有的元件封装,应按以下规范制作,在试用通过后归入相应的元件库中。

一、CAE元件封装制作规则1、CAE元件命名规则常用元件的CAE命名按照表1命名。

特殊元件可用元件名称(元件在ERP中的名称)命名。

表1 常用CAE元件封装命名原理图元件需要具备REF和Value两个属性,REF属性代表元件在原理图中的编号,Value属性对于电阻、电容、电感表示这些元件的标称值,对于其余元件表示为其名称。

REF 和Value属性采用默认值(字体大小100mil,线宽10mil)。

圆点放在元件封装中心。

设计栅格需设为100,具体参数见下图。

这4处的设计值均设置为100二、PCB封装库规则元件PCB封装需具备Name和Value两个属性,分别与原理图封装中REF和Value两个属性对应。

元件PCB封装包括三个部分:封装名称、丝印、焊盘,下面以此分为三部分详述PCB封装库规则。

1、PCB封装库命名规则PCB封装库命名总体上遵守以下规则:一、通用分立元件命名:元件类型简称+元件英制代号(mil)\公制代号(mm)(1mm=39.37mil,1inch=1000mil=25.4mm);二、小外型贴装晶体管命名:元件封装代号;三、集成芯片及接插件命名:元件封装类型+元件参数(包括元件实体尺寸、管脚数、管脚间距、列间距等)。

为方便起见,在元件PCB命名时,元件参数默认采用英制,若采用公制命名,应进行相应的注释;元件管脚间距、列间距采用中心对中心的取值规则;元件实体尺寸表示为元件在PCB板上的占地面积,如右图,元件实体尺寸为16×16mm而不是14×14mm。

特殊元件的PCB封装按PART命名;各元件PCB封装命名详见表2和表3:1)、表面贴装元件(SMD)的命名方法:表2 SMD分立元件的命名方法元件类型简称标准图示命名贴片电阻R 命名方法:元件类型简称+元件英制代号命名举例:R0402,R0603,R0805,R1206, R1210, R2010,R2512。

PADSLOGIC中总体参数的设置

PADSLOGIC中总体参数的设置PADSLOGIC是一款电子设计自动化(EDA)软件,用于电路板设计和布局。

在使用PADSLOGIC时,用户可以根据自己的需要进行一系列参数的设置,以实现其设计需求。

下面是PADSLOGIC中一些常见的总体参数设置。

1.用户界面设置:在PADSLOGIC中,用户可以根据个人喜好设置用户界面的外观和功能。

可以设置菜单显示和工具栏的布局,选择使用的主题和颜色方案等等。

这样可以使用户在使用软件时更加舒适和高效。

2.单位设置:在PADSLOGIC中,用户可以设置使用的单位。

可以选择不同的单位制,如毫米、英寸等。

这样可以确保设计的准确性,并与其他工具和制造流程保持一致。

3.网络设置:在PADSLOGIC中,用户可以设置网络参数,包括网络名称和引脚排列方式。

用户可以修改网络的名称,并选择网络引脚的排序方式,如按名称、引脚号等。

这样可以方便用户对电路进行命名和组织。

4.元器件库设置:在PADSLOGIC中,用户可以设置元器件库的路径和规则。

用户可以添加自定义的元器件库,并设置规则,以便更方便地和引用元器件。

这样可以提高元器件选择和引用的效率。

5.元器件属性设置:在PADSLOGIC中,用户可以设置元器件的属性,如引脚名称、引脚方向、引脚类型等。

用户可以根据自己的设计需求设置元器件属性,以确保设计的准确性和规范性。

6.报表设置:在PADSLOGIC中,用户可以设置生成的报表的格式和内容。

用户可以选择报表的输出格式,如PDF、Excel等,并设置报表的内容,如设计说明、元器件清单等。

这样可以方便用户生成清晰、易读的设计报告。

7.快捷键设置:在PADSLOGIC中,用户可以设置自定义的快捷键。

用户可以根据个人习惯和需求设置快捷键,以快速执行常用的操作。

这样可以提高用户的工作效率和操作速度。

总之,PADSLOGIC提供了丰富的总体参数设置选项,用户可以根据自己的需求进行个性化设置,以满足不同的设计需求和工作习惯。

pads元器件封装端点类型

pads元器件封装端点类型

Pads元器件封装端点类型是指在PCB设计软件Pads中,元器件封装所使用的端点类型。

常见的端点类型有以下几种:

1. Through Hole(通孔型):通过PCB板穿过的端点类型,一般用于DIP封装的元器件。

2. SMD(表面贴装型):直接贴在PCB板表面的端点类型,一般用于SMD封装的元器件。

3. Pad Entry(引脚进入型):引脚从元器件侧面进入,连接到PCB板上的端点类型。

4. Pin Entry(引脚穿过型):引脚从元器件底部进入,穿过PCB 板连接的端点类型。

5. No Connect(未连接型):用于表示某个端点未连接到其他器件或电路。

在Pads中选择正确的元器件封装端点类型,可以有效提高PCB 设计的精度和稳定性,减少出现问题的可能性。

- 1 -。

pads非数字管脚编号

pads非数字管脚编号【最新版】目录1.PADS 简介2.非数字管脚编号的概念3.非数字管脚编号的作用4.非数字管脚编号的应用实例5.结论正文1.PADS 简介PADS(Package for Data Sheet)是一种用于制作电子电路板(PCB)的软件工具,广泛应用于电子设计自动化(EDA)领域。

通过 PADS,设计人员可以轻松地绘制电路图、PCB 布局和进行仿真,以验证设计的正确性。

在 PADS 中,管脚编号对于电路设计和 PCB 布局至关重要。

2.非数字管脚编号的概念在 PADS 中,管脚编号分为数字和非数字两种类型。

数字管脚编号是针对特定器件类型的固定编号,如 CPU 的某个引脚为 A0、A1 等。

而非数字管脚编号则是针对器件的具体功能或特性进行命名,如 VCC、GND 等。

这种编号方式更加灵活,可以适应不同类型的器件和设计需求。

3.非数字管脚编号的作用非数字管脚编号在电路设计和 PCB 布局中具有以下作用:(1)提高设计可读性:非数字管脚编号可以使电路图和 PCB 更加易于阅读和理解,特别是对于复杂的电路设计。

(2)便于修改和维护:非数字管脚编号可以降低由于器件更换或设计修改而导致的编号混乱的风险。

(3)提高设计效率:通过使用非数字管脚编号,设计人员可以更快地完成电路设计和 PCB 布局。

4.非数字管脚编号的应用实例在实际电路设计和 PCB 布局中,非数字管脚编号可以应用于各种不同类型的器件。

例如:(1)电源模块:VCC(正电压)、GND(负电压)、VBAT(电池正极)等。

(2)通信模块:TXD(发送数据)、RXD(接收数据)、CS(片选)等。

(3)传感器模块:SDA(串行数据线)、SCL(串行时钟线)、VIN(电源输入)等。

5.结论非数字管脚编号在 PADS 中具有重要作用,可以提高电路设计和 PCB 布局的可读性、可维护性和设计效率。

元件封装及基本脚位定义说明

元件封裝及基本腳位定義說明PS:以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装.普通的元件封装有针脚式封装(DIP)与表面贴片式封装(SMD)两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

)元件按电气性能分类为:电阻,电容(有极性,无极性),电感,晶体管(二极管,三极管),集成电路IC,端口(输入输出端口,连接器,插槽),开关系列,晶振,OTHER(显示器件,蜂鸣器,传感器,扬声器,受话器)1.电阻: I.直插式[1/20W 1/16W 1/10W 1/8W 1/4W]II.贴片式[0201 0402 0603 0805 1206]III.整合式[0402 0603 4合一或8合一排阻]IIII.可调式[VR1~VR5]2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II.有极性电容分两种:电解电容[一般为铝电解电容,分为DIP与SMD两种]钽电容[为SMD型: A TYPE (3216 10V) B TYPE (3528 16V) C TYPE (6032 25V) D TYPE (7343 35V)]3.电感: I.DIP型电感II.SMD型电感4.晶体管: I.二极管[1N4148 (小功率) 1N4007(大功率) 发光二极管(都分为SMD DIP两大类)]II.三极管[SOT23 SOT223 SOT252 SOT263]5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立) LAN COM(DB-9) RGB(DB-15) LPT DVI USB(常规,微型) TUNER(高频头) GAME 1394 SA TA POWER_JACK等] II.排针[单排双排(分不同间距,不同针脚类型,不同角度)过IDE FDD,与其它各类连接排线.III.插槽[DDR (DDR分为SMD与DIP两类) CPU座PCIE PCI CNR SD MD CF AGP PCMCIA]6.开关:I.按键式II.点按式III.拔动式IIII.其它类型7.晶振: I.有源晶振(分为DIP与SMD两种包装,一個電源PIN,一個GND PIN,一個訊號PIN)II.无源晶振(分为四种包装,只有接兩個訊號PIN,另有外売接GND)8.集成电路IC:I.DIP(Dual In-line Package):双列直插封装。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9.Tristate:三态信号引脚,参考数字电路基础知识。

10.Undefined:没有定义类型。

4.Open Collector:开集电极引脚,三极管集电极没有上拉,参考模拟电路三极管部分,基础知识。

5.Or-Tieable Source:或可连接的源引脚,可以或方式连接在一起的输出信号源,参考数字电路基础知识。

6.Power:电源正。

7.Source:信号源引脚,也就是output,输出信号。

引脚类型一般用在原理图仿真或DRC检查中(pads logic没有DRC检查功能),例如Open Collector没有接上拉电阻,DRC检查就会报错或仿真不正常。

1.Bidirectional:双向引脚,也就是GPIO,具有输入输出功能。

2.Ground收信号。