pc主板常用总线及信号说明

主板上的IO总线

缺省中断设置:(按中断优先级次序排列,二个8259A串联)

IRQ IRQ0 1 2 8 9 10 11 12 13 14 15 3 4 5 6 7 标准功能 系统定时 键盘控制器 内部中断控制器级联,因此下面为另一8259A的中断请求IRQ[8:15] 实时时钟 插卡可用。接原8位ISA槽的IRQ2脚。(现可用于网卡(LAN)) 插卡可用。(现可用于USB) 插卡可用。(现可用于SCSI硬盘卡) PS2鼠标 浮点处理器报错 基本IDE硬盘 第二IDE接口(硬盘或CDROM、磁带机) 串口2(COM2) 串口1(COM1) 并口2(LPT2)(通常用于插卡) 软驱 并口1(LPT1)

2.1

ISA总线信号定义 (续)

– IOCHRDY – 当从设备未准备好传送数据时,变低。使主设备展宽读/写控制波。准备好后 变高,主设备可结束读/写控制信号。 – MEMCS16#、IOCS16# - 为L时,从设备通知主设备/芯片可作 存储器空间、 IO空间的16位访问。 – ZEROWS# - 零等待。从设备通知主设备存储器访问周期(16/8位访问)可缩短到2/3个 SYSCLK周期。也可不用,上拉至高电平。

Page 8

二、ISA(工业标准体系结构)总线

1981年IBM PC引入8位总线;1984年IBM PC/AT扩展到16位 最大标准速度8.33MHz;最高数据传输率8MB/s(最少要用两个周期传二个字节)

ห้องสมุดไป่ตู้2.1 ISA总线信号定义

系统 – SYSCLK (I) – PC/AT时钟,8.33MHz,很少使用(现由PCI时钟四分频)。 – OSC (I) – 14.318MHz 时钟 (三分频为原PC/XT的SYSCLK 4.77MHz) – RESET (I) – 复位 地址/数据 – DATA[15:0] (I/O) –系统数据 – SA[19:0] (I/O) – 系统地址 – LA[23:17] (I/O) – 系统锁存地址(原为非锁存地址,用BALE锁存,现地址锁存器在南桥) – SBHE# (I/O) – 允许传输高字节(16位系统中与SAO一起控制16位/低字节/高字节传送) SA0-SBHE# = 00 传16位;SA0-SBHE# = 01 传低字节;SA0-SBHE# = 10 传高字节。 接口控制 – MEMR#、MEMW#、IOR#、IOW# –访问存储器空间、IO空间的读/写控制,直接控制据传送。 – SMEMR#、SMEMW# - 标准存储器读/写控制。可用于 1MB以下存储空间(00000000 – 000FFFFFh)的访问。分别为MEMR#、MEMW#的延迟(小于16ns) – AEN – 地址允许。DMA传送时用以封锁CPU(南桥)或其它主设备对地址/数据总线的占用。 I/O访问时必需为低(无DMA传送) – BALE – 用于锁存LA[23:17]。BLAE的下降边锁存 (访问存储器空间时,可扩大到16MB)

电脑主板线路图信号解释

I 热断路信号: 当THRMTRIP#信号为低电平型号时,从处理器发出热断路型号,ICH9马上转换为S5状态。ICH9将不等待来自处理器的准予停止的信号返回便进入S5状态。 SLP_S3# O S3 休眠控制信号: SLP_S3# 是电源层控制。

注释: 1. 在正常的三个RTC时钟周期里南桥使电源完全复位并生成完整的PLTRST#信号输出,PWROK必须是最小值处于无效状态。

PWROK必须无假信号,即使RSMRST#是低电平。

控制LINK电源正常信号:当CLPWROK有效时,表示从电源到控制LINK子系统(北桥、南桥等)是稳定的以及通知南桥使CL_RST#无效直到北桥收到这个信号在PWROK有效之后CLPWROK不许有效。

在桌面平台上这个信号能转换成为GPIO信号,这时它就不支持Intel AMT或者ASF。 BATLOW# (仅用于笔记本电脑) / TP0 (仅用于桌面电脑) I 电池低信号: 这个输入信号来自于笔记本电脑的电池组,当电池电量不足以维持系统发出一个信号。该信号有效时它会阻止系统从S3、S4、S5唤醒,也能引起一个SMI# 信号有效。 DPRSLPVR (仅用于笔记本电脑) / GPIO16 O 更深层睡眠-稳压信号:这个信号用于VRM在C4状态下将电压降到更低。当这个信号为高电平,稳压器输出更低的深睡眠电压。该信号为低电平时(默认值为低电平),稳压器输出正常的电压。(稳压器指VRM) DPRSTP# (仅用于笔记本电脑) / TP1 (仅用于桌面电脑) O 深度停机信号:这是DPRSLPVR信号的一个复制,低电平有效。在这1ms内PLT_RST#为低,而正是由于这1ms的低有效,系统才识别到PLT_RST#.该信号会对SIO,FWH,LAN,G(MCH),IDE,TPM等进行reset的动作.也就是说如果该信号异常,这些device都没办法被激活.该信号发出后立刻就会发出PCI_3S_RST#,可以当做是作用相似的第二次reset。

笔记本主板信号详解

一 主板各芯片的功能及名词解释主板芯片组(chipset )(pciset) :分为南桥和北桥:分为南桥和北桥南桥(主外):即系统I/O 芯片(SI/O ):主要管理中低速外部设备;集成了中断控制器、DMA 控制器。

功能如下:功能如下:PCI 、ISA 与IDE 之间的通道。

之间的通道。

PS/2鼠标控制。

(间接属南桥管理,直接属I/O 管理)管理) KB 控制(keyboard )。

(键盘) USB 控制。

(通用串行总线)控制。

(通用串行总线) SYSTEM SYSTEM CLOCK CLOCK 系统时钟控制。

系统时钟控制。

I/O 芯片控制。

芯片控制。

ISA 总线。

总线。

IRQ 控制。

(中断请求)控制。

(中断请求) DMA 控制。

(直接存取)控制。

(直接存取) RTC 控制。

控制。

IDE 的控制。

的控制。

南桥的连接:南桥的连接: ISA ISA——PCI CPU CPU——外设之间的桥梁外设之间的桥梁 内存—外存外存北桥(主内):系统控制芯片,主要负责CPU 与内存、CPU 与AGP 之间的通信。

掌控项目多为高速设备,如:CPU 、Host Host Bus Bus 。

后期北桥集成了内存控制器、Cache 高速控制器;功能如下:高速控制器;功能如下: CPU 与内存之间的交流。

与内存之间的交流。

Cache 控制。

控制。

AGP 控制(图形加速端口)控制(图形加速端口) PCI 总线的控制。

总线的控制。

CPU 与外设之间的交流。

与外设之间的交流。

支持内存的种类及最大容量的控制。

(标示出主板的档次)内存控制器:决定是否读内存(高档板集成于北桥)。

586FX 82438FX VX 82438VX Cache :高速缓冲存储器。

:高速缓冲存储器。

(1)、high high——speed 高速高速 (2)、容量小)、容量小主要用于CPU 与内存北桥之间加速(坏时死机,把高速缓冲关掉)CPU Cache 内 存 I/O 芯片input/output ,(局部I/O )。

了解电脑主板的各种接口及功能

了解电脑主板的各种接口及功能电脑主板是电子设备中的核心组成部分,连接并支持各种硬件设备的正常运行。

了解电脑主板的各种接口及功能对于熟悉电脑内部结构以及维修和升级电脑都非常重要。

本文将介绍常见的电脑主板接口及功能。

一、电源连接接口电脑主板上最重要的接口之一是电源连接接口。

主板上会有一个或多个电源插口,用于接入电脑电源供应器。

常见的主板电源接口有20针和24针两种。

这些接口用于提供电源给主板和其他硬件设备。

二、处理器插槽处理器是电脑主板的核心组件,负责执行各种计算任务。

主板上会有不同类型的处理器插槽,如Intel的LGA插槽和AMD的AM系列插槽。

这些插槽用于安装CPU并与主板上的其他电路链接。

三、内存插槽内存是用于临时存储数据的电子设备,对于电脑系统的性能至关重要。

主板上通常会有多个内存插槽,用于安装内存模块。

常见的内存插槽类型有DIMM和SODIMM,具体插槽类型会根据主板和内存的型号而有所不同。

四、扩展插槽主板上的扩展插槽用于连接额外的硬件设备,如显卡、声卡、无线网卡等。

常见的扩展插槽有PCIe插槽和PCI插槽。

这些插槽通过总线进行数据传输,扩展了电脑的功能和性能。

五、SATA接口SATA接口用于连接硬盘驱动器、光驱和固态硬盘等存储设备。

主板上通常会有多个SATA接口,可以同时连接多个设备。

SATA接口提供了高速数据传输和稳定的连接。

六、USB接口USB接口是电脑中最常用的外部设备连接接口之一。

主板上通常会有多个USB接口,用于连接鼠标、键盘、打印机、摄像头等外部设备。

USB接口具有热插拔和快速传输的特点,方便用户使用各种外部设备。

七、以太网接口以太网接口用于连接电脑和网络,实现网络通信功能。

主板上会有一个或多个以太网接口,可通过网线连接局域网或互联网。

以太网接口支持高速数据传输,使得电脑能够进行网络浏览和在线娱乐。

八、音频接口音频接口用于连接扬声器、麦克风和耳机等音频设备。

主板上会有多个音频接口,用于传输音频信号。

电脑主板常用接口介绍 定义 ps2usb接口网卡串口并口vga针脚定义

电脑主板常用接口介绍定义PS2、USB接口、网卡、串口、并口、VGA针脚定义注意:以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

刚接触电脑的朋友面对着计算机后背那密密麻麻的各种接口和一大把连接线往往会不知所措;接触电脑久的朋友有的时候想搞一些小点子,但常常会找不到各种接口的针脚定义;如果你有以上的经历,那么这一篇文章想必会给您带来一点帮助,那就是外部接口大集合。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

主板重要测试点

主板重要测试点.1 主板总线本节主要介绍主板的总线分类、总线的作用。

读者在使用测试点时,能认识AB、DB、CB 代表的含义就达到学习本节的目的了。

3.1.1 主板总线的分类1.按总线功能分(1)地址总线(AB):用来传递地址信息。

(2)数据总线(DB):用来传递数据信息。

(3)控制总线(CB):用来传送各种控制信号。

下面分别进行介绍。

(1)地址总线AB(Address Bus)是用来传送地址信息的信号线,其特点如下:地址信号一般都由CPU 发出,当采用DMA(Direct Memory Access,即直接内存访问)方式访问内存和I/O 设备时,地址信号也可以由DMA 控制器发生,并被送往各个有关的内存单元或I/O 接口,实现CPU 对内存或I/O 设备的寻址(在PC 中,内存和I/O 设备的寻址都是采用统一编址方式进行的),即采用单向传输。

CPU 能够直接寻找内存地址的范围是由地址线的数目(由于一条地址总线一次传送一位二进制数的地址,故也叫地址总线的位数)决定的,即PC 系统中所能安装内存容量上限由CPU 的地址总线的数目决定。

(2)数据总线DB(Data Bus)是用来传送数据信息的信号线,这些数据信息可以是原始数据或程序。

数据总线来往于CPU、内存和I/O 设备之间,其特点如下:双向传输,三态控制。

既可以由CPU 送往内存或I/O 设备,也可以由内存或I/O 设备送往CPU。

数据总线的数目称为数据宽度(由于一条数据线一次可传送一位二进制数,故也称位数),数据总线宽度决定了CPU 一次传输的数据量,它决定了CPU 的类型与档次。

(3)控制总线CB(Control Bus)是用来传送控制信息的信号线,这些控制信息包括CPU 对内存和I/O 接口的读写信号、I/O 接口对CPU 提出的中断请求或DMA 请求信号、CPU 对这些I/O 接口回答与响应的信号、I/O 接口的各种工作状态信号以及其他各种功能控制信号。

pc总线分类

pc总线分类在计算机领域中,总线(Bus)是连接计算机内部各个组件的通信线路。

它能够传输数据、地址和控制信号,是计算机系统中至关重要的一部分。

根据其功能和结构的不同,PC总线可以分为三类:系统总线、扩展总线和局部总线。

一、系统总线系统总线是计算机中性能最高、传输速度最快的总线。

它主要用于处理器与内存之间的数据传输,分为前端总线和后端总线。

1. 前端总线前端总线是连接处理器与内存、输入输出设备之间的总线。

它承担着处理器与其他组件之间数据和控制信息的传递任务。

前端总线通常由数据总线、地址总线和控制总线组成。

- 数据总线:用于传输数据信息,在32位的计算机中一般为32根。

数据总线的宽度决定了处理器与其他组件之间数据传输的速度。

- 地址总线:用于传输内存地址信息,决定了计算机可寻址的内存空间大小。

在32位系统中,地址总线通常为32根,能够访问的内存空间为2^32字节(4GB)。

- 控制总线:用于传输各种控制信号,如读写控制、中断请求等。

控制总线的具体信号由计算机体系结构决定。

2. 后端总线后端总线是连接处理器与主板芯片组之间的总线。

它负责将前端总线传输过来的数据和控制信号转化为主板芯片组所支持的格式,使其能够被主板上其他芯片所使用。

二、扩展总线扩展总线是计算机中用于连接扩展插件卡的总线。

它允许用户根据个人需求对计算机进行功能扩展。

常见的扩展总线有ISA总线、PCI总线、AGP总线和PCI Express总线等。

1. ISA总线ISA总线(Industry Standard Architecture Bus)是较早期的一种扩展总线,用于连接低速外设。

由于其传输速度较慢,已逐渐被后来的总线所取代。

2. PCI总线PCI总线(Peripheral Component Interconnect Bus)是一种高速的扩展总线,具有较大的带宽和较快的传输速度。

它广泛应用于连接多种外部设备,如显卡、声卡和网卡等。

3. AGP总线AGP总线(Accelerated Graphics Port Bus)是专门用于连接显卡的扩展总线。

19-20主板总线

64位扩展

接口控制

PCI COMPLIANT DEVICE

接口控制

出错报告

中断

仲裁

(主设备有效)

系统

TDI TDO TCK TMS TRST#

JTAG

(IEEE 1149.1)

∗ 信号定义: ∗ 32bit PCI系统的管脚按功能来分有以下几类: 系统控制: CLK:PCI时钟,上升沿有效 RST# :Reset信号 传输控制: FRAME#:标志传输开始与结束 IRDY#:Master可以传输数据的标志 DEVSEL#:当Slave发现自己被寻址时置低应答 TRDY#:Slave可以转输数据的标志 STOP#:Slave主动结束传输数据的信号 IDSEL:在即插即用系统启动时用于选中板卡的信号 地址与数据总线: AD[31::0]:地址/数据分时复用总线 C/BE#[3::0]:命今/字节使能信号 PAR:奇偶校验信号 仲裁号: REQ#:Master用来请求总线使用权的信号 GNT#:Arbiter允许Master得到总线使用权的信号 错误报告: PERR#:数据奇偶校验错 SERR#:系统奇偶校验错

主板总线

∗ 总线的定义和功能 ∗ 总线是连接计算机有关部件的一组信号线,是主板用来传送信息代码的公共通 路 ∗ 总线不公是一组传输线,它还包括与信息代码传送有关的控制信号 ∗ 总线的类型 ∗ 内部总线:在CPU内部,寄存器之间和算术逻辑部件与控制部件这间传输信号 所用的总线。 ∗ 外部总线:指CPU与内存RAM、ROM和输入/输出设备接口之间进行通信的总线, 如FSB、PCI、AGP。 ∗ 总线按功能分为 ∗ 地址总线(Address Bus):用来传送地址信息 ∗ 数据总线(Data Bus):用来传送数据信息。 ∗ 控制总线(Control Bus):用来传送各种控制信号。

主板总线类型

I/O总线类型总线是计算机系统中各个部件之间传输各种信息的公共通路。

微机总线按用途可分为四类信号线:①数据/地址分时复用线:分别决定传输数据的宽度和直接寻址的范围。

②控制、中断和时序信号线:决定总线功能的强弱及适应性的好坏。

③电源线、地线:决定电源的种类和地线的分布与用法。

④备用线:厂家或用户用作性能扩充或特殊要求的信号线。

微机总线按功能和规范可分为三类信号线:①片总线:又称元件级总线,位于芯片内部,把各种不同元件连接在一起构成不同功能插件的所有信号线或连接线,如CPU 内部寄存器与ALU之间的通路。

②内部总线:又称系统总线、板级总线,位于设备内部各插件板之间的连接通路,用来连接CPU、内存和I/O接口电路的信号线。

局部总线:各插件板(包括主板)通常也是一个完整的子系统,板上含有CPU、RAM、ROM、I/O接口芯片等功能电路,这些部件(芯片)之间的信息传送通路称为局部总线,如CPU与外设之间的PCI连接总线。

③外部总线:又称通信总线、设备级总线,位于机箱或板卡外部,是用来连接计算机系统的两个主要部件的通路,如主板与键盘、显示器、硬盘等设备之间的通路。

不论哪一类总线又分为三种总线:①数据总线:用来传输数据信号的三态控制(总线逻辑电路的输出电平的三种状态,逻辑0、逻辑1、高阻)双向总线。

CPU 内部数据总线的宽度(位数)决定了CPU处理数据的能力;CPU 外部数据总线(系统总线)的宽度决定了CPU与外界传输数据的能力。

②地址总线:只由CPU发出存储器单元地址或I/O端口地址时所使用的三态控制单向总线,其宽度(位数)决定了CPU访问存储器或外设的能力。

③控制总线:为协调微机各部件同步动作而传输各种命令信号的三态控制单/双向总线,没有位数。

按主板总线(扩展槽)的发展历史和连接结构,可分为以下6种类型。

⑴ PC总线:用于以8088为CPU的IBM PC/XT机,又称XT总线;总线工作频率4.77MHz;总线宽度8位;数据传输速率2.38MBPS;扩展槽有62个引脚(线);把CPU视为总线的唯一主控设备来传输数据。

计算机三大总线举例(全)

内部总线、系统总线及外部总线举例一、内部总线1.I2C总线I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。

它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。

在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。

2.SPI总线串行外围设备接口SPI(serialperipheral interface)总线技术是Motorola 公司推出的一种同步串行接口。

Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。

SPI总线是一种三线同步总线,因其硬件功能很强,所以,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。

3.SCI总线串行通信接口SCI(serialcommunication interface)也是由Motorola公司推出的。

它是一种通用异步通信接口UART,与MCS-51的异步通信功能基本相同。

二、系统总线1.ISA总线ISA(industrial standard architecture)总线标准是IBM公司1984年为推出PC/AT机而建立的系统总线标准,所以也叫AT总线。

它是对XT总线的扩展,以适应8/16位数据总线要求。

它在80286至80486时代应用非常广泛,以至于现在奔腾机中还保留有ISA总线插槽。

ISA总线有98只引脚。

2.EISA总线EISA总线是1988年由Compaq等9家公司联合推出的总线标准。

它是在ISA 总线的基础上使用双层插座,在原来ISA总线的98条信号线上又增加了98条信号线,也就是在两条ISA信号线之间添加一条EISA信号线。

在实用中,EISA总线完全兼容ISA总线信号。

3.VESA总线VESA(video electronics standard association)总线是 1992年由60家附件卡制造商联合推出的一种局部总线,简称为VL(VESA local bus)总线。

主板上各种信号说明

主板上各种信号说明一、CPU接口信号说明1. A[31:3]# I/O Address(地址总线)ν这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2. A20M# I Adress-20 Mask(地址位20屏蔽)ν此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3. ADS# I/O Address Strobe(地址选通)ν当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4. ADSTB[1:0]# I/O Address Strobesν这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5. AP[1:0]# I/O Address Parity(地址奇偶校验)ν这两个信号主要用对地址总线的数据进行奇偶校验。

6. BCLK[1:0] I Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

ν7. BNR# I/O Block Next Request(下一块请求)ν这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8. BPRI# I Bus Priority Request(总线优先权请求)ν这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。

解刨主板系统总线

主版上的系统总线 (续)

系统总线构成:

系统I/O总线是数据、地址和控制总线的总称。

• 数据总线传送的是数据信号,双向。系统总线的宽度是 指其数据线的位数。

• 地址总线传送的是内存(或I/O接口)的地址信号,单向。 它的线数与系统采用的CPU的地址线宽度一致,它决定了 CPU直接寻址的内存容量。

• 控制总线是CPU和其它控制芯片发出的各种控制信号。

主版上的系统总线 (续)

系统总线构成:(续)

系统中的各个局部电路均需通过它互相连接, 实现了全系统电路的互连。在主板上,系统I/O总线还 连接到一些特定的插槽上去对外开放,以便于外部的 各种扩展电路板连入系统。插座被称为系统I/O总线扩 展插槽(System Input/Output Bus Expanded Slot)。 系统I/O总线的示意图如图6-1。

主板上的系统总线 (续)

总线分类

1.片内总线:片内总线也称为CPU总线。它 位于CPU处理器内部,是CPU内部各功能单元之 间的连线,片内总线通过CPU的引脚延伸到外 部与系统相连。

2.片间总线:片间总线也称为局部总线 (Local BUS)。它是主板上CPU与其它一些部 件间直接连接的总线。

主版上的系统总线 (续)

总线分类 (续)

3.系统总线:系统总线也称为系统I/O总线 (System I/O Bus)。是系统各个部件连接的主要通道, 它具有不同标准的总线扩展插槽对外部开放以便各种 系统功能扩展卡插入相应的总线插槽与系统连接。

4.外部总线:外部总线也称为通信总线。它是电 脑与电脑之间数据通信的连线,如RS-232C、IE1364标 准等。

主板上的系统总线 (续)

总线原理 (续)

系统处理各种信息,实际上就是处理一组组二进制 数,进一步说,就是在总线上不断传送高、低电平信号。

主板上各种信号说明

主板上各种信号说明一、CPU接口信号说明1. A[31:3]# I/O Address(地址总线)ν这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2. A20M# I Adress-20 Mask(地址位20屏蔽)ν此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3. ADS# I/O Address Strobe(地址选通)ν当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4. ADSTB[1:0]# I/O Address Strobesν这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5. AP[1:0]# I/O Address Parity(地址奇偶校验)ν这两个信号主要用对地址总线的数据进行奇偶校验。

6. BCLK[1:0] I Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

ν7. BNR# I/O Block Next Request(下一块请求)ν这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8. BPRI# I Bus Priority Request(总线优先权请求)ν这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。

电脑主板常见信号功能解释

电脑主板常见信号功能解释VCCRTC 实时时钟供电,(VBAT),电池+跑线,经过1k(有点板不是)电阻,到达二极管+,从-出来RTCRST# 实时时钟复位这两步满足后产生晶振32.768KHZ 晶振这三步没上ATX,都有V5REF-SUS 5V待机电压,主用于USB和键盘VCCSUS3-3 SB的3.3V待机电压(经1117,1084等转换而来)PCI 14脚.RSMRST# 待机电压好信号,正常工作为高电平,(低电平引起不开机)PWRBTN# 1 电源开关,送到南桥SLP-S5# 2 南桥发出 3 PS_ON# 这三个为开机信号SLP-S4# 2 南桥发出SLP-S3# 2 南桥发出三个S#有一个是开启内存供电的VDIMM 内存供电VCOREVCC CPU的核心电压,VRMPWRGD CPU供电好信号,当CPU供电电压值正常后,供电电源芯片发出高电平送到SB,用于SB内部产生CPUPWRGD和PLTRST#的重要条件.CLKCEN 时钟开启信号,用于开启时钟芯片工作,SB收到VRMPWRGD后发出高电平开启时钟PWROK 电源好信号,ATX电源供电正常后发出灰色线PG5V,经门电路,IO,后发送到SB,通知SB各路供电已正常CPUPWRGD cpu电源好信号,由SB发送到CPU,是CPU工作PLTRST# 平台复位/总复位,SB供电,时钟正常并收到两个PG信号后将PLTRST#置高发送到NB,IO(两个PG指PWROK,VRMPWRGD) PCIRST# PCI设备复位信号,PLTRST#在SB内部延时后发出到各个PCI设备,正常3.3V,在A15脚测量CPURST# 1.2V左右,由北桥收到PLTRST#产生,(NB没复位。

CPU就没有复位)INTEL的上电流程(五大待机条件和三大信号)VCCRTC--RTCRST#--32.768KHZ--3VSB(插电源5VSB-3VSB)--RSMRST#--PWRBTN#--SLP_S3#--PS_ON#--ATX输出5V,3V.12V.....待机时VCCRTC 3V 高电平RTCRST# 3V 高电平32.768KHZ--3VSB(插电源5VSB-3VSB)--RSMRST# 3V 高电平 !开机触发 PWRBTN# 高--低--高 SLP_S3# 低--高 PS_ON# 高--低ATX输出5V,3V.12V.....。

笔记本主板各种信号说明

笔记本信号笔记本主板各种信号说明(其余的烦请各位达人继续补充,或者有什么错误的请指教)很多的人在看笔记本图纸时,对里面的各种代号,弄不清楚!其实这些都是英文缩写!首先说ALW,它的英文全称是Alway,意思是总是,如+5V ALW,它用在当电源插上后,这个电压就应该都有的,所以我们在插上电源后,只有是ALW,不管是3V ALW,还是5V ALW,只要是ALW,都应该有它相应的电压,它是给开机电路用的,如EC等。

其次是SUS,它的英文全称是Suspend,意思是延缓,挂起的意思,如+3VSUS(SLP_S5# CTRLD POWER这些将在上电时序中讲解)它的电压产生实在ALW的电压后面,当接收到SUS_on控制电压后就会产生此一系列的电压,此电压不是主要供给电压,只是为下一步的电压产生提供铺垫,但不代表这电压不重要,没有SUS电压,后面的电压就不会产生。

再次是RUN电压,RUN电压没有缩写,它的意思就是跑、运行的意思,这个才是南北桥工作的主要电压,当然南北桥也需要SUS电压。

系统真正运行的话就需要RUN电压正常,如果RUN电压不稳定会造成主板的不稳定。

PL TRST#总复位信号: PLTRST#是Intel® ICH9整个平台的总复位(如:I/O、BIOS芯片、网卡、北桥等等)。

在加电期间及当S/W信号通过复位控制寄存器(I/O 寄存器CF9h)初始化一个硬复位序列时ICH9确定PL TRST#的状态。

在PWROK和VRMPWRGD为高电平之后ICH9驱动PL TRST#最少1毫秒是无效的。

当初始化通过复位控制寄存器(I/O 寄存器CF9h)时ICH9驱动PL TRST#至少1毫秒是有效的。

注释: 只有VccSus3_3正常时PL TRST#这个信号才起作用.THRM# 热报警信号:激活THRM#为低电平信号使外部硬件去产生一个SMI#或者SCI 信号THRMTRIP#热断路信号: 当THRMTRIP#信号为低电平型号时,从处理器发出热断路型号,ICH9马上转换为S5状态。

「电脑主板全部接口详解」电脑主板所有接口类型和功能,如何插线

「电脑主板全部接口详解」电脑主板所有接口类型和功能,如何插线前言:观众朋友们大家好!这里是【装机查馆】。

这期我将详细讲解电脑主板上的所有不同连接部位,这些连接的作用,以及如何插入它们?知识很多,考虑到观众朋友们一次性不能耐心看完,这里先放一个【主板详解图】建议收藏文章,慢慢学习。

主板手册首先主板的盒子都会有手册,其中有图表标注主板上的所有的连接位置。

你也可以通过主板制造商的网站下载一份副本。

那么开始我们今天的讲解:01、主板电源接口:主板电源接口主板电源接口大小有:24 Pin(针)或者20 Pin(针)。

20 Pin接口是很旧的电脑才有的,现在大多数电源都有一个24 Pin连接器。

他可以分为4 Pin和20 Pin插头。

现在主板上几乎每个接口都有正反和防呆设计,这就可以让你不可能出现错误的方式连接,除非你在插拔时力气很大。

在我们插入这个电源接口时,你会发现主板上的接口有一个小凹口,对准插头的钩,插上ATX电源接口。

02、CPU电源接口:CPU电源接口主板上另一个为4 Pin、8 Pin、12 Pin、或者是16 Pin的接口,则为CPU供电的接口。

在电源上找到标有CPU的插头,采用ATX电源接口同样的方式,插在接口上。

03、显卡电源接口:显卡显示卡,俗称显卡。

一般配置6 Pin或者8 Pin的电源连接。

我们先以此处的电源连接头为例,可以看到连接头可以分为6 Pin连接头,也可以组成8 Pin连接头。

有些显卡并不需要额外的连接。

显卡供电接口6Pin或者8Pin04、硬盘、机箱风扇、灯带接口:给其他设备供电,电源还配备了多个molex 和sata 供电线。

Molex连接器有四个引脚,而Sata连接器有15个引脚。

Sata中更多的引脚是为了能够支持热插拔设备等附加功能。

Sata连接器头设置为L型,而Molex也设计为只能一种方式插入。

然而,Sata连接器往往主要用于Sata硬盘,Molex连接器最初主要用于硬盘,但现在用于其他设备,例如机箱风扇、灯带等。

计算机PCI总线及设备介绍

回顾总线的发展历程 (PCI总线危机)

危机产生

• 利用PCI 总线技术的显示卡,第一次真正地实 现了多媒体效果,并且可以支持增强色和真彩色 等色彩模式,这与当时只能支持256色的VESA VLB 显示卡相比,简直是不可思义。 • 如果计算机只需要进行上网浏览和软件下载等 简单的应用,PCI 技术也就足够了。然而时光飞 逝,转眼就到了2004年,新的技术和设备层出不 穷,特别是游戏和多媒体应用越来越广泛,PCI 的工作频率和带宽都已经无法满足需求。此外, PCI 还存在IRQ 共享冲突,只能支持有限数量设 备等问题。

• 总线分类

– 局部总线 – 系统总线 – 通信总线

在以Windows为代表的图形用户接口(GUI)进入PC机之 后,要求有高速的图形描绘能力和I/O处理能力。这不仅要求 图形适配卡要改善其性能,也对总线的速度提出了挑战。实 际上当时外设的速度已有了很大的提高,如硬磁盘与控制器 之间的数据传输率已达10MB/s以上,图形控制器和显示器之 间的数据传输率也达到69MB/s。通常认为I/O总线的速度应 为外设速度的3~5倍。因此原有的ISA、EISA已远远不能适 应要求,而成为整个系统的主要瓶颈。 局部总线是PC体系结构的重大发展。它打破了数据I/O 的瓶颈,使高性能CPU的功能得以充分发挥。从结构上看, 所谓局部总线是在ISA总线和CPU总线之间增加的一级总线 或管理层。这样可将一些高速外设,如图形卡、硬盘控制器 等从ISA总线上卸下而通过局部总线直接挂接到CPU总线上, 使之与高速的CPU总线相匹配。 采用PCI总线后,数据宽度升级到64位,总线工频率为 33.3MHZ,数据传输率(带宽)达266MB/S。所以采用PCI 总线解决了数据的I/O瓶颈,使计算机更好地发挥性能。 这是微机系统内部各部件(插板)之间进行连接和传输 信息的一组信号线。例如ISA总线。由于它只具有16位数据 宽度,最高工作频率为8MHz,所以数据传输速率只能达到 16MB/S。 通信总线是系统之间或微机系统与设备之间进行通信的 一组信号线。

电脑主板接线知识图文详解

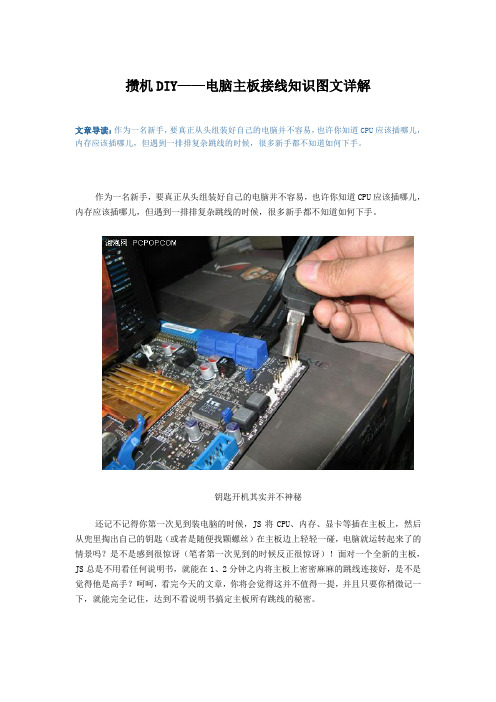

攒机DIY——电脑主板接线知识图文详解文章导读:作为一名新手,要真正从头组装好自己的电脑并不容易,也许你知道CPU应该插哪儿,内存应该插哪儿,但遇到一排排复杂跳线的时候,很多新手都不知道如何下手。

作为一名新手,要真正从头组装好自己的电脑并不容易,也许你知道CPU应该插哪儿,内存应该插哪儿,但遇到一排排复杂跳线的时候,很多新手都不知道如何下手。

钥匙开机其实并不神秘还记不记得你第一次见到装电脑的时候,JS将CPU、内存、显卡等插在主板上,然后从兜里掏出自己的钥匙(或者是随便找颗螺丝)在主板边上轻轻一碰,电脑就运转起来了的情景吗?是不是感到很惊讶(笔者第一次见到的时候反正很惊讶)!面对一个全新的主板,JS总是不用看任何说明书,就能在1、2分钟之内将主板上密密麻麻的跳线连接好,是不是觉得他是高手?呵呵,看完今天的文章,你将会觉得这并不值得一提,并且只要你稍微记一下,就能完全记住,达到不看说明书搞定主板所有跳线的秘密。

C/W这个叫做真正的跳线首先我们来更正一个概念性的问题,实际上主板上那一排排需要连线的插针并不叫做“跳线”,因为它们根本达不”到跳线的功能。

真正的跳线是两根/三根插针,上面有一个小小的“跳线冒”那种才应该叫做“跳线”,它能起到硬件改变设置、频率等的作用;而与机箱连线的那些插针根本起不到这个作用,所以真正意义上它们应该叫做面板连接插针,不过由于和“跳线”从外观上区别不大,所以我们也就经常管它们叫做“跳线”。

看完本文,连接这一大把的线都会变得非常轻松至于到底是谁第一次管面板连接插针叫做“跳线”的人,相信谁也确定不了。

不过既然都这么叫了,大家也都习惯了,我们也就不追究这些,所以在本文里,我们姑且管面板连接插针叫做跳线吧。

为了更加方便理解,我们先从机箱里的连接线说起。

一般来说,机箱里的连接线上都采用了文字来对每组连接线的定义进行了标注,但是怎么识别这些标注,这是我们要解决的第一个问题。

实际上,这些线上的标注都是相关英文的缩写,并不难记。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主板上各种信号说明目录一、CPU接口信号说明(1#)二、VGA接口信号说明(2#)三、AGP接口信号说明(2#)四、Memory 接口信号说明(3#)五、HUB 接口信号说明(4#)六、LAN LINK接口信号说明(4#)七、EEPROM 接口信号说明(4#)八、PCI接口信号说明(5#)九、Serial ATA接口信号说明(6#)十、IDE 接口信号说明(6#)十一、LPC接口信号说明(7#)十二、USB 接口信号说明(7#)十三、SMBus接口信号说明(7#)十四、AC-Link接口信号说明(7#)十五、FDC接口信号说明(8#)十六、Parallel Port 接口信号说明(9#)十七、Serial Port 接口数据说明(9#)一、CPU接口信号说明1.A[31:3]# (I/O) Address(地址总线)这组地址信号定义了CPU的最大内存寻址空间为4GB。

在地址周期的第一个子周期中,这些Pin传输的是交易的地址,在地址周期的第二个子周期中,这些Pin传输的是这个交易的信息类型。

2.A20M# (I) Adress-20 Mask(地址位20屏蔽)此信号由ICH(南桥)输出至CPU的信号。

它是让CPU在Real Mode(真实模式)时仿真8086只有1M Byte(1兆字节)地址空间,当超过1 Mbyte位空间时A20M#为Low,A20被驱动为0而使地址自动折返到第一个1Mbyte地址空间上。

3.ADS# (I/O) Address Strobe(地址选通)当这个信号被宣称时说明在地址信号上的数据是有效的。

在一个新的交易中,所有Bus上的信号都在监控ADS#是否有效,一但ADS#有效,它们将会作一些相应的动作,如:奇偶检查、协义检查、地址译码等操作。

4.ADSTB[1:0]# (I/O) Address Strobes这两个信号主要用于锁定A[31:3]#和REQ[4:0]#在它们的上升沿和下降沿。

相应的ADSTB0#负责REQ[4:0]#和A[16:3]#,ADSTB1#负责A[31:17]#。

5.AP[1:0]# (I/O) Address Parity(地址奇偶校验)这两个信号主要用对地址总线的数据进行奇偶校验。

6.BCLK[1:0] (I) Bus Clock(总线时钟)这两个Clock主要用于供应在Host Bus上进行交易所需的Clock。

7.BNR# (I/O) Block Next Request(下一块请求)这个信号主要用于宣称一个总线的延迟通过任一个总线代理,在这个期间,当前总线的拥有者不能做任何一个新的交易。

8.BPRI# (I) Bus Priority Request(总线优先权请求)这个信号主要用于对系统总线使用权的仲裁,它必须被连接到系统总线的适当Pin 。

当BPRI#有效时,所有其它的设备都要停止发出新的请求,除非这个请求正在被锁定。

总线所有者要始终保持BPRI#为有效,直到所有的请求都完成才释放总线的控制权。

9.BSEL[1:0] (I/O) Bus Select(总线选择)这两组信号主要用于选择CPU所需的频率,下表定义了所选的频率:10.D[63:0]# (I/O) Data(数据总线)这些信号线是数据总线主要负责传输数据。

它们提供了CPU与NB(北桥)之间64 Bit的通道。

只有当DRDY#为Low时,总在线的数据才为有效,否则视为无效数据。

11.DBI[3:0]# (I/O) Data Bus Inversion(数据总线倒置)这些信号主要用于指示数据总线的极性,当数据总在线的数据反向时,这些信号应为Low。

这四个信号每个各负责16个数据总线,见下表:12.DBSY# (I/O) Data Bus Busy(数据总线忙)当总线拥有者在使用总线时,会驱动DBSY#为Low表示总线在忙。

当DBSY#为High时,数据总线被释放。

13.DP[3:0]# (I/O) Data Parity(数据奇偶校验)这四个信号主要用于对数据总在线的数据进行奇偶校验。

14.DRDY# (I/O) Data Ready(数据准备)当DRDY#为Low时,指示当前数据总在线的数据是有效的,若为High时,则总在线的数据为无效。

15.DSTBN[3:0]# (I/O) Data StrobeData strobe used to latch in D[63:0]# :16.DSTBP[3:0]# (I/O) Data StrobeData strobe used to latch inn D[63:0]# :17.FERR# (O) Floating Point Error(浮点错误)这个信号为一CPU输出至ICH(南桥)的信号。

当CPU内部浮点运算器发生一个不可遮蔽的浮点运算错误时,FERR#被CPU驱动为Low。

18.GTLREF (I) GTL Reference(GTL参考电压)这个信号用于设定GTLn Bus的参考电压,这个信号一般被设为Vcc电压的三分之二。

19.IGNNE# (I) Ignore Numeric Error(忽略数值错误)这个信号为一ICH输出至CPU的信号。

当CPU出现浮点运算错误时需要此信号响应CPU。

IGNNE#为Low时,CPU会忽略任何已发生但尚未处理的不可遮蔽的浮点运算错误。

但若IGNNE#为High时,又有错误存在时,若下一个浮点指令是FINIT、FCLEX、FSAVE等浮点指令中之一时,CPU会继续执行这个浮点指令但若指令不是上述指令时CPU会停止执行而等待外部中断来处理这个错误。

20.INIT# (I) Initialization(初始化)这个信号为一由ICH输出至CPU的信号,与Reset功能上非常类似,但与Reset不同的是CPU内部L1 Cache和浮点运算操作状态并没被无效化。

但TLB (地址转换参考缓存器)与BTB(分歧地址缓存器)内数据则被无效化了。

INIT #另一点与Reset不同的是CPU必须等到在指令与指令之间的空档才会被确认,而使CPU进入启始状态。

21.INTR (I) Processor Interrupt(可遮蔽式中断)这个信号为一由ICH输出对CPU提出中断要求的信号,外围设备需要处理数据时,对中断控制器提出中断要求,当CPU侦测到INTR为High时,CPU先完成正在执行的总线周期,然后才开始处理INTR中断要求。

22.PROCHOT# (I/O) Processor Hot(CPU过温指示)当CPU的温度传感器侦测到CPU的温度超过它设定的最高度温度时,这个信号将会变Low,相应的CPU的温度控制电路就会动作。

23.PWRGOOD (I) Power Good(电源OK)这个信号通常由ICH(南桥)发给CPU,来告诉CPU电源已OK,若这个信号没有供到CPU,CPU将不能动作。

24.REQ[4:0]# (I/O) Command Request(命令请求)这些信号由CPU接到NB(北桥),当总线拥有者开始一个新的交易时,由它来定义交易的命令。

25.RESET# (I) Reset(重置信号)当Reset为High时CPU内部被重置到一个已知的状态并且开始从地址0FFFFFFF0H读取重置后的第一个指令。

CPU内部的TLB(地址转换参考缓存器)、BTB(分歧地址缓存器)以及SDC(区段地址转换高速缓存)当重置发生时内部数据全部都变成无效。

26.RS[2:0]# (I) Response Status(响应状态)这些信号由响应方来驱动,具体含义请看下表:27.STKOCC# (O) Socket Occupied(CPU插入)这个信号一般由CPU拉到地,在主机板上的作用主要是来告诉主机板CPU 是不是第一次插入。

若是第一次插入它会让你进CMOS对CPU进行重新设定。

28.SMI# (I) System Management Interrupt(系统管理中断)此信号为一由ICH输出至CPU的信号,当CPU侦测到SMI#为Low时,即进入SMM模式(系统管理模式)并到SMRAM(System Management RAM)中读取SMI #处理程序,当CPU在SMM模式时NMI、INTR及SMI#中断信号都被遮蔽掉,必需等到CPU执行RSM(Resume)指令后SMI#、NMI及INTR中断信号才会被CPU认可。

30.STPCLK# (I) Stop Clock(停止时钟)当CPU进入省电模式时,ICH(南桥)将发出这个信号给CPU,让它把它的Clock停止。

31.TRDY# (I/O) Target Ready(目标准备)当TRDY#为Low时,表示目标已经准备好,可以接收数据。

当为High时,Target没有准备好。

32.VID[4:0] (O) Voltage ID(电压识别)这些讯号主要用于设定CPU的工作电压,在主机板中这些信号必须被提升到最高3V。

1.HSYNC (O) CRT Horizontal Synchronization(水平同步信号)这个信号主要提供CRT水平扫描的信号。

2.VSYNC (O) CRT Vertical Synchronization(垂直同步信号)这个信号主要提供CRT垂直扫描的信号。

3.RED (O) RED analog video output(红色模拟信号输出)这个信号主要为CRT提供红基色模拟视频信号。

4.GREEN (O) Green analog video output(绿色模拟信号输出)这个信号主要为CRT提供绿基色模拟视频信号。

5.BLUE (O) Blue analog video output(蓝色模拟信号输出)这个信号主要为CRT提供蓝基色模拟视频信号。

6.REFSET (I) Resistor Set(电阻设置)这个信号将会连接一颗电阻到地,主要用于内部颜色调色板DAC。

这颗电阻的阻值一般为169奥姆,精度为1%。

7.DDCA_CLK (I/O) Analog DDC Clock这个信号连接NB(北桥)与显示器,这个Clock属于I²C接口,它与DDCA_DATA组合使用,用于读取显示器的数据。

8.DDCA_DATA (I/O) Analog DDC Clock这个信号连接NB(北桥)与显示器,这个Data与Clock 一样也属于I²C接口,它与DDCA_CLK组合使用,用于读取显示器的数据。

1.GPIPE# (I/O) Pipelined Read(流水线读)这个信号由当前的Master来执行,它可以使用在AGP 2.0模式,但不能在AGP 3.0的规范使用。