第7章多处理机

计算机体系结构-第7章 多处理机

第7章 多处理机

主 CPU

主存

CIOP

高速系统总线 BIOP NIOP GIOP

ACOP

CIOP----字符处理机 BIOP----数组处理机 NIOP----网络处理机 GIOP----图形处理机 ACOP----向量加速处理机

图7.5 异构非对称式多处理机的一般结构

第7章 多处理机

2. 松耦合(loosely coupled)多处理机 松耦合多处理机是通过消息传递方式来实现处理机间的相互通 信的。 而每台处理机是由一个独立性较强的计算机模块组成,该模 块由处理器、较大容量的本地存储器(在运算时所需的绝大部分的 指 令 和 数 据 均 取 自 本 地 存 储 器 ) 、 I/O 设 备 以 及 与 消 息 传 递 系 统 (Message Transfer System,MTS)相连的接口组成。当不同模块上 运行的进程间需要通信时,可通过网络接口电路及消息传递系统 进行信息交换。由于这种相互间的耦合程度是很松散的,因此称 之为松耦合多处理机。 松耦合多处理机可分为非层次式和层次式两种结构。

第7章 多处理机

(5)合理地进行资源分配和任务调度。 在MIMD多处理机中,由于任务的大小不相同, 各处理机的速度也可能不相同(如异构型多处理机系统), 互连网络的拓扑结构和通信延迟在不同的多处理机中 也有很大的差别,在执行并发任务时,并不是使用的 处理机个数越多,系统获得的性能就越高。因此需要 采用软件手段,合理地进行资源分配和任务调度,否 则系统性能将受较大影响。而在SIMD并行处理机中, 程序员只需用屏蔽的手段来设置部分处理单元为不活 跃状态,来控制实际参加并行操作的处理单元数目。

因此,Cm*是一个三层总线多处理机,三级的访 存时间分别为:计算机模块内3.5μs,计算机模块群内 9.3μs,而群间则为26μs。

第 7 章 并行处理技术

阵列机特征的形式化表示

• SIMD计算机的操作模型可用五元组表示: • C=<N,C,I,M,R> • 式中: (1) N为机器的处理单元(PE)数。 例如,Illiac IV有64个PE。而连接机 (Connection Machine) CM-2采用65536个PE。 (2) C为由控制部件(CU)直接执行的指令集, 包括标量和程序流控制指令。

• 粗粒度-MIMD方式 (G↗) • 细粒度-SIMD方式 (G↘)

2014-4-22 7

7.2

阵列处理机(SIMD并行计算机)

• 并行计算机的定义 • 并行计算机就是由多个处理单元PE(以下也 称为处理器,或简称为CPU)组成的计算机 系统,这些处理单元相互通信和协作能快 速、高效的求解大型复杂问题。 • 下图给出了从标量到向量和并行计算机的 演变 。

2014-4-22 5

(3)子任务级:属于中粒度。子程序是在单处理机 或多处理机的多道程序设计这一级进行的。这一 级并行性由算法设计者或程序员开发而非用编译 器开发。 (4)任务级:这是与任务、过程、程序段、协同程 序级相对应的中粒度或粗粒度规模。典型粒度包 含的指令几千条,检测本级的并行性比细粒度级 困难得多,需要更多地涉及过程间的相关性分析。 需编译器支持。

2014-4-22

26

7.2.4 典型SIMD计算机举例

• 一、Illiac-IV SIMD阵列机 • 它是由Burroughs公司和Illinois大学1965年开始 制、并于1972年完成的。Illiac-IV是SIMD阵列处 理机的典型代表,其结构框图如下图所示,共有64 个PE,统一由CU控制。B6500作为前端机进行系统 管理。每个PE有自己的局存PEM,容量为2K字,字 长64位,同时每个PE拥有4个64位的寄存器,分别 用作累加器、操作数寄存器、数据路由寄存器和 通用寄存器。此外,尚有1个16位变址器和1 个8 位的方式寄存器,用于存放PE的屏蔽信息。

第七章 多处理机

7.2.2 机间互连形式

多处理机机间互连的形式是决定多处理机性能的一个重要 因素。在满足高通讯速率、低成本的条件下,互连还应灵活多 样,以实现各种复杂的乃至不规则的互连而不发生冲突 1.总线形式 多个处理机、存储器模块和外围设备通过接口和公用总线 相连,采用分时或多路转接技术传送。 为解决多处理机同时访问公用总线冲突,有静态优先级、 固定时间片、动态优先级、先来先服务等多种总线仲裁算法 总线形式适于机数少的多处理机。它结构简单、造价低、 可扩充性好;但总线性能和可靠性受物理因素的影响 2.环形互连形式 构造了一种逻辑总线,让各处理机之间点点相连成环状, 称为环形互连,如图7.6P187所示。在这种多处理机上,信息的 传递过程由发送进程将信息送到环上,经环形网络不断向下一 台处理机传递,直到信息又回到发送者为止

2.松耦合多处理机 松耦合多处理机中,每台处理机都有一个容量较大 的局部存储器,用于存储经常用的指令和数据,以减少 紧耦合系统中存在的访主存冲突。不同处理机间或者通 过通道互连实现通讯,以共享某些外部设备;或者通过 消息传送系统MTS来交换信息,这时各台处理机都带有 自己的外部设备。 一般,松耦合多处理机较适合做粗粒度的并行计算。 处理的作业分割成若干相对独立的任务,在各个处理机 上并行,而任务间的信息流量较小。如果各处理机任务 交互作用较少时。这种耦合度很松的系统是很有效的, 可看作一个分布系统。 图7.4P186给出了典型的经消息传送系统互连的松耦 合非层次型多处理机。

7.4.2 性能模型与分析

假定一个应用程序含T个任务,在N台处理机上运行,每个 任务的执行时间为E,不同处理机间一次通讯开销时间为C。 1.N=2且计算与通讯不能重叠 如果将I个任务分配给一台处理机,余下的T-I给另一台处理 机,则R=Emax{T-I,I}+C(T-I)I 据此,可得到如图7.19P198。由图可见,E/C的大小不影响 总执行时间,只影响总通讯时间。当E/C<=T/2时,所有任务分 配给一台处理机,可使总运行时间R最少;而E/C>T/2时,将任 务分配给两台处理机,可使总运行时间R最少。 2.N>2且计算与通讯不能重叠 若将IK个任务分配给第K台处理机,则 R=Emax{IK}+C/2∑IK (T-IK) 由于∑IK =T,故R=Emax{IK}+C/2(T2-∑IK2)

第7章 事务处理系统

管理信息系统

实时处理的优点是:及时处理、及时更 新和快速响应顾客的要求。 实时处理的缺点是:需要采用一定的保 护措施防止数据库被非法闯入和病毒攻 击。 采用什么样的处理方式一是要在成本、 安全的问题上平衡;二是考虑业务的实 际需求和特点。

管理信息系统

自动输入数据的业务处理要求如下。 (1) 获取数据越早越好。 (2) 获取的数据越接近数据源越好,第一 手资料永远是最珍贵的。 (3) 机械装置准确率高,因为只有真实可 靠的第一手资料才是最珍贵的。

管理信息系统

2.数据处理——数据处理的方式分为 批处理和实时处理

1) 批处理 批处理(batch processing)是定期地 周期性地收集源文件,然后进行成批 处理。批处理的优点是处理大量数据 时,可提高系统资源的利用率,是一 种经济的处理方法如企业的工资处理, 工资管理部门每月收集相关部门的工 资项目的变化,在每个月的具体某一 天处理工资数据。

主要的事务处理系统类型有销售/市场系统、制造/ 生产系统、财务/会计系统、人事/组织系统等。这 些系统的主要功能如表7-1所示。

表7-1 事务处理系统类型

管理信息系统

销售/市场系统 制造/生产系统 财务/会计系统 财务/会计系统 人事/组织系统

销售管理

调度

预算

档案

市场研究 定价 新产品 销售订货 市场研究 报价

管理信息系统

批处理活动如下。 (1) 收集源文件。 (2) 把收集到的源文件记录到存储文件 中。 (3) 按关键字把文件中的记录排序。 (4) 把源文件和主文件合并。 (5) 定期将文件传送到系统之中备份, 提供给其他系统访问,

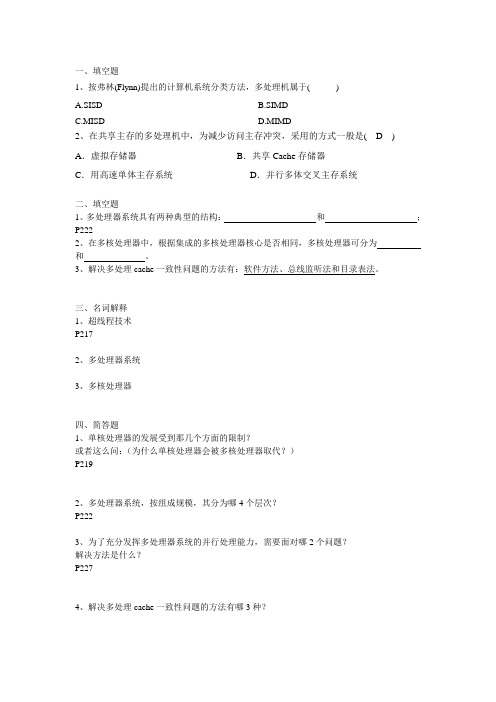

第8章 多处理机 习题

一、填空题

1、按弗林(Flynn)提出的计算机系统分类方法,多处理机属于( )

A.SISD

B.SIMD

C.MISD

D.MIMD

2、在共享主存的多处理机中,为减少访问主存冲突,采用的方式一般是( D )

A.虚拟存储器B.共享Cache存储器

C.用高速单体主存系统D.并行多体交叉主存系统

二、填空题

1、多处理器系统具有两种典型的结构:和;P222

2、在多核处理器中,根据集成的多核处理器核心是否相同,多核处理器可分为

和。

3、解决多处理cache一致性问题的方法有:软件方法、总线监听法和目录表法。

三、名词解释

1、超线程技术

P217

2、多处理器系统

3、多核处理器

四、简答题

1、单核处理器的发展受到那几个方面的限制?

或者这么问:(为什么单核处理器会被多核处理器取代?)

P219

2、多处理器系统,按组成规模,其分为哪4个层次?

P222

3、为了充分发挥多处理器系统的并行处理能力,需要面对哪2个问题?

解决方法是什么?

P227

4、解决多处理cache一致性问题的方法有哪3种?

5、集群系统的特点?

P241

6、构建集群系统的关键技术?P243

7、多核处理器的优点?

P221。

计算机操作系统【第七章】 汤子瀛版

计算机操作系统【第七章】1.试画出微机和主机中常采用的I/O系统结构图。

微机中常采用的I/O系统结构图为:主机中常采用的I/O系统结构图为:2.试说明设备控制器的构成。

设备控制器的构成如图所示:由上图可见,设备控制器由以下三部分组成:(1)设备控制器与处理机的接口,该接口用于实现CPU与设备控制器之间的通信,提供有三类信号线:数据线、地址线和控制线。

(2)设备控制器与设备的接口,可以有一个或多个接口,且每个接口连接一台设备。

每个接口都存在数据、控制和状态三种类型的信号。

(3)I/O逻辑,用于实现对设备的控制。

其通过一组控制线与处理机交互,处理机利用该逻辑向控制器发送I/O命令,I/O逻辑对收到的命令进行译码。

3.为了实现CPU与设备控制器之间的通信,设备控制器应具有哪些功能?为了实现CPU与设备控制器之间的通信,设备控制器应具有如下功能:(1)接受和识别命令。

CPU可以向控制器发送多种不同的命令,设备控制器应能接收并识别这些命令。

设置控制寄存器来存放所接收的命令和参数。

(2)数据交换,指实现CPU与控制器之间、控制器与设备之间的数据交换。

设置数据寄存器来存放有关数据。

(3)设备状态的了解和报告。

控制器记录下所连接设备的状态以供CPU了解。

为此,要在控制器中设置一状态寄存器,用其中的每一位反映设备的某一状态。

(4)地址识别。

配置地址译码器以便于正确识别设备地址。

4.分别就字节多路通道、数据选择通道和数组多路通道进行解释。

①字节多路通道含有许多非分配型子通道分别连接在低、中速I/O设备上,子通道按时间片轮转方式共享主通道,按字节方式进行数据传送。

具体而言,当第一个子通道控制其I/O 设备完成一个字节的交换后,便立即腾出字节多路通道(主通道),让给第二个子通道使用;当第二个子通道也交换完一个字节后,又依样把主通道让给第三个子通道使用,以此类推。

转轮一周后,重又返回由第一个子通道去使用主通道。

②数组选择通道只含有一个分配型子通道,一段时间内只能执行一道通道程序、控制一台设备按数组方式进行数据传送。

第7章流水线结构RISC CPU设计

(7-4)

7.3流水线的性能评价

7.3.1 流水线的性能指标

2.CPU性能公式

总时钟周期数 CPU时间 时钟频率

(7-5)

总时钟周期数 CPI (7-6) IC

CPU时间

(CPI

i 1

n

CPI IC (7-7) 总CPU时间 时钟频率

(7-8)

i

ICi )

时钟频率

CPI

7.1.2流水线CPU的时空图

空间S

I 1 I 2I 3I 4I 5 I 6 I 7 I 8I 9 I 10

空间S

WB EX ID IF

I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 I1 I2 I3 I4 I5 1 2 3 4 5 6 7 8 时间T

Reg

图7-10 例7-4的流水线状态图

ALU

7.2 流水线中的主要问题及处理 CC1 CC2 CC3 CC4 CC5

时钟周期

CC6

ALU

程 序 Reg 执 LW R1,0(R2) IM 7.2.3 数据竞争的处理技术 行 序 列 SUB R4,R1,R5 IM

ALU

DM

Reg

Reg

气泡

DM

AND R6,R1,R7

Reg

ALU

程 序 Reg 执 ADD R1,R2,R3 IM 行 序 列 7.2.3 数据竞争的处理技术 SUB R4,R1,R5 IM

ALU

7.2 流水线中的主要问题及处理

DM Reg DM

时钟周期

CC1

CC2

CC3

CC4

CC5

CC6

第7章-计算机系统结构(第五版)李学干

第7章 多处理机

图 7-4 通过消息传送系统连接的松耦合多处理机结构

第7章 多处理机

卡内基-梅隆大学设计的松耦合多处理机Cm*是层次型总 线式多处理机,其结构如图7 - 5所示。

第7章 多处理机

图 7-5 Cm*多处理机结构

第7章 多处理机

2. 多处理机机间互连的形式是决定多处理机性能的一个重 要因素。 1) 多个处理机、存储器模块和外围设备通过接口与公用总 线相连,采用分时或多路转接技术传送。

第7章 多处理机

图7 - 10给出了一个42×32的Delta网络,这种互连网络比 较适用于输入端数和输出端数不等或通信不规则的多处理机 中。

第7章 多处理机

图 7-10 42×32的Delta网络(榕树形互连网络的特例)

第7章 多处理机

4) 如果每个存储器模块都有多个访问端口,将分布在交叉 开关矩阵中的控制、转移和优先级仲裁逻辑分别移到相应存 储器模块的接口中,就构成了多端口存储器形式的结构。图 7- 11是一个四端口存储器形式的结构。

第7章 多处理机

图 7-25 嵌套并行进程的优先执行过程

第7章 多处理机

7.3.4

使用多处理机的主要目的是用多个处理机并发执行多 个任务来提高解题速度。

第7章 多处理机

7.4 多处理机的操作系统

7.4.1

在主从型操作系统中,管理程序只在一个指定的处理机 (主处理机)上运行。

1. 优点 2. 缺点 3. 适用场合

图 7-21 计算Z=E+A*B*C/D+F的并行程序数据相关图

第7章 多处理机

这条语句又派生出S4,分配给空闲的处理机1,而处理机 2接着执行S3。同样,等S4和S3都先后结束后,才满足JOIN语 句的汇合条件,经GOTO 50进入S5。

《操作系统》第7章 NT内核Windows操作系统

⑷NT是32位的多任务操作系统,克服了DOS的 NT是32位的多任务操作系统,克服了DOS的 640KB的瓶颈限制.支持对称多CPU,支持多线 640KB的瓶颈限制.支持对称多CPU,支持多线 程. ⑸NT内核WINDOWS操作系统支持多重文件系统 NT内核WINDOWS操作系统支持多重文件系统 与异步I/O以及采用面向对象的软件开发技术. 与异步I/O以及采用面向对象的软件开发技术. 多重文件系统包括:MS-DOS的FAT16/32, 多重文件系统包括:MS-DOS的FAT16/32,OS/2 的高性能文件系统HPFS,CDFS,NTFS. 的高性能文件系统HPFS,CDFS,NTFS.NTFS 支持大容量外存. ⑹ NT内核WINDOWS操作系统内置网络功能, NT内核WINDOWS操作系统内置网络功能, 支持分布式计算和互操作性.NT内核WINDOWS 支持分布式计算和互操作性.NT内核WINDOWS 操作系统采用先进的操作系统结构,客户/ 操作系统采用先进的操作系统结构,客户/服务 器模式,微内核结构,对象模型等. ⑺安全可靠,安全性达到美国政府C2级安全标准. ⑺安全可靠,安全性达到美国政府C2级安全标准.

硬件抽象层HAL 硬件抽象层HAL 硬件抽象层HAL( 硬件抽象层HAL(Hardware Abstraction Layer)将内核,设备驱 Layer)将内核,设备驱 动程序,执行体同硬件分隔,HAL隐藏各种与硬件有关的细节, 动程序,执行体同硬件分隔,HAL隐藏各种与硬件有关的细节, 如I/O接口,中断控制器,多处理机通信机制和依赖于硬件平台 I/O接口,中断控制器,多处理机通信机制和依赖于硬件平台 的函数等.HAL是NT内核WINDOWS操作系统在多种硬件平台可 的函数等.HAL是NT内核WINDOWS操作系统在多种硬件平台可 移植性成为可能的关键技术. Windows NT系列操作系统设计的一个至关重要的方面就是在多 NT系列操作系统设计的一个至关重要的方面就是在多 种硬件平台上的可移植性,硬件抽象层(HAL)就是使这种可移植 种硬件平台上的可移植性,硬件抽象层(HAL)就是使这种可移植 性成为可能的关键部分.HAL是一个可加载的核心态模块Hal.dll, 性成为可能的关键部分.HAL是一个可加载的核心态模块Hal.dll, 它为运行在Windows NT/XP上的硬件提供低级接口.HAL隐藏各 它为运行在Windows NT/XP上的硬件提供低级接口.HAL隐藏各 种与硬件有关的细节,例如I/O接口,中断控制器以及多处理机 种与硬件有关的细节,例如I/O接口,中断控制器以及多处理机 通信机制等任何体系结构专用的和依赖于计算机平台的函数. HAL是一个软件层,用来为操作系统的上层隐藏硬件差异,以提 HAL是一个软件层,用来为操作系统的上层隐藏硬件差异,以提 高Windows NT系列操作系统的可移植性.HAL有一虚拟机接口, NT系列操作系统的可移植性.HAL有一虚拟机接口, 可为内核调度程序,可执行体和设计驱动程序所使用.这种方法 的一个优点是每个设备驱动程序只需要一个版本,即它可运行于 各种硬件平台,而无需移植驱动程序.HAL也支持对称多重处理. 各种硬件平台,而无需移植驱动程序.HAL也支持对称多重处理. 设备驱动程序映射设备并直接访问它们,但是映射内存的管理, 配置I/O总线,设置DMA和处理母板等有关细节,都是由HAL接 配置I/O总线,设置DMA和处理母板等有关细节,都是由HAL接 口提供的.

工业设计机械基础第7章常用机构

M

B 3 O3

n = 3, Pl =4, Ph =0 F = 3×3 - 2×4 – 0 = 1

与实际相符

n = 3, Pl=4, Ph =0

F = 3×3 - 2×4 – 0 = 1

2)两构件形成多个具有相同作用的运动副。 (1)两构件组成多个移动副,且导路相互平行或重合时,只有一个 移动副起约束作用,其余为虚约束。

2

1

◆处理方法:计算中只计入一处高副。

F=3n-2Pl-Ph=3x2-2x2-1=1

3、机构中对运动不起独立作用的对称部分,将产生虚约束。

◆处理方法:计算中应将对称部分除去不计。

图7-11 运动简图中构件的表示方法 a)二运动副构件示例 b)三运动副构件示例

常用机构运动简图 国标GB/T 4460-1984 给出了典型机构的运动简图, 表7-1为摘自该国标的部分常用机构的运动简图。

2.转动副 构件组成转动副时,如下图表示。 图垂直于回转轴线用图a表示; 图不垂直于回转轴线时用图b表示。 表示转动副的圆圈,圆心须与回转轴线重合。 一个构件具有多个转动副时,则应在两条交叉处涂黑,或在其内 画上斜线。

F=3n-2Pl-Ph=3x3-2x4-0=1

◆处理方法:计算中只计入一 个移动副。

F=3n-2Pl-Ph=3x1-2x1=1

(2) 两构件组成多个转动副,且轴线重合,只有一个转动副起 约束作用,其余为约束。

◆处理方法:计算中只计入一个转动副。

(3)两构件组成多处接触点公法线重合的高副,只考虑一处高副。

图7-5 液体搅拌机 1—机架 2—曲柄 3—连杆 4—摇杆

⑶从动件 机构中由原动件驱动的其他构件。 若从动件直接实现机构的功能,称为执行件;若从动件把运动输出本 机构,称为输出构件。 图7-5中连杆3、摇杆4都是从动件。

计算机体系结构第七章 多处理机

一、多处理机的特点

1、多处理机的定义 具有两台以上的处理机,在操作系统控制下通过 共享的主存或输入输出子系统或高速通讯网络进 行通讯。实现指令以上级(任务级、作业级)并 行。 按照Flynn分类法,多处理机系统属于MIMD计算 机。 多处理机系统由多个独立的处理机组成,每个处 理机都能够独立执行自己的程序。

K1

若采用平均分配策略:

RETCT2(11) N 2N N

五、多处理机操作系统

主从型(Master-slave Supervisor) 各自独立型(Separate Supervisor) 浮动型(Floating Supervisor)

主从型

管理程序只在主处理机运行 硬件结构管理控制简单,对主处理机要

求高 适用于工作负荷固定,从处理机能力明

显低的紧耦合、异构型、非对称多处理 机系统 实现简单,经济方便,但不够灵活。

各自独立型

每个处理机有独立的管理程序在运行 管理程序可再入,可靠性高,系统表格

少,系统效率高,实现复杂,访存冲突 解决和负载较困难 适合于松耦合多处理机

浮动型

管理程序在多个处理机间浮动 管理程序可再入,实现复杂,负载平衡

当机数由N台增加到N+1台时,总运行 时间的减少量为:

E(T 1 1 )C ETC N N1 N(N1)

令其>=0,有 N ET

临界值

C

3、额外开销与计算工作重叠

假定额外工作被计算工作完全覆盖,则 总运行时间为:

Rma E*x m {IaK)xC 2 ,(K N 1IK(TIK)}

平均分配

RETCT2 CT2 N 2 2N

简单起见,设T是N的整数倍

多核时代“并行计算”课程教学模式研究与实践

多核时代“并行计算”课程教学模式研究与实践雷向东,雷振阳,龙军(中南大学计算机学院,湖南长沙410083)[摘要]多核技术的出现与快速发展使计算机技术发生了重大变化。

国内外著名高校将多核技术引入到计算机教育体系当中,并开设了并行计算课程,培养学生的并行计算思维和并行计算系统能力。

文章对“并行计算”课程建设、教材建设、教学模式和课程思政等方面进行研究和探讨。

[关键词]并行计算;多核;教学模式;课程思政[基金项目]2017年度湖南省研究生教学改革项目“基于协同创新中心专业学位研究生多元化联合培养模式与实践研究”(JG2017B016);2019年度中南大学《并行计算》课程思政项目[作者简介]雷向东(1964—),男,湖南常宁人,博士,中南大学计算机学院副教授,主要从事并行计算研究。

[中图分类号]G642[文献标识码]A[文章编号]1674-9324(2021)02-0141-04[收稿日期]2020-05-06多核技术的出现与快速发展使计算机技术发生了重大变化[1,2]。

多个处理器核心的出现,为软件在单处理器上的并行提供了丰富的硬件资源。

多核技术利用片上多核处理器资源进行线程级并行,通过多核并行编程技术,充分利用这些计算资源。

为了应对多核技术及其引起的相关计算机技术发展的需要,国内外著名高校都开设了“并行计算”课程,将多核技术相关知识内容融入“并行计算”教学中[3,4]。

通过“并行计算”课程的学习,使学生掌握多核相关知识、多核程序设计方法以及相关的多核优化工具,更好地适应计算机技术发展和IT企业的需求。

一、“并行计算”课程建设并行计算是实现高性能、高可用计算机系统的主要途径。

“并行计算”课程以高性能并行计算机为主题,主要介绍当代并行计算机系统及其结构模型,并行算法设计与并行程序的设计原理与方法。

通过“并行计算”课程的学习,使学生从系统结构、算法、程序设计三个方面,了解并行处理的基本概念,把握并行处理技术的最新成就和发展趋势,掌握并行计算编程技术和方法。

《计算机体系结构设计》第07章 并行处理与普适计算

多核CPU,每个处理器核内部有多级指令流水线。 资源共享(Resource Sharing):

是一种软件方式,利用软件让多个用户按一定时间顺序 轮流地使用同一套资源,以提高其利用率,这样相应地提高 整个系统的性能。例如多道程序分时系统。

7.3.2 多处理机系统中的存储器管理

(1)集中共享(共享存储)的并行处理机

每个PE没有局部存触器,存储模块以集中形式为所有

PE共享。

CU

SC

PE0 PE1

… PEN-1

ICN

MM0 MM1

… MMN-1

I/O-CH I/O … SM 图7.15 集中共享存储器结构

(2)分布共享(分布存储)的并行处理机

7.1 并行计算机系统结构 7.2 单处理机系统中的并行机制 7.3 多处理机系统的组织结构 7.4 多处理机操作系统和算法 7.5 从计算机到网络 7.6 普适计算和移动计算 习题7

7.1.1 指令级并行和机器并行

1 并行性(Parallelism)

并行计算机系统最主要的特性就是并行性 (Parallelism),并行性是指计算机系统具有的同时运算或 同时操作的特性,它包括同时性与并发性两种含义。 同时性(Simultaneity):指两个或多个事件在同一时刻

发线程级并行和指令级并行的技术,使用的是线程级并行 性(Thread Level Parallelism,简称TLP)。

实现多线程有两种主要的方法: 细粒度(Fine-Grained)多线程 粗粒度(Coarse-Grained)多线程

7.2.2 单片多核处理器CMP

单芯片多处理器(Chip Multiprocessors,CMP)与同时 多线程处理器(Simultaneous Multithreading,SMT),这

第7章渣铁处理系统ppt课件

7

8

9

圆形出铁场的 优点是可以在 任何方位布 置出铁口。其 缺点是布置二 次除尘有困难, 炉体平台较狭 窄,难以实现 快速大修和扩 容。

10

风口平台及出铁场布置图(2025m3高炉) 1-高炉;2-铁口;3-渣口;4-出铁场;5-炉前吊车;6-渣罐; 7-铁水罐;8-水力冲渣沟;9-高炉计器室;10-炉前仓库;11-电炮操 作室;12-炉前工休息室;13-辅助材料仓;14-放散阀卷扬;15-除尘

49

打泥能力- 6000KN、 工作油压— 35Mpa、 自动化程 度—可手动、 自动、无线 电遥控。

宝钢1号高炉MHG60型液压矮泥炮示意图

50

7.2.3 堵渣口机

高炉的渣口要求在出渣后,将渣口迅速 堵住。在堵渣口时,要求堵碴机械工作可靠, 结构紧凑,塞头进人渣口的轨迹应近似于一 条直线。

目前国内外研制的堵渣机结构形式较多, 按驱动方式可分气动、电动和液压三种。国 内使用较多为连杆式和折叠式堵渣门机。

一. 对泥炮的要求 1.有足够的一次吐泥量; 2.有一定的吐泥速度; 3.有足够的吐泥压力; 4.操作安全可靠,可以远距离控制; 5.炮嘴运动轨迹准确。

42

二. 分类

按驱动方式的不同,泥炮可分为气动式、电 动式和液压式三种。气动泥炮一般采用蒸汽驱动, 由于泥缸容积小,活塞推力不足,堵一次铁口要 多次装泥,操作不方便,故已被淘汰。目前国内 不少高炉采用电动泥炮。随着高炉容积的大型化 和无水炮泥的使用,要求泥炮的推力越来越大, 电动泥炮已难以满足堵铁口要求,采用液压泥炮 的高炉越来越多。

16

7.1.2 渣铁沟和渣铁分离器

一. 主铁沟

1. 概念: 从高炉出铁口到撇渣器之间的一段铁沟称

为主铁沟。

第6章多计算机系统

5、开关枢纽形式

• 将互连结构设置在PE或其接口内部,组成分布 结构(松耦合)。 • 开关枢纽:由仲裁单元和开关单元组成,端口 数不能多。 • 结构:由开关枢纽组成各种结构,如树形结构。 • 开关枢纽网络适宜于PE数较多的系统。

2018/12/11

26

6.2 多机系统中的并行性分析

互连网络

P/C LM NIC …

P/C LM NIC

SM

SM … SM

互连网络

大规模并行处理机(MPP)

并行向量处理机(PVP)

2018/12/11

13

多处理机系统结构(二)

结点 结点

P/C P/C P/C … P/C 互连网络 LM DIR NIC …

P/C LM DIR NIC

SM

SM … SM

2018/12/11 41

2018/12/11

42

3、并行程序设计语言

• 开发方式 设计全新的并行程序语言,难度非常大; 扩充原来的串行语言的语法成份,使它支持并行 特征 不改变串行语言,仅为串行语言提供可调用的并 行库 • 扩展语言的并行结构 FORK-JOIN(在不同的机器上有不同的表现形式) 块结构语言:cobegin-coend(或parbeginparend)

•第1章 •第2章 •第3章 •第4章 •第5章 •第6章 •第7章

计算机系统设计基础 数据表示与指令系统性能分析 通道处理机 流水技术和向量处理 阵列计算机 多处理机系统 其它计算机结构

2018/12/11

1

第6章 多处理机系统

6.1 6.2 6.3 6.4 6.5 基本概念与机间互连形式 多处理机系统中并行性分析 共享存储器体系结构 消息传递体系结构 MPI并行程序设计基础

第7章__例外处理

throw e;

throws Etype1, Etype2 ……

1、例外的概念

程序中的例外不外乎两种情况:一种是运行环境不能 满足程序运行的要求而出错;一种是程序要解决的问 题的约束而导致的。 不管是哪种情况,编写程序时,程序员要考虑到程序 运行时可能遇到的各种情况(条件),并进行处理; 如果不能处理,或者不知该如何处理,就可以认为是 一种错误,这时,就需要交给别人去处理。 以前,是通过返回错误代码来提示别人程序有错误; 在Java中,则是通过例外机制通知别人出错信息。

1、例外的概念

{

用例外的形式处理错误:

try { openTheFile; determine its size; allocate that much memory; read-File; closeTheFile; } catch(fileopenFailed) catch(sizeDetermineFailed) catch(memoryAllocateFailed) catch(readFailed) catch(fileCloseFailed) finally

Exception:一般程序中可预知的问题,其产生的例外 可能会带来意想不到的结果,因此Java编译器要求Java 程序必须捕获或声明所有的非运行时异常。

2、例外的分类

用户自己产生的例外

Throwable

Exception

处理

Error

不做处理 由用户捕获或 声明并处理 RuntimeException

AWTError (in java.awt) …

2、例外的分类

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第7章 多处理机

7.2.2 机间互连形式

1. 总线形式

多个处理机、存贮器模块和外围设备通过接口与公用总线 相连,采用分时或多路转接技术传送。其中,单总线方式结构 简单、成本低, 系统上增减模块方便,但对总线的失效敏感。 而且,处理机数增加会增大访问总线冲突的概率而导致系统效 率急剧下降。虽然可以在处理机中设置局部存贮器和专用外围 设备来减少访问总线的冲突,但这种单总线形式也只适用于处 理机数较少的场合。IBM Stretch和UNIVAC Larg多处理机采用 的就是单总线方式。

第7章 多处理机 图 7.1 紧耦合多处理机的结构

第7章 多处理机 图 7.2 带非对称I/O子系统的多处理机

第7章 多处理机 图 7.3 采用冗余连接的非对称I/O子系统

第7章 多处理机 2. 松耦合多处理机

图 7.4 通过消息传送系统连接的松耦合多处理机结构

第7章 多处理机 图 7.5 Cm*多处理机结构

第7章 多处机

第7章 多处理机

7.1 多处理机的特点及主要技术问题 7.2 多处理机的硬件结构 7.3 程序并行性 7.4 多处理机的性能 7.5 多处理机的操作系统

第7章 多处理机

7.1 多处理机的特点及主要技术问题

1) 2) 程序并行性 3) 4) 进程同步 5) 资源分配和任务调度

第7章 多处理机

第7章 多处理机 图 7.15 多处理机的二维并行存贮器构形

第7章 多处理机

2. 多Cache的一致性问题

为解决多个Cache之间的不一致。主要有两类做法。一类 是以硬件为基础的做法,另一类则主要是以软件为基础的做 法。

以硬件为基础实现Cache一致性的办法有多个。 最普遍采 用的办法叫监视Cache协议(Snoopy Protocal)法,各个处理机中 的Cache控制器随时都在监视着其他Cache的行动。对于采用 总线互连共享主存的多处理机, 可利用总线的播送来实现。

第7章 多处理机

目录表的具体作法又可分 3 种。一种是全映象目录表法。 表中每项有N个标志位对应于多处理机中全部N台处理机的 Cache。 系统中全部Cache均可同时存有同一个信息块的副本。 不过, 这样的目录表很庞大, 硬件及控制均较复杂。 另一种 是有限目录表法。 表中每项的标志位少于N个。因此,限制了 一个数据块在各Cache中能存放的副本数目。这两种目录表都 是集中地存入在共享的主存之中,因此需要由主存向各处理机 广播。第三种是链式目录表法。它把目录分散存放在各个 Cache中,主存只存有一个指针,指向一台处理机。 要查找所 有放有同一个信息块的Cache时,先找到一台处理机的Cache, 然后顺链逐台查找, 直到找到目录表中的指针为空时为止。

第7章 多处理机 2. 环形互连形式

图 7.6 机间采用环形互连的多处理机

第7章 多处理机 3. 交叉开关形式

图 7.7 交叉开关形式

第7章 多处理机 图 7.8 交叉开关中结点开关的结构

第7章 多处理机

图 7.9 用 4×4 16×16 的两级交叉开关网络

第7章 多处理机 4. 多端口存贮器形式

第7章 多处理机

7.3 程 序 并 行 性

7.3.1 并行算法

1. 算术表达式的并行运算 算法必须适应具体的计算机结构。串行处理机上习惯采 用的循环和迭代算法往往不适合于多处理机,而采用直接解 法有时反倒能揭示更多的并行性。 例如,E1=a+bx+cx2+dx3 利用霍纳(Horner)

E1=a+x(b+x(c+x(d)))

(5) 如何将各个任务分配到一个或多个处理机上, 解决好 处理机调度、任务调度和资源分配问题, 防止死锁。

(6) 一旦某个处理机发生故障,如何对系统进行重新组织 而不使其瘫痪。

第7章 多处理机

7.2 多处理机的硬件结构

7.2.1 紧耦合和松耦合

1. 紧耦合多处理机 紧耦合多处理机是通过共享主存来实现处理机间通信的, 其通信速率受限于主存的频宽。但是,由于各处理机与主存 经互连网络连接,系统中处理机数就受限于互连网络带宽及 多台处理机同时访问主存发生冲突的概率。

图 7.10 四端口存贮器形式的结构

第7章 多处理机 5. 开关枢纽结构形式

图 7.11 X-TREE多处理机结构框图

第7章 多处理机

7.2.3 存贮器组织

1. 并行主存贮器的构成

图 7.12 m个模块的低位交叉编址

第7章 多处理机 图 7.13 m个模块的高位交叉编址

第7章 多处理机 图 7.14 本地存贮器的概念

第7章 多处理机

以软件为基础解决Cache一致性的作法,主要优点是可以 减少硬件的复杂性,降低对互连网络通信量的要求, 因而性能 价格比可以较高,比较适用于处理机数多的多处理机。 但应当 指出的是, 现在以软件为基础的办法虽已提出了好几种方案, 但由于可靠性及编译程序的编写困难, 都还没有真正在商品化 多处理机上使用,只在某些试验性系统上使用,如伊利诺大学 的Cedar机。

第7章 多处理机 图 7.16 不同算法影响树高的例子

第7章 多处理机

首先从算术表达式的最直接形式出发,利用交换律把相 同的运算集中在一起。再利用结合律把参加这些运算的操作 数(称原子)配对,尽可能并行运算,从而组成树高最小的子 树。最后,再把这些子树结合起来。例如,给定表达式

第7章 多处理机

有两种办法可以用来提高总线形式的系统效率。一种办 法是,采用优质高频同轴电缆来提高总线的传输速率;进一 步使用光纤通信, 其信息速率可达109~1010 b/s。另一种办法 是,采用多总线方式来减少访问总线的冲突概率。如美国的 Tandem-16 和Pluribus就采用双总线方式来提供一定的总线冗 余和增大系统总的信息传送率。日本的实验多处理机EPOS 采用的是四总线方式。德国西门子公司的结构式多处理机 SMS采用的是八总线方式。 而上节介绍的Cm*多微处理机则 采用分级的多总线方式。

(1) 硬件结构上如何解决好处理机、 存贮器模块及I/O子 系统之间的互连。

(2) 如何最大限度地开发系统的并行性, 以实现多处理机 各级的全面并行。

(3) 如何选择分割任务和子任务的大小, 即任务的粒度大 小, 使并行度高, 而辅助开销小。

(4) 如何协调好多处理机中各并行执行的任务和进程间的 同步问题。