DC逻辑综合使用流程

DC综合教程

DC操作流程

1.在虚拟机中 打开终端

DC操作流程 2. 创建综合 环境 在终端输入: new_dc xxx

xxx为你想要创 建的文件夹的名 字

DC操作流程

3. 修改环境(参考Readme

文件)

a.修改filelist.tcl 添加通过验证的源代 码

DC操作流程

b.修改synopsys.sdc 添加综合约束

DC 工具简要入门

2012年秋

内容

• 1. 逻辑综合以及综合工具

Design Compile • 2.DC操作流程

• 3.现场演示

逻辑综合

• 将RTL代码转换为门级网表 的过程

逻辑综合

DC工具

• Design Compile是常用的综合 工具,在DC中,共有8中设计 实体 • 1、设计(Design):一种能 完成一定逻辑功能的电路。设 计中可以包含子设计

• 对于DC而言,通常要指定下面4种库 • 1、Target library 工艺库,由代工厂提供的和具体工艺 相关的工艺库 • 2、Link library 指定DC查找时所指定的目标,通常 也就是Target library

DC工具--指定参考库

• Synthetic library DC综合时将转化HDL代码为相应元 件时所参考的IP库。比如符号“+”, 通过IP库查找生成某类加法器。默认 使用自带的加法库。 • Symbol library 使用图形界面时,在原理图上绘制 与非门等标准单元的符号库

DC工具

• 2、单元(Cell):子设计的实例 • 3、参考(Reference):单元的参考对 象,即单元是参考的实例 • 4、端口(Port) • 5、管脚(Pin) • 6、线网(Net) • 7、时钟(Clock) • 8、库(Library):综合时用到的一组基 本单元的集合

DC教程

该变量给出了 DC 环境下读入的文件(包括库文件和设计文件)的搜寻路径。当读入没有给出路 径的文件时,DC 则按照 search_path 给出的路径搜索该文件。

如果 search_path 表示多个路径,用 list 将所有路径组合成一个集合。

目标工艺库(target_library)

三、目录组织结构

做综合时各文件的存放目录没有严格的规定,但为了便于管理和查看,一般会分类放在不同的 目录下,下面是一个目录组织结构的范例:

四、操作步骤

Step1:启动 DC 首先进入 deller 服务器,打开一个 Terminal,输入命令:

source cshrc_eda

然后按照前面讲的目录结构建立文件夹,把所需要的文件放入相应的文件夹,进入工作目录 run, 这时在 terminal 中输入命令: design_vision&

6.2 pbist.read

该文件为读取原始的设计文件,内容如下

analyze 语句读入设计文件,‐format 选项的值为 verilog(源代码用 verilog 编写)或 vhdl(源代 码用 vhdl 编写),elaborate 语句建立一个 design,design 的名字为设计文件中 module 的名字。一般 最后读入顶层模块所在的文件,这样执行完所有的语句后,current_design 就是顶层模块对应的 design,这也是后面综合的对象。

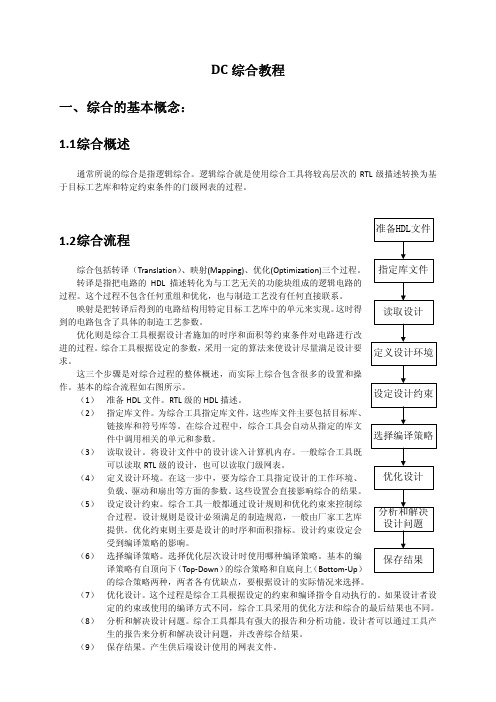

进的过程。综合工具根据设定的参数,采用一定的算法来使设计尽量满足设计要 定义设计环境

求。

这三个步骤是对综合过程的整体概述,而实际上综合包含很多的设置和操

作。基本的综合流程如右图所示。 (1) 准备 HDL 文件。RTL 级的 HDL 描述。

Designed Compile DC综合

建立时间和保持时间的slacks: 例:建立时间: ---------------------------------------------------data required time 31.74 data arrived time -19.80 -----------------------------------------------------slack 11.94 arrived time应比required time提前,这样才能保证建 立时间不违例。

首先选定reset端口,Attribute->Optimization Constraints->Timing Constraints… 点击OK,完成reset的延迟设置. 相对应的脚本命令是: dc_shell> set_max_delay 5 from RESET

Set_max_delay 设置最大延迟

DC时序路径:

时间通路的划分

几个概念

数据传输需要的时间(Data Arrival Time ):信号到达时间是指信号到达电路中 某一点的真实时间,一般等于信号到达 时序路径起点的时间加上信号在该时序 路径上传播所用的时间。 要求到达时间(Data Required Time):指 期望信号到达电路中某一点的时间。 时序裕度(slack):指电路中某点处要求到 达时间与实际信号到达时间的差值

建立时间和保持时间

建立时间(setup time):数据在时钟信号源到 达之前必须要稳定的时间,如果建立时间不 满足,数据不能正确打进时序逻辑单元 保持时间(hold time):数据在时钟信号源到 达之后必须要稳定的时间,如果保持时间不 够,数据被时序逻辑单元正确锁存 基本单元的延时(Tcq):门延时是指信号通 过实际的标准单元所需要的时间.在时序逻辑 单元中,反映为从时钟沿开始,到数据输出 需要的时间 . 线延时:线延时是指由于导线的阻容而导致的 信号传播延时

逻辑综合

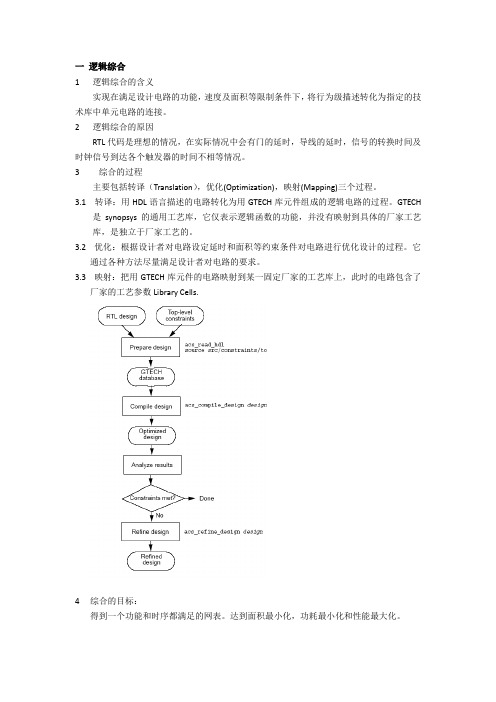

一逻辑综合1 逻辑综合的含义实现在满足设计电路的功能,速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。

2 逻辑综合的原因RTL代码是理想的情况,在实际情况中会有门的延时,导线的延时,信号的转换时间及时钟信号到达各个触发器的时间不相等情况。

3综合的过程主要包括转译(Translation),优化(Optimization),映射(Mapping)三个过程。

3.1 转译:用HDL语言描述的电路转化为用GTECH库元件组成的逻辑电路的过程。

GTECH是synopsys的通用工艺库,它仅表示逻辑函数的功能,并没有映射到具体的厂家工艺库,是独立于厂家工艺的。

3.2优化:根据设计者对电路设定延时和面积等约束条件对电路进行优化设计的过程。

它通过各种方法尽量满足设计者对电路的要求。

3.3映射:把用GTECH库元件的电路映射到某一固定厂家的工艺库上,此时的电路包含了厂家的工艺参数Library Cells.4综合的目标:得到一个功能和时序都满足的网表。

达到面积最小化,功耗最小化和性能最大化。

二综合软件(DC)Design Compile是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

DC综合的流程如下:1 综合环境建立1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

search_path= search_path + {“.”, synopsys_ro ot + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXc ompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

DC使用教程

如何看时序报告:

通过产生的时序报告读出以下信息: 1)是setup time report还是hold time report? 2)时钟频率多少?

确定是setup time report还是hold time report? 看oprating conditions:worst(建立 时间),best(保持时间)。为什么? 看path type:max(建立时间), min(保持时间)。为什么? 时钟频率多少: 通过上升沿和下降沿的时间来确定

Set_load 设置输出负载

估计模块输出的时序——transition time DC默认输出负载为0. 单位由Foundry厂提供,一般是pf.

Set_max_transition 设置最大传 输时间

Transition time 是指改变某线所驱动 的pin所需要的时间,该时间的计算方 法是基于工艺库的。 输出的传输时间是输入传输时间以及输 出负载的函数关系。 DC在优化的过程中就是确保设计的所 有net的对应的传输时间小于所设定的 最大传输时间。

DC时序路径:

时间通路的划分

几个概念

数据传输需要的时间(Data Arrival Time):信号到达时间是指信号到达电 路中某一点的真实时间,一般等于信号 到达时序路径起点的时间加上信号在该 时序路径上传播所用的时间。 要求到达时间(Data Required Time): 指期望信号到达电路中某一点的时间。 时序裕度(slack):指电路中某点处要求 到达时间与实际信号到达时间的差值

DC逻辑综合

变量的设定:设置的变量在DC启动时读入,便于综合的处理,同时有些DC的 变量必须在设置文件中输入。如可以设定命令的简写,保存多少条命令等: alias cud current_design alias rpt report_timing history keep 300

11

综合脚本实例(.synopsys_dc.setup)

✓ 符号库(symbol_library): 定义了单元显示的图形库,当用design_vision来查看图形的时候使用。

✓ 综合库(synthetic_library): 是由Synopsys公司提供的DesignWare库,包含了许多IP核及运算单元,用于 实现verilog描述的运算符,为电路的优化起着重要的作用。

set_operating_conditions -max slow -max_library slow -min fast -min_library fast

可以用set_min_library指定best和worst两种库,在设计中所用到的 库都可以指定。如: # 为综合用的sram库指定最佳情况可最坏情况

。

8

目标库和初始环境的设置

DC启动时会先启动.synopsys_dc.setup文件,它里面设定了综合所需要的工 艺库的信息以及一些对于工具的设定命令。

启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: 1)、DC的安装目录; 2)、用户的home目录; 3)、当前启动目录。 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

由于时钟一般是高扇出(high fanout)的,DC不会对高扇出的连线做设计 规则(DRC)的检查和优化。DC默认的时钟网络是理想的。在综合时不对时 钟的高扇出做处理,而是留在后续的布局布线中做时钟树综合(CTS)。

DC使用说明

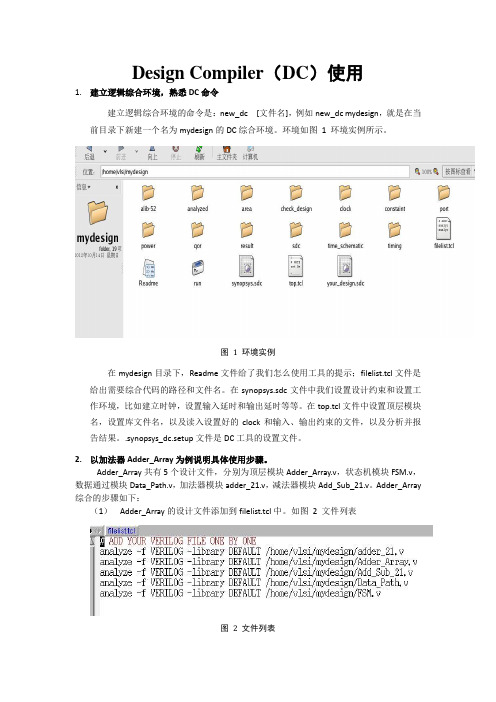

Design Compiler(DC)使用1.建立逻辑综合环境,熟悉DC命令建立逻辑综合环境的命令是:new_dc [文件名],例如new_dc mydesign,就是在当前目录下新建一个名为mydesign的DC综合环境。

环境如图1 环境实例所示。

图1 环境实例在mydesign目录下,Readme文件给了我们怎么使用工具的提示;filelist.tcl文件是给出需要综合代码的路径和文件名。

在synopsys.sdc文件中我们设置设计约束和设置工作环境,比如建立时钟,设置输入延时和输出延时等等。

在top.tcl文件中设置顶层模块名,设置库文件名,以及读入设置好的clock和输入、输出约束的文件,以及分析并报告结果。

.synopsys_dc.setup文件是DC工具的设置文件。

2.以加法器Adder_Array为例说明具体使用步骤。

Adder_Array共有5个设计文件,分别为顶层模块Adder_Array.v,状态机模块FSM.v,数据通过模块Data_Path.v,加法器模块adder_21.v,减法器模块Add_Sub_21.v。

Adder_Array 综合的步骤如下:(1)Adder_Array的设计文件添加到filelist.tcl中。

如图2 文件列表图2 文件列表(2)在top.tcl中将顶层模块设置为Adder_Array。

如图3修改顶层模块名图3 修改顶层模块名(3)修改synopsys.sdc实现以下设计约束:时钟周期1.2ns,input_delay设置为0.5ns,output_delay设置为0.5ns。

如果使用者想增加其他的设计约束可以在此文件中增添。

(4)进入刚才建好的综合环境,在终端中执行run命令,调用Design Compiler执行逻辑综合。

打开终端:cd [建好的环境路径],进入后输入run,即可。

(5)等逻辑综合执行完毕后,查看123.log,对其中的error和warning进行确认,如果有问题修改设计或综合脚本后重新综合,直至没有问题。

dc使用教程

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

DC逻辑综合(DC课件整理)

A D SET Q

这些变量必须准确指定,否则可能产生意外的结果,灵活的使用这些变量可 以可以大大减少工作量例如:你可以指定了一个标准单元库作为一个目标库 (target_library),然后在 link_1ibrary 列表中指定压焊点工艺库以及所有其 它的宏模块(RAMS、ROMs、etc.),这意味着用户将能够利用标准单元库出现的 单元综合设计,然后再在设计中连接 pads 和宏模块的实例,如果压焊点工艺库 被包含在 target_1ibrary 列表中,那么 DC 可能使用 pads 综合内核的逻辑。 target_1ibrary 名也应该被包含在 link_1ibrary 列表中,这很重要,因为如果 link_library 中没有 target_library 的内容,那么当把门级网表读入 DC 中时, DC 将不能解析在网表中映射的单元,这种情况下 DC 产生警告信息,它不能解析

关键变量的介绍:

1、target_1ibrary变量:是DC中保留的变量,这个变量指定的库是DC用来构建

一个电路的。DC进行映射的几个步骤:设置它让它指向你的生产商提供的库文件。

使用厂家提供的工艺库中的时序数据计算这些门的时序。从target_1ibrary指定

的库中选择功能正确的门。设定目标库使用如下语句: set target _1ibrary

详细布线

版图设计后进 行STA

时序满足将要求吗

DC综合

DC综合归纳总结Author:WJDate:Dec 11 2014 概述:●综合是将RTL源代码转换成门级网表的过程。

●电路的逻辑综合一般由三个步骤组成,即综合=转化+逻辑优化+映射(Synthesis=Translation+Logic Optimization+Mapping)●在综合过程中,优化进程尝试完成库单元的组合,使组合成的电路能最好地满足设计的功能、时序和面积的要求●综合是约束驱动(constraint driven)的,给定的约束是综合的目标。

约束一般是在对整个系统进行时序分析得到的,综合工具会对电路进行优化以满足约束的要求。

●综合以时序路径为基础进行优化。

(注意:电路中的cell,对于前一级是load,其电容越大负载能力越大;对于后一级是drive,其电阻越小驱动能力越大。

有:大器件大电容小电阻,小器件小电容大电阻)启动文件:1. search_path指定了综合工具的搜索路径。

2. target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

3.synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

4. link_library是链接库,它是DC在解释综合后网表时用来参考的库。

一般情况下,它和目标库相同;当使用综合库时,需要将该综合库加入链接库列表中。

5. symbol_library为指定的符号库。

6. synlib_wait_for_design_license用来获得DesignWare-Foudation的许可(license)。

7. alias语句与UNIX相似,它定义了命令的简称。

8. 另外,在启动文件中用符号“/*” 和“*/” 进行注释。

综合工具-DesignCompiler学习教程

综合⼯具-DesignCompiler学习教程Design Compiler 13讲中的部分内容:1、逻辑综合的概述DC⼯作流程分为三步2、DC的三种启动⽅式GUIdc_shellBatch mode3、DC-Tcl语⾔的基本结构1、⾼层次设计的流程图2、DC在设计流程中的位置3、使⽤DC进⾏基本的逻辑综合的流程图与相应的命令①准备设计⽂件②指定库⽂件③读⼊设计④定义设计环境⑤设置设计约束⑥选择编译策略⑦编译⑧分析及解决设计中存在的问题⑨存储设计数据(1)启动环境配置简述(2).synopsys_dc.setup配置⽂件的书写(3).synopsys_dc.setup的讲解(1)标准单元库①概述⼀个ASIC综合库包括如下信息:·⼀系列单元(包括单元的引脚)。

·每个单元的⾯积(在深亚微⽶中,⼀般⽤平⽅微⽶表⽰,在亚微⽶⼯艺下,⼀般⽤门来称呼,⾄于具体的单位,可以咨询半导体制造商)。

·每个输出引脚的逻辑功能。

·每个输⼊到输出的传递延时,输出到输出的传递延时;inout到输出的传递延时。

②内容与结构Synopsys的⼯艺库是⼀个.lib⽂件,经过LC编译后,产⽣.db⽂件。

⼯艺库⽂件主要包括如下信息:·单元(cell)(的信息):(主要有)功能、时间(包括时序器件的约束,如建⽴和保持)、⾯积(⾯积的单位不在⾥⾯定义,可按照规律理解,⼀般询问半导体⼚商)、功耗、测试等。

·连线负载模型(wire load models):电阻、电容、⾯积。

·⼯作环境/条件(Operating conditions):制程(process)(电压和温度的⽐例因数k,表⽰不同的环境之间,各参数缩放的⽐例)·设计规则约束(Design ):最⼤最⼩电容、最⼤最⼩转换时间、最⼤最⼩扇出。

⼯艺库的结构如下所⽰:(2)DC的设计对象在了解了综合库之后,下⾯介绍⼀下DC的设计对象,虽然这个设计对象相对于综合库没有那么重要,但是还是要了解⼀下的。

DC逻辑综合使用流程

DC逻辑综合使用流程1、启动软件:新开一个terminal窗口,输入命令:design_vision,回车即可开启图形界面,进入图形界面后可通过菜单、对话框等来实现DC的功能,相关的命令操作同样可以使用。

2、指定相关库文件及路径“File > Setup”打开下图所示对话框Search_path指定了搜索路径,点击右侧按钮进入如图所示对话框点击add添加库文件所在路径。

Target_library为逻辑综合的目标库,由代工厂提供的 * .db 文件,用相似的方法添加所需库文件。

Link_library是链接库,一般和目标库相同注:“*”这一项要保留,否则链接时会出错,该项指示DC在链接时首先搜索内存中的内容。

Symble_library为指定的符号库,一般为 *.sdb 文件,与单元的库文件对应。

3、设计读入“File > Read”读入设计文件,用此方式读入时在此处不用指定顶层文件,但读入后应马上指明设计的顶层名。

通过左侧的窗口可以观察设计的层次4、链接“File > Link Design”在弹出对话框中点击“ok”即可完成链接。

其执行的相关信息可从命令框中可查看5、实例唯一化当设计中有某个子模块被多次调用时就需要进行实例唯一化,实例唯一化就是将同一个子模块的多个实例生成为多个不同的子设计的过程。

之所以要进行实例唯一化是因为DC在逻辑综合时可能使用不同的电路形式来实现同一个子模块的不同实例,从而这些实例在DC看来是不同的设计(尽管其调用的子模块代码和功能完全相同)。

实现方法:“Hierarchy > Uniquify > Hierarchy ”在弹出对话框中默认点击“ok”即可,命令框中将显示“design_vision-t> uniquify”。

若选中“instances to be renamed even if unique or assigned don’t_touch”则会强制将所调用的模块从新命名,此时命令框中显示“design_vision-t> uniquify –force”。

DC综合

读入HDL代码

File ->Analyze

显示代码的基本单元 File ->E根lab据or代ate码设置参数

显示代码的逻辑层次图

查看原理图

点击快捷图标

选中其中一个放单大元之模后块,,会再看点到击快 捷图标“,GT即E可CH查”看,其说符明号设图计还 未映射到工艺库中

双击模块

Attributes->Operating Environment-

❖ 设计约束 (1)跟设计规则(design rules)相关的约束 ❖ transition times (set_max_transition) ❖ fanoutloads (set_max_fanout) ❖capacitances (set_max_capacitance)

最基本的设计规则在工艺库里会明确的设定 好,因为这关系到芯片能否生产成功的问题。

指定参考库的命令格式:

❖set target_library my_tech.db

--指定目标库

❖set link_library {* my_tech.db}

-

-“*”号表示先查找内存

❖set search_path {./mips/lib} --指定查找路径

❖lappend search_path {./mips/source} -添加查找路径

(2)跟优化相关的约束

❖ 逻辑综合前后应进行的步骤

综合前:对代码进行语法检查(LEDA); 进行功能仿真和验证(Modelsim, Vera, VCS, Scirocco )

综合后:形式验证(Formality); 静态时序分析STA (Prime Time); 仿真与验证(Modelsim, VCS)

Tcl与DesignCompiler(三)——DC综合的流程

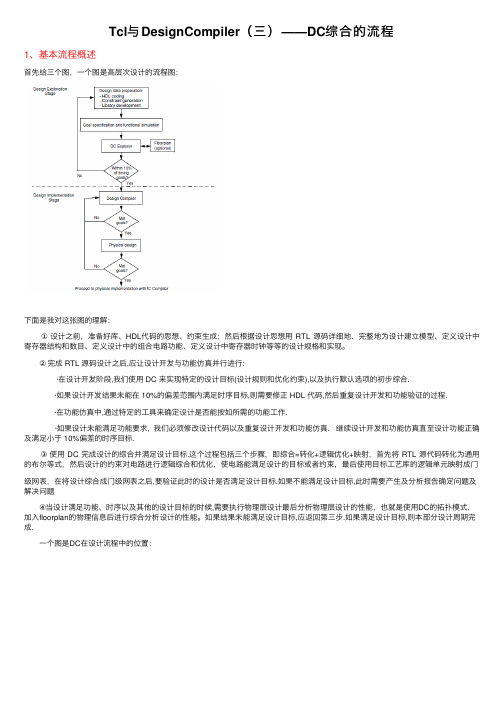

Tcl与DesignCompiler(三)——DC综合的流程1、基本流程概述⾸先给三个图,⼀个图是⾼层次设计的流程图:下⾯是我对这张图的理解: ①设计之前,准备好库、HDL代码的思想、约束⽣成;然后根据设计思想⽤ RTL 源码详细地、完整地为设计建⽴模型、定义设计中寄存器结构和数⽬、定义设计中的组合电路功能、定义设计中寄存器时钟等等的设计规格和实现。

②完成 RTL 源码设计之后,应让设计开发与功能仿真并⾏进⾏: ·在设计开发阶段,我们使⽤ DC 来实现特定的设计⽬标(设计规则和优化约束),以及执⾏默认选项的初步综合. ·如果设计开发结果未能在 10%的偏差范围内满⾜时序⽬标,则需要修正 HDL 代码,然后重复设计开发和功能验证的过程. ·在功能仿真中,通过特定的⼯具来确定设计是否能按如所需的功能⼯作. ·如果设计未能满⾜功能要求, 我们必须修改设计代码以及重复设计开发和功能仿真. 继续设计开发和功能仿真直⾄设计功能正确及满⾜⼩于 10%偏差的时序⽬标. ③使⽤ DC 完成设计的综合并满⾜设计⽬标.这个过程包括三个步骤,即综合=转化+逻辑优化+映射,⾸先将 RTL 源代码转化为通⽤的布尔等式,然后设计的约束对电路进⾏逻辑综合和优化,使电路能满⾜设计的⽬标或者约束,最后使⽤⽬标⼯艺库的逻辑单元映射成门级⽹表,在将设计综合成门级⽹表之后,要验证此时的设计是否满⾜设计⽬标.如果不能满⾜设计⽬标,此时需要产⽣及分析报告确定问题及解决问题 ④当设计满⾜功能、时序以及其他的设计⽬标的时候,需要执⾏物理层设计最后分析物理层设计的性能,也就是使⽤DC的拓扑模式,加⼊floorplan的物理信息后进⾏综合分析设计的性能。

如果结果未能满⾜设计⽬标,应返回第三步.如果满⾜设计⽬标,则本部分设计周期完成. ⼀个图是DC在设计流程中的位置: 这个图将上⾯的流程图细化,着重与DC的部分,描述了使⽤DC进⾏逻辑综合时要做的事,同时,也是对前⾯的流程图解说的图形概述。

利用DC进行逻辑综合

详细布线

版图设计后进 行STA

时序满足将要求吗

no yes

信号一致性(Sign-off) 将设计备份

综合是基于路径的。 设计编辑器(DC)通过使用静态时序分析来计算设计中各路径的时序。时 序路径的种类有四种:输入到寄存器;寄存器到寄存器;寄存器到输出;输入到 输出 1.1.2 初始化文件及系统保留变量 工艺库一般由 ASIC 供应商提供,它必须与 DC 兼容以便用 DC 进行综合。 单元综合的流程:综合的过程 = 转化 + 优化 + 映射。一般,设计的 HDL 源代

它是子设计在设计中的实例(instance)名,在 Synopsys 术语中单元和实 例不区分对待,它们都是单元。 7).引脚(Pin)

它是设计内部单元的输入、输出端,与端口不同的是,端口是设计用来对外

联系的。 这是七类对象类型。不同类型的对象可以使用相同的名字。如果要在在 dc_

shell-t 中发现对象可以使用以下命令: get_designs: 可以得到指定的设计。 get_cells:可以得到指定的单元。 get_nets:可以得到指定的内连线。 get_ports:可以得到指定的端口。 get_clocks:可以得到指定的时钟。 all_inputs:可以得到所有的输入端口。 all_outputs 可以得到所有的输出端口。

ASIC设计流程-DC

--逻辑综合

DDC项目组

基于standcell的ASIC设计流程

Concept + Market Research

Architechtural specs & RTL coding

RTL simulation

No No

Logic Synthesis,Optimization & Scing_conditions -min fast_1v32cm40 -max slow_1v08c125

– link_library:链接库,DC不使用该库中的cells进行映射,它是DC在读 入综合后网表时用来参考的库,RAM,ROM,PAD,macros都应包含在这个 库,目标库和综合库也必须包含在其中。

– symbol_library:指定的符号库,使用GUI时会调用。 – search_path:指明库文件的位置,这样在添加上面的库时就不用写绝对

set_load on output

使用DC进行逻辑综合

• Design Environment

– set_min_library:允许同时设置 worst-case和best-case libraries, 从而在初步编译时,DC修正holdtime violations时,避免出现 setup-time的violation。

PT

Astro AstroRail FORMALITY

PT Hercules

Caliber Virtuoso

使用DC进行逻辑综合

• Setup File

setup file是一个脚本文件,用来指定DC综合时所需的初始化信息,它也可以 和约束文件写在一起,但建议分开写,方便脚本的管理。需要定义的变量有:

使用dc进行逻辑综合的基本步骤

使用dc进行逻辑综合的基本步骤该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

该使用dc进行逻辑综合的基本步骤该文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注。

文档下载说明Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document 使用dc进行逻辑综合的基本步骤can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!DC综合是数字电路设计过程中非常重要的一步,它将逻辑功能描述转换为对应的门级电路。

DC综合教程

启动dc的三种方法:DCSH:dc_shellTCL:dc_shell-t //注意:-t前没有空格图形化界面:design_visiontip1. 综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。

1. 转换阶段:综合工具将高层语言描述的电路用门级的逻辑来实现,对于Synopsys 的综合工具DC 来说,就是使用gtech.db库中的门级单元来组成HDL 语言描述的电路,从而构成初始的未优化的电路。

2. 优化与映射:是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上。

tip2DesignWare 是集成在DC综合环境中的可重用电路的集合DesignWare 分为DesignWare Basic 与DesignWare Foundation,DesignWare Basic 提供基本的电路,DesignWare Foundation提供性能较高的电路结构。

如果需要Foundation的DesignWare,需要在综合的时候设置synthetic_library3。

tip3 日志文件Design Analyzer 在启动时自动在启动目录下面创建两个日志文件:command.log 和view_command.log,用于记录用户在使用Design Compiler 时所执行的命令以及设置的参数,在运行过程中同时还产生filenames.log的文件,用于记录design compiler访问过的目录,包括库、源文件等,filenames.log文件在退出design compiler 时会被自动删除。

启动dc_shell时则只产生command.log 的日志文件。

tip4Propagation Delay传播延时Transition Time转变延时Setup Time建立时间The setup time for a sequential cell is theminimumlength of time the data-inputsignal must remain stable before the active edge of the clockHold Time保持时间The hold time for a sequential cell is the minimum length of time the data-inputsignal must remain stable after the active edge of the clock脚本:################################# Read design file #//read –format verilog[db、vhdl] file //dcsh的工作模式read_db file.db //TCL工作模式读取DB格式read_verilog file.v //TCL工作模式读取verilog格式read_vhdl file.vhd //TCL工作模式读取VHDL格式//设定时钟create_clock -name "clock" -period 20 -waveform { 0.000 10.000 } { clk }//输出文件write -f verilog -out output/count.v //输出网表write -f ddc -out output/count.ddc//综合数据文件write_sdf mapped/count.sdf //标准延时文件//综合compile -map_effort medium -incremental_mappingtip6设置设计环境Define the Design Environment1. Defining the Operating Conditions设置操作环境查看有哪些操作环境dc_shell> read_file my_lib.dbdc_shell> report_lib my_lib指定操作环境dc_shell> set_operating_conditions WCCOM -lib my_lib2.设置线负载模型set_wire_load_mode Top/Enclosed/Segmentedset_wire_load_model "10x10"3. Modeling the System Interface设置系统接口The set_drive and set_input_transition Commands:dc_shell> current_design top_level_designdc_shell> set_drive 1.5 {I1 I2}dc_shell> current_design sub_design2dc_shell> set_driving_cell -lib_cell IV {I3}dc_shell> set_driving_cell -lib_cell AN2 -pin Z -from_pin B {I4} Defining Loads on Input and Output PortsDefining Fanout Loads on Output Ports4. Setting Logic Constraints on Portsset_equal port1 port2set_oppositeset_logic_dcset_logic_oneset_logic_zeroset_unconnectedtip7设定设计约束When Design Compiler optimizes your design, it uses two types of constraints:Design rule constraintsOptimization constraints用于组成逻辑1. Maximum Transition Timedc_shell> set_max_transition 5 [current design]2. Maximum FanoutYou can set a maximum fanout constraint on every driving pin and input port as follows:dc_shell> set_max_fanout 8 [get_designs ADDER]计算Fanout值:Maximum Fanout>=Total Fanout Load注意:取出某些约束用:dc_shell> remove_attribute [get_designs adder] max_transitiondc_shell> remove_attribute [get_ports port_name] max_fanoutdc_shell> remove_attribute [get_designs design_name]max_fanoutdc_shell> remove_attribute port_name fanout_load3. The set_fanout_load command sets the expected fanout load value for listed output ports.To find the fanout load on the input pin of library cell AND2 in library libA, enterdc_shell> get_attribute "libA/AND2/i" fanout_loadTo find the default fanout load set on technology library libA, enterdc_shell> get_attribute libA default_fanout_load用于综合出可以驱动的最大扇出的引脚4. Maximum CapacitanceMaximum capacitance is a design rule constraint. It is set as a pin-level attribute that definesthe maximum total capacitive load that an output pin can drive. That is, the pin cannot connect to a net that has a total capacitance greater than or equal to the maximum capacitance defined at the pin.dc_shell> set_max_capacitance 3 [get_designs adder]5. Minimum CapacitanceThe min_capacitance design rule specifies the minimum load a cell can drive.设计规则的优先权1. Minimum capacitance2. Maximum transition3. Maximum fanout4. Maximum capacitance5. Cell degradationtip8设定优化约束Optimization ConstraintsTiming Constraints对于同步pashscreate_clockset_input_delayset_output_delay对于异步pashsset_max_delayset_min_delayMaximum Areadc_shell> set_max_area 0.0dc_shell> set_max_area 14.0Managing Constraint Prioritiesset_cost_priority [-default] [-delay] cost_listReporting Constraints:dc_shell >report_constraint写脚本tip9:在终端中启动DC用脚本综合dc_shell-t -f ./scripts/seg_drive.tcl > 1将报告写入1文件tip10:设计中有多个模块时,如果用top_down策略,则在脚本中得把所有的模块读入:set active_design seg_drive //注意:相等于一个宏定义,用active_design代替seg_drive read_verilog {encode_seg.v number_mod.v scan.v seg_drive.v} //read_file也可以,它可以读多种格式文件,包括.db#analyze -format verilog {encode_seg.v number_mod.v scan.v seg_drive.v}#elaborate $active_design //注意这里是$active_designcurrent_design $active_design //将顶层设置成当前设计link//read_verilog命令与后面的analyze、elaborate功能相同,可以选择其中一个;参看《ASIC综合与DC使用》:set_svf ./mapped/svf/$active_design.svf //没查###############################################1# Define the Design Environment#1###############################################113Modeling the SystemInterface设置系统接口21)set_operating_conditions slow //设定一个库的环境,库内包含使用温度、电压、电路特征线宽等2)set_wire_load_model –name model_name –lib_name library –max –min//设定线负载模型set_wire_load_model -name tsmc090_wl40 -library slow //表示使用库slow里的tsmc090_wl40线模型如果没有 wire_load_model,可以将 auto_wire_load_selection 参数设置为 true,则 DC自动根据综合之后的面积来选择一个统计的线负载模型用于估计连线延迟。

DC综合流程

综合步骤8:分析修改设计

通常Design Compiler根据设计综合和优化的结果生成众多的报告。根据诸如面积、 约束和时序报告来分析和解决任何设计问题,或者改进综合结果。

需要的报告: report_design:报告用户的综合环境,包括operating condition、wire load report_constraint:用户定义的constraint report_timing -nworts num :所有路径中最差的路径。

DC综合流程

提纲

• 综合概述

• 技术库概述

• 综合基本步骤

综合概念

● 逻辑综合:决定设计电路逻辑门的相互连接。

● 逻辑综合的目的:决定电路门级结构、寻求时序和与面积的平衡、寻求功 耗与时序的平衡、增强电路的测试性。

● 逻辑综合的过程:Translation 、map 、optimization Translation是指把设计的HDL描述转化为GTECH库元件组成的逻辑电路

综合步骤4:design environment

1、operating condition

operating condition包括工作温度、工作电压、制造工艺,通过命令 set_operating_condition来设定

命令set_operating_conditions –min BEST –max WORST用于指示DC对WORST 和BEST条件,同时优化。WORST用于对setup-time进行优化,BEST用于对holdtime进行优化,当BEST和WORST都满足时,TYPICAL也就可以满足。

综合步骤7:优化设计

DC综合操作流程_设置流程

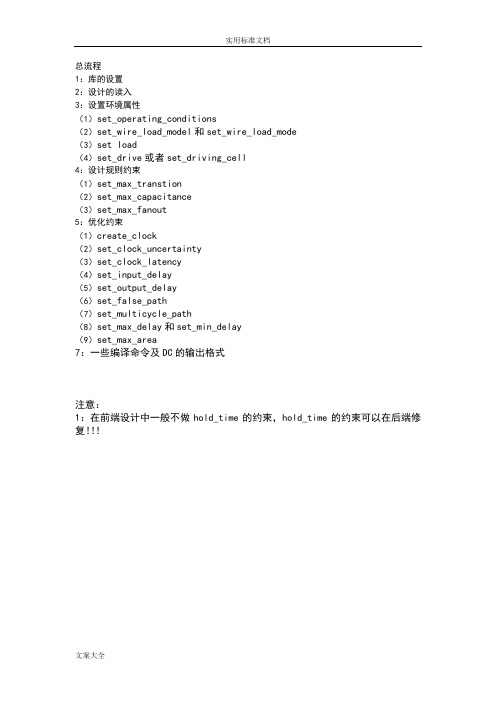

总流程1:库的设置2:设计的读入3:设置环境属性(1)set_operating_conditions(2)set_wire_load_model和set_wire_load_mode(3)set load(4)set_drive或者set_driving_cell4:设计规则约束(1)set_max_transtion(2)set_max_capacitance(3)set_max_fanout5:优化约束(1)create_clock(2)set_clock_uncertainty(3)set_clock_latency(4)set_input_delay(5)set_output_delay(6)set_false_path(7)set_multicycle_path(8)set_max_delay和set_min_delay(9)set_max_area7:一些编译命令及DC的输出格式注意:1:在前端设计中一般不做hold_time的约束,hold_time的约束可以在后端修复!!!总流程:1:对库进行基本设置,如下:设置完成后应该查看.synopsys_dc.setup里面库的设置和软件application setup处的设置是否一样!DC的初始化文件.synopsys.dc.setup需要用ls –a显示,命令:more .synopsys.dc.setup 查看文件内容!2:读入设计,两种方法:read和analyze+elaborateAnalyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下;Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件中的第一个库的工作环境作为优化时使用的工作环境。

(1)set_operating_conditions:工作条件包括三方面—温度、电压以及工艺;工作条件一般分三种情况:best case, typical case, worst case图形界面:#1:先进入the symbol view of the top界面,选择top模块#2:attributes—operating environment—operating conditions命令方式:#1:可通过report_lib libraryname命令来查看,如下图查看的是slow.db库的工作条件,则使用命令:report_lib slow,右边是report_lib fast。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DC逻辑综合使用流程

vlsi设计中心806凌金

启动软件::

1、启动软件

新开一个terminal窗口,输入命令:design_vision,回车即可开启图形界面,进入图形界面后可通过菜单、对话框等来实现DC的功能,相关的命令操作同样可以使用。

2、指定相关库文件

指定相关库文件及及路径

“File > Setup”打开下图所示对话框

Search_path指定了搜索路径,点击右侧按钮进入如图所示对话框点击add添加库文件所在路径。

Target_library为逻辑综合的目标库,由代工厂提供的* .db 文件,用相似的方法添加所需库文件。

Link_library是链接库,一般和目标库相同

注:“*”这一项要保留,否则链接时会出错,该项指示DC在链接时首先搜索内存中的内容。

Symble_library为指定的符号库,一般为*.sdb 文件,与单元的库文件对应。

3、设计读入

“File > Read”读入设计文件,用此方式读入时在此处不用指定顶层文件,但读入后应马上指明设计的顶层名。

通过左侧的窗口可以观察设计的层次

4、链接

“File > Link Design”在弹出对话框中点击“ok”即可完成链接。

其执行的相关信息可从命令框中可查看

5、实例唯一化

当设计中有某个子模块被多次调用时就需要进行实例唯一化,实例唯一化就是将同一个子模块的多个实例生成为多个不同的子设计的过程。

之所以要进行实例唯一化是因为DC在逻辑综合时可能使用不同的电路形式来实现同一个子模块的不同实例,从而这些实例在DC看来是不同的设计(尽管其调用的子模块代码和功能完全相同)。

实现方法:“Hierarchy > Uniquify > Hierarchy ”在弹出对话框中默认点击“ok”即可,命令框中将显示“design_vision-t> uniquify”。

若选中“instances to be renamed even if unique or assigned don’t_touch”则会强制将所调用的模块从新命名,此时命令框中显示“design_vision-t> uniquify –force”。

6、设置电路的工作环境

“Attributes > Operating Environment > Operating conditions”

选折相应的库和其对应的条件点击“Apply”添加,添加完成后点击“ok”关闭对话框。

7、设置连线负载

“Attributes > Operating Environment > Wire Load”

本实例中所用的库有两种连线负载模式“TOP 对应上图TB60C”和“Macro对应MB60C_*”

8、设置输出负载

点击工具栏中“芯片样式”的图标开启符号窗口,选中要设置的输出引脚(可多选),然后点击“Attributes > Operating Environment > Load”打开设置对话框进行设置。

默认电容单位为pf

9、设置输入驱动

方法与上类似,选折需要设置的输入引脚“Attributes > Operating Environment > Drive Strength”打开设置对话框进行相应的设置。

由于通常情况下,设计的时钟端由驱动能力很大的单元或树形缓冲来驱动,所以可以将其驱动能力设为无穷大,即将其阻抗设为0。

如本设计中时钟端口名称为“DCLK”,则只需在命令窗口中输入“set_drive 0 DCLK”即可。

复位端口一般也做相同的处理。

10、创建时钟

选中时钟端口如本设计中的“DCLK”,“Attributes > Specify Clock ”打开设置框

分别填入周期、上升时刻、下降时刻后点击“Apply”,便可在下面窗口中看到时钟波形。

如图生成的是一个周期为25占空比为1:1的时钟。

默认时钟单位为“ns”。

由于时钟端口的负载很大,DC会使用Buffer来增加其驱动能力。

但一般设计者都使用布局布线工具来完成此项工作,所以有必要指示DC不要对时钟网络进行修改,可以选中上图中“Don’t touch network”进行设置。

11、设置输入延时

选中需要设置的输入端口(可多选)“Attributes > Operating Environment > Input Delay”

进行相应设置后点击“OK”

12、设置输出延时

“Attributes > Operating Environment > Output Delay”

设置方式与input delay 完全类似。

如果是从寄存器直接输出,则可以不设置输出延时,因为触发器的输出延时基本是固定的。

13、设置面积约束

“Attributes > Optimization Constraints > Design Constraints”

在Max area中填入0,这样能够尽可能的对面积进行优化。

然后点击“ok”

14、逻辑综合

完成以上基本设定之后便可以对设计进行逻辑综合

“Design > Compile Design”

选折默认设置,点击“ok”

15、查看综合结果

等综合完毕之后,可以从“Design > Repot * ”查看相应的综合报告16、保存综合后的网表文件(*.V)

“File > Save As”打开对话框,Format 选折“Verilog (v)”

17、导出时序文件(*.SDF)

“File > Save Info > Design Timing”

Instance项不选,保持空白。

这样能直接保存与最顶层相对应的延时文件。

之后可用此文件进行综合后的仿真。

“write_sdf /space/FPAA/DC/DIGITAL.sdf”(居然也可以。

)

18、导出设计约束文件(*.SDC)

该操作可以用write_sdc命令实现。

(可参考在用图形界面保存SDF文件时,命令框中出现的与图形界面操作相对应的命令语句)

如:“write_sdc /space/FPAA/DC/DIGITAL.sdc”

执行之后会把DIGITAL.sdc文件保存在/space/FPAA/DC文件夹中。

该文件在会面做布局布线时将会被使用到。

补充:

补充

在每完成一步或几步设置之后应及时对设置进行保存和备份,保存格式为db。

这样只要读入该文件就会读入之前进行的设置。

(不过库文件及路径等需要从新设置)。