模拟锁相环实验报告

实验报告一 模拟锁相环模块

模拟锁相环模块信息工程学院08级电子班安艳芳0839107一、实验目的1、熟悉模拟锁相环的基本工作原理2、掌握模拟字锁相环的基本参数及设计二、实验仪器JH5001通信原理综合实验系统(一台)、20MHz双踪示波器(一台)、函数信号发生器(一台)三、实验原理和电路说明锁相的重要性:在电信网中,同步是一个十分重要的概念。

其最终目的使本地终端时钟源锁定在另一个参考时钟源上。

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一在系统工作中模拟锁相环将接收端的256KHz时钟锁在发端的256KHz的时钟上,来获得系统的同步时钟,如HDB3接收的同步时钟及后续电路同步时钟。

该模块主要由模拟锁相环UP01(MC4046)、数字分频器UP02(74LS161)、D触发器UP04(74LS74)、环路滤波器和由运放UP03(TEL2702)及阻容器件构成的输入带通滤波器(中心频率:256KHz)组成。

因来自发端信道的HDB3码为归零码,归零码中含有256KHz时钟分量,经UP03B构成中心频率为256KHz 有源带通滤波器后,滤出256KHz时钟信号,该信号再通过UP03A放大,然后经UP04A和UP04B两个除二分频器(共四分频)变为64KHz信号,进入UP01鉴相输入A脚;VCO输出的512KHz输出信号经UP02进行八分频变为64KHz信号,送入UP01的鉴相输入B脚。

经UP01内部鉴相器鉴相之后的误差控制信号经环路滤波器滤波送入UP01的压控振荡器输入端;WP01可以改变模拟锁相环的环路参数。

正常时,VCO 锁定在外来的256KHz频率上。

模拟锁相环模块各跳线开关功能如下:1、跳线开关KP01用于选择UP01的鉴相输出。

当KP01设置于1_2时(左端),环路锁定时TPP03、TPP05输出信号将存在一定相差;当KP01设置于2_3时(右端),选择三态门鉴相输出,环路锁定时TPP03、TPP05输出信号将不存在相差。

模拟锁相环实验报告

模拟锁相环实验报告锁相环(PLL)是一种常见的控制系统,它可以将输入信号的频率和相位与参考信号匹配,从而实现精确的信号同步和频率锁定。

本次实验旨在通过模拟锁相环的实验,了解PLL的基本原理和实现方式,并探究其在频率合成和时钟恢复等应用中的优势和局限性。

一、实验原理1.1 PLL的基本原理PLL由相频比较器、环形控制器、振荡器和分频器等组成。

其基本原理如下:(1)将参考信号和输出信号输入相频比较器,得到误差信号;(2)将误差信号输入环形控制器,控制其输出的控制电压;(3)将控制电压输入振荡器,控制其输出的频率和相位;(4)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制。

通过不断比较和修正,PLL可以使输出信号的频率和相位与参考信号匹配,从而实现锁定。

1.2 实验器材本次实验采用的器材如下:信号发生器、示波器、多路开关、振荡器、计数器等。

1.3 实验步骤(1)将信号发生器产生的正弦波信号作为参考信号,通过示波器观测其频率和相位;(2)将信号发生器产生的方波信号作为输入信号,通过多路开关控制输入信号的频率和幅值;(3)将输入信号和参考信号输入相频比较器,得到误差信号;(4)将误差信号输入环形控制器,控制其输出的控制电压;(5)将控制电压输入振荡器,控制其输出的频率和相位;(6)将振荡器的输出信号通过分频器分频后反馈给相频比较器,形成闭环控制;(7)通过计数器观测输出信号的频率和相位,调整环形控制器的参数,使输出信号与参考信号匹配。

二、实验结果在实验过程中,我们先设置参考信号的频率为1KHz,通过示波器观测其频率和相位,然后将信号发生器产生的方波信号作为输入信号,进行频率和幅值的调节,使其与参考信号匹配。

在调节的过程中,我们观测到输出信号的频率和相位逐渐趋近于参考信号的频率和相位,最终实现了同步锁定。

然后,我们进一步测试了PLL在频率合成和时钟恢复等应用中的性能。

我们将输入信号的频率和幅值进行变化,观测输出信号的变化情况。

模拟锁相环实验报告

模拟锁相环实验报告实验一模拟锁相环模块一、实验原理和电路说明模拟锁相环模块在通信原理综合实验系统中可作为一个独立的模块进行测试。

在系统工作中模拟锁相环将接收端的256KHz 时钟锁在发端的256KHz 的时钟上,来获得系统的同步时钟,如HDB3接收的同步时钟及后续电路同步时钟。

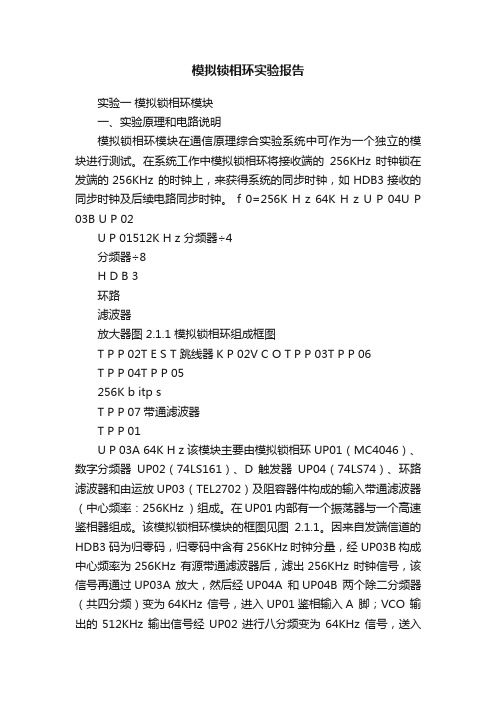

f 0=256K H z 64K H z U P 04U P 03B U P 02U P 01512K H z 分频器÷4分频器÷8H D B 3环路滤波器放大器图 2.1.1 模拟锁相环组成框图T P P 02T E S T 跳线器K P 02V C O T P P 03T P P 06T P P 04T P P 05256K b itp sT P P 07带通滤波器T P P 01U P 03A 64K H z 该模块主要由模拟锁相环UP01(MC4046)、数字分频器UP02(74LS161)、D 触发器UP04(74LS74)、环路滤波器和由运放UP03(TEL2702)及阻容器件构成的输入带通滤波器(中心频率:256KHz )组成。

在UP01内部有一个振荡器与一个高速鉴相器组成。

该模拟锁相环模块的框图见图2.1.1。

因来自发端信道的HDB3码为归零码,归零码中含有256KHz 时钟分量,经UP03B 构成中心频率为256KHz 有源带通滤波器后,滤出256KHz 时钟信号,该信号再通过UP03A 放大,然后经UP04A 和UP04B 两个除二分频器(共四分频)变为64KHz 信号,进入UP01鉴相输入A 脚;VCO 输出的512KHz 输出信号经UP02进行八分频变为64KHz 信号,送入UP01的鉴相输入B 脚。

经UP01内部鉴相器鉴相之后的误差控制信号经环路滤波器滤波送入UP01的压控振荡器输入端;WP01可以改变模拟锁相环的环路参数。

正常时,VCO 锁定在外来的256KHz 频率上。

模拟锁相环模块各跳线开关功能如下:1、跳线开关KP01用于选择UP01的鉴相输出。

实验五锁相环测试及应用实验报告

:锁相环测试及应用实验试验目的:1.了解锁相环的组成、基本原理及性能特点。

2.掌握集成锁相环4046芯片的使用方法。

3.掌握锁相环路及各部件性能(鉴相特性、压控特性、同步带和捕捉带)的测试方法。

4.掌握锁相调频、锁相鉴频电路的构成、基本原理及参数测试测试方法。

5.掌握简单锁相频率合成器的基本原理及性能指标的测试方法实验设备:1.调幅与调频发射模块。

2.直流稳压电压GPD-3303D3.F20A 型数字合成函数发生器/计数器 4.DSO-X 2014A 数字存储示波器实验原理:1. 锁相环的组成及基本原理锁相环路(PLL )亦称自动相位控制(APC )电路,它是一种利用相位误差消除频率误差的反馈控制系统。

如图1所示,由鉴相器(相位比较器)、环路滤波器(低通滤波器)和压控振荡器三个基本部件组成。

若o i f f ≠,瞬时相位差ϕ∆将随时间而变化;若i of f ϕ∆=保持固定值。

锁相环就是利用两个信号之间相位差的变化,控制压控振荡器的输出信号频率,最终使两个信号相位差保持为常数,达到频率相等。

锁相环的工作过程:如图1所示,若o i f f ≠,必将引起ϕ∆的变化,鉴相器输出正比于ϕ∆的误差电压()d u t 。

经环路滤波器滤除()d u t 中的高频分量和噪声,产生缓慢变动的直流电压()c u t 。

VCO 受控于()c u t ,使得振荡频率o f 与输入参考频率i f 的频差逐渐减小,直到o i f f =,电路达到稳定平衡状态,即锁定状态。

此时,ϕ∆保持一个不变的稳态相差ϕ∞,以维持电路的平衡状态。

需要指出,环路能达到锁定状态,是在o f 与i f 相差不大的范围内。

2. 几个重要概念 ⑴ 失锁与锁定开始工作时, o i f f ≠,ϕ∆不固定,环路处于不稳定状态,称为失锁。

当o i f f =时,ϕ∆保持常数,电路进入稳定状态,称为锁定。

⑵ 跟踪过程与捕捉过程在环路锁定状态下,如果输入信号频率i f 发生变化,环路通过自身的调节作用,使输出信号频率o f 以同样的规律跟随着变化,并且始终保持o i f f =,这个过程称为跟踪过程或同步过程。

锁相环实验报告

锁相环实验报告锁相环实验报告一、实验目的本次实验的目的是了解锁相环(PLL)的原理和应用,掌握PLL电路的设计和调试方法,以及了解PLL在通信系统中的应用。

二、实验原理1. PLL原理锁相环是一种基于反馈控制的电路,由比例积分环节、相位检测器、低通滤波器和振荡器等组成。

其基本原理是将输入信号与参考信号进行比较,并通过反馈调整振荡频率,使得输入信号与参考信号同步。

2. PLL应用PLL广泛应用于通信系统中,如频率合成器、时钟恢复器、数字调制解调器等。

三、实验设备和材料1. 实验仪器:示波器、函数发生器等。

2. 实验元件:电阻、电容等。

四、实验步骤1. 搭建PLL电路并连接到示波器上。

2. 调节函数发生器输出正弦波作为参考信号,并将其输入到PLL电路中。

同时,在函数发生器上设置另一个正弦波作为输入信号,并将其连接到PLL电路中。

3. 调节PLL参数,包括比例积分系数和低通滤波器截止频率等,使得输入信号与参考信号同步。

4. 观察示波器上的输出波形,记录下PLL参数的取值。

五、实验结果与分析1. 实验结果通过调节PLL参数,成功实现了输入信号与参考信号的同步,并在示波器上观察到了稳定的输出波形。

记录下了PLL参数的取值,如比例积分系数和低通滤波器截止频率等。

2. 实验分析通过本次实验,我们深入了解了锁相环的原理和应用,并掌握了PLL电路的设计和调试方法。

同时,我们也了解到PLL在通信系统中的重要作用,如时钟恢复、数字调制解调等。

六、实验结论本次实验成功地实现了输入信号与参考信号的同步,并掌握了PLL电路的设计和调试方法。

同时也加深对于PLL在通信系统中应用的认识。

七、实验注意事项1. 在搭建电路时应注意接线正确性。

2. 在调节PLL参数时应注意逐步调整,避免过度调整导致系统失控。

3. 在观察示波器输出波形时应注意放大倍数和时间基准设置。

实验四锁相环应用电路实验

实验三锁相环应用电路实验一、实验目的1.掌握锁相环的组成及基本工作原理;2.了解锁相环应用电路的设计方法。

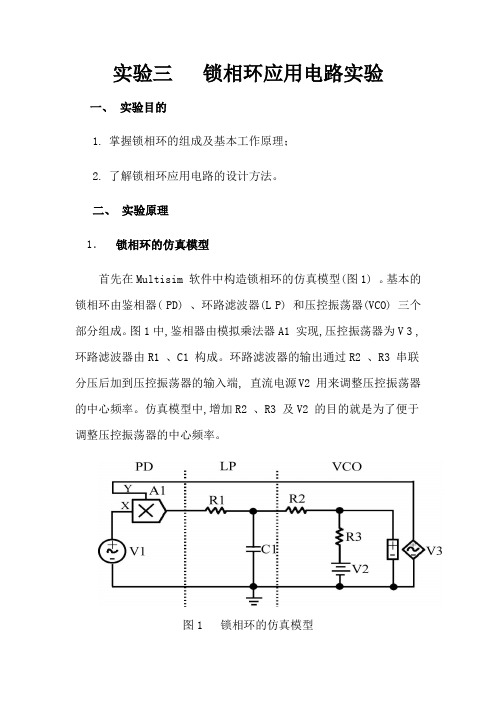

二、实验原理1.锁相环的仿真模型首先在Multisim 软件中构造锁相环的仿真模型(图1) 。

基本的锁相环由鉴相器( PD) 、环路滤波器(L P) 和压控振荡器(VCO) 三个部分组成。

图1中,鉴相器由模拟乘法器A1 实现,压控振荡器为V 3 ,环路滤波器由R1 、C1 构成。

环路滤波器的输出通过R2 、R3 串联分压后加到压控振荡器的输入端, 直流电源V2 用来调整压控振荡器的中心频率。

仿真模型中,增加R2 、R3 及V2 的目的就是为了便于调整压控振荡器的中心频率。

图1 锁相环的仿真模型2.锁相环调频的仿真电路直接调频电路的振荡器中心频率稳定度较低,而采用晶体振荡器的调频电路,其调频范围又太窄。

采用锁相环的调频器可以解决这个矛盾。

其结构原理如图2 所示。

图2 锁相环调频电路的原理框图实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外,也就是说,锁相环路只对慢变化的频率偏移有响应,使压控振荡器的中心频率锁定在稳定度很高的晶振频率上。

而随着输入调制信号的变化,振荡频率可以发生很大偏移。

图3 锁相环调频的仿真电路根据图2 建立的仿真电路如图3 所示。

图中,设置压控振荡器V 1 在控制电压为0 时,输出频率为0 ;控制电压为5V 时,输出频率50kHz 。

这样,实际上就选定了压控振荡器的中心频率为25kHz ,为此设定直流电压V 3 为2.5V 。

调制电压V 4 通过电阻R5 接到VCO 的输入端, R5 实际上是作为调制信号源V 4 的内阻,这样可以保证加到VCO 输入端的电压是低通滤波器的输出电压和调制电压之和,从而满足了原理图的要求。

本电路中,相加功能也可以通过一个加法器来完成,但电路要变得相对复杂一些。

VCO 输出波形和输入调制电压V 4 的关系如图4 所示。

由图可见,输出信号频率随着输入信号的变化而变化,从而实现了调频功能。

滤波法及数字锁相环法位同步提取实验-模拟锁相环实验-载波同步帧同步实验

实验十九滤波法及数字锁相环法位同步提取实验实验项目三数字锁相环法位同步观测(1)观测“数字锁相环输入”和“输入跳变指示”,观测当“数字锁相环输入”没有跳变和有跳变时“输入跳变指示”的波形。

(2)观测“数字锁相环输入”和“鉴相输出”。

观测相位超前滞后的情况从图中可以观察出,若前一位数据有跳变,则判断有效,“输入跳变指示”输出表示1;否则,输出0表示判断无效。

数字锁相环的超前—滞后鉴相器需要排除位流数据输入连续几位码值保持不变的不利影响。

在有效的相位比较结果中仅给出相位超前或相位滞后两种相位误差极性,而相位误差的绝对大小固定不变。

经观察比较,“鉴相输出”比“数字锁相环输入”超前两个码元。

(3)观测“插入指示”和“扣除指示”。

思考题:分析波形有何特点,为什么会出现这种情况。

因为可变分频器的输出信号频率与实验所需频率接近,将其和从信号中提取的相位参考信号同时送入相位比较器,比较的结果若是载波频率高了,就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲,相当于本地振荡频率上升,从而了达到同步的目的。

思考题:BS2恢复的时钟是否有抖动的情况,为什么?试分析BS2抖动的区间有多大?如何减小这个抖动的区间?有抖动的存在,是因为可变分频器的存在使得下一个时钟沿的到来时间不确定,从而引入了相位抖动。

而这种引入的误差是无法消除的。

减小相位抖动的方法就是将分频器的分频数提高。

实验二十模拟锁相环实验实验项目一VCO自由振荡观测(1)示波器CH1接TH8,CH2接TH4输出,对比观测输入及输出波形。

对比波形可以发现TH8与TH4信号输入与输出错位半个周期实验项目二同步带测量(1)示波器CH1接13号模块TH8模拟锁相环输入,CH2接TH4输出BS1,观察TH4输出处于锁定状态。

将正弦波频率调小直到输出波形失锁,此时的频率大小f1为400Hz ;将频率调大,直到TH4输出处于失锁状态,记下此时频率f2为9.25kHz 。

锁相实验心得(通用5篇)

锁相实验心得(通用5篇)锁相实验心得篇1锁相实验是一种用于研究信号处理和系统同步的重要实验方法。

在本次实验中,我们主要探讨了锁相环路的原理、设计及其在控制系统中的应用。

通过本次实验,我对锁相环路的原理和设计有了更深入的理解,并在实践中提高了自己的技能。

在实验中,我们首先介绍了锁相环路的背景和意义。

作为一种常见的信号处理方法,锁相环路在许多领域中都有着广泛的应用,如通信、控制和测量等。

通过对其工作原理和特性的学习,我对锁相环路的应用有了更清晰的认识。

接着,我们详细讲解了锁相环路的原理和设计。

通过模拟仿真和实际电路搭建,我对锁相环路的性能和参数调整有了更深入的了解。

我学会了如何根据具体应用场景选择合适的环路带宽、相位裕度等参数,以实现系统同步和稳定。

在实验过程中,我遇到了一些问题,如电路调试不成功、参数调整不当等。

通过查阅资料和与同学讨论,我找到了问题的原因并加以解决。

这些问题让我更加深入地理解了锁相环路的原理和设计,提高了我的实践技能。

通过本次实验,我收获颇丰。

我深刻理解了锁相环路的原理和设计,掌握了其应用技巧。

同时,我也发现了自己在实验中的不足之处,如对电路理论知识的欠缺、实验技能的提升等。

在未来的学习和工作中,我将继续努力,提高自己的理论水平和实践能力,以更好地应对各种挑战。

总之,本次实验让我对锁相环路的原理和设计有了更深入的理解,提高了我的实践技能。

我将继续深入学习相关理论,并将其应用于实践中,为未来的研究和工作打下坚实的基础。

锁相实验心得篇2在进行锁相实验的过程中,我不仅加深了对相关理论知识的理解,还提高了自己的实验技能。

这次经历使我对信号处理和自动控制有了更深入的认识。

在实验中,我首先根据实验要求,搭建了锁相实验的电路。

我仔细检查了电路连接,确保无误。

然后,我输入待测信号,并观察了实验结果。

通过对比实验结果和预期结果,我发现自己的实验技能有了显著提高。

在实验过程中,我遇到了一些问题。

例如,在调整电路参数时,我无法使输入信号与反馈信号保持相位同步。

锁相环实验报告

锁相环实验报告锁相环实验报告引言:锁相环(Phase-Locked Loop,简称PLL)是一种常见的电子系统控制技术,广泛应用于通信、测量、信号处理等领域。

本实验旨在通过设计和搭建一个基本的锁相环电路,深入理解锁相环的原理和应用。

一、实验目的本实验的主要目的是通过搭建锁相环电路,实现对输入信号的频率、相位的跟踪和稳定。

具体目标包括:1. 理解锁相环的基本原理和工作方式;2. 学会设计和搭建基本的锁相环电路;3. 通过实验验证锁相环的频率和相位跟踪性能。

二、实验原理1. 锁相环的基本原理锁相环是一种反馈控制系统,由相位比较器、低通滤波器、电压控制振荡器(Voltage Controlled Oscillator,简称VCO)和分频器组成。

其基本原理如下:(1)相位比较器:将输入信号和VCO输出信号进行相位比较,输出相位误差信号;(2)低通滤波器:对相位误差信号进行滤波,得到控制量;(3)VCO:根据控制量调整输出频率,使其与输入信号保持相位同步;(4)分频器:将VCO输出信号分频后反馈给相位比较器,形成闭环控制。

2. 锁相环的应用锁相环广泛应用于频率合成、时钟恢复、频率/相位调制解调等领域。

例如,在通信系统中,锁相环常用于时钟恢复电路,保证数据传输的稳定性和可靠性。

三、实验内容与步骤1. 实验器材与元件准备(1)信号发生器:产生待测频率的正弦信号;(2)锁相环芯片:如CD4046、PLL565等;(3)电阻、电容等元件:用于搭建锁相环电路;(4)示波器:用于观测和分析实验结果。

2. 搭建锁相环电路根据锁相环的基本原理和实验要求,设计和搭建一个简单的锁相环电路。

电路中包括相位比较器、低通滤波器、VCO和分频器等模块,并连接好电源和地线。

3. 实验操作步骤(1)将信号发生器的输出信号接入锁相环电路的输入端;(2)调节信号发生器的频率,观察锁相环的跟踪效果;(3)通过示波器观察锁相环输出信号的频率和相位稳定性。

锁相环实验

模拟锁相环实验一、实验目的1、 了解用锁相环构成的调频波解调原理。

2、 学习用集成锁相环构成的锁相解调电路。

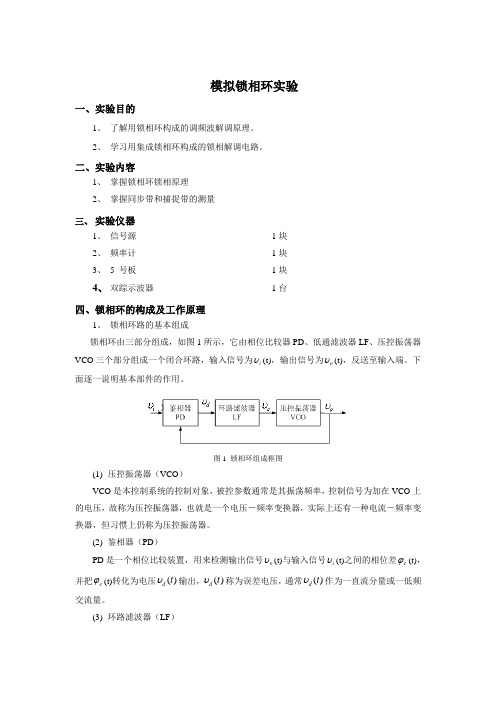

二、实验内容1、 掌握锁相环锁相原理2、 掌握同步带和捕捉带的测量三、 实验仪器1、 信号源 1块2、 频率计 1块3、 5 号板 1块4、 双踪示波器 1台四、锁相环的构成及工作原理1、 锁相环路的基本组成锁相环由三部分组成,如图1所示,它由相位比较器PD 、低通滤波器LF 、压控振荡器VCO 三个部分组成一个闭合环路,输入信号为i υ(t),输出信号为o υ(t),反送至输入端。

下面逐一说明基本部件的作用。

图1 锁相环组成框图(1) 压控振荡器(VCO )VCO 是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO 上的电压,故称为压控振荡器,也就是一个电压-频率变换器,实际上还有一种电流-频率变换器,但习惯上仍称为压控振荡器。

(2) 鉴相器(PD )PD 是一个相位比较装置,用来检测输出信号o υ(t)与输入信号i υ(t)之间的相位差e ϕ(t),并把e ϕ(t)转化为电压()d t υ输出,()d t υ称为误差电压,通常()d t υ作为一直流分量或一低频交流量。

(3) 环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在()d t υ中产生的无用的组合频率分量及干扰,产生一个只反映e ϕ(t)大小的控制信号()c t υ。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使o υ(t)与i υ(t)的相位差e ϕ(t)发生变化,该相位差经过PD 转换成误差电压()d t υ,此误差电压经LF 滤波后得到()c t υ,由()c t υ去改变VCO 的振荡频率使其趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即()()d e t t υϕ∝因此在锁定状态,e ϕ(t)不可能为零,换言之在锁定状态o υ (t)与i υ(t)仍存在相位差。

实验八 模拟锁相环应用实验

实验八模拟锁相环应用实验一、实验目的1、掌握模拟锁相环的组成及工作原理。

2、学习用集成锁相环构成锁相解调电路。

3、学习用集成锁相环构成锁相倍频电路。

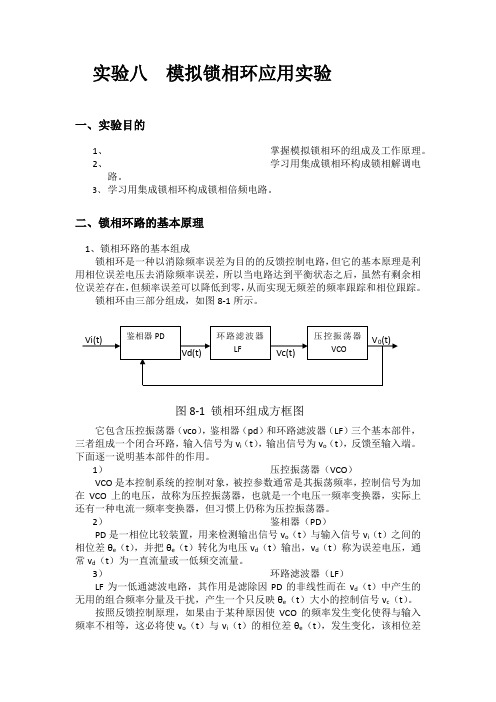

二、锁相环路的基本原理1、锁相环路的基本组成锁相环是一种以消除频率误差为目的的反馈控制电路,但它的基本原理是利用相位误差电压去消除频率误差,所以当电路达到平衡状态之后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。

锁相环由三部分组成,如图8-1所示。

图8-1 锁相环组成方框图它包含压控振荡器(vco),鉴相器(pd)和环路滤波器(LF)三个基本部件,三者组成一个闭合环路,输入信号为v i(t),输出信号为v o(t),反馈至输入端。

下面逐一说明基本部件的作用。

1)压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压一频率变换器,实际上还有一种电流一频率变换器,但习惯上仍称为压控振荡器。

2)鉴相器(PD)PD是一相位比较装置,用来检测输出信号v o(t)与输入信号v i(t)之间的相位差θe(t),并把θe(t)转化为电压v d(t)输出,v d(t)称为误差电压,通常v d(t)为一直流量或一低频交流量。

3)环路滤波器(LF)LF为一低通滤波电路,其作用是滤除因PD的非线性而在v d(t)中产生的无用的组合频率分量及干扰,产生一个只反映θe(t)大小的控制信号v c(t)。

按照反馈控制原理,如果由于某种原因使VCO的频率发生变化使得与输入频率不相等,这必将使v o(t)与v i(t)的相位差θe(t),发生变化,该相位差经过PD转换成误差电压v d(t),此误差电压经LF滤波后得到v c(t),由v c(t)去改变VCO的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即v d(t)∝θe(t)因此在锁定状态,θe(t)不可能为0,换言之在锁定状态v o(t)与v i(t)仍存在相位差。

锁相环仿真报告

ωn =

2 BL ; 1 ζ+ 4ζ

τ1 =

Kd Kr

ω

2 n

;

τ2 =

2ζ

ωn

。

2. 仿真分析(使用 Matlab 中的 Simulink)

(1) 仿真参数 3 给定 ζ=0.707,Kd=4V/rad,Kr=24π×10 rad/(V·S),BL=10Hz,计算得 ωn=19rad/s, τ1=848s,τ2=0.075s,环路滤波器传递函数

0

0.1

0.2

0.3

1/ 2

τ ⎛ Kd Kr ⎞ ⎟ , ζ = ωn = 2 ⎜ ⎟ 2 2⎜ ⎝ τ1 ⎠ τ2

1/ 2

它是传递函数的幅频曲线的最高点对应的频率; ζ 为环路阻尼系数, ωn 为自然谐振频率, 它表示了传递函数幅频响应最大值的衰减程度,该值越大,传递函数幅频曲线最高点越小。 环路噪声带宽 BL 可用 ωn 和 ζ 来表示

BL =

ωn

2

(ζ +

1 ) 4ζ

环路噪声带宽是幅频响应下降到 3dB 时的频宽。

二. 锁相环的锁定过程分析

1. 环路捕获过程的几种情况

① 快捕过程

3

起始频差很小,即输入输出的相差 θe(t)动态变化频率很小,使得 Z(t)的变化不超过一个 周期时环路就进入锁定状态。此时 θe(t)的变化不超过 2π,这种捕获过程称为快捕过程。 快捕带:使得 θe(t)在 2π 之内环路就进入锁定的最大起始频差。 ② 频率牵引的捕捉过程 随着起始频差增大, 相位误差 θe(t)的频率增大, 则误差电压信号 ε(t)频率增大, 此时 ε(t) 通过环路滤波器(低通)有衰减。如果衰减后的误差信号不至于使 Z(t)接近于 0,而是对压控 振荡器(VCO)还是有一定的控制作用,则 VCO 输出频率会逐渐向着输入频率靠近,这就使 得误差信号 ε(t)的频率得到降低,通过环路滤波器的衰减变弱,Z(t)变大,对 VCO 的控制作 用逐渐变大,直到最后进入锁定过程。 捕捉带:可以通过频率牵引过程使环路进入锁定状态的最大起始频差。 ③ 环路无法锁定情况 当起始频差很大,使得误差信号 ε(t)不能通过环路滤波器,Z(t)接近于 0,不能对 VCO 进行电压控制,则 VCO 的输出频率和相位不发生变化,环路不能锁定。

锁相环应用电路仿真

高频电子线路实训报告锁相环路仿真设计专业学生姓名学号2015 年 6 月24日锁相环应用电路仿真锁相环是一种自动相位控制系统,广泛应用于通信、雷达、导航以及各种测量仪器中。

锁相环及其应用电路是“通信电子电路”课程教学中的重点容,但比较抽象,还涉及到新的概念和复杂的数学分析。

因此无论是教师授课还是学生理解都比较困难。

为此,我们将基于Multisim的锁相环应用仿真电路引入课堂教学和课后实验。

实践证明,这些仿真电路可以帮助学生对相关容的理解,并为进行系统设计工作打下良好的基础。

锁相环的应用电路很多,这里介绍锁相环调频、鉴频及锁相接收机的Multisim仿真电路。

1.锁相环的仿真模型首先在Multisim软件中构造锁相环的仿真模型(图1)。

基本的锁相环由鉴相器(PD)、环路滤波器(I P)和压控振荡器(VCO)三个部分组成。

图中,鉴相器由模拟乘法器A 实现,压控振荡器为V3,环路滤波器由R1、C1构成。

环路滤波器的输出通过R2、R3串联分压后加到压控振荡器的输入端,直流电源V2用来调整压控振荡器的中心频率。

仿真模型中,增加R2、R3及的目的就是为了便于调整压控振荡器的中心频率。

图1 锁相环的仿真模型2.锁相接收机的仿真电路直接调频电路的振荡器中心频率稳定度较低,而采用晶体振荡器的调频电路,其调频围又太窄。

采用锁相环的调频器可以解决这个矛盾。

其结构原理如图2所示。

图2 锁相环调频电路的原理框图实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外,也就是说,锁相环路只对慢变化的频率偏移有响应,使压控振荡器的中心频率锁定在稳定度很高的晶振频率上。

而随着输人调制信号的变化,振荡频率可以发生很大偏移。

图3 锁相环调频的仿真电路根据图2建立的仿真电路如图3所示。

图中,设置压控振荡器V1在控制电压为0时,输出频率为0;控制电压为5V时,输出频率为50kHz。

这样,实际上就选定了压控振荡器的中心频率为25kHz,为此设定直流电压V3为2.5V。

模拟锁相环实验报告

实验十四模拟锁相环实验一、实验目的1、了解用锁相环构成的调频波解调原理。

2、学习用集成锁相环构成的锁相解调电路。

二、实验容1、掌握锁相环锁相原理。

2、掌握同步带和捕捉带的测量。

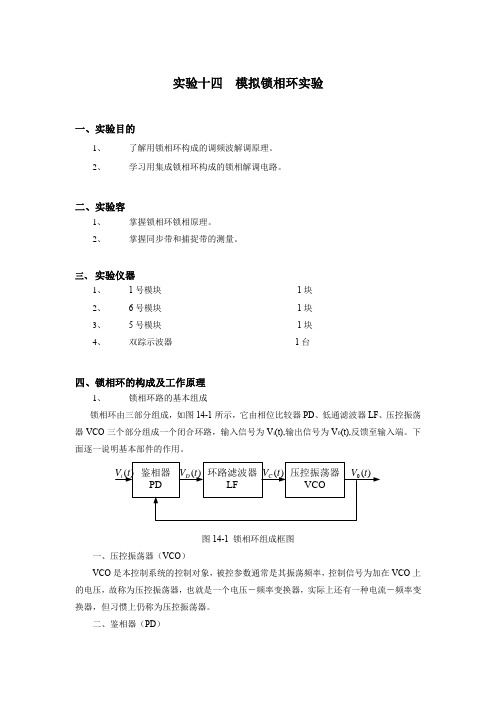

三、实验仪器1、1号模块1块2、6号模块1块3、5号模块1块4、双踪示波器1台四、锁相环的构成及工作原理1、锁相环路的基本组成锁相环由三部分组成,如图14-1所示,它由相位比较器PD、低通滤波器LF、压控振荡器VCO三个部分组成一个闭合环路,输入信号为V i(t),输出信号为V0(t),反馈至输入端。

下面逐一说明基本部件的作用。

图14-1 锁相环组成框图一、压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压-频率变换器,实际上还有一种电流-频率变换器,但习惯上仍称为压控振荡器。

二、鉴相器(PD)PD 是一个相位比较装置,用来检测输出信号V 0(t)与输入信号V i (t)之间的相位差θe (t),并把θe (t)转化为电压V d (t)输出,V d (t)称为误差电压,通常V d (t)作为一直流分量或一低频交流量。

三、环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在V d (t)中产生的无用的组合频率分量及干扰,产生一个只反映θe (t)大小的控制信号V e (t)。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使V 0(t)与V i (t)的相位差θe (t)发生变化,该相位差经过PD 转换成误差电压V d (t),此误差电压经LF 滤波后得到V c (t),由V c (t)去改变VCO 的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即)()(t t V e d θ∝因此在锁定状态,θe (t)不可能为零,换言之在锁定状态V 0(t)与V i (t)仍存在相位差。

实验三模拟锁相环与载波同步实验

实验三模拟锁相环与载波同步实验一、实验目的1. 掌握模拟锁相环的工作原理,以及环路的锁定状态、失锁状态、同步带、捕捉带等基本概念2. 掌握用平方环法从2DPSK信号中提取相干载波的原理及模拟锁相环的设计方法3. 了解相干载波相位模糊现象产生的原因二、实验内容1. 观察模拟锁相环的锁定状态、失锁状态及捕捉过程2. 观察环路的捕捉带和同步带3. 用平方环法从2DPSK信号中提取载波同步信号,观察相位模糊现象三、基本原理常用平方环或同相正交环(科斯塔斯环)从2DPSK信号中提取相干载波。

本实验用平方环,其原理方框图及电路原理图如图3-1、图3-2所示。

图3-1 载波同步方框图载波同步模块上有以下测试点及输入输出点:2DPSK-IN 2DPSK信号输入点MU 平方器输出测试点,VP-P>1V COMP 锁相环输入信号测试点Ud 锁相环压控电压测试点VCO 锁相环输出信号测试点,VP-P>0.2VCAR-OUT 相干载波信号输出点/测试点图3-1中各单元与图3-2中的主要元器件的对应关系如下:平方器 U2:模拟乘法器MC1496 鉴相器 U4: 锁相环HC4046环路滤波器 U4: 锁相环HC4046压控振荡器 U4: 锁相环HC4046÷2 U6:D触发器74HC74移相器 U8:单稳态触发器74LS123滤波器电感L1;电容C43压控振荡器 U5: 锁相环CD4046锁相环由鉴相器(PD)、环路滤波器(LF)及压控振荡器(VCO)组成,如图3-3所示。

图3-3 锁相环方框图模拟锁相环中,PD是一个模拟乘法器,LF是一个有源或无源低通滤波器。

锁相环路是一个相位负反馈系统,PD检测ui(t)与uo(t)之间的相位误差并进行运算形成误差电压ud(t),LF用来滤除乘法器输出的高频分量(包括和频及其他的高频噪声)形成控制电压uc(t),在uc(t)的作用下、uo(t)的相位向ui(t)的相位靠近。

设ui(t)=Uisin[ωit+θi(t)],uo(t)=Uocos[ωit+θo(t)],则ud(t)=Udsinθe(t),θe(t)=θi(t)-θo(t),故模拟锁相环的PD是一个正弦PD。

实验八-模拟锁相环应用实验

实验报告数值大小不同,环路的工作情况也不同。

若1w ∆较小,处于环路滤波器的通频带内,则差拍误差电压()e u t 能顺利通过环路滤波器加到VCO 上,控制VCO 的振荡频率,使其随差拍电压的变化而变化,所以VCO 输出是一个调频波,即()y w t 将在yo w 上下摆动。

由于1w ∆较小,所以()y w t 很容易摆动到i w ,环路进入锁定状态,鉴相器将输出一个与稳态相位差对应的直流电压,维持环路动态平衡。

若瞬时角频差1w ∆数值较大,则差拍电压()e u t 的频率较高,它的幅度在经过环路滤波器时可能受到一些衰减,这样VCO 的输出振荡角频率()y w t 上下摆动的范围也将减小一些,故需要多次摆动才能靠近输入角频率()i w t ,即捕捉过程需要许多个差拍周期才能完成,因此捕捉时间较长,若1w ∆太大,将无法捕捉到,环路一直处于失锁状态。

能够由失锁进入锁定所允许的最大固有角频差1m w ∆的两倍称为环路的捕捉带。

3、集成锁相环NE564介绍及应用(1)在本实验中,所使用的锁相环为NE564(国产型号为L564)是一种工作频率可高达50MHz 的超高频集成锁相环。

'其内部框图和脚管定义如图8-2。

其内部电路原理图如图8-3。

a、在图8-2(a )中,A1(LIMITER )为限幅放大器,它主要由原理图中的Q1~Q5及Q8,Q7组成。

Q1~Q5组成PNP ,NPN 互补的共集—共射组合差分放大器,由于Q2,Q3负载并联有肖特基二极管D1,D2,故其双端输出电压被限幅在20.3~0.4D V v =左右。

因此可有效消除FM 信号输入时,干扰所产生的寄生调幅。

Q7,Q8为射极输出差放,以作缓冲,其输出信号送鉴相器。

(a)NE564内部框图(b)NE564管脚分布图图8-2 锁相环内部框图和引脚图b、鉴相PD (PHASE COMPARATOR )采用普通双差分模拟相乘器,由压控振荡器反馈过来的信号从外部由③端输入。

锁相环倍频器的实训报告

一、实训目的通过本次实训,使学生掌握锁相环倍频器的基本原理、设计方法和实验技能,提高学生运用理论知识解决实际问题的能力,培养学生的动手操作能力和团队协作精神。

二、实训内容1. 锁相环倍频器的基本原理锁相环倍频器是一种能够将输入信号频率进行整数倍放大的电路。

它主要由压控振荡器(VCO)、鉴相器(PD)、低通滤波器(LPF)和分频器组成。

当输入信号与VCO的输出信号之间存在相位差时,PD将这个相位差转换为误差电压,通过LPF滤波后,控制VCO的频率,使VCO的输出信号与输入信号保持同步,从而达到倍频的目的。

2. 锁相环倍频器的设计(1)选择合适的VCO:根据输入信号的频率和所需的倍频次数,选择合适的VCO,确保VCO的频率范围满足设计要求。

(2)设计鉴相器:鉴相器的作用是检测输入信号与VCO输出信号的相位差,并将相位差转换为误差电压。

常用的鉴相器有乘法鉴相器和相位比较鉴相器。

(3)设计低通滤波器:低通滤波器的作用是滤除误差电压中的高频分量,使其平滑,以便控制VCO的频率。

常用的低通滤波器有RC滤波器和有源滤波器。

(4)设计分频器:分频器的作用是将VCO的输出信号进行分频,得到所需的倍频信号。

常用的分频器有数字分频器和模拟分频器。

3. 锁相环倍频器的实验(1)搭建实验电路:根据设计好的电路图,搭建锁相环倍频器实验电路。

(2)测试电路性能:使用示波器、频率计等仪器,测试电路的输出信号频率、相位噪声、频率稳定度等性能指标。

(3)分析实验结果:根据实验数据,分析电路性能,找出存在的问题,并提出改进措施。

三、实训过程1. 实验准备(1)查阅相关资料,了解锁相环倍频器的基本原理、设计方法和实验技巧。

(2)熟悉实验设备和仪器,了解其性能和操作方法。

(3)设计实验电路图,列出所需元器件清单。

2. 搭建实验电路(1)按照实验电路图,连接电路元器件。

(2)检查电路连接是否正确,确保电路安全可靠。

3. 测试电路性能(1)使用示波器观察VCO的输出信号波形,记录频率、相位噪声等数据。

实验1 锁相环跟踪特性的测量实验

2、观察锁相环锁定,跟踪,失锁和再同步过程 、观察锁相环锁定,跟踪, 首先使输出信号锁定在800KHz,用示波器的探 头 分 别 测 试 输 入 信 号 ( IN31 ) 和 分 频 后 的 信 号 (TT32),示波器上同时显示两处的波形,TT32的 波形为方波。 (1) 先增大输入信号频率fR观察示波器上两波形,开始 时,两波形同步移动,此时处在同步跟踪状态。fR 增加到一定值时,只有输入信号fR(正弦波)在移 动。此时,处于失锁状态。 (2) 再减小fR直至进入锁定状态(两波同步移动)。再 增大fR值直至失锁。

三、实验仪器

1、高频电子线路实验箱 (锁相环频率合成 器模块); 2、60MHz双踪模拟示波器。

四、实验原理

1、锁相环路的基本组成; 2、锁相环路的跟踪过程和捕获过程; 3、集成锁相环NE564原理与应用。

1、锁相环路的基本组成 、

图1 锁相环路的基本构成

2、锁相环路的跟踪过程和捕获过程 、

1)环路的跟踪过程 ) 在环路锁定之后,若输入信号频率发生变化, 产生了瞬时频差,从而使瞬时相位差发生变化, 则环路将及时调节误差电压去控制VCO,使VCO 输出信号频率随之变化,即产生新的控制频差, VCO输出频率及时跟踪输入信号频率,当控制频 差等于固有频差时,瞬时频差再次为零,继续维 持锁定,这就是跟踪过程,在锁定后能够继续维 持锁定所允许的最大固有角频差的两倍称为同步 带。

六、实验报告

一、实验目的 二、实验内容 二、实验仪器 四、实验原理

1、锁相环路的基本组成; 2、锁相环路的跟踪过程和捕获过程; 3、集成锁相环NE564原理与应用。

五、实验步骤 六、实验结果(同步带与捕获带) 实验结果(同步带与捕获带)

登记实验记录本 下周交号加到锁相环路的输入端开始,一 直到环路达到锁定的全过程,称为捕获过程。输 入信号频率ωi 一般与被控振荡器自由振荡频率ωo 不同,即两者之差∆ωo≠0。若没有相位跟踪系统 的作用,两信号之间相差

锁相环实验报告

锁相环实验报告1. 引言锁相环(Phase-Locked Loop,简称PLL)是一种常用的控制系统,可以实现输入信号与参考信号之间的相位同步。

在通信、控制、测量等领域有广泛的应用。

本实验旨在通过搭建锁相环电路并进行实验,深入了解锁相环的工作原理和特性。

2. 实验设备和器材本实验所用设备和器材如下: - 函数发生器 - 直流稳压电源 - 射频信号源 - 锁相环芯片 - 示波器 - 电阻、电容等器件 - 连接线等3. 实验原理锁相环是由相位比较器、低通滤波器、控制电压产生电路和VCO(Voltage Controlled Oscillator)组成。

其工作原理可分为以下几个步骤:1.输入信号与参考信号经过相位比较器进行比较,得到相位误差信号。

2.相位误差信号经过低通滤波器得到控制电压。

3.控制电压经过控制电压产生电路产生驱动VCO的控制信号。

4.VCO根据控制信号输出频率可变的信号。

5.输出信号经过除频器和低通滤波器得到稳定的参考信号。

4. 实验步骤1.连接实验电路,将函数发生器作为输入信号源,射频信号源作为参考信号源,分别接入相位比较器的输入端和参考输入端。

将相位比较器的输出接入低通滤波器,再将低通滤波器的输出接入控制电压产生电路。

控制电压产生电路的输出接入VCO的控制信号输入端,VCO的输出信号接入除频器和低通滤波器,最后将低通滤波器的输出与相位比较器的输入相连。

2.将实验电路接通电源,调节函数发生器和射频信号源,使得函数发生器输出的波形为正弦波,在示波器上观察输入信号和输出信号。

3.调节控制电压产生电路中的参数,观察输出信号的频率和相位变化。

4.调节VCO的参数,观察输出信号的频率和相位变化。

5.记录实验数据并进行分析。

5. 实验数据和结果分析根据实验步骤中的操作,记录下实验数据,并进行结果分析。

可以观察到输入信号和输出信号的频率和相位的变化情况,通过对比分析得出锁相环的工作特性。

6. 结论通过本次实验,我们深入了解了锁相环的工作原理和特性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验十四模拟锁相环实验一、实验目的1、了解用锁相环构成的调频波解调原理。

2、学习用集成锁相环构成的锁相解调电路。

二、实验容1、掌握锁相环锁相原理。

2、掌握同步带和捕捉带的测量。

三、实验仪器1、1号模块1块2、6号模块1块3、5号模块1块4、双踪示波器1台四、锁相环的构成及工作原理1、锁相环路的基本组成锁相环由三部分组成,如图14-1所示,它由相位比较器PD、低通滤波器LF、压控振荡器VCO三个部分组成一个闭合环路,输入信号为V i(t),输出信号为V0(t),反馈至输入端。

下面逐一说明基本部件的作用。

图14-1 锁相环组成框图一、压控振荡器(VCO)VCO是本控制系统的控制对象,被控参数通常是其振荡频率,控制信号为加在VCO上的电压,故称为压控振荡器,也就是一个电压-频率变换器,实际上还有一种电流-频率变换器,但习惯上仍称为压控振荡器。

二、鉴相器(PD)PD 是一个相位比较装置,用来检测输出信号V 0(t)与输入信号V i (t)之间的相位差θe (t),并把θe (t)转化为电压V d (t)输出,V d (t)称为误差电压,通常V d (t)作为一直流分量或一低频交流量。

三、环路滤波器(LF )LF 作为一低通滤波电路,其作用是滤除因PD 的非线性而在V d (t)中产生的无用的组合频率分量及干扰,产生一个只反映θe (t)大小的控制信号V e (t)。

按照反馈控制原理,如果由于某种原因使VCO 的频率发生变化使得与输入频率不相等,这必将使V 0(t)与V i (t)的相位差θe (t)发生变化,该相位差经过PD 转换成误差电压V d (t),此误差电压经LF 滤波后得到V c (t),由V c (t)去改变VCO 的振荡频率使趋近于输入信号的频率,最后达到相等。

环路达到最后的这种状态就称为锁定状态,当然由于控制信号正比于相位差,即)()(t t V e d θ∝因此在锁定状态,θe (t)不可能为零,换言之在锁定状态V 0(t)与V i (t)仍存在相位差。

2、锁相环锁相原理锁相环是一种以消除频率误差为目的的反馈控制电路,它的基本原理是利用相位误差电压去消除频率误差,所以当电路达到平衡状态后,虽然有剩余相位误差存在,但频率误差可以降低到零,从而实现无频差的频率跟踪和相位跟踪。

当调频信号没有频偏时,若压控振荡器的频率与外来载波信号频率有差异时,通过相位比较器输出一个误差电压。

这个误差电压的频率较低,经过低通滤波器滤去所含的高频成份,再去控制压控振荡器,使振荡频率趋近于外来载波信号频率,于是误差越来越小,直至压控振荡频率和外来信号一样,压控振荡器的频率被锁定在与外来信号相同的频率上,环路处于锁定状态。

当调频信号有频偏时,和原来稳定在载波中心频率上的压控振荡器相位比较的结果,相位比较器输出一个误差电压,如图14-2,以使压控振荡器向外来信号的频率靠近。

由于压控振荡器始终想要和外来信号的频率锁定,为达到锁定的条件,相位比较器和低通滤波器向压控振荡器输出的误差电压必须随外来信号的载波频率偏移的变化而变化。

也就是说这个误差控制信号就是一个随调制信号频率而变化的解调信号,即实现了鉴频。

图14-2 锁相环 (PLL)3、同步带与捕捉带同步带是指从PLL 锁定开始,改变输入信号的频率f i (向高或向低两个方向变化),直到PLL 失锁(由锁定到失锁),这段频率围称为同步带。

捕捉带是指锁相环处于一定的固有振荡频率f V ,并当输入信号频率f i 偏离f V 上限值max i f 或下限值min i f 时,环路还能进入锁定,则称v i i f f f ∆=-min max 为捕捉带。

测量的方法是从J4输入一个频率接近于VCO 自由振荡频率的高频调频信号,先增大载波频率直至环路刚刚失锁,记此时的输入频率为f H1 ,再减小f i ,直到环路刚刚锁定为止,记此时的输入频率为f H2,继续减小f i ,直到环路再一次刚刚失锁为止,记此时的频率为f L1 ,再一次增大f i ,直到环路再一次刚刚锁定为止,记此时频率为f L2由以上测试可计算得: 同步带为:f H1-f L1 捕捉带为:f H2-f L2五、集成锁相环NE564的介绍下图为NE564部组成框图。

其中限幅器由差分电路组成,可抑制FM 信号的寄生调幅;鉴相器(PD)的部含有限幅放大器,以提高对AM 信号的抗干扰能力:4、5脚外接电容组成环路滤波器,用来滤除比较器输出的直流误差电压中的纹波;2脚用来改变环路的增益;3脚为VCO 的反馈输入端;VCO 是改进型的射极耦合多谐振荡器,有两个电压输出端,9脚输出TTL 电平,11脚输出ECL 电平。

VCO 部接有固定电阻,只需外接一个定时电容就可产生振荡;施密特触发器的回差电压可通过15脚外接直流电压进行调整,以消除16脚输出信号的相位抖动。

图14-3 NE564部组成框图在本实验中,所使用的锁相环为高频模拟锁相环NE564,其最高工作频率可达到50MHz,采用+5V单电源供电,特别适用于高速数字通信中FM调频信号及FSK移频键控信号的调制、解调,无需外接复杂的滤波器。

NE564采用双极性工艺,其部组成框图如图14-3所示,其部电路原理图如图14-4所示。

图14-4 NE564部电路原理图(1)限幅放大器A 1为限幅放大器,它主要由原理图中的Q 1~Q 5及Q 7、Q 8组成PNP 、NPN 互补的共集-共射组合差分放大器,由于Q 2、Q 3负载并联有肖特基二极管D 1、D 2,故其双端输出电压被限幅在2V D =0.3~0.4V 左右。

因此可有效抑制FM 调频信号输入时干扰所产生的寄生调幅。

Q 7、Q 8为射极输出差放,以作缓冲,其输出信号送鉴相器。

(2)相位比较器(鉴相器)PD 部含有限幅放大器,以提高对AM 调幅信号的抗干扰能力;外接电容C 3、C 8与部两个对应电阻(阻值R=1.3k)分别组成一阶RC 低通滤波器用来滤除比较器输出的直流误差电压中的纹波,其截止角频率为31RC c =ω。

滤波器的性能对环路入锁时间的快慢有一定影响,可根据要求改变C 3、C 8的值。

在本实验电路中,改变W1可改变引脚2的输入电流,从而实现环路增益控制。

(3)压控振荡器VCO压控振荡器是一改进型的射极定时多谐振荡器。

主电路由Q 21、Q 22与Q 23、Q 24组成。

其中Q 22,Q 23两射极通过12、13脚外接定时电容C ,Q 21、Q 24两射极分别经过电阻R 22、R 23接电源Q 27、Q 25。

Q 26也作为电流源。

Q 17、Q 18为控制信号输入缓冲极。

接通电源,Q 21,Q 22与Q 23、Q 24双双轮流导通与截止,电容周期性充电与放电,于是Q 22、Q 23集电极输出极性相反的方形脉冲。

根据特定设计,固有振荡频率f 与定时电容C 的关系可表示为振荡频率f 与C 的关系曲线如图14-5所示。

VCO 有两个电压输出端,其中,VCO 01输出TTL 电平;VCO 02输出ECL 电平。

输出放大器A 2与直流恢复电路A 3是专为解调FM 信号与FSK 信号而设计的。

输出放大器A 2由Q 37、Q 38、Q 39组成,显然这是一恒流源差分放大电路,来自鉴相器的误差电压由4、5脚输入,经缓冲后,双端送入A 2放大。

直流恢复电路由Q 42、Q 43、Q 44等组成,电流源Q 40作Q 43的有源负载。

若环路的输入为FSK 信号,即频率在f 1与f 2之间周期性跳变的信号,则鉴相器的输出电压被A 2放大后分两路,一路直接送施密特触发器的输入,另一路送直流恢复电路A 3的Q 42基极,由于Q 43集电极通过14脚外接一滤波电容,图 14-5 f 与c 的关系放直流恢复电路的输出电压就是一个平均值——直流。

这个直流电压V REF再送施密特触发器另一输入端就作为基极电压。

若环路的输入为FM信号,A3用作线性解调FM信号时的后置鉴相滤波器,那么在锁定状态,14脚的电压就是FM解调信号。

施密特触发器是专为解调FSK信号而设计的,其作用就是将模拟信号转换成TTL数字信号。

直流恢复输出的直流基准电压V REF(经R26到Q49基极)与被A2放大了的误差电压V dm分别送入Q49和Q50的基极,V dm与V REF进行比较,当V dm>V REF时,则Q50导通,Q49截止,从而迫使Q54截止,Q55导通,于是16脚输出低电平。

当V dm<V REF时,Q49导通,Q50截止,从而迫使Q54导通Q55截止,16脚输出高电平。

通过15脚改变Q52的电流大小,可改变触发器上下翻转电平,上限电平与下限电平之差也称为滞后电压V H。

调节V H可消除因载波泄漏而造成的误触发而出现的FSK解调输出,特别是在数据传输速率比较高的场合,并且此时14脚滤波电容不能太大。

ST的回差电压可通过10脚外接直流电压进行调整,以消除输出信号TTL0的相位抖动。

六、实验步骤1、锁相环自由振荡频率的测量将5号板开关S1依次设为“1000”,“0100”,“0010”,“0001”(即选择不同的定时电容),从TP6处观察自由振荡波形,并填写表14-1。

表14-12、同步带和捕捉带的测量1)将S2设为0010(即VCO的自由振荡频率为4.5MHz),并完成下表所示的连线。

2)用双踪示波器对比观测5号模块信号输入端TP8和VCO输出信号TP6的波形,观察频率的锁定情况,完成表14-2。

先按下1号模块上“频率调节”旋钮,选择“×10”档,然后慢慢增大载波频率直至环路刚刚失锁,记此时的输入频率为f H1 ,再减小fi ,直到环路刚刚锁定为止,记此时的输入频率为f H2,继续减小fi ,直到环路再一次刚刚失锁为止,记此时的频率为f L1 ,再一次增大fi,直到环路再一次刚刚锁定为止,记此时频率为f L2由以上测试可计算得:同步带为:f H1- fL1捕捉带为:fH2- fL2注:这里我们只是选取了4.5MHz这个频段做实验,其他三个频段的实验操作步骤基本一样,只需要调整5号模块中S1的拨码方式及输入参考信号的频率即可。

3、改变W1的阻值(顺时针旋转,阻值变大;逆时针旋转,阻值变小),重做步骤2,在J1处观察VCO输出波形的幅度、同步带、和捕捉带的变化。

七、实验报告要求1.整理实验数据,按要求填写实验报告2.完成同步带和捕捉带的测量。