嵌入式开发JTAG接口的应用介绍

jtag接口是什么

jtag 接口是什么

JTAG(JointTestAcTIonGroup,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG 技术是一种

嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP (TestAccessPort,测试访问口),通过专用的JTAG 测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持JTAG 协议,如ARM、DSP、FPGA 器件等。

标准的JTAG 接口是4 线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

如今JTAG 接口的连接有两种标准,即14 针接口和20 针接口,其定义分别如下所示。

14 针JTAG 接口

1、13VCC 接电源。

JTAG

JTAGJTAG接口功能引脚图JTAG是英文“Joint Test Action Group(联合测试行为组织)”的词头字母的简写,该组织成立于1985 年,是由几家主要的电子制造商发起制订的PCB 和IC 测试标准。

JTAG 建议于1990 年被IEEE 批准为IEEE1149.1-1990 测试访问端口和边界扫描结构标准。

该标准规定了进行边界扫描所需要的硬件和软件。

自从1990 年批准后,IEEE 分别于1993 年和1995 年对该标准作了补充,形成了现在使用的IEEE1149.1a-1993 和IEEE1149.1b-19 94。

JTAG 主要应用于:电路的边界扫描测试和可编程芯片的在线系统编程。

国际标准测试协议JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG 接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG 接口输出;TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;TRST为测试复位,输入引脚,低电平有效。

GNDTI还定义了一种叫SBW-JTAG的接口,用来在引脚较少的芯片上通过最少的利用引脚实现JTAG接口,它只有两条线,SBWTCK,SBWTDIO。

实际使用时一般通过四条线连接,VCC,SBWTCK,SBTDIO,GND,这样就可以很方便的实现连接,又不会占用大量引脚。

JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Tes t Access Port测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。

J TAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

jtagapb用法

jtagapb用法摘要:一、JTAGAPB简介1.JTAG简介2.JTAGAPB的作用二、JTAGAPB的连接方式1.硬件连接2.软件连接三、JTAGAPB的编程方法1.使用JTAGAPB工具进行编程2.使用编程器进行编程四、JTAGAPB的应用领域1.嵌入式系统开发2.物联网设备开发五、JTAGAPB的发展趋势1.在新技术中的运用2.未来发展方向正文:JTAGAPB是Joint Test Action Group-Advanced Package Bus的缩写,中文意为联合测试行动组-先进封装总线,它是一种用于芯片测试和编程的标准接口。

通过JTAGAPB,可以实现对芯片内部寄存器的访问和控制,从而对芯片进行测试和编程。

在嵌入式系统开发和物联网设备开发等领域中,JTAGAPB被广泛应用。

JTAGAPB的连接方式主要有硬件连接和软件连接两种。

硬件连接是通过JTAG测试接口将JTAGAPB与目标芯片连接起来,从而实现对芯片的访问。

软件连接则是通过在开发环境中配置JTAGAPB的相关参数,实现与目标芯片的通信。

在编程方面,可以使用JTAGAPB工具或编程器进行编程。

JTAGAPB工具通常提供了一个图形化的界面,方便用户进行编程操作。

编程器则需要用户通过命令行的方式进行编程。

无论使用哪种方法,都可以实现对目标芯片的编程。

随着科技的不断发展,JTAGAPB在新技术中的运用也越来越多。

例如,在物联网设备开发中,JTAGAPB可以用于对传感器节点进行编程和测试,从而提高开发效率。

此外,随着集成电路封装技术的进步,JTAGAPB也在不断发展和完善,以满足更高的技术要求。

总之,JTAGAPB作为一项成熟的技术,在嵌入式系统开发和物联网设备开发等领域具有广泛的应用前景。

可以实现的JTAG调试器的嵌入式系统

可以实现的JTAG调试器的嵌入式系统ARM系列处理器正是通过JTAG 接口使用内部集成的ICE 功能, 并采用这种方式实现在线调试。

此外CPLD、FPGA 等器件大多都可以使用JTAG 接口实现在线编程或下载。

因此,JTAG 接口已经成为复杂芯片系统的必备接口, 在芯片测试、调试及实现其他特殊功能方面发挥着重要作用。

基本原理JTAG 标准即IEEE 1149.1 标准。

联合测试行动组JTAG(Joint Test Action Group ) 起草了边界扫描测试BST(Boundary Scan Testing)规范, 该标准为数字集成电路规定了一个测试访问口(TAP) 和边界扫描结构,解决了由于数字电路高度集成化带来的一些测试难题。

它还提供了一种访问和控制芯片内部仿真(ICE) 模块的方法, ICE 模块一般包括内部扫描和自测试的功能, 可以很好地支持集成电路的开发。

JTAG 标准工作原理边界扫描技术的基本思想是在靠近芯片的输入输出管脚增加一个移位寄存器单元。

通过这些边界扫描寄存器单元, 可以实现对芯片输入输出信号的观察和控制。

另外, 靠近芯片输入输出管脚的边界扫描(移位) 寄存器单元可以相互连接起来, 在芯片的周围形成一个边界扫描链(Boundary- Scan Chain) 。

一般的芯片都会提供几条独立的边界扫描链, 用来实现完整的测试功能。

在JTAG标准中, 寄存器被分为两大类: 数据寄存器(DR- Data Register)和指令寄存器(IR- Instruction Register),边界扫描链寄存器即为一种很重要的数据寄存器, 边界扫描链可用来观察和控制芯片的输入输出。

指令寄存器用来实现对数据寄存器的控制。

TAP 是一个通用的端口, 通过TAP 可以访问芯片提供的所有数据寄存器和指令寄存器, 对整个TAP的控制是通过TAP控制器完成的。

TAP包括5个信号接口: (1)TCK(Test Clock), 为TAP操作提供了一个独立的基本的时钟信号。

嵌入式系统的调试与测试技术研究

嵌入式系统的调试与测试技术研究嵌入式系统是一种高度集成的各种硬件和软件系统,其应用范围广泛,包括汽车、医疗设备、航空航天、工业自动化等领域。

嵌入式系统的调试和测试是确保系统可靠性和稳定性的重要步骤。

本文将从嵌入式系统的调试和测试技术入手,深入探讨如何提高嵌入式系统的可靠性和稳定性。

一、嵌入式系统的调试和测试方法嵌入式系统的调试和测试在整个系统开发过程中起着至关重要的作用。

常见的嵌入式系统调试和测试方法包括:仿真测试、单元测试、集成测试、验收测试等。

其中,仿真测试是利用仿真器或者模拟器对嵌入式系统进行各种测试,可以帮助开发人员在没有实际硬件的情况下快速进行开发和调试;单元测试是对嵌入式系统中的各个模块进行测试,确保每个模块的功能正确性;集成测试是对整个系统进行测试,确保各个模块之间的协同工作正常;验收测试是为了验证开发的系统是否符合客户的需求和要求。

二、硬件调试测试技术硬件调试测试技术是指对嵌入式系统硬件进行测试和调试,主要包括CPU分析器、电路分析仪、万用表、示波器等设备。

在进行硬件调试时,一般首先要进行硬件电路图的设计和分析,确保电路图的正确性和稳定性。

其次,要对板子进行功率测试、时钟测试、引脚测试等测试,保证板子的正常工作。

最后,要进行连通性测试,确保各个模块之间的连接正常。

三、软件调试测试技术软件调试测试技术是指对嵌入式系统软件进行测试和调试,主要包括GDB调试、Trace调试、代码覆盖率测试、文本比对测试等技术。

在进行软件调试时,一般首先要对软件进行静态分析和代码审查,发现潜在的错误和问题。

其次,要利用GDB调试器进行调试,对函数的输入、输出进行跟踪和观察。

最后,要进行文本比对测试,确保程序输出结果的正确性和稳定性。

四、嵌入式系统测试工具嵌入式系统测试工具是指针对嵌入式系统进行测试和调试的软件工具,包括MBIST、JTAG debugger、FileScope、Coverity等工具。

MBIST是一种存储器内置自检工具,可以帮助开发人员快速发现存储器中的问题。

JTAG边界扫描技术及其在嵌入式开发中的应用

收稿日期:2004-09-20 作者简介:曾毅(1978-),男,四川自贡人,硕士研究生,主要研究方向:嵌入式应用、网络安全; 张小松(1968-),男,四川双流人,讲师,硕士,主要研究方向:嵌入式应用、网络安全; 陈景春,男,四川成都人,教授,主要研究方向:嵌入式应用、程序理论; 李毅超(1969-),男,四川广汉人,副教授,主要研究方向:嵌入式应用、网络安全.文章编号:1001-9081(2004)12Z -0307-02JT AG 边界扫描技术及其在嵌入式开发中的应用曾 毅,张小松,陈景春,李毅超(电子科技大学计算机科学与工程学院,四川成都610054)(R ichardlyc@uestc .edu .cn )摘 要:介绍了JT AG 边界扫描的概念及基本协议标准,并以工程应用为重点,结合实际开发的一个嵌入式平台,以F LASH 的在系统编程和硬件测试程序为例,详细说明了JT AG 技术在嵌入式开发中的应用。

关键词:JT AG;嵌入式;F LASH;硬件测试中图分类号:TP311.52 文献标识码:A0 引言在现代电子应用系统中,PC B 板越来越复杂,大量使用各种表贴元件和BG A (Ball Grid A rray )封装元件,元器件的管脚数和管脚密度不断提高。

使用万用表、示波器等测试芯片的传统方法已不能满足要求。

早在20世纪80年代,联合测试行动组(Joint Test Acti on Gr oup,JT AG )起草了边界扫描测试(Boundary 2Scan Testing,BST )规范,后来在1990年被批准为I EEE 标准1149.121990规定,简称JT AG 标准。

JT AG 技术在嵌入式系统开发中有着广泛的应用,本文将以工程应用为重点,以F LASH 编程和硬件测试为例详细说明。

1 JT AG 标准概述1.1 JT AG 接口JT AG 标准规定对于数字集成电路的每个引脚都对应一个或多个移动寄存器单元,称为边界扫描单元BSC 。

什么是JTAG及其使用方法?

什么是JTAG及其使用方法?

JTAG不仅仅用于调试和下载程序

你可能熟悉JTAG是因为你使用过带有JTAG接口的工具。

处理器经常使用JTAG来实现调试/仿真功能,而且所有的FPGA和CPLD 都利用JTAG来实现下载程序功能。

JTAG不仅仅是一种用于处理器调试/仿真的技术

JTAG不仅仅是一种为FPGA/CPLD下载程序的技术

通常与JTAG有关的调试和编程工具仅仅利用了潜在技术的一个方面即四线JTAG通讯协议。

这四种信号,作为测试访问端口(TAP)而广为人知。

它是IEEE 1149.1. 标准的一部分。

开发该标准的目的在于提供一种印刷电路板组件(PCBA)测试的技术。

这种技术不需要针床测试的物理访问,也不像功能测试那样需要定制开发量。

设计TAP来与新的寄存器进行交互,这些新的寄存器被添加到器件中,以便实现这种测试方法。

但是很快半导体制造商就意识到了使用TAP来访问寄存器,可以提供其它功能如调试和编程。

专门用于JTAG测试而加入到器件中的寄存器主要是边界扫描寄存器(BSR)。

正如它的名字所示,这个寄存器的单独的位或单元位于器件的边界,处于功能核心与引脚或焊球之间,通过引脚连接到板上JTAG测试经常被称作边界扫描。

基于XC164嵌入式系统的JTAG应用

第 6 总第 1 0期 期 6

20 0 8年 3月

内 蒙 古 科 技 与 经 济

Ile o g l ce c c n lg & Ec n my r lrM n o i S in eTe h o o y r a oo

No 6,t e1 0 h i u . h 6 t s e s Ma.0 8 r2 0

基 于 XC l4嵌入 式 系统 的 J AG 应 用 6 T

黄

摘

王 月

( 吉林大学计算 机教学与研究 中心 , 吉林 长春 要 : 章 以 XC1 4芯 片 为 基 础 就 如 何 通 过 J 文 6 TAG 接 口进 行 芯 片调 试 作 了探 讨 。

文 章 编 号 :0 7 6 2 ( O 8 0 — 0 —O2 1 0 9 1 2 O )6 3

进 行 测 试 . TAG 测试 允 许 多 个 器 件 通 过 . 。J J TAG 接

口串联在 一起 , 成一 个 J 形 TAG 链 , 实 现 对 各 个 器 能

1 1 一 种 常 用 方 法 是 使 用 电路 内 铂 器 ( CE j . 真 I ) 用 于置 入微 处 理 器与 总线之 间的屯路 中 , 许 使 用者 允 监 视 和 控 耕 微 处理 器 所 有 信 号 的 进 出 I E 通 常 是 使 用 特 殊 型 号 称 为 “ o d—o t C 的 bn u”

在 真 实环 境 实时运 行 软件 的优 点 , 其 价格 昂贵 但 、 体

积 较 大 且 无 法 提 供 1 0%精 确 度 , 其 是 涉 及 A1C 0 尤 )

、

比较 器 、 荡 器 及 电 压 参 考 电 路 等 模 拟 外 设

处 理器 资源 , 步 执行 , 理 器复 位 及 其状 态 ( 行 单 处 运 或 者 停 止 ) 典 型 的 , 内外 设 在 OC 期 间 休 眠 ( 片 D 相

JTAG接口介绍

JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试。

目前大多数比较复杂的器件都支持JTAG协议,如ARM、DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

JTAG接口还常用于实现ISP(In-System Programmable在系统编程)功能,如对FLASH器件进行编程等。

通过JTAG接口,可对芯片内部的所有部件进行访问,因而是开发调试嵌入式系统的一种简洁高效的手段。

目前JTAG接口的连接有两种标准,即14针接口和20针接口,其定义分别如下所示。

14针JTAG接口定义:14针JTAG接口定义引脚名称描述1、13VCC接电源2、4、6、8、10、14GND接地3nTRST测试系统复位信号5TDI测试数据串行输入7TMS测试模式选择9TCK测试时钟11TDO测试数据串行输出12NC未连接20针JTAG接口定义引脚名称描述1VTref目标板参考电压,接电源2VCC接电源3nTRST测试系统复位信号4、6、8、10、12、14、16、18、20GND接地5TDI测试数据串行输入7TMS测试模式选择9TCK测试时钟11RTCK测试时钟返回信号13TDO测试数据串行输出15nRESET目标系统复位信号17、19NC未连接下面以S3C4510B开发板为例说明JTAG接口:在保证电源电路、晶振电路和复位电路正常工作的前提下,可通过JTAG接口调试S3C4510B,在系统上电前,首先应检测JTAG接口的TMS、TCK、TDI、TDO信号是否已与S3C4510B 的对应引脚相连,其次应检测S3C4510B的nEWAIT引脚(Pin71)是否已上拉,ExtMREQ 引脚(Pin108)是否已下拉,对这两只引脚的处理应注意,作者遇到多起S3C4510B不能正常工作或无法与JTAG接口通信,均与没有正确处理这两只引脚有关。

JTAG测试介绍

JTAG电路

JTAG测试的两大优点:

1、方便芯片的故障定位,迅速准确地测试两 个芯片管脚的连接是否可靠,提高测试检验 效率。 2、具有J TAG接口的芯片,内置一些预先定 义好的功能模式,通过边界扫描通道来使芯 片处于某个特定的功能模式,以提高系统控 制的灵活性和方便系统设计。

边界扫描

边界扫描技术的基本思想是在靠近芯片的 输入输出管脚上增加一个移位寄存器单元。 因为这些移位寄存器单元都分布在芯片的 边界上(周围),所以被称为边界扫描寄 存器(Boundary-Scan Register Cell)。

在正常工作状态,输入和输出数据可以自 由通过每个BSC ,正常工作数据从NDI 进,从 NDO 出。在测试状态,可以选择数据流动的 通道:对于输入的IC管脚,可以选择从NDI 或 从TDI 输入数据;对于输出的IC 管脚,可以选 择从BSC 输出数据至NDO ,也可以选择从 BSC输出数据至TDO。

另外,芯片输入输出管脚上的边界扫描寄 存器单元可以相互连接起来,在芯片的周 围形成一个边界扫描链(Boundary-Scan Chain)。一般的芯片都会提供几条独立的 边界扫描链,用来实现完整的测试功能。 边界扫描链可以串行的输入和输出,通过 相应的时钟信号和控制信号,就可以方便 的观察和控制处在调试状态下的芯片。

图2 所示是边界扫描测试应用的示意图。为了测试两个J TAG 设备的连接,首先将J TAG 设备1某个输出测试脚的BSC 置为高或 低电平,输出至NDO ,然后,让J TAG设备2 的输入测试脚来捕获 (capture)从管脚输入的NDI 值,再通过测试数据通道将捕获到的数 据输出至TDO ,对比测试结果,即可快速准确的判断这两脚是否连接 可靠

jtag工作原理详解

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它提供了一种简单而有效的方式来访问和控制芯片内部的电路,以便进行故障检测、调试和编程等操作。

本文将详细解释JTAG的工作原理,并介绍其在集成电路测试和调试中的应用。

1. JTAG工作原理概述JTAG接口是由IEEE 1149.1标准定义的,它包含了四个主要的信号线:TCK、TMS、TDI和TDO。

其中,TCK是时钟信号,TMS是状态控制信号,TDI是数据输入信号,TDO是数据输出信号。

通过这四个信号线,JTAG接口可以实现对芯片内部电路的访问和控制。

2. JTAG工作模式JTAG接口定义了四种工作模式:测试模式(Test-Logic-Reset)、编程模式(Programming)、用户模式(User)和配置模式(Configuration)。

在测试模式下,可以通过JTAG接口对芯片内部的逻辑电路进行测试和故障检测。

在编程模式下,可以通过JTAG接口对芯片进行编程和配置。

在用户模式下,芯片将正常运行。

在配置模式下,可以对芯片的配置进行修改。

3. JTAG链JTAG链是由多个JTAG设备连接而成的链路。

每个JTAG设备都有一个唯一的ID码,用于在链路中进行识别和选择。

在JTAG链中,每个设备都有一个TDO输出和一个TDI输入,通过这种方式,可以将多个设备连接在一起,形成一个长链。

4. JTAG测试JTAG测试是通过JTAG接口对芯片内部的逻辑电路进行测试和故障检测的过程。

测试模式下,可以通过TMS信号控制JTAG状态机的状态转移,通过TDI和TDO信号进行数据的输入和输出。

通过在测试模式下对芯片的逻辑电路进行测试,可以检测出逻辑错误、电路故障和短路等问题。

5. JTAG调试JTAG调试是通过JTAG接口对芯片进行调试和故障排除的过程。

调试模式下,可以通过TMS信号控制JTAG状态机的状态转移,通过TDI和TDO信号进行数据的输入和输出。

通过JTAG芯片级调试加速嵌入式Linux设备的开发

向 虚拟寻址、映射内核符号信息、并且排除用户和内核空

间内复杂的缺陷故障。通过内核 调试器(

)或

调试器( )这样基于代理的调试解决方案,很难解决以上

这些问题。

调试 时需要面对的挑战

硬件初始化 调试引导加载程序 访问指令和数据高速缓存 访问 内核中的初始化代码 对应用程序和 内核间的交互作用进行调试

内核模块的调试也将需要初始化代码的透明性,同时还要处理 中动态分配的内存。

要求稳定的 内核和定制的硬件接口(例如设备驱动程 序)都就绪后,代理才能工作。基于代理的调试不具有对硬件的 可见性,而且也无法提供理解硬件和 内核间交换作用所需 的完整诊断功能。代理要求对 内核的探测,这可能会对嵌 入式设备造成副作用。

内核或调试应用程序时,可能会造成后续程序问题。手动 设置寄存器将是一个非常繁复的过程。

2 通过

芯片级调试加速嵌入式

设备的开发

引导加载程序开发中的另一个常见的挑战是如何对引导加载程 序将 载入到 中,然后启动操作系统时出现的问题进行 调试。当引导加载程序将 内核载入到物理内存时,内核会 创建自己的虚拟内存映射,这样往往就很难确定哪些是内核正在 使用的地址。因此,当内核执行内存不足时,要确定如何重新定 位 操作系统的符号表是相当复杂的。但是,基于代理的调 试解决方案不支持引导加载程序调试,因为在这一过程中操作系 统还没有起作用。因此,开发人员需要依赖 工具来对这一 关键流程进行调试。

用程序开发、调试和分析都在一个基于

的集成开发环境

( )中进行,被称为风河

。当传统的基于代理的

解决方案在技术或经济上不可行的时候,这种能力可以允许开发

人员使用 连接。

以对硬件、引导加载程序、 内核和用户空间进行调试,发 现系统崩溃事件以及在内核、用户空间和目标设备之间发生的其 他问题。此外,使用风河 操作系统的开发人员还可以在代 理和 调试间进行无缝地转换。当基于代理的调试不可用或 者过于昂贵时,这些芯片级调试的创新为项目提供了强大的备选 方案。

jtagulator识别引脚原理_理论说明

jtagulator识别引脚原理理论说明1. 引言1.1 概述本篇长文旨在对JTAGulator识别引脚原理进行详细的理论说明。

随着现代电子设备日益复杂和智能化,许多通信设备和嵌入式系统采用JTAG(Joint Test Action Group)技术来进行测试、调试和编程。

由于安全性的考虑,很多设备会将JTAG接口隐藏或者不公开。

此时,JTAGulator作为一种非侵入式的引脚识别工具应运而生。

它通过扫描目标设备上的引脚,并利用两种方法来识别是否存在隐藏的JTAG接口。

本文将深入探讨JTAG技术概述、JTAGulator工具简介以及其引脚识别原理。

1.2 文章结构文章主要分为五个部分。

首先是引言部分,概述了文章的目的和结构。

其次是“2. JTAGulator识别引脚原理的理论说明”,详细介绍了JTAG技术的背景知识、JTAGulator工具的基本情况以及其引脚识别原理。

第三部分为正文内容,具体展开讲解待定名称的要点,包括待定名称下各个小节内容。

第四部分同样展开讲解待定名称的要点,包括待定名称下各个小节内容。

最后一部分是结论部分,总结文章的主要内容并探讨其研究意义和进一步展望。

1.3 目的本文的目的在于深入理解JTAGulator识别引脚原理,并通过对JTAG技术背景、JTAGulator工具及其引脚识别原理的详细阐述,帮助读者更好地了解该工具在现代电子设备测试、调试和编程中的应用。

同时,通过分析和总结相关知识,揭示该原理背后的核心思想以及未来可能的发展方向。

2. JTAGulator识别引脚原理的理论说明:2.1 JTAG技术概述:JTAG(全称为Joint Test Action Group)是一种用于测试集成电路(IC)的接口标准。

它允许在IC制造过程中和芯片集成到系统中后对其进行测试、调试和编程。

JTAG技术通过访问芯片内部的测试逻辑,使得开发人员可以非常方便地获取芯片的内部状态和应用程序运行数据。

名词解释jtag -回复

名词解释jtag -回复

JTAG(Joint Test Action Group,联合测试行动小组)是一种业界标准的硬件调试和测试接口。

它最初是为了在集成电路板上进行边界扫描测试而开发的,但现在广泛用于嵌入式系统的调试、编程和硬件诊断。

JTAG接口通常包括一个或多個引脚,如TMS(测试模式选择)、TCK(测试时钟)、TDI(测试数据输入)、TDO(测试数据输出)和TRST(测试复位)等。

通过这些引脚,开发者可以访问处理器内部的寄存器和内存,进行低级别调试和故障排查。

利用JTAG技术,开发者可以实现以下功能:

1. 下载和调试固件代码。

2. 监视和修改处理器内部寄存器的值。

3. 读取和修改内存中的数据。

4. 进行硬件级别的故障检测和诊断。

JTAG已经成为许多嵌入式系统设计的标准组成部分,为开发者提供了强大的调试和测试工具。

嵌入式系统设计大作业

嵌入式系统设计大作业-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN嵌入式系统设计大作业学号:姓名:罗翔1、叙述JTAG接口在嵌入式开发中的作用。

答:(1)用于烧写FLASH烧写FLASH的软件有很多种包括 fluted flashpgm等等,但是所有这些软件都是通过jtag接口来烧写flash的,由于pc机上是没有jtag接口的,所以利用并口来传递信息给目标板的jtag接口。

所以就需要并口转jtag接口的电路。

(2)用于调试程序同时应该注意到jtag接口还可以用来调试程序。

而调试程序(如ARM开发组件中的AXD)为了通过jtag接口去调试目标板上的程序,同样是使用pc的并口转jtag接口来实现与目标板的通信。

这样,并口转jtag接口的电路就有了两种作用。

(3)仿真器根据(1)和(2)的总结,并口转jtag接口的电路是两种应用的关键,而这种电路在嵌入式开发中就叫仿真器。

并口转jtag接口的电路有很多种,有简单有复杂的,常见的仿真器有Wigger,EasyJTAG,Multi-ICE等。

这些所谓的仿真器的内部电路都是并口转jtag接口,区别只是电路不同或使用的技术不同而已。

2、叙述嵌入式平台的搭建过程,以linux为例。

答:1) 一:建立宿主机开发环境建立交叉编译的环境即在宿主机上安装与开发板相应的编译器及库函数,以便能够在宿主机上应用开发工具编译在目标板上运行的Linux引导程序,内核,文件系统和应用程序交叉编译:在特殊的环境下,把嵌入式程序代码编译成不同的CPU所对应的机器代码。

开发时使用宿主机上的交叉编译,汇编及链接工具形成可执行的二进制代码(该代码只能在开发板上执行),然后下载到开发板上运行2) 下载和安装arm-Linux-gcc编译工具链下载最新的arm-Linux-gcc并解压至当前目录下在系统配置文件profile中设置环境变量方法:直接在profile文件中加入搜索路径立即使新的环境变量生效:运行source命令,检查是否将路径加入到path,测试是否安装成功,编译程序,测试交叉工具链3) 配置超级终端minicom minicom是宿主机与目标板进行通信的终端:在宿主机Linux终端中输入:minicom-s或输入minicom然后按ctrl+A+O对超级终端minicom进行配置,再选择串口并配置串口,最后保存即可4) 建立数据共享服务:NFS服务是Linux系统中经常使用的数据文件共享服务5) 编译嵌入式系统内核:内核配置,建立依存关系,建立内核6) 制作文件系统3、给出现今有哪些用于嵌入式开发的芯片名称,他们分别是哪些公司的产品体系结构是什么S3C2410X基于ARM的Sumsang;XscalePXA255/PXA270基于ARM的Intel;摩托罗拉MC基于68k;Power 601基于Power PC;MIPS32Kc基于MIPS4、现今较流行的嵌入式操作系统有哪些答:(1) VxWorks(2)wince(3)linux(4)android(5)μC/OS-Ⅱ5、PXA270嵌入式开发板的接口有哪些答:全双工异步串行口和硬件流控制串行口,10M标准以太网接口10M/100M标准以太网接口,USB接口,红外通讯口,音频接口,存储卡口,视频和触摸屏接口摄像头接口,RTC时钟接口,调试接口,下载接口,电源接口。

JTAG详解

JTAG详解来自嵌入式系统Linux内核开发实战指南 /showart.php?id=3258第10章自制简易JTAG下载烧写工具对于普通嵌入式系统爱好者来说,不太可能花太多的钱去买比较高档的调试仿真工具来调试我们自己的目标板,最经济的做法就是自己制作一个简单JTAG 线缆用来烧写flash,先将bootloader固化到flash中,因为bootloader编译出来都很小,一般几十KB,最多几百KB,用简易 JTAG烧写不需要多少时间,如果顺利,bootloader能够正常工作,那么就可以在bootloader菜单中通过串口或者TFTP下载其他程序到目标板的DRAM中进行运行调试或者烧写最后定型的软件,因为通过串口或者TFTP下载的速度比简易JTAG线缆下载烧写速度快。

当然也可以从网上搜索购买一个简易JTAG线缆(很便宜,最多不超过50RMB),不管是什么版本都行,然后用我们下面介绍的简易JTAG烧写软件来烧写目标板的flash,使用烧写软件之前只需先根据所购买JTAG线缆的具体连线图中并口与JTAG口的对应关系适当修改源代码中的管脚变量定义,然后重新编译链接就可以了。

这一章我们就介绍简易JTAG线缆硬件原理,烧写软件流程,并说明使用简易JTAG线缆烧写flash的方法。

10.1 JTAG简介JTAG接口的基本工作原理是:在芯片内部定义一个TAP(Test Access Port,测试访问端口),开发人员使用连接到芯片的JTAG外部接口上的JTAG调试器,通过访问芯片内部的TAP端口来扫描芯片内部各个扫描单元以写入或读取扫描寄存器的状态,从而对芯片进行测试和调试。

一个扫描单元对应一个外部管脚,每个外部管脚有一个扫描寄存器BSR单元,所有这些管脚的扫描寄存器连在一起就形成了扫描链。

简单地说,PC通过JTAG调试器对目标板的调试就是通过TAP端口完成对扫描寄存器BSR和指令寄存器IR的读写访问。

要了解关于JTAG 更全面的知识,请参阅 IEEE1149.1标准。

嵌入式系统中的JTAG接口编程技术

3 JTAG 接口的使用

JTAG 接口有不同的使用方式,不仅可以进行芯片测试, 还可以进行电路板程序的编程。在记性程序编程时,主要有 2 种常见的方法,一种是将 PC 机与 JTAG 接口连接,实现模 拟 JTAG 时序,还有一种是用 PC 机内插卡控制编程器访问。

2.1 JTAG 结构

1.2 使用板上编程器编程

在使用板上进行编程器编程主要是在芯片焊接完成之后 再开展的工作,首先要用电缆将计算机和电路板相连,然后 工作人员要在计算机中进行使用板上的芯片代码编辑。在编 辑过程中,使用板外的编辑器会提供编辑所需要的信号、电 源、数据等,值得注意的是,要将外部信号与 CPU 电源调节 到高阻状态,这样可以防止其与板外提供的数据冲突 [1]。这 种编程方式有一定的优点,第一,可以避免手动编程常发生 的方向错误、引脚错位等问题,也可以提高编程的准确度和 可靠性,提高编程的效率。第二,可以实现软件更新的功能, 这对于手机等常用电子设备来讲是非常重要的优点。但是, 这种使用板编程也有一定的缺点,就是编程比较复杂,还要 在使用板上安排隔离、接口这类辅助电路,并且编程中会进 行 FET 开关与工作状态的转换,从而使使用的芯片增加,提 高了设备成本。

Abstract: This article first elaborated through programmer programming, using plate programmer programming, system programming, the three common chip programming method, and then the structure of the JTAG, JTAG pins and TAG test access port controller, these three aspects introduced the related contents of JTAG interface, the final from two aspects of hardware configuration and control software are analyzed using the JTAG interface.

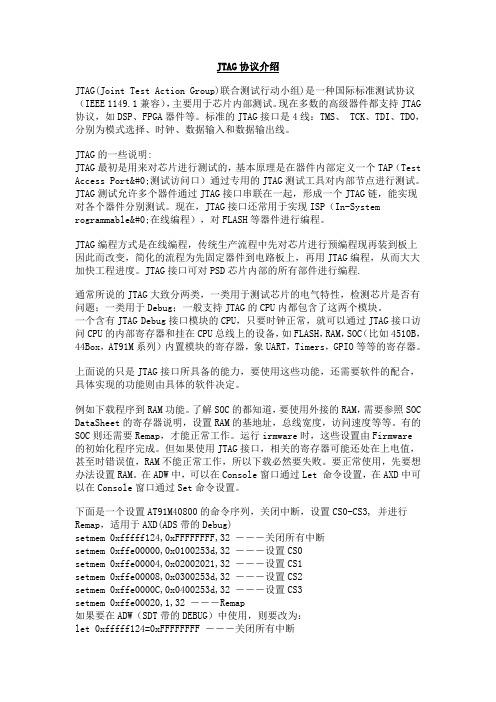

JTAG协议介绍

JTAG协议介绍JTAG(Joint Test Action Group)联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG 协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、 TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG的一些说明:JTAG最初是用来对芯片进行测试的,基本原理是在器件内部定义一个TAP(Test Access Port�测试访问口)通过专用的JTAG测试工具对内部节点进行测试。

JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。

现在,JTAG接口还常用于实现ISP(In-System rogrammable�在线编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对PSD芯片内部的所有部件进行编程.通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。

一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。

上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。

例如下载程序到RAM功能。

了解SOC的都知道,要使用外接的RAM,需要参照SOC DataSheet的寄存器说明,设置RAM的基地址,总线宽度,访问速度等等。

JTAG接口介绍

JTAG接口介绍JTAG接口用途介绍JTAG就是一个通信/调试的接口,即便在操作系统损坏了或未安装的情况下,也可以直接访问flash芯片。

如果你的flash烧录了不当固件,或中断烧录过程等,导致该设备报销了,可以通过JTAG使你的设备起死回生!还可以通过JTAG来备份现存flash中的内容。

这对移植大有裨益。

所需要的仅仅是一条短短的接口电缆,一段软件,当然您设备的电路板上还要具有一个JTAG接头。

这个JTAG接头一般距离flash芯片很近。

多数情况下JTAG接头有12-14个插脚孔位,插脚之间的间距一定是2.54mm自制接口电缆相当的容易。

需要些备件,都可以在当地电子商店买到,还需要些锡焊技术和一个万用表。

备件:4个100欧姆电阻1个25针D型插头(PC并口插头)1个D型插头用的外壳12-14股的排线或单线。

1个合适的JTAG插座(将焊在电路板的)1个合适的JTAG插头(插在焊接在电路板上的插座)电路图:25针D型插头 JTAG插头Pin 2 -------[100欧姆]------- Pin 3(D0) ( TDI)Pin 3 -------[100欧姆]------- Pin 9(D1) ( TCK)Pin 4 -------[100欧姆]------- Pin 7(D2) ( TMS)Pin 13 -------[100欧姆]------- Pin 5(Select) (TD0)Pin 20 ---+------------------ Pin 6(GND) | ( GND)|Pin 25---+100欧姆的电阻在这里的主要作用应该是限流的,如果实在没有100欧姆的电阻,这种的情况可以省略:JTAG接口已经配置了4.7 K 欧姆电阻。

注意,JTAG的接口位置的丝印字样可能有所不同,甚至没有。

某些板上的JTAG标记是“ JP1 ”而COM端口的标记是“ JP2 ”。

从针脚上和COM端口区分有点困难,但是JTAG有12个接点,COM 端口有10个接点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

嵌入式开发JTAG接口的应用介绍

通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。

一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU 的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。

上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。

例如下载程序到RAM功能。

了解SOC的都知道,要使用外接的RAM,需要参照SOCDataSheet的寄存器说明,设置RAM的基地址,总线宽度,访问速度等等。

有的SOC则还需要Remap,才能正常工作。

运行Firmware时,这些设置由Firmware的初始化程序完成。

但如果使用JTAG接口,相关的寄存器可能还处在上电值,甚至时错误值,RAM不能正常工作,所以下载必然要失败。

要正常使用,先要想办法设置RAM。

在ADW中,可以在Console窗口通过Let 命令设置,在AXD中可以在Console窗口通过Set 命令设置。

下面是一个设置AT91M40800的命令序列,关闭中断,设置CS0-CS3,并进行Remap,适用于AXD(ADS带的Debug)

setmem 0xfffff124,0xFFFFFFFF,32 ---关闭所有中断

setmem 0xffe00000,0x0100253d,32 ---设置CS0 0xffe00004,0x02002021,32 ---设置CS1

setmem 0xffe00008,0x0300253d,32 ---设置CS2

setmem 0xffe0000C,0x0400253d,32 ---设置CS3

setmem 0xffe00020,1,32 ---Remap

如果要在ADW(SDT带的DEBUG)中使用,则要改为:

let 0xfffff124=0xFFFFFFFF ---关闭所有中断。