第9章 8253芯片介绍

微机第9章8253

0 0----选计数器0

0 1----选计数器1 1 0----选计数器2 1 1----无意义

写入控制口,地址A1A0=11

2、计数初值的写入

若规定只写低8位,则写入的为计数值的低8位, 高8位自动置0; 若规定只写高8位,则写入的为计数值的高8位, 低8位自动置0; 若是16位计数值,则分两次写入,先写低8位, 再写入高8位。

计数值写入计数器各自的 计数通道(端口地址)

注: ① 写入控制字后,所有控制逻辑电路复位, 输出端OUT进入初始状态。 ② CPU向8253写入的计数初值,要在CLK端输入一个 正脉冲后才能被真正装入指定通道(若在此CLK下降 沿之前读计数器,则其值是不定的)。 之后再次输入时钟脉冲(CLK)才开始计数,且每次 在脉冲的下降沿减1计数。 即:写入计数初值后,经过一个CLK,8253才开始计 数。

④ 当GATE变为低电平时计数 停止,再变为高电平时计数继 续进行。 ⑤若计数过程中重新送入初值, 则按新值重新计数。

(2)方式1——可重复触发单稳触发器

WR CLK GATE OUT 3 2 1 0 FFFE 3 2 方式1时序图 CW N=3

③计数过程中,再次给通道写入时间 ①写入CW后OUT变为高电平, GATE 常数,不影响现行操作过程,GATE再 上升沿触发后,OUT变为低并开始计数, 次触发后才按新的时间常数操作。 归零时OUT变为高电平。 ④计数过程中,GATE触发沿提前到来, ②GATE再来一次上升沿使OUT为低, 在下一个CLK的下降沿,计数器开始重 新计数,这将使输出单稳脉冲比原先 计数器以初值重新计数。 设定的计数值加宽。 可重复触发——当计数归零后,不用再次送计数值,只要给它触发脉冲,即 可产生一个同样宽度的单稳脉冲输出。

8253的主要功能

4)计数器通道 计数器0 计数器1 计数器2 计数器0、计数器1、计数器2 独立16位减法计数器,计数值可写入或读出。 16位减法计数器 独立16位减法计数器,计数值可写入或读出。 5)引线 CLK — 时钟脉冲输入线 GATE—门控信号输入 为低时禁止计数器计数. 门控信号输入, GATE 门控信号输入,为低时禁止计数器计数. 计数/定时输出,当计数到0时输出信号. OUT — 计数/定时输出,当计数到0时输出信号. A0、 A0、A1 — 通道地址选择 计数器0 计数器1 00 — 计数器0;01 — 计数器1; 计数器2 10 — 计数器2;11 — 控制字寄存器

ቤተ መጻሕፍቲ ባይዱ

2)确定计数值 ) 位为80, 位为 位为50 低8位为 ,高8位为 位为 3)初始化程序 ) 计数器: 端口地址 计数器:0F8H 控制字寄存器: 控制字寄存器:0FBH MOV AL,33H , OUT 0FBH,AL , MOV AL,80H , OUT 0F8H,AL , MOV AL,50H , OUT 0F8H,AL , 若计数器工作后,要读取某时刻的计数值, 若计数器工作后,要读取某时刻的计数值,则 程序实现为: 程序实现为:

控制字: 控制字:00 00 001 1B=03H MOV AL,03H , OUT 0FBH,AL , IN AL,0F8H , MOV CL,AL , IN AL,0F8H , MOV CH,AL ,

8253的控制字 三、8253的控制字 控制字的作用是决定 控制字的作用是决定8253各计数器工作方式 各计数器工作方式 。 控制字寄存器实际上是 个,分别控制三个计 控制字寄存器实际上是3个 数器,但它们的端口地址相同。 数器,但它们的端口地址相同。 D7、D6 :计数器选择 、 00 — 计数器 ; 01 — 计数器 计数器0; 计数器1 10 — 计数器 ; 11 — 非法 计数器2; D5、D4 :读写格式 、 00 — 计数器锁存;使当前计数值锁存,以后 计数器锁存;使当前计数值锁存, 再读取;因计数器为16位,而数据线8位,故 再读取;因计数器为 位 而数据线 位 需锁存,分次读取。 需锁存,分次读取。

第9章 计数器8253-PIT

注: 下面的约定适用于所有的工作方式波形图:

计数器编程采用二进制方式,只对低字节操作 计数器的片选信号 CS 一直处于低电平; CW表示控制字(Control Word);CW=10 表示10H写 入计数器; LSB表示计数器的低字节; 图下的数字表示计数值:上面的数是高字节,下面 的数是低字节;

方式2波形图

四、方式3 (方波速率发生器)

计数过程 方式3的计数过程按计数初值的不同分为两种 情况:

(1)计数初值为偶数 写入控制字后的第一个时 钟上升沿,输出端OUT变成高电平。若GATE= 1,写入计数初值后的第一个时钟下降沿开始减2 计数。减到N/2个CLK时,输出端OUT变为低电 平;再减到0时,输出端OUT又变成高电平,并 重新从初值开始新的计数过程。可见,输出端 OUT的波形是连续的方波,故称方波发生器

8253的内部结构

一、数据总线缓冲器

该缓冲器为8位双向三态的缓冲器,可直接 挂在数据总线上。通过它,一方面可以向控 制寄存器写入控制字,向计数器写入计数初 值;另一方面也可由CPU通过该缓冲器读取 计数器的当前计数值 二、读/写控制逻辑

读/写逻辑的功能是接收来自CPU的控制信 号,包括读信号RD 、写信号 WR 、片选信号 CS 和芯片内部寄存器的寻址信号A1、A0,并完成 对8253各计数器的读/写操作

方式4波形图

六、方式5 (硬件触发选通方式)

计数过程

写入控制字后,输出OUT即为高电平。写入计 数初值后,计数器并不立即开始计数,而是由门控 脉冲的上升沿触发。计数结束 (计数器减到0),输 出一个持续时间为一个CLK时钟周期的负脉冲,然 后输出恢复为高电平。直到GATE信号再次触发。 输出负脉冲可以用作选通脉冲,它是通过硬件 电路产生的门控信号上升沿触发得到的,所以叫硬 件触发选通方式

第9章 8253

与系统的连接示意

8253

DB

IOW

IOR

A1

A0 高

位 地

译码器

址

D0~D7

WR CLK RD GATE A1

OUT A0

CS

外部时钟 门控信号

外设

应用中的注意点

n 每一次启动计数,需有两次写操作:

• 写控制字 • 写计数器初值

n 如果初值为8位字长,则一次写入;若初值为16位字长,则 需两次写入

初始化程序流程

写入全部计数器控制字

写CNT0计数初值 写CNT1计数初值

原则:

u 先写入控制字 u 后写入计数初值

写CNT2计数初值

8253应用例一

n 采用8253作定时/计数器,其接口地址为 0120H~0123H。

n 输入8253的时钟频率为2MH。要求:

• CNT0每10ms输出一个CLK周期宽的负脉冲 工启作动的方计式数器

A0

OUT0

OUT1 CS

OUT2

+5V 2MHz

8253应用例——初始化程序

CNT0: MOV DX, 0123H MOV AL,34H OUT DX,AL MOV DX, 0120H MOV AX,20000 OUT DX,AL

MOV AL,AH OUT DX,AL

CNT1: ……

CNT2: ……

: A5 A11 A10

&

&

≥1 A4 A3 A2

G1

Y

0

G2A

G2B

C B A

例二解

n 8253计数初值: n 8253初始化程序:

• 2MHz/100Hz=200 00

n 8253工作方式:

最新第九章可编程计数器定时器8253及其应用概要PPT课件

arsf 发菜

银鱼(WhiteBait)是指鲱鱼苗或小鲱鱼,这种小型的银鱼通常 是在地中海及大西洋捕获。 全年都有供应,但春夏两季时肉质最肥美。

arsf 发菜

生鲜或冷冻鱼都有卖。 白色稍透明,长不过 3 厘米左右,通体无鳞,一向作为整体性食 物应用即(内脏、头、翅等均不去掉,整体食用),而整体性食 物目前作为一种天然的“长寿食品”为国际营养学会所确认。

arsf 发菜

欢它,不惜以重金购买馈赠亲朋或制作佳肴。

arsf 发菜

arsf 发菜

入肝、肾、膀胱经。 具有清热消滞、软坚化痰、理肠除垢、解毒滋补、通便利尿、化 湿去腻、散结和降血压的功效。

arsf 发菜

据中医书籍中介绍,发菜对甲状腺肿大,淋巴结核、脚气病、鼻 出血、缺铁性贫血、高血压和妇科病等都有一定的疗效。 贴士因发菜跟“发财”谐音,港、澳、台同胞和海外侨胞特别喜

方式3——方波发生器

8253计数/定时器——工作方式

方式3——方波发生器

写入工作方式字

微机原理与接口技术——第9章(8253)

8253工作方式 工作方式2—频率发生器 工作方式 频率发生器

8253工作方式 工作方式2—频率发生器 工作方式 频率发生器

8253工作方式 方波发生器 工作方式3-工作方式

• 方式3在计数过程中的输出(OUT)有一半时间为高电 平,另一半时间为低电平。所以,方式3的输出OUT为 一个方波 。 • CPU设置方式3后,输出保持为高电平,若GATE=1, 写入计数值后,输出仍为高电平,并自动开始计数。当 计数到一半计数值时,输出变为低,直到计数为0,输 出又变高,并重新装入初始值,开始计数 。 • 当计数值为偶数时,前一半输出为高电平,后一半输出 为低电平。如果计数值为奇数,前一半输出为高电平的 持续时间多一个时钟脉冲,随后输出为低电平的持续时 间(比高电平少一个时钟脉冲的持续时间)。

8253工作方式 工作方式4--软件触发 工作方式

• 方式4:软件触发选通信号发生 (一次性) • 与方式0不同是输出OUT的相位相反。门控信 号GATE变低不影响输出,但停止计数过程。 • 置方式4后,输出OUT变高,写入计数值后, 输出仍保持高。从下一时钟装入计数值,开始 计数,到计数值为0时,OUT变低,并持续一 个时钟周期,再变高,并停止计数。 • 若GATE=0,写入计数值后,不开始计数工作, 直到GATE=1,开始计数。 • 若计数未完成,重新写入计数值,将从新值重 新开始。

实现定时功能的主要方法

1. 2. 3. 4. CPU软件延时; 简单的硬件电路定时; 可编程芯片的硬件定时; 专用时钟芯片。

软件定时器

• 设计循环程序,通过精心计算循环次数,和循 环中每条指令的执行时间。执行一次这个程序 段,就产生一个延时时间。 • 优点是不需硬件,缺点是占用CPU时间,并且 不容易实现精确定时。 • 在不同的系统时钟频率下,同一个软件延时程 序的定时时间也会相去甚远,因此这种方法常 用在对延时时间小,并且不需精确定时的场合, 如等待模数变换等。

第九章_计数器8253—PIT

表 9-5在计数过程中改变计数值

方式 0 1 2 3 4 5 功 能 改变计数值 立即有效 外部触发后有效 计数到1后有效 (1) 外部触发后有效 (2) 计数到0后有效 立即有效 外部触发后有效

计完最后一个数中断 硬件再触发单拍脉冲 速率发生器 方波速率发生器 软件触发选通 硬件触发选通

9.4 8253-PIT的编程 的编程

8253的初始化编程步骤: 的初始化编程步骤: 的初始化编程步骤

当初始化8253某个计数通道时, (1)首先把相应的方式控制字写入到控制字寄存器中, (2)再根据控制字中数据读/写格式(D5D4)位的规定,写 入计数初值到对应的计数通道。 8253工作过程中,任一通道的计数值,CPU可用输入指令 读取。CPU读到的是执行输入指令瞬间计数器的当前值, 但8253的计数器是16位的,所以要分2次读至CPU,因 此,若不锁存的话,在前后两次执行输入指令的过程中, 计数值可能已经发生变化了

9.3 8253-PIT的工作方式 的工作方式

8253的每一个计数器都可以按照控制字的规定有 6种不同的工作方式。下面结合时序波形图介绍各种 工作方式的计数过程 一、方式0(计数结束中断方式) 计数过程 当写入方式0控制字后,OUT立即变为低电平, 并且在计数过程中一直维持低电平。若GATE=1,写 入初值后,CLK第1个下降沿到,计数值装入计数器, 随后每一个CLK脉冲下降沿到,计数器减1。计数器 减到零时,OUT输出变为高电平,并且一直保持到 该通道重新装入计数值或重新设置工作方式为止

工作方式(D3D2D1) 8253的每个通道可以有6种不同的工作方式,由 D3D2D1 三位决定,具体情况在9.3节中详细介绍 数制选择(D0) 8253的每个通道都有两种计数制:二进制和二十进制(BCD码),由D0位决定。在二进制时,写 入初值的范围为0000H~FFFFH,其中0000H是 最大值,表示65536。在二—十进制时,写入初 值范围为0000~9999,其中0000表示最大值 l0000。因为计数器是先减1,再判断是否为0, 所以写入0实际代表最大计数值

第9章常用可编程接口芯片及其应用8253

8253寄存器选择表

4. 8253的控制字格式

在8253工作之前,必须对它进行初始化编程,

也就是向8253的控制字寄存器写入一个控制字和

向计数器赋计数初值。 控制字的功能是:选择 计数器,确定对计数器的读/写格式,选择计数 器的工作方式以及确定计数的数制。8253控制字 的格式如图 所示。

D7 SC1

BCD:数制选择。8253的每个计数器有两种数制二 进制和二—十进制,由这一位决定选择哪一种。 BCD=0表示采用二进制计数,写入的初值范围为 0000H~FFFFH;BCD=1表示采用二—十进制计数, 写入的初值范围为0000~9999。 注意:

(1)8253内部的三个计数通道共用一个控制寄存 器,当前控制字倒底对哪一个通道有用是由最高两 位决定的。 (2)用户如果需要读出当前计数器的值,必须先 发控制字令计数值锁存;然后在下一条指令才能读 回已锁存的计数值。

例1

8253工作为计数器 0,方式 0,初值为4, 二进制计数,设寄存器地址为40H 、42H、 44H、46H 0 0 0 1 0 0 0 0 10H 控制字

MOV AL,10H

编程

OUT 46H,AL ;写计数器 0 的控制字

MOV AL,04H OUT 40H,AL ;写计数器 0 的初值

8253的读操作所得到的是当前计数值,通常用于实时检测、 实时显示和数据处理。在进行读操作时需要注意以下几点:

① 读操作是通过访问对应于各计数器的地址单元来实 现的。② 每个计数器的读操作必须按照控制字确定的 格式。 如果是16位计数,读操作要进行两次,先读低 8位,后读高8位。 ③ 当计数器为16位时,为了避免在 两次读出过程中计数值的变化,要求先将计数值锁存。 锁存计数值的常用方法是使用计数器锁存命令:控制 字的D7D6两位为所要锁存的计数值, D5D4两位置为00。 8253的每个计数器都有一个输出锁存器(16位),平 时它的值跟随计数值而变化。当向计数器写入锁存命 令后,现行计数值被锁存(计数器仍能继续计数)。 这样CPU读取的就是锁存器中的值。 当CPU读取了计 数值或对计数器重新编程以后,锁存状态被解除,输 出锁存器的值又随计数值变化。

微机原理第09章 8253-2(完)

方式3 方波发生器

方式3

WR CLK 4

GATE

4 3 2 1 0 4 3 2 1 0 4 3 2 1 0 4 3 2波频率

方式4 软件触发选通信号

方式4 WR CLK GATE 4

4 3 2 1 0

OUT

方式5 硬件触发选通信号

方式5 WR 4

CLK GATE

3

2

1

0

④ 计 数 ⑥初 ⑤② ③ 值① 计送 计写 硬 数减 写 数入 入 件 结 1计 过 控 启 束计 程数 制 动 初 数 字 值 寄 存 器

方式2 频率发生器(分频器)

方式2 4

WR CLK

GATE 4 3 2 1 0 4 3 2 1 0 4 3 2 1 0 4 3 2 1 0

OUT

计数初值=时钟脉冲频率/负脉冲发生频率

向控制字端口地址:写入锁存命令 从计数器端口地址:读取锁存的当前计数值

读取计数值,要注意读写格式和计数数制

例1:要求计数器0工作于方式3,输出方波的频率为 2KHz,计数脉冲的频率为2.5MHz,采用二进制计数,试 写出初始化程序段。

1. 8253的端口地址为:80H,81H,82H,83H。 2. 计数初值计算:TC = 2.5MHz/2KHz=1250 3. 8253的方式控制字为: 00 11 011 0 4. 初始化程序段: MOV OUT MOV OUT MOV OUT AL,00110110B 83H,AL AX, 1250 80H,AL AL, AH 80H,AL

D3 D2

D1

D0

计数器

00: 计数器0 01: 计数器1 10: 计数器2 11: 无意义

读写格式

00: 锁存计数值 01: 只读写低8位 10: 只读写高8位 11: 先读写低8位 后读写高8位

微机原理 8253简介

;计数器0,双字节,

;方式3,二进制计数

;写入控制寄存器 ;写低字节 ;写高字节

16

MOV

OUT

AX,533H

40H,AL

MOV

OUT

AL,AH

40H,AL

MOV AL, 54H OUT MOV OUT 43H,AL AL,18 41H,AL

;计数器1,只写低字节 ;方式2二进制计数 ;写入控制寄存器 ;将低字节计数值18 ;写入计数器1

0#计数器初始化编程 1#计数器初始化编程 MOV OUT MOV OUT MOV OUT AL, 37H ; 01010100B 37H=0011,0111B ;对1#计数器送控制字 43H, AL AL, 54H 18H 40H, AL 41H, AL, 23H 40H, AL ;送初值高8位

19

间间隔

• 计数电路如果记录外设提供的具有一定随机性

的脉冲信号时,它主要反映脉冲的个数(进而

获知外设的某种状态),常又称为计数器

定时功能的实现方法

• 软件延时——利用微处理器执行一个延 时程序段实现 • 不可编程的硬件定时——采用分频器、 单稳电路或简易定时电路控制定时时间 • 可编程的硬件定时——软件硬件相结合、 用可编程定时器芯片构成一个方便灵活 的定时电路

本章作业

P267 9-5 、 9-6

33

8253/8254定时计数器

• 3个独立的16位计数器通道 • 每个计数器有6种工作方式 • 按二进制或十进制(BCD码)计数 • 最高计数频率达2MHz

8254是8253的改进型

8253/8254的I/O地址

CS 0 0 0 RD 1 1 1 WR 0 0 0 A1 0 0 1 A0 0 1 0 功 能

8253芯片

方式5——硬件触发选通方式

CW=1AH N=3 WR

GATE 启动计数

CLK OUT GATE

3

21

0

GATE重复 OUT 启动计数 GATE

3

2

3 21

0

WR

CW=1AH

N=4

N=2

计数中改 变计数值

OUT

4

3

2

2

1

0

GATE

工作方式

000:方式0 001:方式1 ×10:方式2 ×11:方式3 100:方式4 101:方式5

0:二进制计数 进制方式 1:十进制计数

8253三个计数器均有6种工作方式,主要区别: 输出波形不同 启动计数器的方式不同 计数过程中门控信号GATE对计数操作的影响不同

方式0——计数结束中断方式

0

1

0

选中计数器2#

1

0

读输出锁存器OL当前值

0

1

1

0

1

选中控制寄存器

由控制字格式中SC1SC0位 决定属于哪个计数器

8253的工作方式

方式0——计数结束中断方式 方式1——外触发单稳脉冲方式 方式2——频率发生器方式 方式3——方波发生器方式 方式4——软件触发选通方式 方式5——硬件触发选通方式

8253的控制字格式

由控制字寄存器决定

D7

D6

D5

D4

D3

D2

D1

D0

SC1

SC0

RL1

RL0

M2

M1

M0

BCD

选择计数器

0 0:选0#计数器的控制寄存器 0 1:选1#计数器的控制寄存器 1 0:选2#计数器的控制寄存器 1 1:非法值

第9章 8253芯片介绍

3.可编程的定时 在微机系统中,常采用软件、硬件相 结合的方法,用可编程定时计数器芯片构 成一个方便灵活的定时计数电路。这种电 路不仅定时值和定时范围可用程序确定和 改变,而且具有多种工作方式,可以输出 多种控制信号,它由微处理器的时钟信号 提供时间基准,故计时也精确稳定。如 Intel 8253。

2. 方式1 —— 可编程的单稳态触发器 (Programmable One Short)

硬件启动,不自动重复计数。装入初值后OUT端变高电平, 计数开始OUT端变为低电平,计数结束后又变高。

方式1的工作波形如图9.5(a)、 (b)、(c)所示。

CW = 12 WR

LSB = 3

CLK GATE

OUT

3 2 1 0 FF 3 2

图9.5(a) 方式1 正常计数

CW = 12 LSB = 3 WR CLK GATE OUT 3 2 1 3 2 1 0

图9.5(b) 方式1时GATE 信号的作用

CW = 12 WR CLK GATE

LSB = 2

LSB=4

OUT

2 1 0 FF FE 4 3

CW = 16 WR CLK GATE OUT

LSB = 5

LSB = 4

5

4

3

2

1

4

3

d. 方式3 计数过程中改变计数值

图9.7(d) 方式3 计数过程中改变计数值

5. 方式4 —— 软件触发选通方式 (Software Triggered Strobe)

软件启动,不自动重复计数。装入初值后输出端变 高电平,计数结束输出一个CLK宽度的负脉冲

(2)读/写控制逻辑

决定三个计数器和控制字寄存器中哪一个能进行工 作,并控制内部总线上数据传送的方向。

8253的主要功能

8253的控制字 三、8253的控制字 控制字的作用是决定 控制字的作用是决定8253各计数器工作方式 各计数器工作方式 。 控制字寄存器实际上是 个,分别控制三个计 控制字寄存器实际上是3个 数器,但它们的端口地址相同。 数器,但它们的端口地址相同。 D7、D6 :计数器选择 、 00 — 计数器 ; 01 — 计数器 计数器0; 计数器1 10 — 计数器 ; 11 — 非法 计数器2; D5、D4 :读写格式 、 00 — 计数器锁存;使当前计数值锁存,以后 计数器锁存;使当前计数值锁存, 再读取;因计数器为16位,而数据线8位,故 再读取;因计数器为 位 而数据线 位 需锁存,分次读取。 需锁存,分次读取。

在二进制计数方式下, 在二进制计数方式下,写入计数器初值范围 的计数值最大, 为0000H~FFFFH,其中 ,其中0000H的计数值最大 的计数值最大 数值为2 数值为 16=65536 在BCD码计数方式下,写入计数器初值范围 码计数方式下, 码计数方式下 计数值最大, 为0000~9999,其中 ,其中0000计数值最大,数值为 计数值最大 10000。 。

2)确定计数值 ) 位为80, 位为 位为50 低8位为 ,高8位为 位为 3)初始化程序 ) 计数器: 端口地址 计数器:0F8H 控制字寄存器: 控制字寄存器:0FBH MOV AL,33H , OUT 0FBH,AL , MOV AL,80H , OUT 0F8H,AL , MOV AL,50H , OUT 0F8H,AL , 若计数器工作后,要读取某时刻的计数值, 若计数器工作后,要读取某时刻的计数值,则 程序实现为: 程序实现为:

8253的工作方式 四、8253的工作方式 方式0 方式5, 方式 ~ 方式 ,共6种。详略 种 8253的初始化 五、8253的初始化 在硬件连接好后,在使用 在硬件连接好后,在使用8253时必须对其初 时必须对其初 始化。 始化。 对8253初始化编程有两项内容:先写入计数 初始化编程有两项内容: 初始化编程有两项内容 通道的控制字,再写入通道的计数值。 通道的控制字,再写入通道的计数值。 三个通道的控制字寄存器使用同一个端口地 三个通道的控制字寄存器使用同一个端口地 由控制字的内容 内容决定是哪个通道的控制字 址由控制字的内容决定是哪个通道的控制字 。 初始化步骤 1)写入通道控制字,设置通道工作方式 )写入通道控制字, 2)写入计数值 )

8253(8254的使用说明讲义)

第9章 计数器和定时器电路Intel 8253/8254-PIT在控制系统中,常常要求有一些实时时钟以实现定时或延时控制,如定时中断、定时检测、定时扫描等,也往往要求有计数器能对外部事件计数。

要实现定时或延时控制,有三种主要方法:软件定时、不可编程的硬件定时、可编程的硬件定时器。

软件定时——即让计算机执行一个程序段,这个程序段本身没有具体的执行目的,但由于执行每条指令都需要时间,则执行一个程序段就需要一个固定的时间。

通过正确地挑选指令和安排循环次数很容易实现软件定时,但软件定时占用了CPU的时间,降低了CPU的利用率。

不可编程的硬件定时可以采用小规模集成电路器件如555,外接定时部件——电阻和电容构成。

这样的定时电路简单,而且利用改变电阻和电容,可以使定时在一定的范围内改变。

但是,这种定时电路在硬件连接好以后,定时值及定时范围不能由程序(软件)来控制和改变,由此就生产了可编程的定时器电路。

可编程定时器电路的定时值及其范围,可以很容易地由软件来确定和改变。

所以,功能较强,使用灵活。

本章就介绍这种定时器电路。

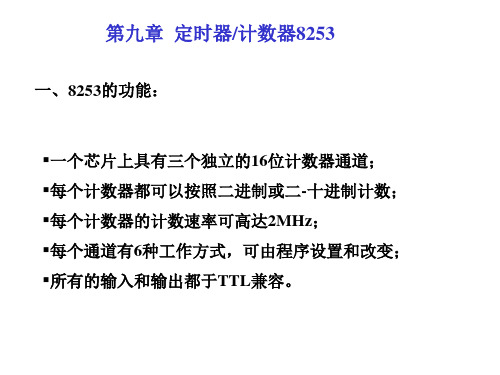

§9.1 概述Intel系列的计数器/定时器电路为可编程序间隔定时器PIT(Programmable Interval Timer),型号为8253,改进型为8254。

Intel 8253具有3个独立的16位计数器通道,使用单一5V电源,它是24个引脚的双列直插式器件。

9.1.1 8253-PIT的主要功能Intel 8253-PIT具有以下主要功能:(1) 一个芯片上有三个独立的16位计数器通道;(2) 每个计数器都可以按照二进制或二—十进制计数;(3) 每个计数器的计数速率可高达2MHz。

(82C54-2计数频率可达到10MHz);(4) 每个通道有6种工作方式,可由程序设置和改变;(5) 所有的输入输出都与TTL兼容。

9.1.2 8253-PIT的内部结构8253的内部结构如图9-1所示。

8253芯片

计数器 0

数据线

计数器 1

控制线

计数器 2

电源线

8253引脚

8253与CPU的接口

8 位数据线:D0 ~ D7

寻址控制线:A0、A1、CS

读写控制线: RD、WR

8253与外设的接口

注: 三个独立的计数器/定时器 时钟输入:CLK 输入门控:GATE

波形输出:OUT

8253寄存器选择表

方式3—方波发生器

与方式2类似,但其输出方波或准方波 计数值完成一半时,使OUT变低,直到计 数任务全部完成为止,OUT恢复为高 初值为偶数时,每次减2,直至0时OUT输 出变为低电平,然后又从初值开始,每次减 2,直至0时OUT输出变为高电平 初值为奇数时,先减1,后每次减2,直至为 0。即有(N+1)/2个脉宽的高电平,(N-1)/2个脉 宽的低电平 GATE由低变高时,重新开始计数

内部的各计数器的结构

锁存后读 出当前值 CLK GATE

MSB 16位当前计数值锁存器

LSB

&

16位减一计数器

16位计数初值寄存器 LSB MSB

OUT (减1 至0时)

装入初值

9.2.2

8253的控制字

例

将计数器2初始化为工作方式3,计数初值为533H, 为二进制计数方式,设寄存器地址为40H ~ 43H 1 0 1 1 0 1 1 0

8253各工作方式的共同点

控制字写入计数器时,所有控制逻辑 立即复位,输出端OUT进入初始态

写入初值后,要经过一个时钟周期后 计数执行部件CE才开始工作 时 钟 脉 冲 CLK 的 上 升 沿 , 门 控 信 号 GATE被采样

微机接口8088第九章8253

START: MOV11A先L读, 1写4低H位字节 011 方式 3

OUT 7再3读H写, A高L位字节 100 方式 4

MOV AL, 100

101 方式 5

OUT 70H, AL

CODE ENDS END START

示例2

例:设三个计数器的端口地址为70H、71H、72H,控制寄存 器端口地址73H。计数器1,工作模式1,初值为1234H,计数 值使用BCD。

计数方式选择 0 二进制 1 BCD 码

五、8253的工作模式(6种) 方式0——计数结束产生中断

计数初值写入CR后,OUT由0到1跳变出现在n+1个时钟脉冲之后 延迟时间TD=(n+1)TCLK

方式1——可重复触发的单脉冲发生器

单脉冲宽度T=n TCLK

方式2——分频器(定时时钟)

3

方式3——方波发生器

第九章 定时器/计数器8253

一、8253的功能:

▪一个芯片上具有三个独立的16位计数器通道; ▪每个计数器都可以按照二进制或二-十进制计数; ▪每个计数器的计数速率可高达2MHz; ▪每个通道有6种工作方式,可由程序设置和改变; ▪所有的输入和输出都于TTL兼容。

二、8253的内部结构及管脚

D7-D0

C计O数DE器S选E择GMENT 读写方式选择

工作方式选择

AS0S0TS计AUR数MT器E:C0MS:OCOVD0AE0,DL锁S,存:1D6AHTA,SS:STACK000 方式 0

首先,CPU把控制字写入控制寄存器,计数初始值 写入初值寄存器;

GATE=1,经过一个CLK输入后开始计数。 计数从初值开始,每当CLK信号出现一次,计数值 减1,当计数值减到0,从OUT端输出规定的信号。

微机原理与接口技术第九章8253

功 能 向CNT 0写入计数初值 读取CNT 0的当前计数值 向CNT 1写入计数初值

0

0 0 0 0

1

0 1 0 1

0

1 0 1 0

0 1

1 0 1 0 1 1 1 1

读取CNT 1的当前计数值

向CNT 2写入计数初值 读取CNT 2的当前计数值 写入控制字

0

1

1

×

1

×

× ×

× ×

数据引脚D7 ~ D0呈高阻

N为奇数,CR内容先减1,再装入CE中, 其他同前(近似方波)

35

(6)工作方式3—方波发生器

CW=16h WR LSB=4

CLK GATE

OUT CE

N

N

N

4

2

4

2

4

2

4

2

4

2

36

(6)工作方式3—方波发生器

CW=16 WR LSB=5

CLK

GATE OUT CE

N

N

N

5

4

2

4

2

5

4

2

4

2

37

65536×55ms = 3600s

计数器1

18÷1.19MHz = 15.08μs

计数器2

1.19MHz÷1331 = 896Hz,驱动后送给扬声器

47

8253端口地址为40H ~ 43H

MOV OUT MOV OUT OUT MOV OUT MOV OUT AL,00110110B ;计数器0初始化 43H,AL ;双字节读写,方式3,二进制 AL,0 40H,AL ;写入低字节 40H,AL ;写入高字节 AL,01010100B ;计数器1初始化 43H,AL ;只读写低字节,方式2,二进制 AL,18 41H,AL ;写入低字节

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)WR——写信号,输入,低电平有效,用于控制CPU对 8253 的写操作,可与 A1,A0 信号配合以决定 是写入控制字还是计数初值;

(4)RD——读信号,输入,低电平有效。用于控制CPU 对8253的读操作,可与A1,A0信号配合读取 某个计数器的当前计数值; (5)A0,A1——地址输入线。用于8253内部寻址的4个 端口,即3个计数器和一个控制字寄存 器。一般与CPU低位的地址线相连 。

定时功能,这种方法不需要增加硬件,可通过

编程来控制和改变定时时间,灵活方便,节省 费用。缺点是CPU重复执行的这段程序的本身 并没有什么具体目的,仅为延时,从而降低了 CPU利用率。

2.不可编程的硬件定时 这种方法采用数字电路中的分频器将 系统时钟进行适当的分频产生需要的定时 信号;也可以采用单稳电路或简易定时电 路(如常用的555定时器)由外接RC电路 控制定时时间。但是,这种定时电路在硬 件接好后,定时范围不易由程序来改变和 控制,使用不甚方便,而且定时精度也不 高。

对8253来讲,外部输入到CLK引脚上的时钟脉冲 频率不能大于2.6MHZ,否则需分频后才能送到CLK端。

内部总线 初值寄存器

控制单元

减1计数器

OUT CLK GATE

输出锁存器

图9.2 计数器内部逻辑图

二、8253的引脚信号

8253是 一片具有3 个独立通 道的16位 计数器/定 时器芯片, 使用单一 +5V电源, 24引脚双 列直插式 封装,如 图9.3所示

OUT

3 2 1 0 FF 3 2

图9.5(a) 方式1 正常计数

CW = 12 LSB = 3 WR CLK GATE OUT 3 2 1 3 2 1 0

图9.5(b) 方式1时GATE 信号的作用

CW = 12 WR CLK GATE

LSB = 2

LSB=4

OUT

2 1 0 FF FE 4 3

CW = 14 WR CLK GATE OUT

LSB = 3

3

2

1

3

2

1

3

a. 方式2 正常计数

图9.6(a) 方式2 正常计数

CW = 14 WR CLK GATE OUT

LSB = 3

3

2

2

3

2

1

3

图9.6(b) 方式2时GATE信号的作用

b. 方式2 GATE信号的作用

CW = 14

LSB = 4

调度。

定时器和计数器都由数字电路中的计数电路构成。 前者记录高精度晶振脉冲信号,因此可以输出准确的时 间间隔,称为定时器,而当记录外设提供的具有一定随 机性的脉冲信号时,它主要反映脉冲的个数,称为计数 器。

定时的方法有3种:软件定时、不可编程的硬件定 时和可编程的定时。

1. 软件定时

根据CPU执行每条指令需要一定的时间, 重复执行一些指令就会占用一段固定的时间, 通过适当地选取指令和循环次数便很容易实现

用方式4工作时,GATE门控信号只是 用来允许或不允许定时操作的,定时的 执行过程由装入的初值决定,波形图如 图9.8(a)、(b)、(c)所示。

图9.8(a) 方式4 正常计数

CW = 18 WR CLK GATE OUT

LSB = 3

3

2

1

0

FF

a. 方式4 正常计数

图9.8(a) 方式4 正常计数

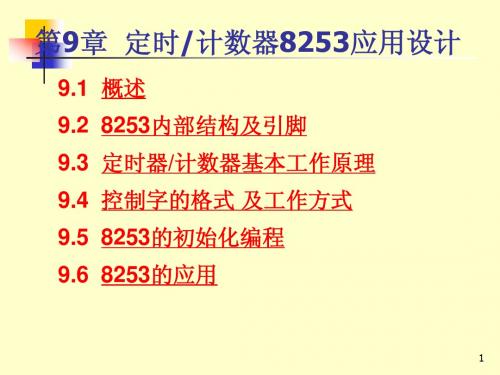

本章内容

· 定时与计数技术及应用 定时/计数器 —— 8253

学习目的

了解定时/计数技术的应用情况

掌握8253的连接与编程

熟习8253的工作方式

9.1 定时与计数

定时计数技术在计算机中具有极为重要的

作用。微机控制系统中,常要按一定的采样周

期对处理对象进行采样或定时检测某些参数等, 用计数器对外部事件计数,即记录外设提供的 脉冲个数。在实时操作系统和多任务操作系统 中,可以利用定时器产生的定时中断进行进程

2. 与外部设备的接口信号

(1)CLK0(CLK1,CLK2)——时钟脉冲输入端,用于输 入定时脉冲或计数脉冲信号。CLK可以是系统时钟脉冲,也 可以是由其他脉冲源提供。8253规定加在CLK引脚的输入时 钟周期不得小于380ns; (2)GATE0(GATE1,GATE2)——门控输入端,用于外 部控制计数器的启动或停止计数的操作。当GATE为高电平 时,允许计数器工作,当GATE为低电平时,禁止计数器工 作; ( 3 ) OUT0(OUT1,OUT2)—— 计数输出端。在不同工 作方式中,当计数器计数到 0 时, OUT 引脚上必输出相应的 信号。

2. 8253的内部结构

8253的内部结构如图9.1所示,由数据总线缓冲器、 控制寄存器、读/写控制逻辑和计数器等部分组成。

图9.1 8253的内部结构示意图

(1)数据总线缓冲器

该缓冲器为8位双向三态的缓冲器,可直接 挂在数据总线上。CPU通过8位数据总线D0~D7传

送如下信息:

①向控制寄存器写入控制字。 ②向某计数器写入计数初值。 ③CPU通过缓冲器读取计数器的当前计数值

LSB = 5

CLK GATE OUT 5 4 3 2 1 5 4 3 2 1

b. 方式3 计数值为奇数时的波形

图9.7(b) 方式3 计数值为奇数时的波形

CW = 16 WR

LSB = 4

CLK GATE

OUT 4 3 2 1 4 4 4 3 2 1

c. 方式3 GATE信号的作用

图9.7(c) 方式3 GATE信号的作用

三、8253的工作方式

8253 是一种面向微机系统的专用接口芯片,它的 每一个计数器都可以按照控制字的规定有 6 种不同的工 作方式, 每种工作方式中都有以下三种情况:

* 正常计数的波形图;

* 正在计数过程中改变门控信号GATE后对整个计

数工作的影响;

* 正在计数的过程中改变计数值对整个计数工作的

CW = 18 WR CLK GATE OUT

LSB = 3

3

3

3

2

1

0

FF

b. 方式4 GTAE信号的作用

图9.4(c) 方式0时计数过程中改变计数值

注意

8253写计数值是由CPU的WR信号控 制的,在WR信号的上升沿,计数值被送 入对应计数器的计数值寄存器,在WR信 号上升沿之后的下一个CLK脉冲才开始计 数。如果设置计数初值N,输出OUT是在 写入命令执行后,第N+1个CLK脉冲之后, 才变为高电平的。后面的方式1、2、4、5 也有同样的特点。

CW = 16 WR CLK GATE OUT

LSB = 5

LSB = 4

5

4

3

2

1

4

3

d. 方式3 计数过程中改变计数值

图9.7(d) 方式3 计数过程中改变计数值

5. 方式4 —— 软件触发选通方式 (Software Triggered Strobe)

软件启动,不自动重复计数。装入初值后输出端变 高电平,计数结束输出一个CLK宽度的负脉冲

LSB =5

WR

CLK

GATE OUT

4 3 2 1 5 4 3

图9.6(c) 方式2时计数过程中改变计数值

4. 方式3 —— 方波发生器 (Square Wave Generator)

软、硬件启动,自动重复计数。装入初值后OUT端变 高电平,然后OUT连续输出对称方波:

前 N/2或(N+1)/2 个CLK,OUT为高, 后N/2或(N-1)/2 个CLK, OUT为低。

3

2

1

0

FF

a. 方式0 正常计数

图9.4(a) 方式0 正常计数

CW = 10 WR CLK GATE OUT

LSB = 3

3

2

2

2

1

0

FF

图9.4(b) 方式0时GATE 信号的作用

CW = 10 WR CLK GATE OUT

LSB = 3

LSB = 2

3

2

1

2

1

0

FF

C. 方式0 计数过程中改变计数值

表9.1 8253读/写操作逻辑表 CS RD WR A1 A0

寄存器选择和操作

0 0 0 0 0 0 0 0 1 0

1 1 1 1 0 0 0 0 × 1

0 0 0 0 1 1 1 1 × 1

0 0 1 1 0 0 1 1 × ×

0 1 0 1 0 1 0 1 × ×

写入计数器0 写入计数器1 写入计数器2 写入控制字寄存器 读计数器0 读计数器1 读计数器2 无操作 禁止使用 无操作

9.2 Intel 8253可编程定时器/计数器

一、8253的基本功能和内部结构

1. 8253 PIT的基本功能

(1)3个独立的16位计数器,最大计数范围为0~65535; (2)每个计数器均可以按二进制或二—十进制计数; (3)计数器速率可达2.6MHz; (4)可编程6种不同的工作方式; (5)所有输入和输出都与TTL兼容。 8253具有较好的通用性和使用灵活性,几乎适合于任 何一种微处理器组成的系统。

3.可编程的定时 在微机系统中,常采用软件、硬件相 结合的方法,用可编程定时计数器芯片构 成一个方便灵活的定时计数电路。这种电 路不仅定时值和定时范围可用程序确定和 改变,而且具有多种工作方式,可以输出 多种控制信号,它由微处理器的时钟信号 提供时间基准,故计时也精确稳定。如 Intel 8253。

(3)控制寄存器

接收从CPU来的控制字,并由控制字的D7、D6位的 编码决定该控制字写入哪个计数器的控制寄存器,控制 寄存器只能写入,不能读出。

(4)计数器

当8253用作计数器时,加在CLK引脚上脉冲的间隔 可以是不相等的;当它用作定时器时,则在CLK引脚应 输入精确的时钟脉冲,8253所能实现的定时时间,取决 于计数脉冲的频率和计数器的初值,即:定时时间=时 钟脉冲周期Tc×预置的计数初值n。