数字ic设计实验报告

芯片设计实验报告

芯片设计实验报告芯片设计实验报告引言:芯片设计是现代电子工程中的重要环节,它涉及到电路设计、模拟与数字信号处理、逻辑设计等多个领域。

本实验旨在通过设计一个简单的数字逻辑电路芯片来加深对芯片设计流程的理解,并掌握相关工具的使用。

一、实验目标本实验的主要目标是设计一个4位加法器芯片,实现两个4位二进制数的相加。

通过这个实验,我们将学习到如何进行芯片设计的基本步骤,包括电路设计、逻辑门的选择与布局、电路模拟与验证等。

二、实验步骤1. 电路设计根据实验要求,我们需要设计一个4位加法器芯片。

首先,我们需要确定所需的逻辑门类型。

在这个实验中,我们选择使用AND门、OR门和XOR门。

然后,我们根据加法器的逻辑功能,设计出相应的电路图。

2. 逻辑门的选择与布局在芯片设计中,逻辑门的选择和布局非常重要。

我们需要根据电路的逻辑功能和性能要求,选择适当的逻辑门,并合理布局。

在这个实验中,我们选择使用CMOS逻辑门,并根据实验要求进行布局。

3. 电路模拟与验证在设计完成后,我们需要使用相应的电路模拟工具对设计进行验证。

通过模拟,我们可以检查电路的功能是否符合预期,并进行必要的调整。

在这个实验中,我们可以使用SPICE软件进行电路模拟。

4. 电路布线与布局在电路设计验证通过后,我们需要进行电路布线与布局。

这一步骤是将逻辑电路转化为物理电路的过程,需要考虑电路的布线规则、信号线的长度匹配等因素。

在这个实验中,我们可以使用EDA工具进行电路布线与布局。

5. 物理设计与制造在完成电路布线与布局后,我们需要进行物理设计与制造。

这一步骤是将电路布线转化为实际的芯片结构,并进行制造。

在这个实验中,我们可以使用CAD 工具进行物理设计与制造。

三、实验结果与分析通过以上的实验步骤,我们成功设计并制造了一个4位加法器芯片。

通过电路模拟与验证,我们确认了芯片的功能正常,并且满足了设计要求。

此外,我们还对芯片的性能进行了评估,包括功耗、速度等指标。

芯片设计实践实训报告

一、实训背景随着信息技术的飞速发展,集成电路(IC)产业已成为我国战略性新兴产业的重要组成部分。

为了培养具备实际操作能力和创新精神的集成电路设计人才,我们参加了为期四周的芯片设计实践实训。

本次实训旨在通过实际操作,让学生掌握芯片设计的基本流程,了解行业现状,提高动手能力和团队协作能力。

二、实训内容1. 理论学习实训开始前,我们学习了芯片设计的基本理论,包括半导体物理、数字电路基础、模拟电路基础、集成电路制造工艺等。

这些理论为后续的实践操作奠定了基础。

2. EDA工具学习为了提高芯片设计效率,我们学习了电子设计自动化(EDA)工具的使用。

主要使用的工具包括:(1)Cadence:用于电路原理图绘制、仿真、布局布线等。

(2)Verilog/VHDL:用于硬件描述语言(HDL)编程,实现数字电路设计。

(3)ModelSim:用于仿真验证,验证设计是否满足功能要求。

3. 芯片设计实践在理论学习和工具掌握的基础上,我们开始进行芯片设计实践。

以下为部分实训内容:(1)设计一个简单的数字电路,如加法器、乘法器等。

(2)设计一个模拟电路,如放大器、滤波器等。

(3)设计一个完整的芯片,包括模拟和数字部分。

4. 团队协作在实训过程中,我们分组进行芯片设计,每个小组由4-5人组成。

小组成员分工明确,共同完成芯片设计任务。

三、实训成果1. 个人成果通过本次实训,我们掌握了以下技能:(1)熟练使用Cadence、Verilog/VHDL、ModelSim等EDA工具。

(2)具备一定的电路设计和仿真能力。

(3)提高了团队协作和沟通能力。

2. 团队成果我们小组设计了一款具有以下功能的芯片:(1)数字部分:包括加法器、乘法器、比较器等。

(2)模拟部分:包括放大器、滤波器等。

(3)芯片具有低功耗、高精度等特点。

四、实训总结1. 实训收获本次实训让我们对芯片设计有了更深入的了解,提高了我们的实际操作能力和团队协作能力。

同时,我们也认识到芯片设计是一项复杂的系统工程,需要不断学习和积累经验。

IC版图设计报告

数字集成电路设计实验报告组长:李金玮14061114组员:陈久春14045101黄思佳14045102孔燕婷14045103王雨嫣14045104杨阳14045105张淼140451062016.11.10一.设计目的:1.通过本次实验,熟悉Cadence 软件的特点并掌握其使用流程和设计方法;2.了解集成电路工艺的制作流程、简单集成器件的工艺步骤、集成器件区域的层次关系,与此同时进一步了解集成电路版图设计的λ准则以及各个图层的含义和设计规则;3.掌握数字电路的基本单元CMOS 的版图,并利用CMOS 的版图设计简单的门电路,然后对其进行基本的DRC 检查;4. 掌握BC F +A =的掩模板设计与绘制。

二.设计原理:1、版图设计的目标:版图 (layout ) 是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸、各层拓扑定义等器件相关的物理信息数据。

版图设计是创建工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:① 满足电路功能、性能指标、质量要求;② 尽可能节省面积,以提高集成度,降低成本;③ 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

2、版图设计的内容:①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。

②布线:设计走线,实现管间、门间、单元间的互连。

③尺寸确定:确定晶体管尺寸(W 、L )、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。

④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。

⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。

哈理工数字IC实验3

哈尔滨理工大学软件与微电子学院实验报告(2017-2018第一学期)课程名称:数字IC班级:集成15-1学号:1514020114姓名:卢轶实验全过程记录一、实验目的:通过对NAND的VTC曲线的仿真,掌握 NAND的VTC的原理。

二、实验内容:1. 使用0.18um的工艺,写出2输入与非门的HSPICE网表,仿真出VTC曲线。

2. 仿真其逻辑功能三、实验用设备仪器及材料:软件需求:HSPICE硬件需求:微型计算机四、实验原理图:五、实验方法及步骤:1.根据电路结构编写网表2.编译3.调试、直到运行成功4.观察输出波形六、实验结果分析:1、网表:1、*nand2.include 'C:\lib\180nm_bulk.l'.param Supply=1.8.global Vdd Gnd.opt scale=0.1uVdd Vdd Gnd 'Supply'.subckt nand2 a b fmandpa f a vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandpb f b vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandna f a 1 gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandnb 1 b gnd gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 .endsX1 a b f nand2*Va a 0 pulse 0 ‘supply’0 200ps 200ps 20ns 40nsVb b 0 pulse 0 ‘supply’0 200ps 200ps 30ns 60ns.tran 140ps 100ns.plot tran v(f).end2、*nand2.include 'C:\lib\180nm_bulk.l'.param Supply=1.8.global Vdd Gnd.opt scale=0.1uVdd Vdd Gnd 'Supply'.subckt nand2 a b fmandpa f a vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandpb f b vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandna f a 1 gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandnb 1 b gnd gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 .endsX1 a b f nand2Va a 0 pulse 0 ‘supply’0 200ps 200ps 20ns 40ns*Vb b 0 pulse 0 ‘supply’0 200ps 200ps 30ns 60ns.tran 140ps 100ns.plot tran v(f).end3、*nand2.include 'C:\lib\180nm_bulk.l'.param Supply=1.8.global Vdd Gnd.opt scale=0.1uVdd Vdd Gnd 'Supply'.subckt nand2 a b fmandpa f a vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandpb f b vdd vdd PMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandna f a 1 gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mandnb 1 b gnd gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 .endsX1 a b f nand2Va a 0 pulse 0 ‘supply’0 200ps 200ps 20ns 40ns Vb b 0 pulse 0 ‘supply’0 200ps 200ps 30ns 60ns.tran 140ps 100ns.plot tran v(f).end总结:通过本次实验,我学会了编写通过对NAND网表,并分析了VTC曲线的仿真,掌握 NAND的VTC的原理。

数字IC设计实验

数字IC设计实验前言IC集成芯片设计的设计流程主要包括代码设计和验证VCS(Verilog Compiled Simulator)、前端设计与逻辑综合DC(Design Compiler)、后端实体设计ICC(IC Compiler)和时序验证PT(Prime Time)。

此次实习根据初学者的知识掌握程度合理地安排了实习的实习难度,也让实习生同学能够初步了解IC芯片设计的整个流程,充分的了解芯片设计每一阶段所需要掌握的基本知识和技能。

HDMI芯片的仿真验证设计是本次实习的主要研究内容,其中每一阶段从工具介绍、指令操作、仿真设计和最后所要达到的实验目的都有严格的标准,能够达到本次实习要求的目的。

该文档为实验文档,还有一篇《后端实验基础知识》作为知识的补充,里面从易到难讲解了一些linux系统、工具和流程方面的基础知识。

此外,Synopsys公司官方提供的参考文档也是非常好的资料(以User Guide为主),非常详细。

IC前端设计指逻辑设计;前端主要负责逻辑实现,通常是使用verilog/VHDL之类语言,进行行为级的描述,当然,也会要使用一些仿真软件。

IC后端设计指物理设计。

主要负责将前端的设计变成真正的schematic&layout,流片,量产。

后端设计需要的则会更加多一些了,包括综合,到P&R,以及最后的STA,这些工具里Candence 和Synopsys都有一整套系统的。

有关心的可以去他们的网站看看。

打个比喻来说,前端就像是做蓝图的,可以功能性,结构性的东西。

而后端则是将蓝图变成真正的高楼。

除了RTL编程和仿真这两个基本要求外,前端设计还可以包括IC 系统设计、验证(verification)、综合、STA、逻辑等值验证(equivalence check)。

其中IC系统设计最难掌握,它需要多年的IC设计经验和熟悉那个应用领域。

后端设计简单说是P&R,但是包括的东西不少,像芯片封装和管脚设计,floorplan,电源布线和功率验证,线间干扰的预防和修正,时序收敛,STA,DRC,LVS等,要求掌握和熟悉多种EDA工具以及IC生产厂家的具体要求。

ic设计研究报告

ic设计研究报告摘要本文介绍了IC设计的基本概念、设计流程和相关技术。

IC设计是集成电路(Integrated Circuit,IC)制造中的核心环节,它涉及到电路设计、模拟和数字电路、布局设计等多个领域。

文章着重讨论了IC设计的主要挑战和解决方案,并对未来的发展进行了展望。

1. 简介IC设计是一项关键的技术,它充当了集成电路中的大脑。

IC设计包括从电路设计到物理布局等多个环节,它的目标是设计出电子系统中的芯片或集成电路,以实现特定的功能。

2. IC设计的基本概念2.1 集成电路集成电路是一种将多个电子元件、电路元件和其他功能电子元器件(例如晶体管、二极管、电容器等)集成在一起的半导体器件。

2.2 IC设计的分类根据设计的复杂性,IC设计可以分为模拟IC设计和数字IC设计。

模拟IC设计是关于电流和电压变化的,而数字IC设计则是专注于逻辑电路的设计。

3. IC设计流程3.1 需求分析和规划在进行IC设计之前,首先需要进行需求分析和规划。

这一阶段确定了电路的功能和性能指标,并制定了设计的目标和计划。

3.2 电路设计在电路设计阶段,设计师使用工具如EDA(Electronic Design Automation)软件,根据需求建立电路模型,设计电路的逻辑结构。

3.3 电路模拟和验证在电路设计完成后,需要进行电路模拟和验证。

设计师使用电路仿真软件,模拟电路的行为和性能,以确保电路的正确性和稳定性。

3.4 物理布局设计物理布局设计是将电路设计转化为真实的物理形式。

设计师通过选择合适的尺寸和位置,将设计中的逻辑元件放置在芯片上,并进行连线。

3.5 特性提取和验证在物理布局设计完成后,需要进行特性提取和验证。

设计师使用特性提取软件,提取出芯片上的各种特性参数,并进行验证。

3.6 验证和测试验证和测试阶段对硬件进行全面的测试,以确保芯片的性能和功能符合设计要求。

4. IC设计的挑战和解决方案4.1 尺寸和功耗随着技术的迅猛发展,IC的尺寸越来越小,功耗也越来越低。

数字ic设计实验报告

数字集成电路设计实验报告实验名称二输入与非门的设计一.实验目的a)学习掌握版图设计过程中所需要的仿真软件b)初步熟悉使用Linux系统二.实验设备与软件PC机,RedHat,Candence三.实验过程Ⅰ电路原理图设计1.打开虚拟机VMware Workstation,进入Linux操作系统RedHat。

2.数据准备,将相应的数据文件拷贝至工作环境下,准备开始实验。

3.创建设计库,在设计库里建立一个schematic view,命名为,然后进入电路图的编辑界面。

4.电路设计设计一个二输入与非门,插入元器件,选择PDK库(xxxx35dg_XxXx)中的nmos_3p3、pmos_3p3等器件。

形成如下电路图,然后check and save,如下图。

图1.二输入与非门的电路图5.制作二输入与非门的外观symbolDesign->Create Cellview -> From Cellview,在弹出的界面,按ok后出现symbol Generation options,选择端口排放顺序和外观,然后按ok出现symbol编辑界面。

按照需要编辑成想要的符号外观,如下图。

保存退出。

图2.与非门外观6.建立仿真电路图方法和前面的“建立schemtic view”的方法一样,但在调用单元时除了调用analogL 库中的电压源、(正弦)信号源等之外,将之前完成的二输入与非门调用到电路图中,如下图。

图3.仿真电路图然后设置激励源电压输出信号为高电平为3.5v,低电平为0的方波信号。

7.启动仿真环境在ADE中设置仿真器、仿真数据存放路径和工艺库,设置好后选择好要检测的信号在电路中的节点,添加到输出栏中,运行仿真得到仿真结果图。

图4.仿真结果图Ⅱ版图设计1.数据准备2.建立设计库,然后建立一个layout view,tool选virtuso,然后进入版图编辑界面3.版图绘制在版图编辑界面中,从LSW中选择图层,然后进行二输入与非门的版图绘制。

芯片实训报告

一、引言随着科技的飞速发展,集成电路(IC)产业已成为全球最具竞争力的产业之一。

芯片作为集成电路的核心,其研发、设计、制造和应用已成为我国科技发展的关键领域。

为了提高我国芯片产业的技术水平和创新能力,我们开展了芯片实训课程,旨在让学生深入了解芯片产业,掌握芯片设计的基本方法,提高动手实践能力。

以下是我对本次芯片实训的总结报告。

二、实训内容本次实训课程主要分为三个部分:芯片设计基础、芯片设计与仿真以及芯片制造工艺。

1. 芯片设计基础实训课程首先介绍了芯片设计的基本概念、发展历程和行业现状。

通过学习,我了解到芯片设计主要包括数字电路设计、模拟电路设计、版图设计、封装设计等环节。

在此基础上,我们还学习了数字逻辑电路、模拟电路、微电子器件等专业知识,为后续芯片设计打下坚实基础。

2. 芯片设计与仿真在掌握了芯片设计基础知识后,我们开始进行芯片设计与仿真。

实训课程采用了FPGA(现场可编程门阵列)作为设计平台,通过Verilog语言进行芯片设计。

在导师的指导下,我们完成了以下任务:(1)设计一个简单的数字电路,如全加器、译码器等;(2)利用FPGA实现设计的数字电路,并进行功能测试;(3)根据实际需求,对设计的数字电路进行优化,提高其性能;(4)利用仿真软件对设计的数字电路进行功能仿真,验证其正确性。

3. 芯片制造工艺芯片制造工艺是芯片产业的核心环节,实训课程介绍了以下内容:(1)半导体材料与器件;(2)集成电路制造工艺流程;(3)光刻、刻蚀、离子注入等关键工艺;(4)封装技术。

三、实训收获通过本次芯片实训,我收获颇丰:1. 理论知识与实践能力的提升在实训过程中,我不仅巩固了所学理论知识,还学会了将理论知识应用于实际项目。

通过设计、仿真和制造工艺的学习,我对芯片产业有了更深入的了解。

2. 团队协作能力的提高实训课程要求学生分组进行项目设计,这使我学会了与他人沟通、协作,共同完成任务。

在团队中,我学会了倾听他人的意见,尊重他人的观点,为团队的成功贡献力量。

数字集成电路设计实验二报告

《数字集成电路设计》实验报告

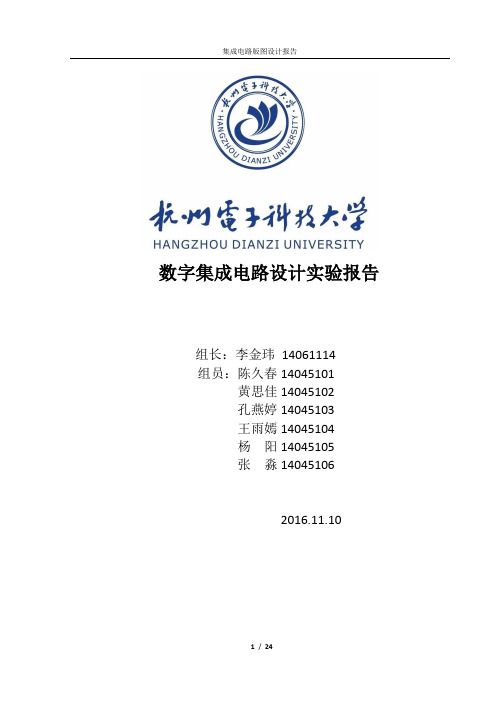

一、实验内容

有一水箱由大、小两台水泵M

L 和M

S

供水,如下图所示,箱中设置了3个水位

检测元件A、B、C。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位低于C点时两个水泵同时工作;水位高于C点而低于B点时M

S

单独工作;水位低于A点而高于B点时

M L 单独工作;水位高于A点时M

L

和M

S

停止工作。

试设计一个集成电路用于控

制两台水泵的工作,要求电路尽量简单。

二、实验目的

1、熟悉Cadence环境

2、熟悉并掌握Cadence的操作步骤

3、利用Cadence软件进行相应的电路原理图的设计并进行仿真

4、利用Cadence绘制版图并进行DRC和LVS等验证

三、实验使用软件环境、硬件设备

PC电脑Windows XP平台,Cadence软件

四、实验步骤

1,打开Cadence软件;

2,电路设计;

3,计算Mos管数值;

4,电路仿真;

5,

五、实验结果

1.实现要求目标

2.实验电路图:

3.实验仿真图:

六、实验心得体会

掌握了集成电路设计的一般步骤,熟悉Cadence软件的使用,了解简单的水位控制器设计原理。

通过这次课程设计,进一步的掌握了数字集成电路设计的基础知识与实际应用。

数字ic设计项目总结

数字ic设计项目总结

数字IC设计项目总结

一、项目概述

项目名称:数字IC设计项目

项目成员:XXX、XXX、XXX

项目时间:XXXX年XX月-XXXX年XX月

项目目标:设计一款高性能的数字IC,以满足市场需求,提高产品竞争力。

二、项目实施过程

1. 需求分析:对市场需求进行深入调研,明确产品性能要求、应用场景和目标客户群体。

2. 架构设计:根据需求分析结果,设计数字IC的架构,包括逻辑功能模块、接口、时钟系统等。

3. 逻辑设计:根据架构设计,进行逻辑电路设计和仿真,确保逻辑功能的正确性。

4. 物理设计:对数字IC进行物理布局和布线,优化芯片面积和性能。

5. 可靠性测试:对数字IC进行各种环境下的可靠性测试,确保产品质量的可靠性。

6. 调试与优化:对数字IC进行功能和性能调试,优化产品性能。

三、项目成果

1. 完成数字IC设计,包括逻辑电路、物理布局和布线等。

2. 通过可靠性测试,确保产品质量的可靠性。

3. 与市场需求对接,提高产品竞争力。

四、问题与解决方案

1. 问题:在进行物理设计时,发现芯片面积较大,不符合公司要求。

解决方案:优化逻辑电路设计,减少芯片面积。

2. 问题:在进行可靠性测试时,发现产品存在一些功能缺陷。

解决方案:对逻辑电路进行重新仿真和调试,修复缺陷。

五、经验与教训

1. 在项目开始阶段,应充分了解市场需求,明确产品性能要求和应用场景。

2. 在设计过程中,应注重团队沟通和协作,确保项目进度的顺利进行。

3. 在调试和优化阶段,应不断反思和总结经验教训,提高设计水平。

《数字芯片设计实训》实验指导书

数字芯片设计实训实验指导书编写人:许一男审核人:金永镐延边大学工学院电子信息通信学科目录一、基础实验部分实验一Quartus Ⅱ软件安装与测试 (11)实验二全加器的Verilog HDL程序设计与FPGA应用 (11)实验三串行进位加法器的Verilog HDL程序设计与FPGA应用 (11)实验四选择器的Verilog HDL程序设计与FPGA应用 (11)实验五译码器的Verilog HDL程序设计与FPGA应用 (11)实验六编码器的Verilog HDL程序设计与FPGA应用 (11)实验七比较器的Verilog HDL程序设计与FPGA应用 (11)二、选做实验部分实验八移位器的Verilog HDL程序设计与FPGA应用 (11)实验九存储器的Verilog HDL程序设计与FPGA应用 (11)实验十串行/并行转换器的Verilog HDL程序设计与FPGA应用 (11)实验十一触发器的Verilog HDL程序设计与FPGA应用 (11)实验十二计数器的Verilog HDL程序设计与FPGA应用 (11)三、创新实验部分实验十三时序电路系统设计与FPGA应用 (11)实验十四ModelSim软件安装与测试 (11)实验十五FPGA设计与逻辑分析仪的应用 (11)实验一Quartus Ⅱ软件安装与测试一、实验目的1. 熟悉Quartus Ⅱ软件的安装。

2. 熟悉ADS软件的安装。

二、实验仪器及材料1. 电脑2. Quartus Ⅱ软件3. ADS软件三、预习要求1. 预习半加器的工作原理。

2. 预习半加器的Verilog HDL程序设计。

四、实验内容首先总体上介绍数字芯片设计的软件环境,然后按照以下顺序来进行安装软件-《Quartus Ⅱ软件安装、设置license、安装ADS软件》。

软件安装结束之后设计半加器的Verilog HDL程序,并进行功能仿真和时序仿真。

内容1. Quartus Ⅱ软件安装(1)在D盘里创建“quartus40”的文件夹,并在此文件夹里安装Quartus Ⅱ软件的相关程序;(2)执行“install”,并进行安装Quartus Ⅱ软件。

关于芯片的实验报告(3篇)

第1篇一、实验目的1. 了解集成电路封装知识,熟悉集成电路封装类型。

2. 掌握集成电路工艺流程,了解其基本原理。

3. 掌握化学去封装的方法,为后续芯片检测和维修提供技术支持。

二、实验仪器与设备1. 烧杯、镊子、电炉2. 发烟硝酸、浓硫酸、芯片3. 超纯水、防护手套、实验台等三、实验原理与内容1. 传统封装(1)塑料封装:双列直插DIP、单列直插SIP、双列表面安装式封装SOP、四边形扁平封装QFP、具有J型管脚的塑料电极芯片载体PLCC、小外形J引线塑料封装SOJ。

(2)陶瓷封装:具有气密性好、高可靠性或大功率的特点。

2. 集成电路工艺(1)标准双极性工艺(2)CMOS工艺(3)BiCMOS工艺3. 去封装(1)陶瓷封装:一般用刀片划开。

(2)塑料封装:化学方法腐蚀,沸煮。

四、实验步骤1. 打开抽风柜电源,打开抽风柜。

2. 将要去封装的芯片(去掉引脚)放入有柄石英烧杯中。

3. 戴上防护手套,确保实验安全。

4. 将烧杯放入电炉中,加入适量的发烟硝酸,用小火加热20~30分钟。

5. 观察芯片表面变化,待芯片表面出现裂纹后,取出烧杯。

6. 将烧杯放入冷水中冷却,防止芯片损坏。

7. 取出芯片,用镊子轻轻敲打芯片,使封装材料脱落。

8. 清洗芯片,去除残留的化学物质。

9. 完成实验。

五、实验结果与分析1. 实验结果通过本次实验,成功去除了芯片的封装材料,暴露出芯片内部结构,为后续检测和维修提供了便利。

2. 实验分析(1)实验过程中,严格控制了加热时间和温度,避免了芯片损坏。

(2)化学去封装方法操作简便,成本低廉,适用于批量处理。

(3)本次实验成功掌握了化学去封装的基本原理和操作步骤,为后续芯片检测和维修提供了技术支持。

六、实验总结1. 本次实验使我们对集成电路封装知识有了更深入的了解,熟悉了不同封装类型的特点。

2. 掌握了化学去封装的基本原理和操作步骤,为后续芯片检测和维修提供了技术支持。

3. 通过本次实验,提高了我们的实验操作能力和团队协作精神。

大连理工大学数字集成电路实验报告

大连理工大学本科实验报告课程名称:数字集成电路设计学院(系):电子信息与电气工程学部专业:集成电路设计与集成系统班级:学号:学生姓名:2017年05月04日一、实验目的利用Cadence icfb工具对CMOS反相器进行电路设计、仿真。

以及进行数字激励—数模混合仿真。

并对CMOS反相器进行版图设计和版图验证。

二、实验内容1、电路设计、仿真(1)添加单元,完成CMOS反相器电路图的设计。

如下图所示。

图1 CMOS反相器电路图(2)按照步骤Check成功后,生成单元供调用。

生成单元结果如下图所示。

图2 CMOS反相器生成单元图(3)建立测试平台tb—testbench,调入单元,并加入电源、激励,建立仿真环境,开始仿真。

图3 CMOS反相器反正测试电路图图4 CMOS反相器仿真波形图通过仿真波形图可以看到,该电路逻辑符合反相器理论逻辑,电路设计正确。

波形测量,测量延迟时间。

测量结果如下图所示。

图5 波形测量结果图2、版图设计及验证(1)从电路产生版图,利用Cadence icfb工具画出CMOS反相器的版图。

设计版图如下图所示。

图6 CMOS反相器版图(2)版图验证,按照实验步骤进行设置,进行DRC验证,验证结果如下图所示。

通过验证结果可以看到,设计正确。

图7 DRC验证结果(3)Lvs:Layout与schematic的一致性检查,按照实验步骤进行设置,Lvs验证结果如下图所示。

通过验证结果可以看到结果正确。

图8 Lvs验证结果三、实验中遇到的困难以及解决方法在电路设计中,Check后存在错误,经过观察发现,PMOS和NMOS的B极没有正确的接到VDD和GND,通过添加调整后,电路设计正确,通过仿真,测试波形正确。

在版图设计验证时,进行DRC验证,发现存在错误。

错误结果如下图所示。

可以看到错误是contact without metall,通过按照错误提示调整版图,最终版图验证正确。

图9 DRC验证错误结果四、实验体会通过本次实验,学会了利用Cadence icfb工具对CMOS反相器进行电路设计、仿真,并对CMOS反相器进行版图设计和版图验证。

IC设计实践

《IC设计实践》实验报告IC设计实践专业:集成电路班级:电子0 6 0 4学号:200681131姓名:高丕龙目录1 设计目标 (2)2 设计平台 (2)3 电路原理图和前仿真 (3)4 电路板图设计 (12)5 寄生参数提取和后仿真 (15)6 学习心得 (19)一、设计目标本次IC设计实践采用Mentor Graphics 0.13um工艺库设计两级运算放大器,指标如下:电源电压 working voltage:VDD=3.3V;直流增益 gain at dc:Av>1000(60dB);单位增益带宽 gain-bandwidth:GB>1MHz;共模输入电压范围 input common-mode range:CMR=0.8~2.3V;输出电压范围 output voltage range:Vout range=0.6~2.8V;压摆率 slew rate:SR>2V/us;功耗 power dissipation:P<2mW;负载电容:CL=3pF;沟道长:channel length>0.35um。

偏置电路差分输入级单管放大级图一,电路设计原理图二、设计平台Mentor Graphics软件及其0.13um工艺库三.电路原理图和前仿真电路结构与工作原理该两级运放由一个查分放大器和一个共源MOSFET放大器加上输入偏置电路组成。

差分放大器(M1M2M5)将差模输入电压转换为差模电流,此差模电流作用在电流镜负载(M3M4)上恢复成差模电压。

在静态条件下,即无差模信号时,M1M2两管中电流相等且电流和为Iss,即电流漏M5中的电流。

M1电流决定M3电流,理想情况下,M4中应该产生这个电流的镜像。

若Vgs1=Vgs2,M1M2匹配,则M1M2管中电流相等,因此电流源M4到M2的电流应该等于M2需要电流,是输出电流在忽略负载情况下为0。

若电流不相等,假设负载电阻无穷大,电流只在M2和M4自身电阻中流动,若Vgs1>Vgs2,相对于Id2,Id1将增大,意味着Id3和Id4增加,但当Vgs1>Vgs2时,Id2减小,因此唯一能让电路平衡的方法是输出电流为正且输出电压增加。

数字系统电路实验报告(3篇)

第1篇一、实验目的1. 理解数字系统电路的基本原理和组成。

2. 掌握数字电路的基本实验方法和步骤。

3. 通过实验加深对数字电路知识的理解和应用。

4. 培养学生的动手能力和团队合作精神。

二、实验原理数字系统电路是由数字逻辑电路构成的,它按照一定的逻辑关系对输入信号进行处理,产生相应的输出信号。

数字系统电路主要包括逻辑门电路、触发器、计数器、寄存器等基本单元电路。

三、实验仪器与设备1. 数字电路实验箱2. 数字万用表3. 示波器4. 逻辑分析仪5. 编程器四、实验内容1. 逻辑门电路实验(1)实验目的:熟悉TTL、CMOS逻辑门电路的逻辑功能和测试方法。

(2)实验步骤:1)搭建TTL与非门电路,测试其逻辑功能;2)搭建CMOS与非门电路,测试其逻辑功能;3)测试TTL与门、或门、非门等基本逻辑门电路的逻辑功能。

2. 触发器实验(1)实验目的:掌握触发器的逻辑功能、工作原理和应用。

(2)实验步骤:1)搭建D触发器电路,测试其逻辑功能;2)搭建JK触发器电路,测试其逻辑功能;3)搭建计数器电路,实现计数功能。

3. 计数器实验(1)实验目的:掌握计数器的逻辑功能、工作原理和应用。

(2)实验步骤:1)搭建同步计数器电路,实现加法计数功能;2)搭建异步计数器电路,实现加法计数功能;3)搭建计数器电路,实现定时功能。

4. 寄存器实验(1)实验目的:掌握寄存器的逻辑功能、工作原理和应用。

(2)实验步骤:1)搭建4位并行加法器电路,实现加法运算功能;2)搭建4位并行乘法器电路,实现乘法运算功能;3)搭建移位寄存器电路,实现数据移位功能。

五、实验结果与分析1. 逻辑门电路实验通过搭建TTL与非门电路和CMOS与非门电路,测试了它们的逻辑功能,验证了实验原理的正确性。

2. 触发器实验通过搭建D触发器和JK触发器电路,测试了它们的逻辑功能,实现了计数器电路,验证了实验原理的正确性。

3. 计数器实验通过搭建同步计数器和异步计数器电路,实现了加法计数和定时功能,验证了实验原理的正确性。

数字IC实验NOR VTC

哈尔滨理工大学软件学院数字IC实验报告班级集成12-2专业集成电路设计与集成系统姓名王亮学号12140202272014年11月26日Lab 4 NOR VTC 目的:通过对NOR的VTC曲线的仿真,掌握NOR的VTC的原理。

内容: 1. 使用0.18um的工艺,写出2输入或非门的HSPICE网表,仿真出VTC曲线。

2. 仿真其逻辑功能(Additional网表:* NOR Gate with one input B tied to Vdd,input A switching*Set supply and library.param Supply=1.8 *for 0.18 technology.include 'c:\lib\180nm_bulk.l'.opt scale=0.1u *Set lambda*Power supply.global Vdd GndVdd Vdd Gnd 'Supply' *Supply is set by .lib call*Top level simulation netlistmpa x Ain Vdd Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4 mpb out Bin x Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4 mna out Bin Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mnb out Ain Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 Vin Ain Gnd 'Supply'*Simulation.dc Vin 0 'Supply' 'Supply/50'.plot dc V(out).end单端输入A* NOR Gate with one input B tied to Vdd,input A switching *Set supply and library.param Supply=1.8 *for 0.18 technology.include 'c:\lib\180nm_bulk.l'.opt scale=0.1u *Set lambda*Power supply.global Vdd GndVdd Vdd Gnd 'Supply' *Supply is set by .lib call*Top level simulation netlistmpa x Ain Vdd Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4mpb out Bin x Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4mna out Bin Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4mnb out Ain Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4Vin Bin Gnd 'Supply'*Simulation.dc Vin 0 'Supply' 'Supply/50'.plot dc V(out).end单端输入B*NOR Gate with one input B tied to Vdd,input A switching *Set supply and library.param Supply=1.8 *for 0.18 technology.include 'c:\lib\180nm_bulk.l'.opt scale=0.1u *Set lambda*Power supply.global Vdd GndVdd Vdd Gnd 'Supply' *Supply is set by .lib call*Top level simulation netlistmpa x in Vdd Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4mpb out in x Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4mna out in Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4mnb out in Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4*Simulation.dc Vin 0 'Supply' 'Supply/50'.plot dc V(out).endA、B绑定同时输入仿真结果:或非门的逻辑关系:(网表)*NOR Gate*Set supply and library.temp 25.include 'c:\lib\180nm_bulk.l' *for 0.18 technology.opt scale=0.1u *Set lambda*Power supply.global Vdd GndVdd Vdd Gnd 'Supply' *Supply is set by .lib call*Top level simulation netlistmpa x Ain Vdd Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4 mpb out Bin x Vdd PMOS l=2 w=16 ad=20 pd=4 as=20 ps=4 mna out Bin Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4 mnb out Ain Gnd Gnd NMOS l=2 w=4 ad=20 pd=4 as=20 ps=4Va Ain Gnd pulse 'Supply' 0 2ns 50ps 50ps 4.0ns 8nsVb Bin Gnd pulse 'Supply' 0 1ns 100ps 100ps 2ns 4ns*Simulation.tran 100ps 40ns.plot tran V(out).end仿真结果:。

数字电路实验的实验报告(3篇)

第1篇一、实验目的1. 理解和掌握数字电路的基本原理和组成。

2. 熟悉数字电路实验设备和仪器的基本操作。

3. 培养实际动手能力和解决问题的能力。

4. 提高对数字电路设计和调试的实践能力。

二、实验器材1. 数字电路实验箱一台2. 74LS00若干3. 74LS74若干4. 74LS138若干5. 74LS20若干6. 74LS32若干7. 电阻、电容、二极管等元器件若干8. 万用表、示波器等实验仪器三、实验内容1. 基本门电路实验(1)验证与非门、或非门、异或门等基本逻辑门的功能。

(2)设计简单的组合逻辑电路,如全加器、译码器等。

2. 触发器实验(1)验证D触发器、JK触发器、T触发器等基本触发器的功能。

(2)设计简单的时序逻辑电路,如计数器、分频器等。

3. 组合逻辑电路实验(1)设计一个简单的组合逻辑电路,如4位二进制加法器。

(2)分析电路的输入输出关系,验证电路的正确性。

4. 时序逻辑电路实验(1)设计一个简单的时序逻辑电路,如3位二进制计数器。

(2)分析电路的输入输出关系,验证电路的正确性。

5. 数字电路仿真实验(1)利用Multisim等仿真软件,设计并仿真上述实验电路。

(2)对比实际实验结果和仿真结果,分析误差原因。

四、实验步骤1. 实验前准备(1)熟悉实验内容和要求。

(2)了解实验器材的性能和操作方法。

(3)准备好实验报告所需的表格和图纸。

2. 基本门电路实验(1)搭建与非门、或非门、异或门等基本逻辑电路。

(2)使用万用表测试电路的输入输出关系,验证电路的功能。

(3)记录实验数据,分析实验结果。

3. 触发器实验(1)搭建D触发器、JK触发器、T触发器等基本触发电路。

(2)使用示波器观察触发器的输出波形,验证电路的功能。

(3)记录实验数据,分析实验结果。

4. 组合逻辑电路实验(1)设计4位二进制加法器电路。

(2)搭建电路,使用万用表测试电路的输入输出关系,验证电路的正确性。

(3)记录实验数据,分析实验结果。

IC版图设计实训报告

IC版图设计实训报告班级:实训科目:姓名:学号:实训时间:IC版图设计实训报告一、实训目的1.熟练使用Cadence工具设计一个CMOS与非门线路图和版图。

2.学习Cadence 中原理图设计与分析。

3.熟练掌握静态CMOS逻辑电路设计原理。

4.掌握CMOS与非门版图结构,集成电路工艺与版图的图层关系。

5.掌握Cadence仿真环境,完成与非门的仿真。

二、实训要求1.熟悉Cadence的工作环境。

2.能够熟练使用Cadence工具设计CMOS与非门/或非门等基本电路。

3.熟记Cadence中的快捷操作。

比如说“W”是连线的快捷键。

4.能够看懂其他人所画的原理图以及仿真结果,并进行分析等。

三、实训设备与工具1.计算机一台。

2.Cadence 集成电路设计软件。

四、实训步骤1.按照正确的方法打开软件。

2.确定工艺规则。

3.绘制与非门版图。

4.加入工作电源进行分析。

5.记录结果并进行LVS比较。

五、实训内容首先正确的启动软件,新建一个原理图文件。

然后根据给出的电路图在软件上正确绘制原理图。

其原理图如下:把画好的原理图保存好,然后再进行检查是否有错。

如果有错根据报错进行修改,没错就直接进行下一步模拟仿真,观察仿真结果是否真确。

其仿真图如下:接下来就是最后一道工序,把绘制好的原理图就行打包封装。

其封装图如下:六、实训心得通过这次实训使我们了解了Cadence软件的工作环境,并且能过进行一些基本的操作。

能够新建原理图文件并绘制原理图。

能够对电路的电学参数进行模拟,以确定电路图能够实现其电学功能。

并且通过此次实训使我们了解了与非门/或非门的基本数字电路。

还有就是了解了Cadence软件的一些快捷键的操作。

比如像“M”就是移动的原件快捷键。

“K”是标尺的快捷键。

如果选中原件然后按“Q”就是调出性能参数调节界面。

在画原理图的时候要细心,因为很容易漏连接线,或者参数没有调整等。

还有就是在选择电源和接地的时候注意选择正确的形式。

IC实习报告

实习报告课程名称实习设计报告题目名称 IC集成芯片设计学生学院材料与能源专业班级微电子(2)班学号学生姓名指导教师2015 年7 月25 日目录:前言 (1)正文 (3)第一部分——LINUX介绍与常用指令 (3)第二部分——VCS实验设计步骤简要说明 (5)实验一 (5)实验二 (7)实验三 (8)第三部分——DC实验设计步骤简要说明 (9)第四部分——ICC实验设计步骤简要说明 (17)一、给你的设计先创建一个Milkway library (17)二、加载网络表,TLU +:的约束和控制 (18)三、基本流程:设计规划 (20)四、布局 (20)五、CTS (21)六、布线 (21)第五部分——PT实验设计步骤简要说明 (22)实习总结: (24)前言:终于迎来了期盼已久的实习,毕业实习是每个大学生必须拥有的一段经历,它使我们在实践中了解社会,让我们学到了很多在课堂上根本就学不到的知识,受益匪浅,也打开了视野,增长了见识,使我认识到将所学的知识具体应用到工作中去,为以后进一步走向社会打下坚实的基础,只有在实习期间尽快调整好自己的学习方式,适应社会,才能被这个社会所接纳,进而生存发展。

刚进入单位的时候我有些担心,经历了一连串的实习之后,我努力调整观念,正确认识了单位和个人的地位以及发展方向,我相信只要我们立足于现实,改变和调整看问题的角度,锐意进取,在成才的道路上不断攀登,有朝一日,那些成才的机遇就会纷至沓来,促使我们成为社会公认的人才。

1、培训目的IC集成芯片设计的设计流程主要包括代码设计和验证VCS(Verilog Compiled Simulator)、前端设计与逻辑综合DC(Design Compiler)、后端实体设计ICC(IC Compiler)和时序验证PT(Prime Time)。

此次实习根据初学者的知识掌握程度合理地安排了实习的实习难度,也让实习生同学能够初步了解IC芯片设计的整个流程,充分的了解芯片设计每一阶段所需要掌握的基本知识和技能。

数电芯片实验报告

数电芯片实验报告一、实验目的本实验旨在通过实际操作,加深对数电芯片原理和应用的理解,掌握数电芯片的基本使用方法以及逻辑门电路的设计与实现。

二、实验设备与材料1. 数电实验箱2. 7400四路与非门芯片3. 7402四路与或门芯片4. 电压源5. 示波器6. 连线三、实验原理1. 与非门(NAND Gate)与非门是由两个与门级联后再接入反相器得到的,其操作规则为:只有所有输入都为高电平时,输出为低电平。

其真值表如下:A B OUT0 0 10 1 11 0 11 1 02. 或门(OR Gate)或门的操作规则为:只要有一个输入为高电平,输出即为高电平。

其真值表如下:A B OUT0 0 00 1 11 0 11 1 1四、实验步骤1. 准备工作调整实验箱上的电压源,使其输出电压为3V,并将其连接至芯片供电端。

2. 与非门实验将7400芯片插入实验箱上的插槽中,并将其中一个与非门的A、B端分别连接至两路开关,输出端接至一只LED灯,如图所示。

。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字集成电路设计

实验报告

实验名称二输入与非门的设计

一.实验目的

a)学习掌握版图设计过程中所需要的仿真软件

b)初步熟悉使用Linux系统

二.实验设备与软件

PC机,RedHat,Candence

三.实验过程

Ⅰ电路原理图设计

1.打开虚拟机VMware Workstation,进入Linux操作系统RedHat。

2.数据准备,将相应的数据文件拷贝至工作环境下,准备开始实验。

3.创建设计库,在设计库里建立一个schematic view,命名为,然后进入电路

图的编辑界面。

4.电路设计

设计一个二输入与非门,插入元器件,选择PDK库(xxxx35dg_XxXx)中的nmos_3p3、

pmos_3p3等器件。

形成如下电路图,然后check and save,如下图。

图1.二输入与非门的电路图

5.制作二输入与非门的外观symbol

Design->Create Cellview -> From Cellview,在弹出的界面,按ok后出现symbol Generation options,选择端口排放顺序和外观,然后按ok出现symbol编辑界面。

按照需

要编辑成想要的符号外观,如下图。

保存退出。

图2.与非门外观

6.建立仿真电路图

方法和前面的“建立schemtic view”的方法一样,但在调用单元时除了调用analogL 库中的电压源、(正弦)信号源等之外,将之前完成的二输入与非门调用到电路图中,如下图。

图3.仿真电路图

然后设置激励源电压输出信号为高电平为3.5v,低电平为0的方波信号。

7.启动仿真环境

在ADE中设置仿真器、仿真数据存放路径和工艺库,设置好后选择好要检测的信号在电路中的节点,添加到输出栏中,运行仿真得到仿真结果图。

图4.仿真结果图

Ⅱ版图设计

1.数据准备

2.建立设计库,然后建立一个layout view,tool选virtuso,然后进入版图编辑界

面

3.版图绘制

在版图编辑界面中,从LSW中选择图层,然后进行二输入与非门的版图绘制。

如下图所示。

图5.版图设计

Ⅲ.版图验证

1.采用DIVA做DRC验证

将divaDRC.rul拷贝到版图库中,然后在版图编辑界面选择需要进行DRC检查的复选项然后点击OK,在icfb的LOG窗口出现运行结果。

2.Debug

若版图存在错误:如最小宽度限制,最小间距限制等几何设计规则错误在LOG窗口会报错,版图编辑界面同时会标出错误的地方,按照提示修改错误再重做DRC验证直至没有错误出现,如下图所示。

图6.版图验证成功提示窗口

至此,二输入与非门的版图设计与验证已全部完成。