8人抢答器

八位多路抢答器

题目: 多路抢答器的设计与实现初始条件:本设计主要选用集成计数器、寄存器、脉冲发生器和必要的门电路等来实现。

要求用蜂鸣器和光电二极管作声光报警器件。

要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1周。

2、技术要求:1)同时供8名选手参赛,其编号分别是1到8,各用一个抢答按钮,按钮的编号与选手的编号相对应;给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。

2)抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管上显示出选手的编号,同时扬声器给出音响提示。

此外,要封锁输入电路,禁止其它选手抢答。

优先抢答选手的编号一直保持到主持人将系统清零为止。

3)抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30秒)。

当节目主持人启动“开始”键后,要求定时器立即进行减法计时,并用显示器进行显示,同时扬声器发出短暂的声响,声响持续时间0.5秒左右。

4)参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止。

5)如果定时抢答的时间已到,却没有选手抢答时,本次抢答无效,系统进行短暂的报警,并封锁输入电路,禁止选手超时后抢答,定时显示器上显示00。

目录摘要 (1)Abstract (2)1引言 (3)1.1 多路抢答器简介 (3)1.2 多路抢答器工作原理 (3)1.3 课程设计的目的 (4)2设计方案 (5)方案选择 (5)2.1抢答电路设计 (6)2.2计时电路设计 (7)2.3报警电路设计 (8)2.4时序控制电路设计 (9)3单元电路仿真 (10)3.1抢答电路 (10)3.2计时电路 (11)3.3报警电路 (13)4总结 (14)4.1课程设计中遇到的困难和不足 (14)4.2课程设计的收获 (14)5参考文献 (16)附录 (17)抢答器整体电路图 (17)整体电路图................................................................................................................... 错误!未定义书签。

八人智力竞赛抢答器

摘要本报告设计的八路智力竞赛抢答器电路主要采由74系列常用集成电路组成,涉及到触发器、编码器、加法器、译码器和RC电路组成的多谐振荡电路。

该抢答器具有基本的抢答功能,通过共阴极数码管显示选手的号码。

当一轮抢答开始后,首先抢答的人由触发器保持状态并阻止其他任何选手输入状态,此次设计的抢答器在选手输入信号后先经过D触发器,再经过优先编码器编码,所有选手没有优先级之分,真正做到比赛的公平公正性。

编码后的信号经过加法器后输出合适的的二进制码,再经过显示译码器的作用,驱动共阴极数码管显示抢答选手的编号。

主持人可以通过控制按钮结束本轮的抢答并可以从新开始下一轮抢答。

本次设计的抢答器运用74LS148上升沿D触发器记录第一个抢答人的状态;运用47LS279控制触发器的工作,从而使第一个抢答者的状态保持,而其他人无法再抢答;运用优先编码器编码加0001,输出合适的二进制数;最后采用BCD-显示选手编号。

关键词: 抢答器触发器编码器加法器显示译码器八人智力竞赛抢答器1、设计任务及要求:设计任务:设计一个8人竞赛抢答电路。

要求:1.1 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮1~ 8表示。

每个参赛者控制一个按钮,用按动按钮发出抢答信号。

1.2 设置一个系统清除和抢答控制开关,该开关由主持人控制。

1.3 抢答器具有锁存与显示功能。

竞赛开始后,先由主持人将“开始/清零”按键按下,然后先按动按钮的参赛者将被显示器显示出来,此后其他三人参赛者再按动按钮对电路不起作用。

优先抢答的参赛者编号将一直被显示直至主持人将系统清零。

另外,在主持人按下“开始/清零”键时,计时器开始计时,时间为三十秒,在规定的时间内,仍无人作答,系统将发出蜂鸣声示警,抢答结束。

2、实验原理:2.1 八人竞赛抢答器电路的总体设计方案2.2 工作原理当抢答比赛开始时,主持人按下“开始/清零”开关,接通电源,抢答器开始工作,定时器倒计时,如选手在规定的时间内抢答,则抢答器完成:优先判断、编号锁存、编号显示等一系列动作,当一轮抢答之后,定时器停止、禁止二次抢答。

PLC控制八路抢答器

控制要求1抢答器同时共8名选手或8个代表团比赛,分别用8个按钮SB1-SB8示2设置一个系统清除和抢答控制开关 S,该开关由主持人控制。

3抢答器具有锁存于显示功能。

即选手按动按钮,锁存相应的编号,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(30秒)。

当主持人启动“开始”键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间为0.5秒。

5参赛选手在设定时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时间,并保持到主持人将系统清除为止。

6如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答。

四设计梯形图程序0.01 0.00 CNTRD0 10.01 10.02 10.03 10.04 10.05 10.06 10.0710.0010.00根据系统控制0要求CN TR I/O 通0道0分配02设计弟形.64如下0510.06 10.070.01 0.00 CNTR0 0 10.01 10.°210.03 10.04 10.05 10.06 10.07 0.01 0.00 CNTR0 0 10.01 10.02 10.03 10.04 10.05 10.06 10.07段0 10.00-~0' 0.0刃0 切辟^00).。

0®0?100)110.03 10?°)5)4101.0605101.0706 10.07 0.02 八/CC _ J 屮・01U2 ] 10.01 10.00.00 CNTF0 0 10.00 10.02 10.03 10.04 10.05 10.06 10.07 10.01 210.010.U------ 00^ 0.00.006^;冊巳10).001000011 100013 1^02 11(0;04 10005 叫0706 10.07 0.03 0.00 CNTR0 0 10.00 10.01 10.03 10.04 10.05 10.06 10.07 1 0.04 0.00 CNTF0 0 10.00 10.01 10.02 10.04 10.05 10.06 0.04)5 0.00)0 10.0310.031W004 0.05 0.00 CNTF0 0 10.00 10.01 10.02 10.03 10.05 10.06 10.07 ~o M U NTFU U o M )oU H o H u H u fc^fc 曦10.04--- 10.06050.00 CNTR0010.00 10.01 10.02 10.03 10.04 10.06 10.07 ——.0^~^0圧1^0^04^0^40&404^01^10^够C" ——10.05 10071 .0610.0410015)7 ----- . 0.00 CNTR00 10.00 10.01 10.02 10.03 10.04 CJTRDO 10.00 10.01 10.02 10.03 10.04 10.05 0.00 CNTR0010.00 10.01 10.02 10.03 10.04 10.05 10'. 0610.060.08 0^8070.01 10.07O.OO CNTR0010.00 10.01 10.02 10.03 10.04 10.05 10.07 」(0|0^ 0.00 0.00CMPXC MP Xi 1d #010100 #00003.140706 10.007CNTR7CNTR00 00.00 0.0000#3 0 4 410.0110.0210.0310.0410.0510.0610.07CMPX 10 11 #0000CNTR 00 #3 0#3^0 25353.150.00卜253.15200.00 200.0010.000.00MOV#3 00.00 253.15200.00。

八人数字抢答器

目录一、设计任务与要求二、设计目的三、抢答器的系统概述3.1 抢答器的工作原理3.2 抢答器的系统需求分析3.3 抢答器的工作流程3.4 抢答器的工作过程四、抢答器的电路设计4.1 抢答器的总体结构4.2 优先判断与编号锁存电路五、抢答器的单元设计电路5.1 抢答器设计中的优先编码电路5.2 抢答器设计中的定时电路5.3 抢答器设计中的报警电路5.4 抢答器设计中的时序控制电路5.5 七段显示译码器与数码管5.6 抢答器的优点及组成六、总结与体会参考文献一、设计任务与要求1. 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2. 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3. 抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如30秒)。

当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

5. 参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

二、设计目的通过课程设计,对数字逻辑的基本内容有进一步的了解,特别是时序逻辑电路的设计。

能把上学期学到的数字逻辑理论知识进行实践,操作。

在提高动手能力的同时对常用的集成芯片有一定的了解,在电路设计方面有感性的认识。

而且在进行电路设计的时候遇到问题,通过独立的思考有利于提高解决问题的能力。

在经过课程设计后,更明白数字逻辑电路设计的一般方法,以及在遇到困难怎么排除问题。

三、抢答器的系统概述3.1抢答器的工作原理简介如图3-1所示为抢答器的结构框图,它由主体电路和扩展电路两部分组成。

电子技术课程设计8路抢答器设计

电子技术课程设计8路抢答器一、设计任务与要求1. 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2. 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3. 抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED 数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

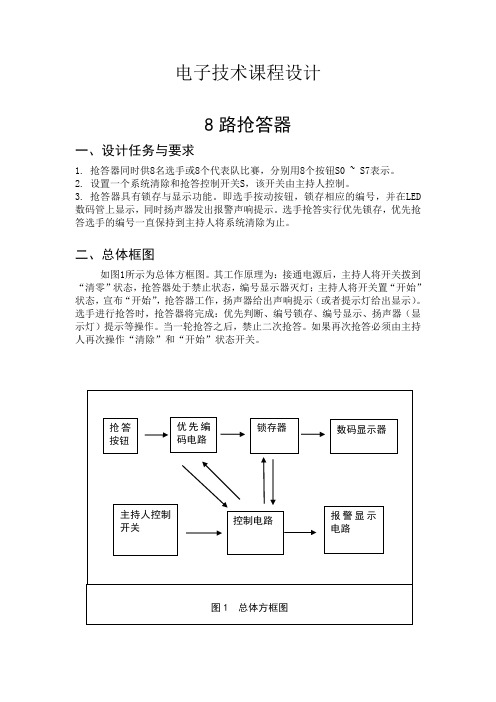

二、总体框图如图1所示为总体方框图。

其工作原理为:接通电源后,主持人将开关拨到“清零”状态,抢答器处于禁止状态,编号显示器灭灯;主持人将开关置“开始”状态,宣布“开始”,抢答器工作,扬声器给出声响提示(或者提示灯给出显示)。

选手进行抢答时,抢答器将完成:优先判断、编号锁存、编号显示、扬声器(显示灯)提示等操作。

当一轮抢答之后,禁止二次抢答。

如果再次抢答必须由主持人再次操作“清除”和“开始”状态开关。

上面的总体框图是我认为的最佳方案。

具体的说明:抢答器按钮就是输入一些高低电平信号,此实验是低电平有效。

优先编码电路用来把输入的高低电平信号编码,74LS148优先编码器及8—3编码器,输出3位2进制数,以代表不同的低电平信号。

锁存器用D触发器,因为D触发器结构和功能都比较简单,方便使用。

D 触发器使用4个,第四个除用来输出2进制数的最高位外,还用于控制信号的锁定,即触发或锁定触发器的工作状态。

数码显示器用DCD—七段数码显示管,即有4个输入信号的管子,能表示0到9十个数,而且输入的二进制数正好和十进制数一一对应。

主持人控制开关就是一个开关,用来清零和开始工作。

控制电路比较复杂,除了第四个触发器和主持人的开关外,还需要8个抢答器按钮组成的8输入与非门和第四个触发器用一个与门共同组成一个控制电路来控制信号的传输和锁定。

报警显示电路,由于没有报警器,所以选择一个LED灯来表示信号的锁定。

为了使更明显一些,给LED灯加了个连续脉冲信号,以使灯能够按我们需要的频率一闪一闪。

基于触发器设计的8人抢答器(带作弊功能)

基于触发器设计的8人抢答器(带作弊功能)一、本抢答器具有以下功能:1:抢答器同时供8名选手或8个代表队比赛,分别用8个开关按钮K0~ K7表示。

设置一个系统复位控制开关S,该开关由主持人控制。

2.抢答器具有封锁功能,即一旦有选手按动开关按钮,此选手的抢答指示灯发亮,可以优先抢答,其他选手按动开关后抢答指示灯将不予反应,优先抢答选手抢答指示灯发亮一直保持到主持人将系统复位为止。

3:本抢答器具有内部选手抢答作弊功能。

二、利用Multisim11.0绘制的具体电路图:说明:由于元件较多,这里只绘制了四个触发器,8人抢答器可在此电路的基础上增加4只触发器。

4只触发器为上升沿触发的边沿JK触发器。

如果文档中电路图较小,不易观察,可以将电路图片提取出来,放大观看。

三:电路分析:1:电路实际使用四只JK触发器,J、K端接在一起并接高电平,由Q*=JQ’+K’Q知Q*=Q’,故由JK触发器构成T’触发器,当T’触发器的输入由低电平转换为高电平时,相当于输入一个上升沿时钟信号,输出将为高电平,发光二极管发亮。

2:功能实现:主持人复位清零后,Q1~Q4输出为“0000”,4只发光二极管灭,或非门输出为“1”,四个与门均由选手开关控制。

抢答前,4个与门输出为“0000”,有抢答时,假定选手1抢答,则该与门输出一瞬间的“1”,JK触发器1得到上升沿触发,由Q*=Q’,输出反转,由“0”→“1”,然后或非门输出“0”,各JK 触发器的时钟输入为“0”,各用户被封锁,注意此过程时间极短,远远小于其他选手按下开关的反应时间。

然后直到主持人异步清零(跟各时钟信号无关),使Q1~Q4重新等于“0000”才能重新让JK触发器工作。

3:一个重要细节是:JK触发器的输出是与上升沿时钟信号紧密相关的,而不是电平信号控制的,不能说输入为“0”时输出就一定为“1”,或是输入为“1”时输出就一定为“0”,也就是说触发器工作方式为边沿触发方式。

八位竞赛抢答器

摘要抢答器的设计是基于VHDL语言,可以支持八个选手抢答,抢答器不仅具有倒计时功能,具有计数功能,还准备了重置的功能。

抢答器主要包含第一判断电路模块、倒计时电路模块、计分电路模块、显示电路模块以及位选择电路模块。

参赛选手如果成功抢答,则开始倒计时,答对者可以得到相应的分数,答错不扣分。

通过利用QUARTUS 软件完成相应的底层代码编写,用这些底层的模块来构建顶层模块,以及对顶层模块仿真、编译,以实现我们所需要的功能。

关键字:抢答器;EDA;VHDL;FPGADesign of 8 bit contest Responder based on FPGAAbstractResponder this design is based on VHDL language, supporting eight players responder.Responder has not only the function of the countdown has counting comprises a first judgment circuit module,coutdown circuit module, scoringmodule, display circuit module and a selection circuit module. If the contestants are successful to require the answer firstly, then the responder will start the countdown, you can get the corresponding scores, wrong answers are not penalized. By using the QUARTUS software to complete the underlying code written by the corresponding, the underlying model to construct the top module, as well as the top module, compiled simulation, in order to realize the functions we need.Keywords:Responder; EDA; VHDL; FPGA目录摘要 (I)Abstract (II)第一章绪论 (3)1.1 引言 (3)1.2 电子抢答器研究的背景与意义 (3)1.3 系统设计要求 (4)第二章电子抢答器总体设计方案 (5)2.1 系统总体方案设计 (5)2.2 主控芯片简介 (5)2.2.1 FPGA和CPLD器件 (5)2.2.2 可编程逻辑器件分类 (6)2.2.3 FPGA的基本结构 (6)2.3 EDA技术 (7)2.4 VHDL (8)2.4.1 关于VHDL (8)2.4.2 VHDL语言程序结构 (8)2.4.3 VHDL语言描述方式 (8)第三章电子抢答器的具体设计方案 (9)3.1 系统具体方案设计 (10)3.2 主要模块设计 (11)3.2.1 第一判断电路 (11)3.2.2 计分电路 (12)3.2.3 倒计时电路 (13)3.2.4 显示电路 (13)3.2.5 位选选择电路 (14)第四章电子抢答器系统仿真与分析 (15)4.1 系统总原理图分析与仿真 (15)4.2 倒计时模块分析与仿真 (17)4.3 判断电路模块分析与仿真 (17)4.4计分模块分析与仿真 (18)结束语 (18)致谢............................................... 错误!未定义书签。

8位竞赛抢答器课程设计

目录1. 原理分析(by 张潇) (2)1.1 设计任务 (2)1.2 性能指标 (2)1.3 工作原理 (2)2. 方案选择(by 张潇) (3)2.1 方案设定 (3)2.2 方案比较 (3)2.3 方案选择 (3)3. 电路原理图绘制及仿真(by 王倩) (3)3.1 所需元器件型号及数量 (3)3.2 电路原理图 (4)3.3 电路仿真结果 (5)4. Pcb图绘制(by 朱文广) (5)4.1 pcb绘制步骤 (5)4.2 pcb绘制原则 (5)4.3 8路抢答器pcb图 (7)5. 综合调试(by 朱文广) (7)5.1 软件调试 (7)5.2 硬件调试 (9)6. 总结(by 王倩) (10)附录1:电路仿真图 (11)附录2: 8路抢答器完整程序 (12)1.1 设计任务以单片机为核心,设计一个8位竞赛抢答器,同时供8名选手或8个代表队比赛。

设置一个系统清除和抢答控制开关S,开关由主持人控制。

抢答器具有锁存与显示功能。

即选手按按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

抢答器具有定时抢答功能,且一次抢答的时间可由主持人设定。

参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

1.2 性能指标电源电压:直流5V±10%选手组数:2-8组初始抢答倒计时:20s初始回答倒计时:30s倒计时范围:1-99s可设倒计时提示时间:最后5s1.3 工作原理八路数字抢答器原理框图如图1所示,其工作原理为:接通电源后,主持人未按下开始抢答,抢答器处于禁止状态,数码管显示“----”;主持人宣布“开始”同时按下开始抢答按键,抢答倒计时开始计时,扬声器给出声响提示。

选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示、扬声器提示。

八位抢答器课程设计

八位抢答器课程设计一、课程目标知识目标:1. 学生理解抢答器的基本工作原理,掌握其电路组成及功能。

2. 学生了解数字电路基础知识,并能运用到抢答器的设计中。

3. 学生掌握抢答器程序设计的基本方法,能运用所学知识分析并解决实际问题。

技能目标:1. 学生能独立完成抢答器的电路搭建,提高动手实践能力。

2. 学生能通过编程实现抢答器的功能,培养编程思维和解决问题的能力。

3. 学生具备团队协作能力,能在小组合作中发挥个人优势,共同完成抢答器的设计与制作。

情感态度价值观目标:1. 学生培养对电子技术的兴趣,激发创新意识。

2. 学生在学习过程中,养成积极思考、勇于探索的良好习惯。

3. 学生通过小组合作,培养沟通协调能力和团队精神,树立集体荣誉感。

课程性质:本课程为信息技术与电子技术的结合课程,注重实践操作和团队合作。

学生特点:八年级学生对电子技术有一定的基础,好奇心强,具备一定的动手能力和合作意识。

教学要求:结合学生特点,以实践为主,引导学生主动探究,注重培养学生的创新精神和实践能力。

将课程目标分解为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. 数字电路基础知识:介绍抢答器中涉及的逻辑门电路、触发器等基本元件,对应教材第3章相关内容。

- 逻辑门电路原理与功能- 触发器种类及其应用2. 抢答器电路设计与搭建:讲解抢答器电路原理,引导学生进行电路搭建,对应教材第4章相关内容。

- 抢答器工作原理- 电路元件选择与连接- 抢答器电路搭建与调试3. 抢答器程序设计:教授编程基础知识,指导学生进行抢答器程序设计,对应教材第5章相关内容。

- 编程语言基础- 程序流程图设计- 抢答器程序编写与调试4. 抢答器功能实现与优化:培养学生解决问题和团队协作能力,对应教材第6章相关内容。

- 抢答器功能测试与优化- 团队合作与分工- 项目总结与展示教学大纲安排:第一周:数字电路基础知识学习,了解逻辑门电路和触发器原理。

第二周:抢答器电路设计与搭建,动手实践电路连接与调试。

八路抢答器设计说明书 精品

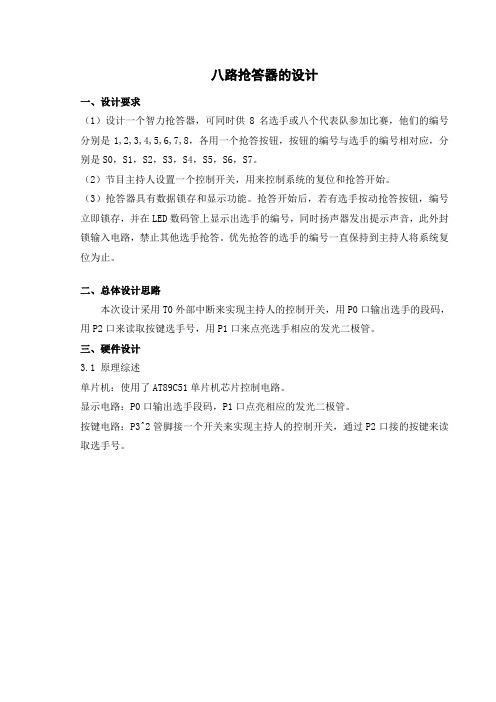

八路抢答器的设计一、设计要求(1)设计一个智力抢答器,可同时供8名选手或八个代表队参加比赛,他们的编号分别是1,2,3,4,5,6,7,8,各用一个抢答按钮,按钮的编号与选手的编号相对应,分别是S0,S1,S2,S3,S4,S5,S6,S7。

(2)节目主持人设置一个控制开关,用来控制系统的复位和抢答开始。

(3)抢答器具有数据锁存和显示功能。

抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管上显示出选手的编号,同时扬声器发出提示声音,此外封锁输入电路,禁止其他选手抢答。

优先抢答的选手的编号一直保持到主持人将系统复位为止。

二、总体设计思路本次设计采用T0外部中断来实现主持人的控制开关,用P0口输出选手的段码,用P2口来读取按键选手号,用P1口来点亮选手相应的发光二极管。

三、硬件设计3.1 原理综述单片机:使用了AT89C51单片机芯片控制电路。

显示电路:P0口输出选手段码,P1口点亮相应的发光二极管。

按键电路:P3^2管脚接一个开关来实现主持人的控制开关,通过P2口接的按键来读取选手号。

图3.1 硬件框图3.2 元器件清单3.3 硬件原理图图3.2 硬件原理图四、软件设计4.1 程序流程图图4.1 主程序流程图4.2 程序及注释#include<reg51.h> //包含头文件REG51.H #define uchar unsigned char#define uint unsigned int //数据类型的宏定义uchar code seg7[9]={0xff,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80}; //7段数码管0-8断码uchar act[9]={0xff,0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f}; //低电平有效的位码uchar num; //宏定义全局变量num bit bdata start; //定义开始按键start sbit bz=P3^3; //定义P3.3为bz//延时函数*********************************************************** void delay(uint k){uint i,j;for(i=0;i<k;i++){for(j=0;j<121;j++){;}}}//蜂鸣器*********************************************************void buzzer(void){while(1){bz=~bz;delay(10);}}//外中断0 ************************************************************ void EA_INT0() interrupt 0 //定义函数名为EA_INT0的T0外中断服务函数,中断号为0 {uchar in=1; //定义in=1start=!start; //start取反if(start==1) //判断是否开始抢答{while(in) //循环{P2=act[0]; //初始化P2if(P2!=0xff) //判断有无选手按下{delay(10); //延时确定有选手按下for(num=1;num<9;num++) //判断选手号{if(P2==act[num]) //读取选手号{bz=1;in=0;break;} //停止循环}}}}else{num=0;P3=0xff;bz=0;}}//******************************************************************************* void main(void) //主函数{ start=0; //初始化startP0=seg7[0]; //初始化段码P1=act[0]; //初始化发光二级管bz=0; //初始化蜂鸣器EX0=1; //允许外中断T0IT0=1; //外中断T0设为边沿触发EA=1; //开启总中断while(1) //无限循环{P0=seg7[num]; //P0输出段码P1=act[num]; //点亮相应的二极管}}五、软硬件调试5.1 软硬件仿真环境设置1)Keil 与Proteus连接连接开始必须在proteus安装目录下VDM51.dll文件复制到Keil安装目录的\C51\BIN 目录中,但新版本中没有,所以必须下载安装补丁vdmagdi.exe,则在Keil 安装目录的 \C51\BIN 目录中有文件:VDM51.dll2)修改keil安装目录下 Tools.ini文件用记事本(其它的编辑软件也可以,如Ultra Edit)打开Keil 根目录下的TOOLS.INI 文件,在[C51] 栏目下加入TDRV3=BIN\VDM51.DLL ("Proteus VSM Monitor-51 Driver" ) ,其中“TDRV3”中的“3”要根据实际情况写,不要和原来的重复。

8路智能抢答器

一、作品介绍1、基本功能①抢答器同时供8名选手,分别用8个按钮S0 ~ S7表示。

②设置一个系统清除和抢答控制开关S,该开关由主持人控制。

③抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,扬声器发出声响提示,并在七段数码管上显示选手号码。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

2、扩展功能①抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如20秒)。

当主持人启动"开始"键后,定时器进行减计时。

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

②设置一个计分电路,具有加减分功能,加减分以10分为基准,并在数码管上显示得分情况。

二、系统工作1、电源部分①、原理输入交流220V通过电压变压器,再通过桥式整流电路和极性电容滤波,在固定式三端稳压器的Vin和GND两端形成一个并不十分稳定的直流电压(该电压常常会因为市电电压的波动或负载的变化等原因而发生变化)。

此直流电压经过三端稳压器的稳压和其后的极性电容滤波便在稳压电源的输出端产生了精度高、稳定度好的直流输出电压。

②、测试结果1、不接负载时2、抢答器部分①、原理当开关S置于闭合时,RS触发器的R、S端均为0,4个触发器输出置0,使74LS148的优先编码工作标志端(图中5号端)=0,使之处于工作状态。

当开关S置于断开时,抢答器处于等待工作状态,当有选手将抢答按键按下时(如按下S5),74LS148的输出经RS锁存后,CTR=1,RBO(图中4端) =1,七段显示电路74LS48处于工作状态,4Q3Q2Q=101,经译码显示为“5”。

此外,CTR=1,使74LS148 优先编码工作标志端(图中5号端)=1,处于禁止状态,封锁其他按键的输入。

当按键松开即按下时,74LS148的此时由于仍为CTR=1,使优先编码工作标志端(图中5号端)=1,所以74LS148仍处于禁止状态,确保不会出二次按键时输入信号,保证了抢答者的优先性。

8路抢答器设计(含完整图)

数字电路课程设计报告8路数字抢答器1.概述抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

另外设置系统清除开关一个,该开关由主持人控制。

抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,扬声器发出声响提示,并在七段数码管上显示选手号码。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清零为止。

当主持人按下清除键后,参赛选手可以进行抢答,同时倒计时电路开始倒计时,抢答有效时,红灯亮,倒计时停止,显示器上显示选手的编号,并保持到主持人将系统清零为止。

2、8路数字抢答器各主要芯片介绍2.1、74LS14874LS148是一个8线—3线优先编码器。

74LS148外部管脚图、真值表如图所示:图一 74ls148 真值表由表不难看出,在0=S 电路正常工作状态下,允许70~I I 当中同时有几个输入端同时为低电平,即有编码输入信号。

7I 的优先权最高,0I 的优先权最低。

当07=I 时,无论其它输入端有无输入信号(表中以x 表示),输出端只给出7I 的编码,即000012=Y Y Y ,当74LS148的功能表输 入输 出S0I 1I 2I 3I 4I 5I 6I 7I2Y 1Y 0Y S Y EX Y1 0 0 0 0 0 0 0 0 0 x x x x x x x x 1 1 1 1 1 1 1 1 x x x x x x x 0 x x x x x x 0 1 x x x x x 0 1 1 x x x x 0 1 1 1 x x x 0 1 1 1 1 x x 0 1 1 1 1 1 x 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 0U CC Y EX Y S I 3 I 2 I 1 I 0 Y 0I 4I 5I 6I7S Y 2Y 1GND 图2 74LS148管脚图16 9 74LS148 1 80167==I I 、时,无论其它输入端有无输入信号,只对6I 编码,即输出为001012=Y Y Y 。

8路抢答器设计八路智力竞赛抢答器

1 前言1.1主要功能介绍(1)抢答器最多可供8名选手参赛,编号为1~8号,各队分别用一个按钮(分别为S1~S8)控制,并设置一个系统清零和抢答控制开关S,该开关由主持人控制。

(2)抢答器具有数据锁存功能,并将锁存数据用LED数码管显示出来,同时蜂鸣器发出间歇式声响(持续时间为0.5秒),主持人清零后,声音提示停止。

(3)开关S作为清零及抢答控制开关(由主持人控制),当开关S被按下时抢答电路清零,松开后则允许抢答。

输入抢答信号由抢答按钮开关S1~S8实现。

(4)有抢答信号输入(开关S1~S8中的任意一个开关被按下)时,并显示出相对应的组别号码。

此时再按其他任何一个抢答器开关均无效,指示灯依旧“保持” 第一个开关按下时所对应的状态不变。

1.2扩展功能介绍(1)抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30秒)。

当节目主持人启动“开始”键后,要求定时器立即减计时,并用显示器显示,同时扬声器发出短暂的声响,声响持续时间0.5秒左右。

(2)参加选手在设定的时间内抢答,抢答有效,定时器停止工作,显示上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止。

(3)如果定时抢答的时间已到,却没有选手抢答时,本次抢答无效,系统短暂报警,并封锁输入电路,禁止选手超时后抢答,时间显示器上显示00。

(4)当选手抢答完后,主持人可根据相关题的加减分对选手进行加分或减分。

2总体方案设计此次课程设计我们有两套方案一是硬件部分主要由单片机、74LS373锁存器、LED显示器、声音报警器和其它基本外围电子电路组成软件部分则采用51系列单片机通用C语言精心设计编写。

它所具有的功能包括:抢答器同时供8名选手或8个代表队比赛,当开关S按下,抢答器发出0.5秒的报警声系统开始进行计时,选手可进行抢答,当计时30秒之后若没人抢答,则系统发出警报并禁止抢答,定时显示数码管上显示00字样,之后等待开关S按下,系统复位;若在30秒内有选手进行抢答,此时扬声器会发出3秒时间的警报,同时在定时显示数码管上显示选手抢答时间(以秒为最小单位),编号显示数码管上显示抢答选手编号,显示器上的状态直到开关S按下将系统复位为止;系统复位时所有的数码管不显示任何的数据。

8人抢答器课程设计

8人抢答器 课程设计一、课程目标知识目标:1. 学生能理解抢答器的原理和功能,掌握基本的电路知识和电子技术。

2. 学生能描述抢答器的电路组成和各个部分的作用,了解数字电路的基本原理。

3. 学生能够运用所学的电路知识,解释抢答器的工作过程和抢答规则。

技能目标:1. 学生能够动手搭建一个简单的8人抢答器电路,培养实际操作能力和问题解决能力。

2. 学生通过小组合作,学会与他人协作完成任务,提高团队协作能力和沟通技巧。

3. 学生能够运用抢答器进行互动学习,提升反应速度和思维敏捷性。

情感态度价值观目标:1. 学生通过参与抢答活动,培养积极进取的态度和竞争意识,增强自信心。

2. 学生在团队合作中学会尊重他人、倾听他人意见,培养友善和谐的同伴关系。

3. 学生通过电子制作活动,激发对科学技术的兴趣,培养创新意识和探索精神。

课程性质:本课程为实践性强的电子技术课程,结合物理知识和实际操作,提高学生的动手能力和创新能力。

学生特点:考虑到学生所在年级的特点,他们在物理知识和电子技术方面有一定的基础,具备初步的操作能力,但对复杂电路的搭建和原理理解还需引导。

教学要求:注重理论与实践相结合,强调学生的主体地位,鼓励学生动手实践和思考,培养解决问题的能力。

在教学过程中,关注学生的个体差异,提供适当的指导和支持。

通过课程目标的分解,确保学生能够达到预期的学习成果,为后续的教学设计和评估提供依据。

二、教学内容本课程教学内容紧密围绕课程目标,结合教材中相关章节,组织以下内容:1. 电路基础知识:复习和巩固电路的基本概念,如电流、电压、电阻等,为理解抢答器电路打下基础。

2. 数字电路原理:介绍数字电路的基本原理,如逻辑门、触发器等,为学生搭建抢答器电路提供理论支持。

3. 抢答器电路组成:详细讲解抢答器电路的各个部分,包括开关、按钮、指示灯、编码器、解码器等,以及它们的作用和工作原理。

4. 实践操作:指导学生动手搭建8人抢答器电路,让学生在实际操作中掌握电子技术,提高动手能力。

单片机报告八人抢答器

一、题目:八人抢答器(自拟)二、问题的提出通过延时程序设计倒计时,外部中断实现手动复位,键盘功能实现抢答并LED显示器的输出,设计成一个供最多八人使用的抢答器。

三、总体设计1、问题功能:用于多人抢答的抢答器2、系统总体结构设计1)硬件设计: MCS-51单片机、P3接口、键盘,LED显示器、外部中断INT0等;2)软件设计:首先我们的软件设计中包含了软件延时模块,用于读题倒计时和回答问题的时间控制。

其次我们软件设计还包括LED的控制模块用于控制LED。

我们还包括按键控制模块控制按键。

四、详细设计:1、硬件详细设计:2)进行硬件资源分配:8000H 硬件入口地址导线P1.0 P3.0 P1.0 P3.1 P1.2 /INT0 P1.3 /INT1 SDA SCL RSTKEY18003H /INTO 中断入口地址使用导线连接:P3.0-→ SDA ,P3.1-→ SCL , P3.4-→ RST-L 外部中断连线:使用导线将A2区的/INT0与D1区J53的KEY1口连接 2、软件详细设计:我们用软件延时程序控制延时。

软件流程图:3、设计中的主要困难及解决方案在这部分论述设计中遇到的主要困难及解决方案。

1)困难1:开始不会用LED 显示器,然后参考试验14的程序进行研究,完成了LED 的控制。

2)困难2:我们开始不能让答题时间结束后自动恢复到下一次抢答。

三、程序清单SDA BIT P3.0 SCL BIT P3.1 RST BIT P3.4 INT_KEY BIT P3.3 MTD EQU 40H进入下一轮抢答8000H 开始设置参数读题时间答题时间抢答时间本轮循环结束当前循环结束 /INTY0中断响应倒计时19秒倒计时10秒MRD EQU 48HDisBuf EQU 38H ;定义ZLG7290器件地址及子地址ZLG7290 EQU 70HACK BIT 10HSLA DA TA 50HSUBA DA TA 51HNUMBYTE DA TA 52HKey DATA 53HSystemReg EQU 00HKeyReg EQU 01HCmdBuf0 EQU 07HCmdBuf1 EQU 08HDpRam EQU 10HORG 8000HLJMP MAINORG 8003HLJMP INT0SVORG 8100H;-------主程序如下:MAIN: MOV DisBuf+2,#0MOV DisBuf+3,#0MOV DisBuf+4,#0MOV DisBuf+5,#0MOV DisBuf+6,#0MOV DisBuf+7,#0MOV SP,#60HSETB EASETB IT0SETB EX0CLR RSTLCALL DELAYSETB RSTLCALL DELAYLCALL ClsDispNBTC:MOV R2,#01HN1: MOV A,R2MOV DisBuf+1,ALCALL DisplayMOV R3,#09HN2:MOV A,R3MOV DisBuf+0,ALCALL Display编号:自拟MOV R6,#32HLCALL DELAY1DJNZ R3,N2MOV A,R2DEC R2JZ WaitKeyMOV DisBuf+0,#0LJMP N1WaitKey: JB INT_KEY,WaitKeyLCALL GetKeyMOV A,KeyJZ WaitKeyMOV DisBuf+0,AMOV DisBuf+1,#0LCALL DisplayDJS: MOV R2,#09HN3: MOV A,R2MOV DisBuf+4,ALCALL DisplayMOV R6,#32HLCALL DELAY1DJNZ R2,N3MOV R2,#0MOV A,R2MOV DisBuf+4,ALJMP NBTCNOKEY: LJMP DJSMOV DisBuf+0,#0MOV DisBuf+1,#0LCALL DisplayORG 8200HDELAY1: push 06HL1: push 06HL2: push 06HL3: DJNZ R6,L3POP 06HDJNZ R6,L2POP 06HDJNZ R6,L1POP 06HDJNZ R6,DELAY1RET;子程序名:GetKey;功能:获取用户按键值(Key);调用:VI2C_ASM.INC;入口参数:无;出口参数:Key;占用资源: R0,R1,R2,R3(工作寄存器组1),ACC,CyGetKey: MOV SLA,#ZLG7290 ;指定器件地址MOV SUBA,#01H ;指定子地址MOV NUMBYTE,#01H ;读1字节数据push ACC ;保护ACCpush PSW ;保护PSWsetb RS0 ;切换工作寄存器,I2C通信软件使用工作寄存器组1clr RS1LCALL IRDNBYTE ;调用读1字节数据程序pop PSW ;恢复PSWpop ACC ;恢复ACCmov Key,MRD ;读取的数据送Keyret ;子程序返回;子程序名:ClsDisp;功能:清除显示内容;调用:VI2C_ASM.INC;入口参数:无;出口参数:无;占用资源: R0,R1,R2,R3(工作寄存器组1),ACC,Cy,R5(当前工作寄存器组)ClsDisp: MOV R5,#8MOV A,#01100000BCls1: MOV SLA,#ZLG7290MOV SUBA,#CmdBuf0MOV MTD,AMov MTD+1,#1FHMOV NUMBYTE,#02HPUSH ACCPUSH PSWSETB RS0CLR RS1LCALL IWRNBYTEPOP PSWPOP ACCINC ALCALL DELAYDJNZ R5,Cls1RET;子程序名:Display;功能:在8段LED数码管显示;调用:VI2C_ASM.INC;入口参数: Disbuf+0~ Disbuf+7,8字节显示缓冲区;出口参数:无;占用资源: R0,R1,R2,R3(工作寄存器组1),ACC,Cy,R0,R5(当前工作寄存器组)Display: MOV R5,#8MOV A,#01100000BMOV R0,# DisbufDisp1: MOV SLA,#ZLG7290MOV SUBA,#CmdBuf0MOV MTD,AMOV MTD+1,@R0MOV NUMBYTE,#02HPUSH ACCPUSH PSWSETB RS0CLR RS1LCALL IWRNBYTEPOP PSWPOP ACCINC AINC R0LCALL DELAYDJNZ R5,Disp1RET;子程序名: DELAY;功能:延时约36.5 ms(11.0592MHz时钟);调用:YS500US;入口参数:无;出口参数:无;占用资源: R7,R6DELAY: MOV R7,#80HMIN: LCALL YS500USDJNZ R7,MINRET;子程序名: YS500US;功能:延时约279us(11.0592MHz时钟);调用:无;入口参数:无;出口参数:无;占用资源: R6YS500US: MOV R6,#80HDJNZ R6,$RET$INCLUDE(VI2C_ASM.INC)INT0SV: MOV DisBuf+4,#0LJMP NBTCRETEND四、调试程序的方法1)硬件调试方法:首先,排除常见的硬件故障,无逻辑错误,元器件状态良好无失效现象,电源正常。

8路抢答器

74LS48的引脚图

74LS48的逻辑图

74LS48的功能表

十进数 或功能 输入 LT RBI BI/R A3A2A1A0 BO 输出 a b c d e f g 备注

0

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 BI RBI LT

H

H H H H H H H H H H H H H H H x H L

• 74LS48为七段显示译码器。该集成译码 器设有多个辅助控制端,以增强器件的 功能。BI/RBO为灭灯输入,当BI=0时 ,所有字形熄灭。LT为试灯输入,当 LT=0且RBO=1时,显示字形为8,常用 于检测自身的好坏。RBI为动态灭灯输 入,当LT=1,RBI=0且输入均为0时, 输出均为低电平,数码管“灭零”。

当按下的键松开后,74LSl48的为 高电平,但由 于CTR维持高电平不变,所以74LSl48仍处于禁止 工作状态,其它按键的输入信号不会被接收。这 就保证了抢答者的优先性以及抢答电路的准确性。 当优先抢答者回答完问题后,由主持人操作控制 开关S,使抢答电路复位,以便进行下一轮抢答。

• 扩展电路设计 • 定时电路 • 由节目主持人根据抢答题的难易程度,设定 一次抢答的时间,通过预置时间电路对计数 器进行预置,计数器的时钟脉冲由秒脉冲电 路提供。可预置时间的电路选用十进制同步 加减计数器74LS192进行设计

• 时序控制电路是抢答器设计的关键,主要完成三 项功能: • ①主持人将控制开关拨到"开始"位置时,扬声器 发声,抢答电路和定时电路进入正常抢答工作状 态。 • ②当参赛选手按动抢答键时,扬声器发声,抢答 电路和定时电路停止工作。 • ③当设定的抢答时间到,无人抢答时,扬声器发 声,同时抢答电路和定时电路停止工作。

八人抢答器的课程设计

八人抢答器的课程设计一、课程目标知识目标:1. 学生能理解抢答器的原理,掌握其电路组成和功能。

2. 学生能运用所学的电子技术知识,设计并制作一个简易的八人抢答器。

3. 学生了解抢答器在现实生活中的应用,提高对电子技术实用性的认识。

技能目标:1. 学生通过动手实践,提高焊接、调试电子电路的技能。

2. 学生学会运用所学知识解决实际问题,提高创新能力。

3. 学生能够熟练运用抢答器进行课堂互动,提高课堂参与度。

情感态度价值观目标:1. 学生在课程学习中,培养对电子技术的兴趣和热情。

2. 学生通过团队协作,培养沟通、合作能力,增强团队意识。

3. 学生认识到科技发展对生活的改善,激发对科技创新的热情。

课程性质:本课程为实践性课程,结合电子技术知识和实际操作,让学生在动手实践中掌握知识,提高技能。

学生特点:八年级学生对电子技术有一定的基础,具备一定的动手能力和创新能力。

教学要求:教师应注重引导学生运用所学知识解决实际问题,关注学生在实践过程中的表现,及时给予指导和鼓励,提高学生的自信心和成就感。

同时,注重培养学生的团队合作精神和创新能力。

通过本课程的学习,使学生能够将所学知识运用到实际生活中,提高学生的综合素养。

二、教学内容1. 理论知识:- 电路基础知识:电流、电压、电阻的概念及其关系。

- 数字电路基础:逻辑门、触发器、计数器等原理及应用。

- 抢答器原理:介绍抢答器的工作原理及其在课堂互动中的应用。

2. 实践操作:- 电路搭建:指导学生动手搭建简易的八人抢答器电路。

- 焊接技能:教授学生焊接技巧,完成电路组件的焊接。

- 调试与优化:引导学生对抢答器进行调试,发现问题并进行优化。

3. 教学大纲:- 第一课时:回顾电路基础知识,介绍抢答器原理。

- 第二课时:学习数字电路基础,分析抢答器电路组成。

- 第三课时:动手搭建抢答器电路,进行初步调试。

- 第四课时:焊接电路组件,完成抢答器制作。

- 第五课时:抢答器功能测试与优化,课堂互动应用。

单片机课程设计 八位竞赛抢答器的设计

《单片机》课程设计报告题目:八位竞赛抢答器的设计目录第1章目的 (3)1.1八位竞赛抢答器的概述 (3)1.2系统主要功能 (3)第2章系统硬件设计 (3)2.1芯片的选择及工作原理 (3)2.3系统的硬件构成及功能 (4)2.3.1 抢答器的电路框图 (4)2.3.2 抢答器的电路图 (5)2.3.3 总体流程图 (6)第3章系统软件设计 (6)3.1系统主程序设计 (6)3.2抢答器的源程序 (7)第4章调式 (7)4.1主要技术参数 (7)4.2抢答器使用说明 (7)4.3常见故障 (8)附件: (8)小结 ............................................................................................................ 错误!未定义书签。

参考文献. (18)第1章目的1.1八位竞赛抢答器的概述本试验涉及的是八路数显抢答器,它具有电路简单、成本较低、操作方便、灵敏可靠等优点。

该电路由直流稳压电源、抢答器、超时报警与电子计分四部分组成。

抢答器由8个发射器和1个接收器组成,可用于8组或8组以下的竞赛中:将参赛组按顺序排号1~8,每组发给对应的一个发射器。

将接收器放于各组中央或前方。

当启动键按下后,抢答开始。

当其中一个发射器被按下后,接收器就立即显示该组的组号锁定。

之后按下任何一路抢答键均不起反映。

当再次按动启动键后,进行下一轮抢答。

1.2系统主要功能抢答器具有第一个抢答信号的鉴别和数据锁存、显示的功能。

每名选手有一个抢答按钮,按钮的编号与选手的编号相对应,抢答开始后,某抢答按钮被按下,电路具备自锁功能将信号锁定,禁止其他选手再抢答,优先抢答选手信息一直保持到启动键再次被按下,将系统清0 为止。

同时,对应该选手的指示灯亮,并在数码管上显示该选手编号,且扬声器发出音响提示。

第2章系统硬件设计2.1芯片的选择及工作原理本设计使用到的元器件包括:8051芯片(功能强大,操作简单,所用到的外围器件较少)、数码LED显示器、七段LED数码管的译码。

8位竞赛抢答器程序与仿真图

8位竞赛抢答器的设计设计要求以单片机为核心,设计一个8位竞赛抢答器:同时供8名选手或8个代表队比赛,分别用8个按钮S0~S7表示。

设置一个系统清除和抢答控制开关S,开关由主持人控制。

抢答器具有锁存与显示功能。

即选手按按钮,锁存相应的编号,并在优先抢答选手的编号一直保持到主持人将系统清除为止。

抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如30秒)。

当主持人启动“开始”键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间为0.5s左右。

参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

通过键盘改变抢答的时间,原理与闹钟时间的设定相同,将定时时间的变量置为全局变量后,通过键盘扫描程序使每按下一次按键,时间加1(超过30时置0)。

同时单片机不断进行按键扫描,当参赛选手的按键按下时,用于产生时钟信号的定时计数器停止计数,同时将选手编号(按键号)和抢答时间分别显示在LED上。

程序:ORG 0000HLJMP MAINORG 0003HLJMP SHESHORG 000BHLJMP IT0PORG 0100HMAIN: MOV TMOD,#01H //定时器T0工作于方式1MOV TH0,#3CH //1秒的初值MOV TL0,#0B0HSETB EASETB ET0 //开总中断,T0中断,外部中断0开启,外部中断跳沿触发。

SETB EX0SETB IT0MOV R4,#30 // R4存放30,用于存放倒计时初值MOV R3,#0AHMOV R7,#0AH // 个十百初始显示"FFF" ,R3存放选手编号,R7存放倒计时的十位,R6存放倒计时的个位MOV R6,#0AHMOV R0,#30 //R0存放倒计时的显示值,初值设为30LCALL XIANSH2STAR: setb P3.6 //关喇叭MOV R1,#00H //选手按键,复位按键,无人抢答的标志位,用于从等待中断中返回到初始//=========复位部分程序======FW: JNB P3.1,FW1 //预判复位键按下否JMP FWFW1: LCALL DELAY //去抖动,判断是否真按下JNB P3.1,FW2JMP FWFW2: MOV R3,#0BH //复位按下,则存放选手编号的R3,放入"灭"的代码MOV A,R4 //倒计时初值R4放入显示倒计时寄存器R0中MOV R0,ALCALL XIANSH1//=========开始部分程序======SAM: JNB P3.0,PKJMP SAMPK: JNB P3.0,PK1 //扫描开始键是否按下JMP SAMPK1: MOV R3,#0BH //按下则R3存"灭"代码,SETB TR0 //启动定时器MOV R2,#0AH //中断次数设为10次,刚好1秒HERE: CJNE R1,#01H,YY //若R1中存放的选手按键标志位为1,则转入STARJMP STAR //否则继续循环等待中断YY: JMP HERE//=======中断程序=======IT0P: CLR TR0DEC R2CJNE R2,#05H,JX0 // 中断5次后,开启扬声器clr P3.6JX0: CJNE R2,#00H,JX1 //中断10次后,关闭扬声器,这样喇叭响0.5秒setb P3.6DEC R0LCALL XIANSH1MOV R2,#0AH //R2中再存入中断次数JX1: LCALL SAMOCJNE R1,#01H,JX2 //扫描选手按键标志位R1,未按下则转JX2 ,按下则返回JMP RETURNJX2: JNB P3.1,PK2JMP CZPK2: LCALL DELAY //检测复位键按下否JMP CZQFW: MOV R1,#01HJMP RETURN //按下则返回CZ: CJNE R0,#00H,CZ1 //倒计时是否计时完毕clr P3.6 //及时完毕无人抢答则扬声器开启LCALL DELAY5 //延时1秒MOV R1,#01H //R1设1JMP RETURN //中断返回CZ1: MOV TH0,#3CH //计时器初值重装MOV TL0,#0B0HSETB TR0RETURN: RETI//========选手键盘扫描程序========SAMO: JNB P1.0,XS1JNB P1.1,XS2JNB P1.2,XS3JNB P1.3,XS4 //预扫描选手按键是否按下JNB P1.4,XS5JNB P1.5,XS6JNB P1.6,XS7JNB P1.7,XS80RETURN2:RET //未按下则返回XS80: LJMP XS8XS1: LCALL DELAY //去抖动再判是否按下JNB P1.0,XS11JMP RETURN2XS11: MOV R1,#01Hsetb P3.6 //按下则显示1号扬声器关闭MOV R3,#01HLCALL XIANSH1JMP RETURN2XS2: LCALL DELAYJNB P1.1,XS22JMP RETURN2XS22: MOV R1,#01Hsetb P3.6 //按下则显示2号扬声器关闭MOV R3,#02HLCALL XIANSH1JMP RETURN2XS3: LCALL DELAYJNB P1.2,XS33JMP RETURN2XS33: MOV R1,#01Hsetb P3.6 //按下则显示3号扬声器关闭MOV R3,#03HLCALL XIANSH1JMP RETURN2XS4: LCALL DELAYJMP RETURN2XS44: MOV R1,#01H //按下则显示4号扬声器关闭setb P3.6MOV R3,#04HLCALL XIANSH1JMP RETURN2XS5: LCALL DELAYJNB P1.4,XS55JMP RETURN2XS55: MOV R1,#01Hsetb P3.6 //按下则显示5号扬声器关闭MOV R3,#05HLCALL XIANSH1JMP RETURN2XS6: LCALL DELAYJNB P1.5,XS66JMP RETURN2XS66: MOV R1,#01Hsetb P3.6 //按下则显示6号扬声器关闭MOV R3,#06HLCALL XIANSH1JMP RETURN2XS7: LCALL DELAYJNB P1.6,XS77JMP RETURN2XS77: MOV R1,#01Hsetb P3.6MOV R3,#07H //按下则显示7号扬声器关闭LCALL XIANSH1JMP RETURN2XS8: LCALL DELAYJNB P1.7,XS88JMP RETURN2XS88: MOV R1,#01Hsetb P3.6 //按下则显示8号扬声器关闭MOV R3,#08HLCALL XIANSH1JMP RETURN2//=========显示程序======XIANSH1:MOV A,R0MOV B,#0AH //R0中存放的倒计时显示值除10 分出十位和个位DIV ABMOV R7,A //十位存入R7中MOV R6,B //个位存入R6中XIANSH2:SETB P0.4CLR P0.5 //选择选手编号的数码管CLR P0.6MOV A,R3MOV DPTR,#SEGTAB //调入代码MOVC A,@A+DPTRMOV P2,A //显示选手编号CLR P0.4SETB P0.5 //选择显示十位的数码管CLR P0.6MOV A,R7MOV DPTR,#SEGTAB //调入代码MOVC A,@A+DPTRMOV P2,A //显示十位CLR P0.4CLR P0.5 //选择显示个位的数码管SETB P0.6MOV A,R6MOV DPTR,#SEGTAB //调入代码MOVC A,@A+DPTRMOV P2,A //显示个位RET//=======抢答时间设置程序======SHESH:INC R0 //倒计时初值加1CJNE R0,#31,BQL //倒计时初值设置超过30 自动清零MOV R0,#00HBQL: MOV R3,#0BHMOV A,R0 //倒计时初值存入其专用寄存器R4中,这样可以全局不变,R0会倒计时中递减而改变MOV R4,ALCALL XIANSH1RETI//====10ms延时程序(去抖动)====DELAY: MOV R7,#20D1: MOV R6,#248D2: DJNZ R6,D2DJNZ R7,D1RET//1s延时程序(无人抢答报警)====DELAY5:MOV R7,#40DL1: MOV R6,#50DL2: MOV R5,#248DL3: DJNZ R5,DL3DJNZ R6,DL2DJNZ R7,DL1RET//======数码管显示调用代码======SEGTAB:DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82H,0F8H,80H,90H,8EH,0FFH//0,1,2,3,4,5,6,7,8,9,F,灭END说明:仿真开始显示FFF;按下复位键显示倒计时初值,起初设的是30秒;再按下设时键,按一下计数初值加1,到30自动清零;按下开始键开始倒计时,每减一,有0.5秒的声响;当有选手按下,则倒计时停止,显示当前倒计时数值和选手编号;若在倒计时计数到0,无人抢答则有1秒声响的报警。

八路抢答器实验报告

八路抢答器的实验报告一、设计题目八路抢答器设计二、设计要求1.设计一个竞赛抢答器, 可同时供8名选手或者8个代表队参加比赛, 他们的编号分别是 1.2.3.4.5.6.7、8, 各用一个抢答器的按钮, 按钮的编号与选手的编号相对应。

2.给节目主持人设计一个控制开关, 用来控制系统的清零和抢答开始。

3.抢答器具有数据锁存、显示的功能和声音提示功能。

抢答开始后, 若有选手按动按钮, 编号立即锁存, 在数码管上显示选手的编号, 并有声音提示。

此外, 要封锁其他选手抢答。

优先抢答的选手的编号一致保持到主持人将系统清零为止。

三、设计思路工作原理为:接通电源前, 抢答按钮与清零按钮都未按下。

接通电源后, 主持人清除开关处于工作状态, 抢答器处于工作状态, 编号显示器显示为0, 蜂鸣器未鸣响(为方便控制, 电路设计为清除开关按下时是清零状态, 未按下时为工作状态)。

等一轮抢答完成后(七段数码管显示出优先抢答队员编号, 并蜂鸣器鸣响), 主持人将清零开关按下数码管清为零, 蜂鸣器停止鸣响。

然后先后把各队员抢答按钮与主持人清零按钮复位。

即可进入下一轮抢答。

原理为:电路中清零按钮控制D触发器集成块74LS175清零端低电平输入, 按下时清零端输入为低电平(清零端低电平有效), 未按下时输入高电平。

清零后D 触发器集成块74LS175 Q`端输出全变为高电平, 使编码器74HC147(有效输入电平为低电平)无有效低电平输入, 七段数码管上显示为0。

抢答时, 队员按下抢答按钮的时间有先后次序, 电路中每个抢答按钮连接一个D触发器, 当一抢答按钮按下后其对应的触发器锁存住信号, Q`端输出有效低电平, 同时通过反馈电路使D触发器集成块得脉冲信号终止输入, 从而使其他D触发器停止工作, 抢答后也无法锁存。

达到有先输入有先锁存功能。

原理为:根据与门功能特点:只要有一低电平输入输出即为低电平。

当D触发器集成块74LS175输出端输出一有效低电平后, 电路中第7个与门U15A输出即为低电平, 而U15A输出信号又与555触发器构成的多谐振荡器输出信号相与, 因此只要U15A输出低电平, 多谐振荡器产生的脉冲就无法输入, 只有当D触发器集成块74LS175输出端输出全为高电平时脉冲才正常输入, 各D触发器正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.12.集成电路八人抢答器

一、设计任务

采用集成电路设计一八人抢答器。

二、设计要求与指标

1. 抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S0 ~ S7表示。

2. 设置一个系统清除和抢答控制开关S,该开关由主持人控制。

3. 抢答器具有锁存与显示功能。

即选手按动按钮,锁存相应的编号,并在LED数码管上显示,同时扬声器发出报警声响提示。

选手抢答实行优先锁存,优先抢答选手的编号一直保持到主持人将系统清除为止。

4. 抢答器具有定时抢答功能,且一次抢答的时间由主持人设定(如30秒)。

当主持人启动"开始"键后,定时器进行减计时,同时扬声器发出短暂的声响,声响持续的时间0.5秒左右。

5. 参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答的时间,并保持到主持人将系统清除为止。

6. 如果定时时间已到,无人抢答,本次抢答无效,系统报警并禁止抢答,定时显示器上显示00。

二、预习要求

1.复习编码器、十进制加/减计数器的工作原理。

2.设计可预置时间的定时电路。

3.分析与设计时序控制电路。

4. 画出定时抢答器的整机逻辑电路图

三、设计原理与参考电路

1.数字抢答器总体方框图

如图3.12.1所示为总体方框图。

其工作原理为:接通电源后,主持人将开关拨到"清除"状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置开始"状态,宣布"开始"抢答器工作。

定时器倒计时,扬声器给出声响提示。

选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示、扬声器提示。

当一轮抢答之后,定时器停止、禁止二次抢答、定时器显示剩余时间。

如果再次抢答必须由主持人再次操作"清除"和"开始"状态开关。

图3.12.1抢答器框图

2.系统硬件组成框图

系统硬件框图如图3.12.2所示。

图3.12系统硬件组成框图

3.抢答器主体电路设计

抢答器的主体主要由CD4532八输入优先权编码器,CD4042四D锁存器,CD4511七段译码驱动器,CD4514 4线—16线译码器。

CD4532优先编码器的功能作用是将八路按键的输入转化成三位二进制编码,同时由GS端指示编码的有效性。

没有键按下时GS为低电平、输出无效的000,反之,GS高电平、此时的代码有效,如果为000则是0号键的代码。

之所以采用优先权编码器,是考虑如果有多个键真正的同时按下(时间上的差别微小到电路无法区分)时稳定输出这几个键中优先权最高的键的代码。

电路的关键之处是对四锁存器的巧妙利

Q相连。

由其功能表可知,无任何键按下时,编码器的GS端为0,故锁存用,其CP端与0

器的CP端为1,译码器的BI端为0,译码器的INH端为1,由于锁存器的M模式控制端为1,故其各锁存器的输出跟随对应输人的变化,Q1一Q3为无效的000,锁存器处于一个稳态;此时,CD4511译码器处于消隐状态,数码管无任何显示,而CD4514处于输出禁止状态,指示灯也全灭。

当AN0一AN7中有任何一个键按下时,编码器输出有效数据的同时其GS端变为1,该

组数据(包括GS)到达锁存器输出端时CP端获得下降沿,数据被锁存的同时禁止了后续输

人,也就是说抢先选手的编号被锁存的同时屏蔽了后续选手的动作;此时两个译码器正常工作,数码管显示抢先选手的编号,该选手面前的灯也点亮了。

当主持人按下AN8时(此时,

图3.12.3抢答器主体部分原理图

AN0-AN7应该无键按下,编码器的GS端为0),锁存器的M端变为0,由功能表知锁存器先是处于跟随状态,其CP端恢复为1,后是CP的正跳变使锁存器转为锁存状态(即无效数据状态),CD4511译码器消隐, CD4514输出禁止。

然后AN8松开, M端恢复为1,锁存器又回到初始的跟随状态,为下一轮抢答作好准备。

电路中的音响电路由音乐IC和功放LM386组成。

音乐IC可选用CK9561, 根据具体情况选取声音。

音乐CI的触发信号来自于编码器的GS端, 有键按下时, GS为1即可触发音乐发音, 所以可以在调试时通过有无声音来判断各按键的连接可靠性。

主体电路原理图的如图3.12.3所示.

抢答器扩展部分,计时控制电路主要由NE555多谐振荡器,74LS160计数器,74LS48译码器,74LS00与非门构成。

抢答器扩展部分-定时器原理图如图3.12.4所示。

图3.12.4 抢答器扩展-定时器部分原理图

4.安装及调试

通过设定仿真器的属性,即选定Multisimim仿真软件实现硬件的仿真。

对应主体电路和扩展电路两方面在硬件电路实现,通过仿真软件的全速执行,来观察硬件电路的反应是否正常。

通过反复多次调试,通过单步执行操作,观察软件中单条程序的运行是否与硬件各控制信号的动作相一致。

调试过程中,发现一步操作结果不对,便分析原因进行修改,直到整个系统正常运行。

显示电路仿真如图3.12.5(图为2号选手抢答结果显示);扩展电路的仿真图如3.12.6所示。

然后进行硬件安装调试,只要电路安装没有错误,便能成功运行实际电路。

图3.12.5抢答器主体电路仿真图

表3.4 CD4042逻辑功能表

表3.6 CD4514功能表

图3.12.6 抢答器扩展-定时器部分仿真图

5.设计电路给定的元器件

CD4532,CD4042,CD4511,74LS160,74LS48,NE555,74LS00,74LS04,排阻,电阻,开关,数码管,LM386等。