跨导运算放大器设计实例n

跨导运算放大器设计实例

李福乐 lifule@

1

Specifications

• CSMC 0.6um DPDM CMOS Process • GBW > 100MHz, PM > 60 when CL=2pF • DC Gain > 80dB • Output swing > 4V (differential) • Full differential architecture • Low Power (Large FOM)

所设计的OTA要应用于课程设计10bit cyclic ADC中。 在开关电容ADC中,ADC的速度取决于级电路的建立速度,而级电路的建立过程 可视为由大信号压摆区和小信号线性建立区构成,其中,小信号建立区的时间通 常要占到总建立时间的80%~90%,因此,OTA的大信号压摆率对ADC的速度影响 较小; 从另一个方面来说,压摆率只取决于偏置电Байду номын сангаас,当偏置电流和电容确定后,无论 输入管的VGS-VT是大是小,压摆率都不变。对于连续信号处理电路,我们希望 OTA在整个设计带宽内工作时,输出信号不会因为摆率跟不上而幅度受限,这个 时候需要SR/GBW大一些,即输入管的VGS-VT大一些;但是,对于采样信号处理 电路,比如我们所要设计的ADC,当我们确定好偏置电流,然后降低输入管的 VGS-VT,这个时候,SR不变,GBW变大,即SR/GBW变小了,而最终的建立时 间反而缩小了,ADC的速度加快了。 因此,SPEC中没有提出对SR的具体要求。 注意:不同应用对SR/GBW的不同要求!

3

MOST parameters

• u? Cox?

– Find out un, up, toxn and toxp from model library

(完整word版)跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

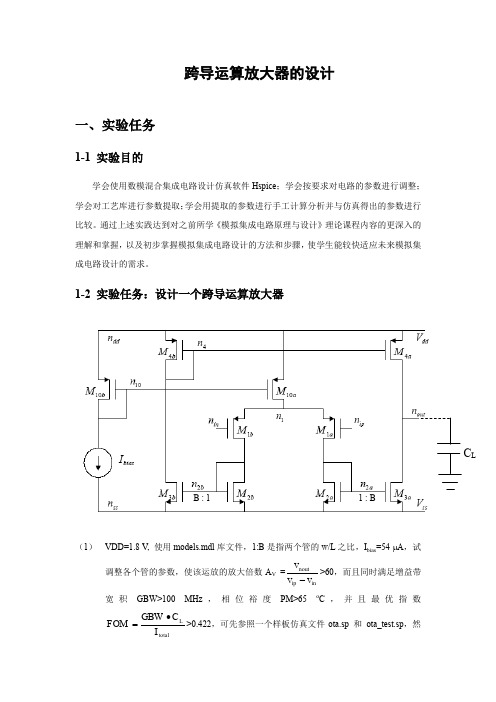

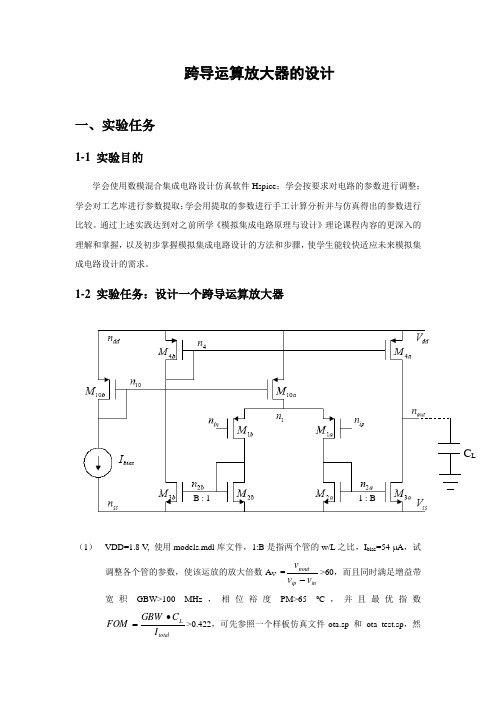

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

共栅运算跨导放大器

折叠式共源-共栅运算跨导放大器姓名:刘淑杰学号:U200714149班级:2007级2班院系:控制系专业:测控技术与仪器同组人姓名:黄大龙葛金炬目录1设计目标 02相关背景知识 (1)(1)课题背景 (1)(2)题目理解 (1)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.3计算DC 增益 (3)3.4计算GBW (5)3.5实际计算 (7)3.6参数验证 (9)4 电路仿真 (10)4.1 用于仿真的电路图 (10)4.2 仿真网表 (10)4.3 仿真波形 (12)5 讨论 (14)收获和建议 (15)参考文献 (17)1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见下表,参考电路原理图如下图所示,用0.35um coms工艺。

Cload DC Gain GBW Vdd Idd3pF 40dB~50dB 300MHz 3V Don’t Care图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识(1)课题背景共源共栅级的普及有两个主要原因。

第一个主要原因是它们由于大输入阻抗,对单级有相当大的增益。

为了得到这个高增益,与输出节点相连的镜像电流源可以用高质量共源共栅镜像电流源实现。

通常,得到这个高增益不会导致任何速度降低,而且有时还会提高速度。

(完整word版)跨导运算放大器的设计

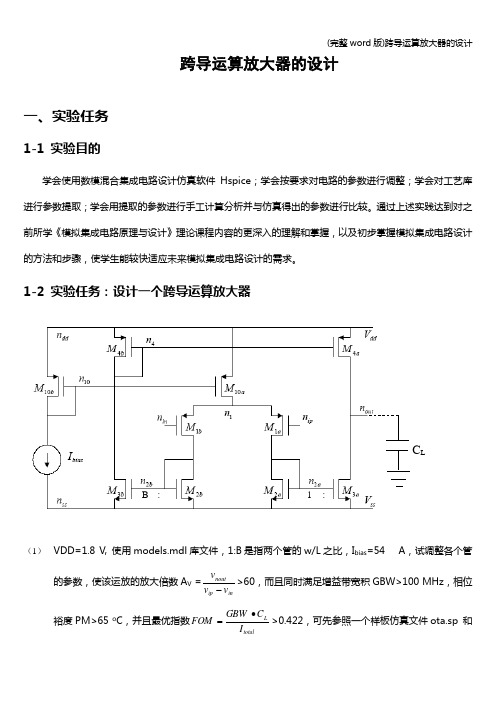

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

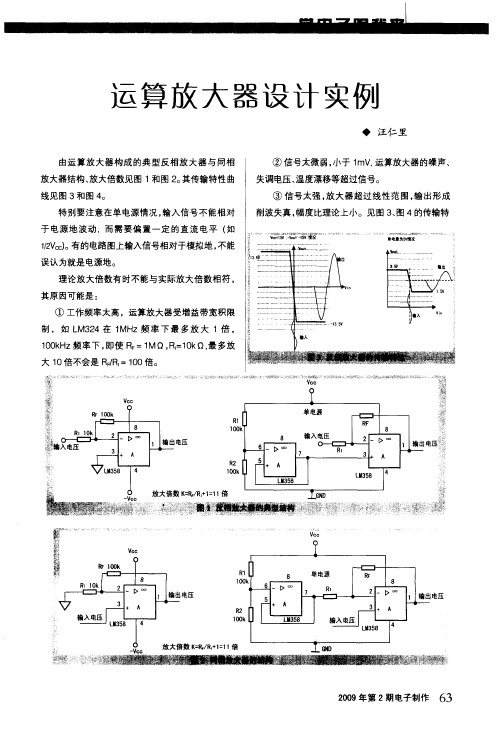

运算放大器设计实例

电压

20 年第 2 09 期电子制作

6 3

⑤ 信 号源 内阻太高。 在反相放大器的放大倍数

计算中, I R 要加上信号源 内阻。为了使 R 远远大于

信号源 内阻 ,使 K=R . 立 , R 要成 比例增 成 R、 .

加 , 旦 R> 0 一 。1 MQ, 运放 的输 入 电 流不 可 忽 略 。 想 理

模范 围受跟随器

线性区限制 。 不

能 保 证 输 入 偏 置

O~5 的范 围 。 V

圈豳

6 电子制作 20 年 第 2 4 O9 期

的原 因, 限制了输 出电流 。 显然一般 的运放驱动几十 毫安的 电流是 困难的。 同样 , R 等取值 在 1 Q R。 k

以下 , 影响 实 际放 大倍 数 。

w依 输 出 然 是 U = 2

j

K , U1 K=1 V 。 嗍 不

A

仅 是 直 流 ,也 可 以是 交流信号 , 如 5H 例 Oz

化运放 的“ 断” 虚短 ” 虚 “ 假设认 为运放的输入 电流 为 零。L 2 M3 4实际输入电流 为零点几微安 。 用 MO ( S 型输 入的运放输入电流可以小几百倍 ) 虚断” “ 假设 不能成立。同相放 大器或跟随器 的 l N+输入端直接 性曲线的水平部分 .就是放大器输出饱和到固定 电 平。 输入幅度再增加 。 出幅度不变。对 5 输 V情况下 。 输出幅度在 1 ~ V 。 35 。有一种“ aI a 中文翻 5 R l0R t 译为“ 轨至轨” 运放 , 出幅度几乎与电源相齐 。对 输 接信号源 .运放 的输入电流在信号源高内阻上形成 压降 , 实际放大倍数减小。 另外高阻输入电路容易受

运 算 放 大 器设 计 实例

跨导放大器设计实例

模拟集成电路实验——跨导放大器设计实验报告学院:电信学院班级:微电子23班姓名:游晓东学号:2120503069一、设计指标二、电路结构确定电路结构的原因: ① 根据设计指标② 电路结构对称,匹配度高,,Offset CMRR 性能指标好③ 电路稳定性好,只有一个主极点④ 该电路为差分输入,单端输出,共模抑制比大,输出共模点较稳定三、电路原理概述该电路主要由三部分组成:带隙基准电流源、偏置电路、跨导放大器9~21M M 构成一个跨导放大器,其中13M 为尾电流源,向输入的差动对管提供电流偏置。

11,12M M 为输入差分对管,将小信号电压转换成小信号电流。

9,14M M 和10,17M M 为两个对称的电流镜,比例复制小信号电流。

14,15M M 与16,17M M 为共源共栅结构,可以提高输出阻抗和开环增益。

18,19,20,21M M M M 为低压共源共栅电流镜,可以作为单端输出并且提高输出摆幅。

0~8M M 构成偏置电路部分,为跨导放大器提供偏置电流。

22~34,0~2,0~2M M Q Q R R 构成带隙基准电流源部分,为电路提供基准电流源。

四、设计过程1. 分配电流根据静态电流250A μ限制,分配带隙基准电流源部分20A μ,偏置电路部分10A μ(其中每一路2A μ),跨导放大器部分210A μ。

分配14,17M M 的偏置电流14M I 时主要考虑三个指标:,,GBW SR GMGM 要求900~1100/A V μ,因此GM 取1000/A V μ。

由于11GM B gm =⋅,B为14,9M M 的偏置电流之比,因此111000/B gm A V μ⋅= (1)GBW 要求大于3MHZ 。

112LB gm GBWC π⋅=⋅,因此11566/B gm A V μ⋅> (2)SR 要求大于3/V S μ。

92M LB I SRC ⋅=,因此9290M B I A μ⋅> (3)由于9112M ODI gm V =,若OD V 取0.2V ,则由(1)得9100M B I A μ⋅=,由(2)得956.6M B I A μ⋅>,由(3)得945M B I A μ⋅>。

折叠式共源-共栅运算跨导放大器的设计

《IC课程设计》报告折叠式共源-共栅运算跨导放大器的设计姓名:王志伟学号:U200713959班级:0707院系:控制系专业:自动化同组人姓名:田绍宇胡月目录1设计目标 (1)2相关背景知识 (2)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.2.1直流工作点分析 (2)3.2.2带宽分析及原件参数计算 (3)3.2.3直流增益的小信号模型分析 (4)3.3 计算参数验证 (5)4电路仿真 (5)4.1交流特性仿真 (7)4.2最大输出摆幅仿真 (9)4.3共模输出的仿真验证 (11)5讨论 (12)6收获和建议 (13)7参考文献 (14)摘要:折叠式共源共栅结构的运算放大器不仅能提高增益、增加电源电压噪声抑制比、而且在输出端允许自补偿。

1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见表1,参考电路原理图如下图所示,用0.35um coms工艺。

图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识随着集成电路技术的不断发展,高性能运算放大器得到广泛应用,其性能直接影响电路及系统的整体性能。

折叠式共源共栅运算放大器具有二阶优化性能,因此设计一个实用价值的折叠式共源共栅运算放大器是非常有现实意义的。

CMOS管的参数并不能通过简单的理论计算进行准确的预测,在给定的工艺条件下,理论计算出的管子宽长不考虑实际情况下工艺条件等诸多外界因素,仿真的结果会和设计指标有很大的差距。

第八讲 跨导运放的分析与设计讲解

由于零点的作用,相位裕度 从60多度减小至39度!

交流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

分析miller补偿效应

.probe ac v(vo1) v(vo) vp(vo)

.op

*.dc v_vdc 2.48 2.495 0.0001

失调分析

在MOS晶体管的参数中考虑失配 例:原有的 W=12u, M=2 修改为 W=‘12u+12u*0.04u*alfa/sqrt(2*12um*5um)’ M=2 delvto=‘12.5n*alfa/sqrt(2*12um*5um)’ 这里alfa为(0,1)高斯分布变量 依次将网表的内容按照上面的方法修改

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

.probe dc v(vo1) v(vo)

.op .dc v_vdc 2.48 2.495 0.0001

精扫

*.trans 10ns 200ns 20ns 0.1ns

*.ac dec 10 1k 100meg $sweep rzv 0 2k 0.2k

耗,因此可查得电路功耗为2.47mW • 对于MOS管,注意各参量的含义:region、id、vgs、

vds、vth、vdsat、gm、gmb、gds……可查得流过 M_U3的偏置电流为149.8uA,并注意到M_M3的 region为Linear

直流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

CMOS恒跨导运算放大器设计

(2)跨导运算放大器模型 ● OTA的符号如图所示,它有两个输入端,一个输出端,一个控制端。符号上的 “+”号表示同相输入端,“一”表示反相输入端, I O 是输出电流, I B 是偏置电流,即外 部控制电流。 I O G(V V ) GVid ● OTA的传输特性用下列方程式描述:

lim Rnn ( ) 0 此外,若时延足够大,则

所以时延足够大时,只输出信号自身的相关函数 R( ) Rss ( )

三、互相关检测

1、基本原理:

若已知发送信号的重复周期或频率,就可在接收端发 出一个与发送信号周期相同的“干净的”重复周期信 号,称为本地信号,将它与混有噪声的输入信号进行 互相关,即可除去噪声的影响,提高电路的抗干扰能 力。

OTA的小信号理想模型

2 CMOS恒跨导运算放大器的设计

(1)设计指标

● 工作电压: 2.7V

● 直流开环增益:90dB

● 相角裕度: 70 ● 增益带宽积:1.4MHz ● 负载电容:25pF

(2)运算放大器原理框图

● 输入级采用互补差分对结构, 使共模输入电压范围达到轨到轨,

通过3倍电流镜控制尾电流使输

U s1 (t )

窄带滤波 放大 输入信号

U 1 (t )

×

U 2 (t ) 参考信号

U O (t )

锁定放大器原理

锁定放大器理论推导

设输入信号: X (t ) S (t ) N (t )

A sin(t ) N (t )

S (t ) 为有用信号,A为其幅值, 角频率为,初相角为 其中, N (t ) 为随机噪声,

由上式可以得到输出阻抗:Zout ( A 1) gmro1ro2 而单共源共栅电路的输出阻抗为: gmro1ro2 电路的小信号分析表明输出阻抗 Z out值增大。

具有较小跨导的跨导放大器结构的一个比较设计方法

具有较小跨导的跨导放大器结构的一个比较设计方法摘要:一个家用CMOS运算放大器(OTAS)已经被设计成具有非常小的跨导以保证晶体管在温和的反转中工作。

许多的OTA设计方案如传统的利用电流转换、浮栅和大容量驱动技术都已经被讨论过。

这些方案的一些性能特点如功耗、有源硅区、信号噪音比我们也进行了一些详细的比较。

我们已经在一个1.2μm的n阱COMS工艺和工作电源2.7V 的条件下爱制备出了这种跨导放大器。

并且芯片的测试结果与理论计算结果也有很好的吻合。

引言由于人类身体的相对缓慢的电活动在医疗电子设备、有源滤波器和低截止频率等领域是很必要的。

低频电路应用的另一个领域是斜坡生成模拟---数字转换器(ADC)测试和神经网络领域。

因此,我们致力于研究出一个能够在低频率下工作的开发集成解决方案的电路。

对于一个运算跨导放大器—电容(OTA-C)滤波器来实现这样一个低频率来说就意味着需要大型电容器和非常低的跨导。

因此,我们有两个完全独立的角度去处理这个问题。

一种是设计出具有非常低的跨导(一般没伏几微毫安)、高线性;另一种是在芯片上实现大电容(通常是几纳法)。

按照上述思路,我们来分析不同工艺取得低跨导,我们在功耗、有源硅区、信号噪声比(SNR)等性能特性方面针对不同的方法已经开展了比较研究。

特别强调了在温和反转区的MOS晶体管的操作设计以便在功率和面积要求上达到一个较好的折中可能。

OTA拓扑在温和的反转中我们设计四种不同的OTA拓扑结构,在相同的跨导值为10nA/v的所有MOSFET模型中我们用一个方程式来权衡相关的设计参数如功耗、有源硅区和SNR。

A参考的OTA设计A如图一所示,这个OTA主要由两个不同部分(M1和M2)和三个电流镜。

放大器的全部跨导Gm跟M1、M2相同(M3=M4=M5=M6,M7=M8)。

根据所需的跨导值,此基本拓扑电流的结构水平可以非常小(大约在微微安培每伏),这就会使得W/L的比值为0.001甚至更少。

跨导放大器的分析与设计(1)-清华大学模拟集成电路分析与设计

单级OTA

z 输出共模电平 不稳定

依赖于上下 两个电流镜 之间的电流 匹配程度

需要共模反 馈环路来稳 定输出共模 电平

差模半电路

跨导放大器的负载

z 低负载阻抗RL会大幅降低放大器的增益

RL可能是片外负载或来自反馈网络的负载效应

z 反馈系统的高精度要求放大器有高的增益

反馈网络采用高阻值电阻

M2的过驱动电压增加,输出端摆幅减小

z 减小噪声:减小Cgg1,提高M1的特征频率

常用积分公式

单级Cascode放大器

z 减小噪声:减小gm2(减小Cascode管的跨导效率)

M2的过驱动电压增加,输出端摆幅减小 减小gm2/gm1和Cx

两级放大器

推导过程见网 络学堂中上载 的阅读材料

z 降低噪声:增加Cc z 如果CL较小,β较大,第二级对噪声有较大贡献

z 右半平面零点将减小相位裕度

除非gm2>>βgm1

消除右半平面零点的影响

z 消除补偿电容Cc所引起的前馈通路

插入源极跟随器 插入共栅放大器

z 电阻与Miller电容串联

将零点频率推高到无穷远处 将零点移到左半平面,并与非主极点相消

消除右半平面零点:插入源极跟随器

z前馈支路由CC

M3

和Cgs3串联组成:

绝大多数集成放大器都 是OTA

电压控制电流源(VCCS) 高输出阻抗

不能驱动低的电阻性负 载

采用电容性反馈(如开 关电容电路)

提要

z 跨导放大器的基本概念 z 单级跨导放大器 z 两级OTA的基本特性 z 两级OTA的频率补偿:Miller补偿 z 反馈型OTA中的噪声 z 两级OTA的设计 z 阶跃响应:线性建立过程 z 阶跃响应:放大器中的压摆问题

高增益跨导性运算放大器设计

10212020059 赵琦

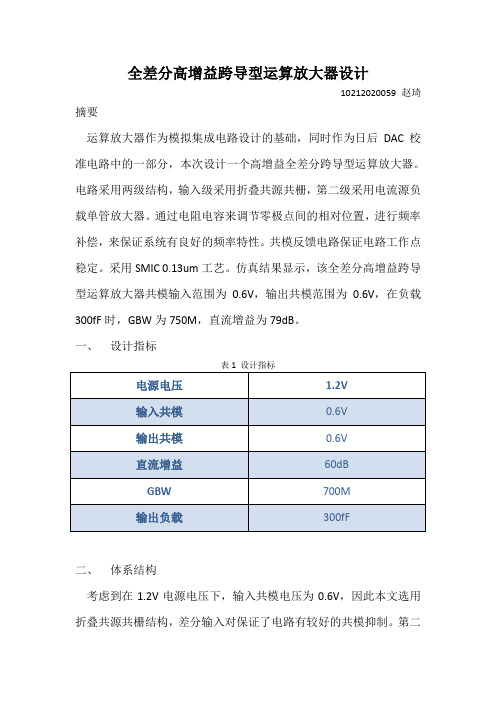

摘要 运算放大器作为模拟集成电路设计的基础,同时作为日后 DAC 校 准电路中的一部分,本次设计一个高增益全差分跨导型运算放大器。 电路采用两级结构,输入级采用折叠共源共栅,第二级采用电流源负 载单管放大器。通过电阻电容来调节零极点间的相对位置,进行频率 补偿,来保证系统有良好的频率特性。共模反馈电路保证电路工作点 稳定。采用 SMIC 0.13um 工艺。仿真结果显示,该全差分高增益跨导 型运算放大器共模输入范围为 0.6V,输出共模范围为 0.6V,在负载 300fF 时,GBW 为 750M,直流增益为 79dB。 一、 设计指标

GBW

gm

g m1、 2 2 Cc

2I Vgs Vth

其中补偿电容粗略估算,留有余量取 300fF。 Vgs Vth 取 0.2V。可以粗

略估算 I 为 120uA,本设计中取为 150uA。 通过简单 miller 补偿,主极点

P 1

C 为 miller 补偿电容, 次级点

表 1 设计指标

电源电压 输入共模 输出共模 直流增益 GBW 输出负载

1.2V 0.6V 0.6V 60dB 700M 300fF

二、 体系结构 考虑到在 1.2V 电源电压下,输入共模电压为 0.6V,因此本文选用 折叠共源共栅结构,差分输入对保证了电路有较好的共模抑制。第二

级采用了电流源负载的单管放大器。电阻 R2 和电容 C 用来调节零极 点的位置进行频率补偿,以保证系统的稳定性。基本原理是增加一个 左半平面 (LHP) 零点来抵消次级点对相位的影响, 同时会把主极点推 向原点。最左边部分是共模反馈电路。

50 0 -50

-100 0 10

跨导运算放大器及其Spice电路模型的构建

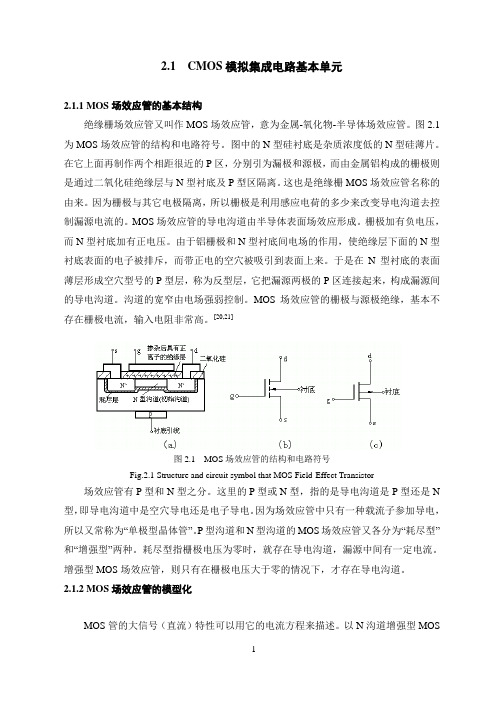

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

采用共源共栅差分结构实现差分运算跨导放大器的设计-设计应用

采用共源共栅差分结构实现差分运算跨导放大器的设计-设计应用近十几年来,移动电话、掌上电脑、笔记本电脑等便携式设备及医疗、测试仪器的迅猛发展拉动了具有低压差、低功耗的LDO(LowDropout)稳压器的快速发展。

当前,LDO稳压器已经实现500mV以下的压差。

在LDO稳压器中,电源是主要的噪声源。

尤其在高频,电源电压的变化为系统稳定性带来的影响更大。

误差放大器是LDO稳压器的重要组成部分,其稳定性与整个LDO稳压器系统的稳定性能密切相关。

因此,研究电源电压变化对LDO稳压器中误差放大器的影响是非常必要的。

电源抑制比(PSRR)衡量模拟系统对抗电源噪声的能力,是放大器一个非常重要的性能指标。

本文设计的误差放大器为带共源共栅电流镜负载的共源共栅差分运算跨导放大器。

它应用在一款超低功耗的LDO线性稳压器中,采用共源共栅差分结构,提高了PSRR,低频达到119dB。

同时,该放大器具有高共模抑制比(CMRR),低频达到106dB,静态电流不超过0.62μA。

OTA的设计与仿真PSRR定义为输入端到输出端的电压增益与电源到输出端的电压增益之比,即Gm(s)和Gmp(s)分别是输入端到输出端、电源到输出端之间的跨导。

在LDO线性稳压器中,只有VDD一个低压电压源供电,因此,这里只讨论VDD的PSRR。

电流镜负载放大器是LDO线性稳压器中误差放大器的基本结构,如图1所示。

VDD通过M3、M4,为输出端引入一个电流(go4+sCp4)VDD,通过M3、M1、M2,为输出端引入一个电流(go1+sCp1)VDD,则式中,go为输出导纳,Cp=CGD+CDB。

图1基本电流镜负载差分电路对这种结构的放大器的PSRR进行Spice仿真,如图2所示。

从图2中可以看出,低频时的PSRR只能达到47.6dB,远远不能达到LDO 线性稳压器的性能要求。

从(2)式可以看出,减小M1、M4的输出导纳,可以提高低频时的PSRR,减小M1、M4的寄生电容,即减小MOS管的尺寸,可以提高高频时的PSRR。

跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp ,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

跨导运算放大器

5.2 双极型集成 OTA

5.2.1 OTA 的基本概念

OTA 是跨导运算放大器的简称,它是一种通用标准部件。OTA 的符号如图 5.1 所示,它有 两个输入端,一个输出端,一个控制端。符号上的“+”号代表同相输入端, “-”号代表反相 输入端,io 是输出电流,IB 是偏置电流,即外部控制电流。 OTA 的传输特性可用下列方程式描述

186

式(5.10)是传输特性的精确表达式,显然 io 与 uid 之间具有非线性函数关系。在输入电压信 号很小,即 uid<<2UT 条件下,利用双曲正弦函数的特性(即当 x<<1 时,thx≈ x) , 。则由式(5.10) 可得,io 与 uid 之间具有的近似线性关系为

io ic1 ic2 I B

i o G m ( u i u i ) G m u id

(Hale Waihona Puke .1)183式中 io 是输出电流;uid 是差模输入电压;Gm 是开环跨导增益。 通常由双极型集成工艺制作的 OTA 在小信号下,跨导增益 Gm 是偏置电流 IB 的线性函数, 其关系式为

G m hI B

h q 1 2 kT 2U T

VD6

-EE

图 5.4 基本型 OTA 电路

在图 5. 4 所示电路中,VT1、VT2 组成跨导输入级,它是共射差动式电路,输入电压信号, 输出电流信号,因此是跨导放大级。VT3 和 VD1 组成一个基本镜象电流镜,与结构框图 5.3 中 Mw 的作用相同,将外加偏置电流 IB 送到输入级作 VT1、VT2 的射极长尾电流。VT7、VT8、VT9 和 VD5 组成威尔逊电流镜, 起结构框图 5.3 中 Mz 的作用, VT8 与 VT9 的达林顿接法可提高电流 镜的输出电阻, 并联在 VT8 发射结上的二极管 VD4 用来加快电路的工作速度。 同理, VT4、 VT5、 VT6 与 VD2、VD3 组成威尔逊电流镜,起结构框图 5.3 中 Mx 的作用。VT10、VT11 和 VD6 组成第 三个威尔逊电流镜起框图中 My 的作用。输出端为 VT9 集电极与 VTl0 集电极的相交点。因此是 高阻抗输出端,输出电流为 VT9 集电极电流与 VT10 集电极电流之差。 如果上述电路中 4 个电流镜的电流传输比均等于 1 ,从而使得 ic9=ic2 , ic10=icl , io= ic9-ic10=ic2-ic1。因此,上述 OTA 电路的传输特性(即 io 与 uid 的函数关系)将由差动输入级的传输 特性来决定。

模拟集成电路设计(跨导运算放大器)【范本模板】

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器.跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3。

6V,Temp=27℃〈250μA输出摆幅输入共模电压VDD =3。

6V,Temp=27℃VDD =3。

6V,Temp=27℃0.6~1。

2V0。

1~1V开环增益(低频)VDD =3。

6V,Temp=27℃1800~2200单位增益带宽VDD =3。

6V,Temp=27℃>3MHz相位裕度VDD =3。

6V,Temp=27℃〉60°PSRR(低频)VDD =3。

6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3。

6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因); 2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数.5.采用全典型模型,27℃,验证电路是否满足设计指标;6.设计偏置电路:a)选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c)采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标"要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a)一输入端固定为0。

CMOS恒跨导运算放大器设计实用PPT课件

一、相关函数的定义与计算

功率有限信号的自相关函数

R ()R x(x)T l i T 1 m T 2 T 2x(t)x(t)dt

两个功率有限信号的互相关函数

R x(y)T l im T 1 T 2T 2x(t)y(t)dt R y(x)T l im T 1 T 2T 2y(t)x(t)dt

● 当Vcm处于中间状态时,

互补差分输入管M1,M2,M3,M4均工作,

开关管M5和M8均截止,此时只有 和 提供尾电流, 从而电路跨导保持恒定。(Vcm为共I ref模1 输I入ref 2电压)

3倍电流镜输入级电路图

第6页/共42页

(4)增益级

● 本设计的运算放大器利用反 馈增大输出阻抗,实现高直流增 益,放大输入级产生的两对差分输 入电流iinp/iin与p iinn/i,inn运算 放大器A1和A2为晶体管M14和M18 提供电压增益,最终放大的信号驱动 输出晶体管M26和M22的栅端。

● 对于这个理想模型,两个电压输入之间开路, 差模输入电阻为无穷大;输出端是一个受差模输入 电压控制的电流源,输出电阻为无穷大。同时, 理想跨导放大器的共模输入电阻、共模抑制比、 频带宽度等参数均为无穷大,输入失调电压、 输入失调电流等参数均为零。

OTA的小信号理想模型

第3页/共42页

2 CMOS恒跨导运算放大器的设计

(t

)dt

2

T

ni

(t )ni

(t

)dt]

2

2

R ss ( ) R sn ( ) R ns ( ) R nn ( )

在一般情况下,噪声和信号不相关,有 Rsn ()Rn(s)0

此外,若时延足够大,则 l i mRnn()0

一种具有高增益和超带宽的全差分跨导运算放大器

0中国集成电路设计♦China lntegrated Circult一种具有高增益和超带宽的全差分跨导运算放大器罗杨贵1,曾以成1,邓欢2,唐金波21.湘潭大学物理与光电工程学院;2.湖南毂梁微电子有限公司摘要:基于GSMC0.18um CM OS工艺,设计了一种应用于12位ADC的全差分运算放大器。

为了提高增益,在套筒式共源共栅结构上运用了增益提高技术。

为了提高输入跨导,采用隔离效果更好的深N阱CMOS作为输入端,从而提升增益带宽。

为了降低功耗,利用单端放大器作为辅助运放。

整体电路结构简单优化。

仿真结果表明,运算放大器直流开环增益大于100dB,单位增益带宽大于800M H z,相位裕度大于70毅,完全满足目标ADC的性能要求,是一种新型且质量较高的运放,也可应用于其它场合。

关键词:增益提高;套筒式共源共栅;高增益带宽;深N阱中图分类号:TN432文献标识码:AA Fully Differential Transconductance Operational Amplifierwith high Gain and ultra GBWLUO Yang-gui,ZENG YirCheng1,DENG Huan2,TANG Jn-bo21.SchoolofPhysicsand Opibe]ectronics,X iangtan University;2.H unan Greai-Leo M icroe]ectronicsCO.LTDAbstract:Based on theGM SC0.18um CM OS process,a fuUy differentialoperationalam plifierlbr12-bitADC is designed.In orderto increase the gain,a gain-enhancing technique is used on the te]escopic cascode structure.In order to increase input transconductance,the deep N-W elltansistorwith better isolation function was used as the input,thereby to enhance the gain bandwidth.In order to reduce power consumption,a single-ended amplifier is used as an auxiliary operational amplifier.The overall circuit structure is simple and optimized.The simulation results show that the operational amplifier DC open-loop gain is greater than100dB,the unity gain bandwidth is greater than800MHz, and the phase margin is greater than70毅,which fully meets the performance requirements of ADC.It is a new and high-quality operational amplifier that can also be applied to other applications.Keywords:Gain enhancement;Telescopic cascode;High gain bandwidth;Deep N_well0引言模数转换器作为连接模拟信号与数字信号的桥梁,越来越显示出其重要性。

高增益恒跨导低失调轨至轨运算放大器的设计

高增益恒跨导低失调轨至轨运算放大器的设计1 引言运放是电子工程学科中最常用的基础电路元件之一。

其主要功能是接收输入信号,经过处理后输出一个信号,这可以是电压、电流、复合信号等不同形式的信号。

高增益恒跨导低失调轨至轨运放是一种广泛应用的运放类型,其优点包括高增益、宽带宽、低失调和能够处理大量信号等等。

本文将介绍高增益恒跨导低失调轨至轨运算放大器的基本原理和设计方法。

2 关键设计参数高增益恒跨导低失调轨至轨运放的设计需要考虑一系列关键参数。

这些参数包括放大器的增益、带宽、失调、输入阻抗、输出阻抗等等。

下面将分别介绍这些关键参数。

2.1 增益放大器的增益通常是设计时需要优化的主要参数之一。

在高增益恒跨导低失调轨至轨运放的设计中,增益主要取决于差分对输入和不同的反馈电路。

因此,设计者需要选用适当的反馈结构和电容来达成所需的增益。

2.2 带宽高增益恒跨导低失调轨至轨运放的带宽通常被设计为大于几百Mhz,这是因为其应用涉及高速信号处理和光纤通信业等领域。

带宽取决于放大器的极点,因此,在设计时需要确保放大器的布局和电气特性能够支持所选的带宽,以避免输出失真和衰减。

2.3 失调失调是指差分输入信号被误差放大,产生输出偏移的情况。

失调可由差分对的非对称性引起,因此,设计时需要确保差分对的匹配性,以减小失调。

2.4 输入阻抗放大器的输入阻抗取决于前级电阻和差分对的电阻。

输入阻抗影响放大器的干扰抗性和电路的灵敏度。

设计时需要选择合适的前级电阻和差分对的电阻,以实现所需的输入阻抗。

2.5 输出阻抗放大器的输出阻抗通常很低,这是因为高输出阻抗可能会导致信号变形。

输出阻抗与两级输出级的负载电阻有关。

设计时需要选择合适的负载电阻和输出级的电路结构,以实现所需的输出阻抗。

3 设计方法高增益恒跨导低失调轨至轨运算放大器的设计方法包括:3.1 选择运放类型选择合适的高增益恒跨导低失调轨至轨运放类型取决于应用需求。

常用的类型包括单放大器、差动放大器和多级放大器等。