mips汇编

mips 汇编代码

MIPS汇编代码MIPS汇编代码是MIPS微处理器的汇编语言,由MIPS Technologies公司开发。

它是一种低级编程语言,允许程序员直接控制处理器的寄存器和指令。

MIPS汇编代码通常用于嵌入式系统和实时系统,因为它可以提供对硬件的精细控制和高性能。

MIPS汇编代码由一系列指令组成,每条指令由一个操作码和零个或多个操作数组成。

操作码指定要执行的操作,而操作数指定操作的参数。

MIPS汇编代码中的指令可以分为以下几类:算术和逻辑指令:这些指令用于执行算术和逻辑运算,例如加、减、乘、除、与、或、非等。

数据传送指令:这些指令用于在寄存器和内存之间传送数据。

控制流指令:这些指令用于控制程序的执行流程,例如跳转、分支、调用和返回等。

系统指令:这些指令用于与系统进行交互,例如加载和存储程序和数据、读写I/O设备等。

MIPS汇编代码通常使用以下语法:label: instruction operand1, operand2, ...其中,label是指令的标签,instruction是指令的操作码,operand1、operand2等是指令的操作数。

MIPS汇编代码的程序结构通常包括以下几个部分:数据段:数据段用于存储程序中使用的数据,包括常量、变量和数组等。

代码段:代码段用于存储程序的指令。

堆栈段:堆栈段用于存储程序的局部变量和临时数据。

MIPS汇编代码的编译过程通常包括以下几个步骤:预处理:预处理阶段将源代码中的宏和条件编译指令进行处理。

汇编:汇编阶段将源代码中的指令转换成机器码。

链接:链接阶段将汇编生成的机器码与库函数和系统库进行链接,生成可执行文件。

MIPS汇编代码的优点包括:高性能:MIPS汇编代码可以提供高性能,因为它可以直接控制处理器的寄存器和指令。

精细的控制:MIPS汇编代码允许程序员对硬件进行精细的控制,这对于嵌入式系统和实时系统非常重要。

可移植性:MIPS汇编代码可以移植到不同的MIPS处理器上,因为MIPS处理器具有相同的指令集架构。

MIPS汇编

ext d,s,shf,sz 从32位寄存器提取位域。Shf是位域在s中的移位到 第0位所需要的位移量,sz是位域包含的位的个数。 mask=(2**sz-1)<<shf,d=(s&mask)>>shf

/p-141124298.html (MIPS指令与汇编)

or d,s,t

d=s | t

ori d,s,j 作OR

d=s|(unsigned)j,跟一个常数执行“或”操

sllv d,t,s d=t<<(s%32) (shift left logic by variable)

sll d,s,shf d=s<<shf;sll d,t,s,d=t<<(s%32)

sra d,s,shf d=(signed)s>>shf,shift-right arithmetic,算术右移, 最高位填充,适用于有符号数,sra d,s,t,d=(signed)s>>(t%32)

srav d,s,t sra d,s,t

srl d,s,shf d=(unsigned)s>>shf ,shift-right logical,逻辑右移, 类似C的无符号量的移位

.data伪指令

定义程序的数据段,程序的变量需要在该伪指令 下定义,汇编程序会分配和初始化变量的存储空间

.text伪指令

定义程序的代码段

.global伪指令

声明一个符号位全局的,全局符号可以被其他的 文件引用,用该伪指令声明一个程序的main过程

寻址

➢ 直接寻址

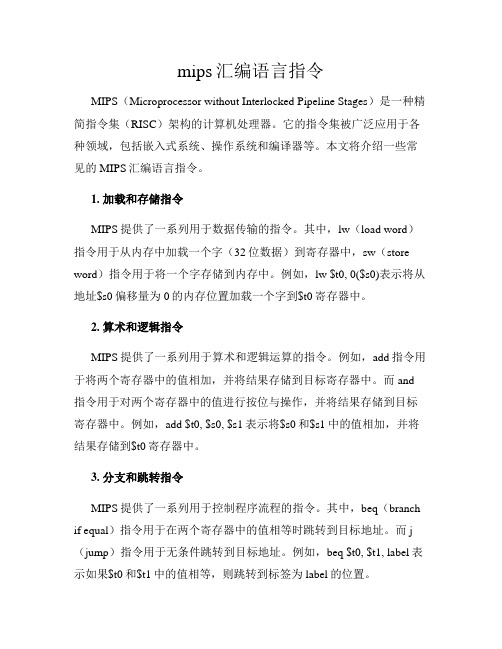

mips汇编语言指令

mips汇编语言指令MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集(RISC)架构的计算机处理器。

它的指令集被广泛应用于各种领域,包括嵌入式系统、操作系统和编译器等。

本文将介绍一些常见的MIPS汇编语言指令。

1. 加载和存储指令MIPS提供了一系列用于数据传输的指令。

其中,lw(load word)指令用于从内存中加载一个字(32位数据)到寄存器中,sw(store word)指令用于将一个字存储到内存中。

例如,lw $t0, 0($s0)表示将从地址$s0偏移量为0的内存位置加载一个字到$t0寄存器中。

2. 算术和逻辑指令MIPS提供了一系列用于算术和逻辑运算的指令。

例如,add指令用于将两个寄存器中的值相加,并将结果存储到目标寄存器中。

而and 指令用于对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

例如,add $t0, $s0, $s1表示将$s0和$s1中的值相加,并将结果存储到$t0寄存器中。

3. 分支和跳转指令MIPS提供了一系列用于控制程序流程的指令。

其中,beq(branch if equal)指令用于在两个寄存器中的值相等时跳转到目标地址。

而j (jump)指令用于无条件跳转到目标地址。

例如,beq $t0, $t1, label表示如果$t0和$t1中的值相等,则跳转到标签为label的位置。

4. 移位指令MIPS提供了一系列用于移位操作的指令。

其中,sll(shift left logical)指令用于将一个寄存器中的值左移指定的位数,并将结果存储到目标寄存器中。

例如,sll $t0, $s0, 2表示将$s0中的值左移2位,并将结果存储到$t0寄存器中。

5. 系统调用指令MIPS提供了一系列用于进行系统调用的指令。

其中,syscall指令用于触发系统调用,并根据不同的系统调用号执行相应的操作。

mips汇编程序设计 -回复

mips汇编程序设计-回复MIPS(Microprocessor without Interlocked Pipeline Stages)是一种RISC(Reduced Instruction Set Computer)架构的计算机处理器。

它是由斯坦福大学开发的,并且成为了一种非常流行的汇编语言。

MIPS架构的设计理念是简化指令集,以提高指令的执行效率。

它采用了统一的指令格式,所有的指令都是32位长,并且具有相同的4个字段:操作码(opcode)、目标寄存器(destination register)、源寄存器1(source register 1)和源寄存器2(source register 2)。

这种规范化的指令格式使得MIPS的指令编码非常简洁和高效。

首先,让我们来介绍一些MIPS汇编程序设计的基本概念和概述。

MIPS 指令集包括一系列的算术和逻辑操作指令,如加法、减法、乘法、除法等。

它还包括一些数据传输指令和控制指令,如加载字(load word)、存储字(store word)、分支(branch)和跳转(jump)等。

这些指令使用寄存器来存储和操作数据,寄存器是一个特殊的存储空间,它可以读取、写入和运算数据。

在MIPS汇编程序设计中,我们可以使用众多的指令来编写程序。

以中括号内的内容为主题,我们可以考虑编写一个简单的计算器程序,实现两个数的加法、减法、乘法和除法运算。

首先,我们需要确定使用哪些寄存器来存储和操作数据。

MIPS架构提供了32个通用目标寄存器(0-31),我们可以根据需要选择使用哪些寄存器。

在本文中,我们将使用寄存器2和3来存储输入的两个数,寄存器4来存储计算结果。

接下来,我们需要编写程序的伪代码。

伪代码是一种类似于编程语言的描述方式,它可以帮助我们更好地理解和设计程序。

下面是我们的伪代码:1. 读取输入的两个数2. 计算加法结果3. 计算减法结果4. 计算乘法结果5. 计算除法结果6. 输出计算结果现在,我们可以将伪代码转换为MIPS汇编指令。

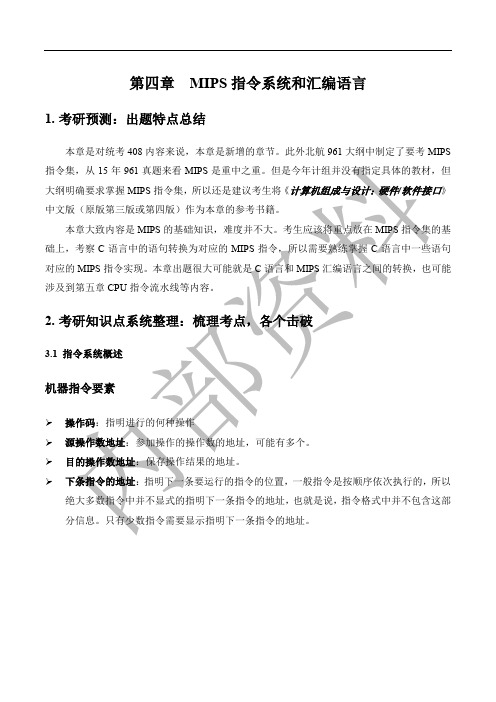

MIPS 指令系统和汇编语言

其中 A1 为目的操作数地址,A2 为源操作数地址。 指令的含义:(A1)OP(A2)→A1。 (3)一地址指令 一地址指令顾名思义只有一个显地址,它的指令格式为: OP A1

一地址指令只有一个地址, 那么另一个操作数来自何方呢?指令中虽未明显给出,但按事 先约定,这个隐含的操作数就放在一个专门的寄存器中。因为这个寄存器在连续性运算时,保 存着多条指令连续操作的累计结果,故称为累加寄存器(AC) 。 指令的含义:(AC)OP(A1)→AC (4)零地址指令 零地址指令格式中只有操作码字段,没有地址码字段,其格式为: OP 零地址的运算类指令仅用在堆栈计算机中的。 堆栈计算机没有一般计算机中必备的通用寄 存器,因此堆栈就成为提供操作数和保存运算结果的唯一场所。通常,参加运算的两个操作数 隐含地从堆栈顶部(栈顶和次栈顶单元)弹出,送到运算器中进行运算,运算的结果再隐含地 压入堆栈中。对于同一个问题,用三地址指令编写的程序最短,但指令长度(程序存储量)最 长;而用二、一、零地址指令来编写程序,程序的长度一个比一个长,但指令的长度一个比一 个短。

作码结构等,是一个很复杂的问题,它与计算机系统结构、数据表示方法、指令功能设计等都 密切相关。

指令的基本格式

一条指令就是机器语言的一个语句, 它是一组有意义的二进制代码, 指令的基本格式如下: 操作码字段 地址码字段

其中操作码指明了指令的操作性质及功能,地址码则给出了操作数的地址。 指令的长度是指一条指令中所包含的二进制代码的位数, 指令长度与机器字长没有固定的 关系,它可以等于机器字长,也可以大于或小于机器字长。通常,把指令长度等于机器字长的 指令称为单字长指令; 指令长度等于半个机器字长的指令称为半字长指令;指令长度等于两个 机器字长的指令称为双字长指令。 在一个指令系统中,若所有指令的长度都是相等的,称为定长指令字结构。定长结构指令 系统控制简单,但不够灵活。若各种指令的长度随指令功能而异,就称为变长指令字结构。现 代计算机广泛采用变长指令字结构,变长结构指令系统灵活,但指令的控制较复杂。 计算机执行一条指令所需要的全部信息都必须包含在指令中。 对于一般的双操作数运算类 指令来说,除去操作码之外,地址码字段中应包含以下信息: 第一操作数地址。 第二操作数地址。 操作结果存放地址。 这些信息可以在指令中明显的给出,称为显地址;也可以依照某种事先的约定,用隐含的 方式给出,称为隐地址。所以,从地址结构的角度可以分为三地址指令、二地址指令、一地址 指令和零地址指令。 (1)三地址指令 三地址指令格式为: OP A1 A2 A3

MIPS汇编学习

MIPS汇编学习MIPS汇编学习 mips汇编不同于x86汇编,属于精简指令集,常见于路由器等⼀些嵌⼊式设备中。

mips汇编没有对堆栈的直接操作,也就是没有push和pop指令,mips汇编中保留了32个通⽤寄存器,但是不同于x86汇编,mips汇编中没有ebp/rbp寄存器。

mips每条指令都⽤固定的长度,每条指令都是四个字节,所以内存数据的访问必须以32位严格对齐,这⼀点也不同于x86汇编。

通过⼀个demo,⽤mips-linux-gnu-gcc编译,通过IDA远程调试,来理解mips汇编中的⼀些概念。

#include<stdio.h>int sum(int a,int b){return a+b;}int main(){int a=1,b=2,c;c=sum(a,b);printf("%d\n",c);return 0;}32个通⽤寄存器的功能和使⽤约定定义如下:mips汇编中重要的寄存器: 1.堆栈指针$sp,也就是$29指向堆栈的栈顶,类似于x86中的ebp和rbp指针; 2.$0寄存器的值始终为常数0; 3.PC寄存器保留程序执⾏的下⼀条指令,相当于x86架构中的eip寄存器; 4.参数传递的时候,$a0-$a3寄存器保存函数的前四个参数,其他的参数保存在栈中; 5.$ra寄存器,保存着函数的返回地址,这⼀点也不同于x86汇编中将返回地址保存在栈中。

在函数A执⾏到调⽤函数B的指令时,函数调⽤指令复制当前的$PC寄存器的值到$RA寄存器,然后跳转到B函数去执⾏,即当前$RA寄存器的值就是函数执⾏结束时的返回地址。

如上图所⽰,调⽤sum函数之前,$ra寄存器的值是0x7f62eca8。

进⼊分⽀延迟槽之后,$ra寄存器的值被赋值为$pc寄存器的下⼀条指令地址。

在结束sun函数调⽤之后,通过:jr $ra指令跳转回main函数继续执⾏。

5.mips架构下,对静态数据段的访问,通过$gp寄存器配合基址寻址来实现; 7.$30寄存器表⽰帧指针,指向正在被调⽤的栈桢,mips和x86由于堆栈结构的区别,调⽤栈时会出现⼀些不同。

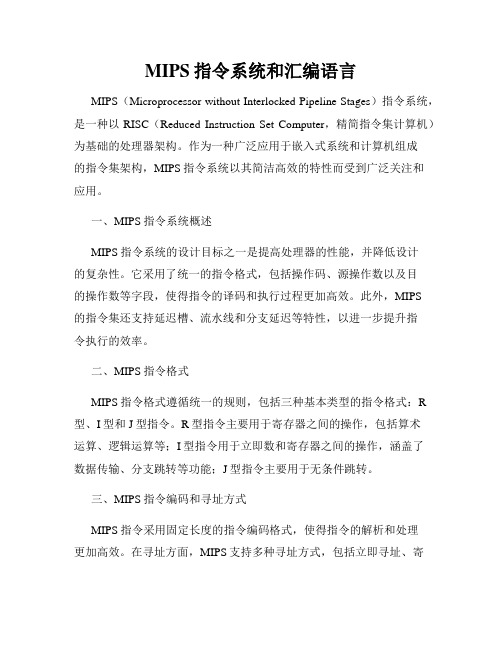

MIPS指令系统和汇编语言

MIPS指令系统和汇编语言MIPS(Microprocessor without Interlocked Pipeline Stages)指令系统,是一种以RISC(Reduced Instruction Set Computer,精简指令集计算机)为基础的处理器架构。

作为一种广泛应用于嵌入式系统和计算机组成的指令集架构,MIPS指令系统以其简洁高效的特性而受到广泛关注和应用。

一、MIPS指令系统概述MIPS指令系统的设计目标之一是提高处理器的性能,并降低设计的复杂性。

它采用了统一的指令格式,包括操作码、源操作数以及目的操作数等字段,使得指令的译码和执行过程更加高效。

此外,MIPS的指令集还支持延迟槽、流水线和分支延迟等特性,以进一步提升指令执行的效率。

二、MIPS指令格式MIPS指令格式遵循统一的规则,包括三种基本类型的指令格式:R 型、I型和J型指令。

R型指令主要用于寄存器之间的操作,包括算术运算、逻辑运算等;I型指令用于立即数和寄存器之间的操作,涵盖了数据传输、分支跳转等功能;J型指令主要用于无条件跳转。

三、MIPS指令编码和寻址方式MIPS指令采用固定长度的指令编码格式,使得指令的解析和处理更加高效。

在寻址方面,MIPS支持多种寻址方式,包括立即寻址、寄存器寻址和间接寻址等。

这些灵活的寻址方式使得MIPS指令更加适用于不同的计算需求。

四、MIPS汇编语言MIPS汇编语言是一种用于编写MIPS指令的低级语言。

它是一种基于文本的表示形式,使用助记符来表示不同的指令和操作。

MIPS汇编语言具有简单易学的特性,更加接近底层硬件的工作原理,使得程序员可以更加精准地控制和优化程序的执行过程。

五、MIPS指令系统的应用由于MIPS指令系统的优越性能和灵活性,它被广泛应用于各种领域。

在嵌入式系统中,MIPS处理器可以实现高性能和低功耗的设计,广泛应用于智能手机、路由器、电视机等设备中。

在计算机组成和操作系统领域,MIPS指令系统被用于讲解和研究计算机的工作原理和底层机制。

汇编语言的类型

汇编语言的类型汇编语言是一种底层的编程语言,它与计算机硬件密切相关,常用于控制硬件的操作。

汇编语言的类型也有多种,下面将分别介绍。

1. x86汇编语言x86汇编语言是一种广泛使用的汇编语言,主要用于Intel和AMD 处理器。

它是一种基于寄存器的汇编语言,通过寄存器来访问内存和其他设备。

x86汇编语言非常灵活,可以用来编写各种类型的应用程序,包括操作系统、驱动程序、安全软件等。

2. ARM汇编语言ARM汇编语言是一种使用ARM处理器的汇编语言。

ARM处理器是一种低功耗的处理器,广泛应用于移动设备和嵌入式系统。

ARM 汇编语言是基于寄存器的汇编语言,也可以通过其他方式来访问内存和其他设备。

ARM汇编语言通常用于编写嵌入式系统的驱动程序和操作系统。

3. MIPS汇编语言MIPS汇编语言是一种使用MIPS处理器的汇编语言。

MIPS处理器是一种高性能的处理器,常用于路由器、交换机和数字信号处理器等。

MIPS汇编语言是基于寄存器的汇编语言,也可以通过其他方式来访问内存和其他设备。

MIPS汇编语言通常用于编写嵌入式系统的驱动程序和操作系统。

4. AVR汇编语言AVR汇编语言是一种使用AVR微控制器的汇编语言。

AVR微控制器是一种低功耗的微控制器,广泛应用于嵌入式系统、电子设备和工业控制等领域。

AVR汇编语言主要基于寄存器,也可以通过其他方式来访问内存和其他设备。

AVR汇编语言通常用于编写嵌入式系统的驱动程序和操作系统。

5. SPARC汇编语言SPARC汇编语言是一种使用SPARC处理器的汇编语言。

SPARC处理器是一种高性能的处理器,常用于服务器和超级计算机等。

SPARC汇编语言主要基于寄存器,也可以通过其他方式来访问内存和其他设备。

SPARC汇编语言通常用于编写操作系统和高性能计算程序等。

总结汇编语言的类型有很多种,不同的汇编语言适用于不同的处理器和应用场景。

汇编语言虽然比高级语言难以学习和使用,但它可以直接控制硬件,因此在某些特定的应用领域中有着不可替代的作用。

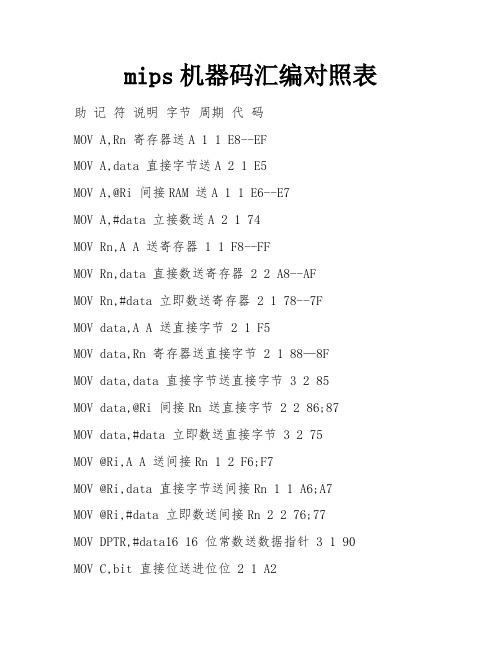

mips机器码汇编对照表

mips机器码汇编对照表助记符说明字节周期代码MOV A,Rn 寄存器送A 1 1 E8--EFMOV A,data 直接字节送A 2 1 E5MOV A,@Ri 间接RAM 送A 1 1 E6--E7MOV A,#data 立接数送A 2 1 74MOV Rn,A A 送寄存器 1 1 F8--FFMOV Rn,data 直接数送寄存器 2 2 A8--AFMOV Rn,#data 立即数送寄存器 2 1 78--7FMOV data,A A 送直接字节 2 1 F5MOV data,Rn 寄存器送直接字节 2 1 88—8FMOV data,data 直接字节送直接字节 3 2 85MOV data,@Ri 间接Rn 送直接字节 2 2 86;87MOV data,#data 立即数送直接字节 3 2 75MOV @Ri,A A 送间接Rn 1 2 F6;F7MOV @Ri,data 直接字节送间接Rn 1 1 A6;A7MOV @Ri,#data 立即数送间接Rn 2 2 76;77MOV DPTR,#data16 16 位常数送数据指针 3 1 90 MOV C,bit 直接位送进位位 2 1 A2MOV bit,C 进位位送直接位 2 2 92MOVC A,@A+DPTR A+DPTR 寻址程序存贮字节送A 3 2 93 MOVC A,@A+PC A+PC 寻址程序存贮字节送A 1 2 83 MOVX A,@Ri 外部数据送A(8 位地址) 1 2 E2;E3 MOVX A,@DPTR 外部数据送A(16 位地址) 1 2 E0 MOVX @Ri,A A 送外部数据(8 位地址) 1 2 F2;F3 MOVX @DPTR,A A 送外部数据(16 位地址) 1 2 F0 PUSH data 直接字节进栈道,SP 加1 2 2 C0POP data 直接字节出栈,SP 减1 2 2 D0XCH A,Rn 寄存器与A 交换 1 1 C8—CFXCH A,data 直接字节与A 交换 2 1 C5XCH A,@Ri 间接Rn 与A 交换 1 1 C6;C7XCHD A,@Ri 间接Rn 与A 低半字节交换 1 1 D6;D72.逻辑运算指令(35条)助记符说明字节周期代码ANL A,Rn 寄存器与到A 1 1 58—5FANL A,data 直接字节与到A 2 1 55ANL A,@Ri 间接RAM与到A 1 1 56;57ANL A,#data 立即数与到A 2 1 54ANL data,A A与到直接字节 2 1 52ANL data,#data 立即数与到直接字节 3 2 53 ANL C,bit 直接位与到进位位 2 2 82ANL C,/bit 直接位的反码与到进位位 2 2 B0 ORL A,Rn 寄存器或到A 1 1 48—4FORL A,data 直接字节或到A 2 1 45ORL A,@Ri 间接RAM或到A 1 1 46;47ORL A,#data 立即数或到A 2 1 44ORL data,A A或到直接字节 2 1 42ORL data,#data 立即数或到直接字节 3 2 43 ORL C,bit 直接位或到进位位 2 2 72ORL C,/bit 直接位的反码或到进位位 2 2 A0 XRL A,Rn 寄存器异或到A 1 1 68—6FXRL A,data 直接字节异或到A 2 1 65XRL A,@Ri 间接RAM异或到A 1 1 66;67XRL A,#data 立即数异或到A 2 1 64XRL data,A A异或到直接字节 2 1 62XRL data,#data 立即数异或到直接字节 3 2 63 SETB C 进位位置1 1 1 D3SETB bit 直接位置1 2 1 D2CLR A A清0 1 1 E4CLR C 进位位清0 1 1 C3CLR bit 直接位清0 2 1 C2CPL A A求反码 1 1 F4CPL C 进位位取反 1 1 B3CPL bit 直接位取反 2 1 B2RL A A循环左移一位 1 1 23RLC A A 带进位左移一位 1 1 33RR A A右移一位 1 1 03RRC A A 带进位右移一位 1 1 13SWAP A A 半字节交换 1 1 C43.算术运算指令(24条)助记符说明字节周期代码ADD A,Rn 寄存器加到A 1 1 28—2FADD A,data 直接字节加到A 2 1 25ADD A,@Ri 间接RAM 加到A 1 1 26;27 ADD A,#data 立即数加到A 2 1 24ADDC A,Rn 寄存器带进位加到A 1 1 38—3F ADDC A,data 直接字节带进位加到A 2 1 35ADDC A,@Ri 间接RAM 带进位加到A 1 1 36;37 ADDC A,#data 立即数带进位加到A 2 1 34SUBB A,Rn 从A 中减去寄存器和进位 1 1 98—9F SUBB A,data 从A 中减去直接字节和进位 2 1 95 SUBB A,@Ri 从A 中减去间接RAM 和进位 1 1 96;97 SUBB A,#data 从A 中减去立即数和进位 2 1 94 INC A A加1 1 1 04INC Rn 寄存器加1 1 1 08—0FINC data 直接字节加1 2 1 05INC @Ri 间接RAM 加1 1 1 06;07INC DPTR 数据指针加1 1 2 A3DEC A A减1 1 1 14DEC Rn 寄存器减1 1 1 18—1FDEC data 直接字节减1 2 1 15DEC @Ri 间接RAM 减1 1 1 16;17MUL AB A乘B 1 4 A4DIV AB A被B除 1 4 84DA A A十进制调整 1 1 D44.转移指令(22条)助记符说明字节周期代码AJMP addr 11 绝对转移 2 2 *1LJMP addr 16 长转移 3 2 02SJMP rel 短转移 2 2 80JMP @A+DPTR 相对于DPTR 间接转移 1 2 73JZ rel 若A=0 则转移 2 2 60JNZ rel 若A≠0 则转移 2 2 70JC rel 若C=1 则转移 2 2 40JNC rel 若C≠1 则转移 2 2 50JB bit,rel 若直接位=1 则转移 3 2 20JNB bit,rel 若直接位=0 则转移 3 2 30JBC bit,rel 若直接位=1 则转移且清除 3 2 10CJNE A,data,rel 直接数与A 比较,不等转移 3 2 B5CJNE A,#data,rel 立即数与A 比较,不等转移 3 2 B4CJNE @Ri,#data,rel 立即数与间接RAM比较,不等转移 3 2 B6;B7CJNE Rn,#data,rel 立即数与寄存器比较不等转移 3 2 B8—BFDJNZ Rn,rel 寄存器减1 不为0 转移 2 2 D8—DFDJNZ data,rel 直接字节减1 不为0 转移 3 2 D5ACALL addr 11 绝对子程序调用 2 2 *1 LCALL addr 16 子程序调用 3 2 12 RET 子程序调用返回 1 2 22RETI 中断程序调用返回 1 2 32NOP 空操作 1 1 00。

MIPS汇编指令集

MIPS汇编指令集MIPS汇编MIPS指令集MIPS指令集属于精简指令集MIPS的所有指令都是32位,指令格式简单,⽽X86的指令长度不是固定的。

简单的指令和格式易于译码和流⽔线操作,但是代码密度不⾼,导致⼆进制⽂件⼤MIPS有32个通⽤寄存器REG,为什么是32个⽽不是更多呢?因为更多的寄存器需要更多的指令空间对寄存器编码,也会增加上下⽂切换的负担。

MIPS指令格式R格式655556op rs rt rd shamt funct⽤处:寄存器-寄存器ALU操作读写专⽤寄存器I格式65516op rs rt⽴即数操作⽤处:加载/存储字节,半字,字,双字条件分⽀,跳转,跳转并链接寄存器J格式626op跳转地址⽤处:跳转,跳转并链接陷阱和从异常中返回各字段含义:op:指令基本操作,称为操作码。

rs:第⼀个源操作数寄存器。

rt:第⼆个源操作数寄存器。

rd:存放操作结果的⽬的操作数。

shamt:位移量;funct:函数,这个字段选择op操作的某个特定变体。

例:add $t0,$s0,$s1表⽰$t0=$s0+$s1,即16号寄存器(s0)的内容和17号寄存器(s1)的内容相加,结果放到8号寄存器(t0)。

指令各字段的⼗进制表⽰为:016178032op=0和funct=32表⽰这是加法,16=$s0表⽰第⼀个源操作数(rs)在16号寄存器⾥,17=$s1表⽰第⼆个源操作数(rt)在17号寄存器⾥,8=$t0表⽰⽬的操作数(rd)在8号寄存器⾥。

把各字段写成⼆进制,为:00000010000100010100000000100000这就是上述指令的机器码(machine code),可以看出是很有规则性的。

MIPS指令MIPS没有栈操作指令,调⽤⼦程序时没有⾃动压栈的call指令,只能⽤jal。

MIPS的内存映射、中断等功能都做到了协处理器0(cp0)中,浮点运算做到了协处理器1(cp1)中。

MIPS的寻址⽅式最简单,仅有寄存器加偏移寻址⽅式。

MIPS汇编指令学习

MIPS汇编指令学习MIPS汇编语⾔基础 MIPS的系统结构及设计理念⽐较先进,其指令系统经过通⽤处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV、MIPS V,以及嵌⼊式指令体系MIPS16、MIPS32到MIPS64的发展。

MIPS32的架构是⼀种基于固定长度的定期编码指令集,并采⽤导⼊/存储(load/store)数据模型。

经改进,这种架构可⽀持⾼级语⾔的优化执⾏。

在路由器中,经常使⽤的⼀种MIPS架构就是MIPS32。

MIPS寄存器 RISC的⼀个显著特点就是⼤量使⽤寄存器。

因为寄存器的存取可以在⼀个时钟周期内完成,同时简化了寻找⽅式,所以,MIPS32的指令中除了加载/存储指令以外,都使⽤寄存器或者⽴即数作为操作数,以便让编译器通过保持对寄存器内数据的频繁存取进⼀步优化代码的⽣成性能。

MIPS32寄存器分为两类:通⽤寄存器(GPR)和特殊寄存器。

1、通⽤寄存器(GPR) 在MIPS体系结构中有32个通⽤寄存器,在汇编程序中可以⽤编号$0~$31表⽰,也可以⽤寄存器的名字表⽰,如$sp、$t1、$ta等,如图,堆栈是从内存的⾼地址⽅向向低地址⽅向增长的。

编号寄存器名称寄存器描述0 zero第0号寄存器,其值始终为01$at保留寄存器2~3$v0~v1values, 保存表达式或函数返回结果4-7$a0~a3aruments, 作为函数的前4个参数8~15$t0~$t7temporaries,供汇编程序使⽤的临时寄存器16~23$s0~$s7saved values,⼦函数使⽤时需要先保存原寄存器的值24~25$t8~t9temporaries, 供汇编程序的临时寄存器,补充$t0~t726~27$k0~$k1保留,中断处理函数使⽤28$gp global pointer,全局指针29$sp stack pointer, 堆栈指针,指向堆栈的栈顶30$fp frame pointer, 保存栈指针31$ra return address, 返回地址$0:即$zero,该寄存器总是返回0,为0这个有⽤常数提供了⼀个简洁的编码形式。

MIPS微处理器原理-MIPS汇编语言

操作数:寄存器、存储器、常数

因常数的值可以立即访问,故又称为立即数(immediate)。

加立即数指令 ( addi ):

# $s0=a, $s1=b

addi $s0, $s1, 4 # a=b+4 addi $s1, $s0,-2 # b=a-2

没有NOT,可用下面代替 A NOR $0 = NOT A

Source Values $s1 0000 0000 0000 0000 0000 0000 1111 1111

andi rt、rs、imm

Assembly Code

imm 0000 0000 0000 0000 1111 1010 0011 0100

用途 常数0 汇编器临时变量 函数返回值 函数参数 临时变量 保存变量

名称 $t8 ~ $t9 $k0 ~$k1 $gp $sp $fp $ra

编号 24~25 26~27 28 29 30 31

用途

临时变量

操作系统临时变量

全局指针

栈指针

帧指针

保存变量

8

MIPS Register Set

Name $0 $at $v0-$v1 $a0-$a3 $t0-$t7 $s0-$s7 $t8-$t9 $k0-$k1 $gp $sp $fp $ra

4个准则: ① 简单设计有助于规整化; ② 加快常见功能; ③ 越小的设计越快; ④ 好的设计需要好的折中方法。

4

R I S C 指令集的特点

Reduced Instruction Set Computer Complex Instruction Set Computer

• 精简了指令系统,流水线以及常用指令均可用硬件执行;

c语言 mips指令

MIPS是一种精简指令集(RISC)架构,它是一种用于构建嵌入式系统、超级计算机和游戏机的微处理器架构。

在C语言中,您可以使用汇编指令集来与MIPS架构进行交互。

以下是一些常用的MIPS汇编指令:1. add:将两个操作数相加并将结果存储在指定的寄存器中。

2. sub:从第一个操作数中减去第二个操作数并将结果存储在指定的寄存器中。

3. mul:将两个操作数相乘并将结果存储在指定的寄存器中。

4. div:将第一个操作数除以第二个操作数并将结果存储在指定的寄存器中。

5. move:将一个操作数的值复制到另一个操作数中。

6. load:将数据从内存加载到寄存器中。

7. store:将数据从寄存器存储到内存中。

8. jump:无条件跳转到指定的地址。

9. jr:将控制权转移给指定的寄存器中的地址。

10. syscall:发起系统调用并等待其完成。

在C语言中,您可以使用内联汇编(inline assembly)来编写MIPS汇编代码。

下面是一个使用内联汇编实现两个整数相加的示例:```cint main() {int a = 10;int b = 20;int result;__asm__ __volatile__("add $t0, %1, %2; move %0, $t0" : "=r"(result) : "r"(a), "r"(b));printf("The result is %d\n", result);return 0;}```在这个示例中,使用了add指令将a和b相加,并将结果存储在$t0寄存器中。

然后使用move指令将$t0寄存器的值复制到result变量中。

注意,使用了$符号来标识寄存器,%符号来标识操作数。

MIPS指令集及汇编

和R12000(1997年)等型号。 z 随后,MIPS公司把重点放在嵌入式系统。

{ 1999年发布MIPS32和MIPS64架构标准,集成了所有原 来MIPS指令集,并且增加了许多更强大的功能。陆续开发 了高性能、低功耗的32位处理器内核(core)MIPS324Kc 与高性能64位处理器内核MIPS64 5Kc。

{ 应用广泛的32位MIPS CPU包括R2000,R3000 其ISA都是MIPS I,另一个广泛使用的、含有许多 重要改进的64位MIPS CPU R4000及其后续产 品,其ISA版本为MIPS III

一、 MIPS简介

{ 1984年,MIPS计算机公司成立。1992年,SGI收购了 MIPS计算机公司。1998年,MIPS脱离SGI,成为MIPS 技术公司。

龙芯2E笔记本电脑运行 OpenOffice打开Word文档

ቤተ መጻሕፍቲ ባይዱ

二、MIPS体系结构

{ 指令集体系结构类型:寄存器——寄存器型

(1)寄存器的特点 (2)整数乘法单元和寄存器 (3)寻址方式 (4)存储器和寄存器中的数据类型 (5)流水线冒险

二、 MIPS体系结构——(1)寄存器

{ MIPS 包含32个通用寄存器

{ 2000年,MIPS公司发布了针对MIPS32 4Kc的版本以及 64位MIPS 64 20Kc处理器内核。

一、 MIPS简介

{ 基于龙芯2E处理器的千元的PC、1999元的笔记本电脑、 意法半导体3000万元购买龙芯2E 5年的生产和销售权, 国产操作系统内核在龙芯2E上测试成功。

mips汇编语言代码示例

mips汇编语言代码示例MIPS汇编语言代码示例:计算两个数的和MIPS汇编语言是一种基于RISC(精简指令集计算机)架构的汇编语言,它被广泛应用于嵌入式系统、数字信号处理、计算机视觉等领域。

本文将以计算两个数的和为例,介绍MIPS汇编语言的基本语法和指令。

我们需要了解MIPS汇编语言的寄存器。

MIPS架构中有32个通用寄存器,分别用$0~$31表示。

其中,$0$寄存器始终为$0$,$1~$3寄存器用于函数调用,$4~$7寄存器用于保存函数调用时的参数,$8~$15寄存器用于保存临时变量,$16~$23寄存器用于保存全局变量,$24~$25寄存器用于保存函数调用时的返回值,$26~$27寄存器用于保存系统调用的参数,$28寄存器用于保存全局指针,$29寄存器用于保存栈指针,$30寄存器用于保存帧指针,$31寄存器用于保存程序计数器。

接下来,我们可以编写计算两个数的和的MIPS汇编语言代码。

假设我们要计算$a+b$的值,可以使用以下代码:```.dataa: .word 2b: .word 3sum: .word 0.text.globl mainmain:lw $t0, alw $t1, badd $t2, $t0, $t1sw $t2, sumli $v0, 10syscall```我们使用.data段定义了三个变量:$a$、$b$和$sum$。

$a$和$b$分别被初始化为$2$和$3$,$sum$被初始化为$0$。

接着,我们使用.text段定义了一个全局函数$main$,并使用.globl指令将其声明为全局函数。

在$main$函数中,我们首先使用lw指令将$a$和$b$的值分别加载到$t0$和$t1$寄存器中。

然后,我们使用add指令将$t0$和$t1$的值相加,并将结果保存到$t2$寄存器中。

最后,我们使用sw指令将$t2$的值存储到$sum$变量中。

最后,我们使用li指令将$v0$寄存器设置为$10$,并使用syscall指令退出程序。

mips汇编指令手册

mips汇编指令手册摘要:一、概述MIPS汇编指令手册二、MIPS汇编指令的基本结构1.指令格式2.操作码和操作数3.寄存器文件三、数据传输指令1.加载和存储指令2.寄存器间的数据传输四、算术和逻辑指令1.加法和减法指令2.乘法和除法指令3.逻辑指令五、移位和位操作指令1.移位指令2.位操作指令六、条件跳转和分支指令1.无条件跳转指令2.条件跳转指令3.分支指令七、循环指令1.循环开始和结束指令2.循环计数指令八、调用和返回指令1.调用指令2.返回指令九、中断和异常处理指令1.中断指令2.异常处理指令十、系统调用指令1.系统调用指令概述2.常用系统调用举例正文:一、概述MIPS汇编指令手册MIPS(Microprocessor without Interlocking Protection Structures)是一种精简指令集计算机(RISC)架构,广泛应用于嵌入式系统和处理器设计。

MIPS汇编指令手册提供了详细的指令集和编程指南,帮助开发者更好地使用MIPS处理器。

本文将简要介绍MIPS汇编指令的基本结构和分类,以供参考。

二、MIPS汇编指令的基本结构1.指令格式MIPS汇编指令采用固定长度的指令格式,包括操作码和操作数。

操作码表示指令的类型,操作数表示指令处理的数据。

2.操作码和操作数MIPS汇编指令的操作码和操作数分为两类:立即数和寄存器。

立即数直接参与运算,而寄存器表示要从寄存器文件中操作的数据。

3.寄存器文件MIPS处理器具有31个通用寄存器,分为两组:一组是30个32位寄存器(X0-X29),另一组是1个32位通用寄存器(PC)。

三、数据传输指令数据传输指令主要用于在内存和寄存器之间传输数据。

1.加载和存储指令加载指令(LDR)将内存中的数据加载到寄存器中,存储指令(STR)将寄存器中的数据存储到内存中。

2.寄存器间的数据传输寄存器间的数据传输可以通过指令如:MOV、CMP等实现。

MIPS体系结构和汇编语言快速入门

MIPS体系结构和汇编语言快速入门一、MIPS体系结构概述(200字)MIPS处理器由五个流水线阶段组成:取指令(IF)、指令解码(ID)、执行(EX)、访存(MEM)和写回(WB)。

这种流水线架构能够并行处理多条指令,提高了处理器的性能。

二、MIPS汇编语言基础(400字)MIPS汇编语言是一种低级语言,与二进制机器码一一对应。

它使用助记符(mnemonics)来表示不同的指令和操作数。

MIPS指令主要分为以下几类:1.加载和存储指令:- lw $t, offset($s):从地址$s+offset处加载一个字,并存入寄存器$t中。

- sw $t, offset($s):将寄存器$t中的值存储到地址$s+offset处。

2.算术和逻辑指令:- add $d, $s, $t:将寄存器$s和$t中的值相加,结果存入寄存器$d中。

- sub $d, $s, $t:将寄存器$s和$t中的值相减,结果存入寄存器$d中。

- and $d, $s, $t:将寄存器$s和$t的值逐位与运算,结果存入寄存器$d中。

- or $d, $s, $t:将寄存器$s和$t的值逐位或运算,结果存入寄存器$d中。

3.分支和跳转指令:- beq $s, $t, offset:如果寄存器$s和$t的值相等,则跳转到当前PC加上offset的地址处。

- j target:无条件跳转到指定的目标地址。

三、MIPS程序示例(600字)下面是一个使用MIPS汇编语言编写的简单程序,用于计算斐波那契数列的第10个数:.dataresult: .space 4 # 用于存储结果.text.globl mainmain:#初始化前两个斐波那契数li $t0, 0 # 第一个数为0sw $t0, result # 存储到result中li $t1, 1 # 第二个数为1sw $t1, result+4 # 存储到result的下一个字节中#循环计算剩下的斐波那契数li $t2, 2 # 计数器初始值为2loop:add $t3, $t0, $t1 # 计算下一个数sw $t3, result+($t2*4) # 存储到result的下一个位置addi $t2, $t2, 1 # 计数器加1move $t0, $t1 # 更新前两个数move $t1, $t3blt $t2, 10, loop # 如果计数器小于10,跳转到loop处继续循环#输出结果li $v0, 1 # syscall代码1表示输出整数lw $a0, result+36 # 读取result的第10个字节syscall # 执行系统调用#程序结束li $v0, 10 # syscall代码10表示程序结束syscall代码中使用了伪指令(如.data和.text)来指定数据段和代码段。

mips汇编语言指令

mips汇编语言指令MIPS(Microprocessor without Interlocked Pipelined Stages)是一种常见的RISC(Reduced Instruction Set Computer)体系结构,广泛用于许多计算机体系结构和嵌入式系统中。

本文将对MIPS汇编语言指令进行详细介绍和解析。

一、MIPS汇编语言概述MIPS汇编语言是一种低级语言,用于直接操作计算机硬件。

其指令集由一系列操作码(Opcode)和操作数组成。

MIPS指令集基于三个基本原则:简单性、固定的指令长度和规则对齐。

MIPS指令主要包括算术操作指令、逻辑操作指令、控制类指令和数据传输指令等。

二、MIPS汇编语言的基本指令1. 算术操作指令MIPS提供了一系列算术操作指令,如add(加法)、sub(减法)、mul(乘法)和div(除法)等。

这些指令用于对寄存器中的数据进行算术运算,并将结果保存在目标寄存器中。

示例:add $t0, $s1, $s2 # 将$s1和$s2中的值相加,结果保存在$t0中2. 逻辑操作指令逻辑操作指令用于对寄存器中的数据进行逻辑运算,如and(逻辑与)、or(逻辑或)和not(逻辑非)等。

示例:and $t0, $s1, $s2 # 将$s1和$s2中的值进行逻辑与运算,并将结果保存在$t0中3. 控制类指令MIPS提供了一系列控制类指令,如beq(条件分支)、j(无条件跳转)和jr(函数返回)等。

这些指令用于改变程序执行的流程。

示例:beq $t0, $t1, label # 如果$t0和$t1中的值相等,则跳转到label处继续执行4. 数据传输指令数据传输指令用于在寄存器和存储器之间传输数据,如lw(从存储器中加载数据)和sw(将数据存储到存储器中)等。

示例:lw $t0, 0($s1) # 从地址$s1+0处加载数据,并保存到$t0中三、MIPS汇编语言的特点与优势1. 简洁性MIPS汇编语言指令集相对较为简单,指令数目较少,易于理解和学习。

mips汇编指令手册

mips汇编指令手册摘要:1.MIPS 汇编指令手册简介2.MIPS 汇编指令的分类3.MIPS 汇编指令的寻址方式4.MIPS 汇编指令的指令集5.MIPS 汇编指令的应用领域正文:1.MIPS 汇编指令手册简介MIPS 汇编指令手册是一本详细描述MIPS(Microprocessor without Interlocked Pipeline Stages,无锁流水线处理器)指令集的参考书。

MIPS 汇编指令手册包含了MIPS 处理器能够理解和执行的所有指令,以及这些指令的格式、功能和寻址方式等内容。

对于计算机体系结构和汇编语言程序设计等相关领域的研究者和开发者来说,MIPS 汇编指令手册是一本非常重要的参考资料。

2.MIPS 汇编指令的分类MIPS 汇编指令可以分为三类:(1)存储器指令:这类指令主要用于对存储器进行读写操作,包括加载(load)和存储(store)指令。

(2)算术逻辑指令:这类指令主要用于执行各种算术和逻辑运算,包括加法、减法、乘法、除法等运算指令,以及与、或、非等逻辑运算指令。

(3)转移指令:这类指令主要用于控制程序的执行流程,包括条件跳转、无条件跳转、循环等指令。

3.MIPS 汇编指令的寻址方式MIPS 汇编指令的寻址方式主要有以下几种:(1)直接寻址:指令中直接给出操作数的地址。

(2)间接寻址:指令中给出操作数的地址的地址,需要通过两次访问存储器才能获取到操作数。

(3)寄存器寻址:指令中给出操作数在寄存器中的名字。

(4)立即寻址:指令中直接给出操作数,操作数紧跟在指令后面。

4.MIPS 汇编指令的指令集MIPS 汇编指令集包含了大量的指令,这里列举一些常见的指令:(1)加载指令:load(2)存储指令:store(3)算术运算指令:add、sub、mul、div(4)逻辑运算指令:and、or、not(5)转移指令:jmp、jz、jnz、循环指令等5.MIPS 汇编指令的应用领域MIPS 汇编指令广泛应用于计算机体系结构、操作系统、编译原理等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

XVECENT宏中的分支延迟槽执行数据加载,但是由于数据加载延迟,不能在f(romExcHandle)的第一条指令中访问k0参数,或者在li后添加一条nop指令。

############################################

1.5.2 编址及内存访问

跳转指令(j):有限的32位指令长度对于大型程序的分支跳转支持确实是个难题。MIPS指令中最小的操作码域占6位,剩下的26位用于跳转目标的编址。由于所有指令在内存中都是4字节对齐的,因此最低的2个地址位是无需存储的,这样可供寻址范围为2^28=256MB。分支跳转地址被当做一个256MB的段内绝对地址,而非PC相对寻址。这对于地址范围超过256MB的跳转程序而言是无能为力的,所幸目前很少遇到这么大的远程跳转需求。

1.5.4 Programmer-Visible Pipeline Effects

Delayed branches: The pipeline structure of the MIPS CPU (Figure 1.3) means that when a jump/branch instruction reaches the execute phase and a new program counter is generated,the instruction after the jump will already have been started. Rather than discard this potentially useful work, the architecture dictates that the instruction after a branch must always be executed before the instruction at the target of the branch. The instruction position following any branch is called the branch delay slot.

1.5.4 程序员可见的流水线效果

延迟分支:MIPS CPU的流水线结构(见图1-3)意味着,当跳转/分支指令到达执行阶段并且新的程序计数器已经产生时,紧随其后的下一条指令已经开始执行了。MIPS体系架构并没有抛弃这部分潜在的有用工作,而是规定分支之后的指令总是在分支目标指令之前执行。紧随分支指令之后的位置称为分支延迟槽。

对条件分支来说需要很小心,分支延迟指令必须对(至少)两条路径都不会产生不良影响。在没有任何可用操作时,延迟槽将填充空指令(nop)。

--------------------------------------------------------------

数据加载延迟(加载延迟槽):流水线的另一后果是数据加载指令的数据在下一条指令的ALU阶段启动之后才能从缓存或内存系统中取得,于是下一条指令便不能使用该数据。图1-4显示了此工作原理。

(2) A subroutine call is “jump and link” or“branch and link” and the mne-monics end . . .al.

8.7.8 Jumps, Subroutine Calls, and Branches

The MIPS architecture follows Motorola nomenclature for these instructions, as follows:

(1) PC-relative instructions are called“branch” and absolute-addressed instructions “jump”; the operation mnemonics begin with b orj.

--------------------------------------------------------------

It is the responsibility of the compiler system or the assembly programming wizard to allowfor and even to exploit the branchdelay; it turns out that it is usually possible toarrange that the instruction in the branch delay slot does useful work. Quite often,the instruction that would otherwise have beenplaced before the branch can be moved into the delay slot.

Onmodern MIPS CPUs the load result is interlocked:If you try to use the result too early, the CPU stops until the data arrives. But on early MIPS CPUs, there were no interlocks, and the attempt to use data in the load delay slot led to unpredictable results.

紧跟在加载指令后的指令位置叫做加载延迟槽,优化的编译器可以用延迟槽来做一些有用的工作。这一特性对程序员是透明的,很多时候汇编器向该延迟槽填入一个空操作指令(nop)。

在现代MIPS CPU中加载结果会导致互锁:如果你想过早使用该数据,CPU就会停下来直到该数据到达。但早期的MIPSCPU中没有互锁硬件,任何企图提前使用加载延迟槽中的数据的操作都将导致无法预料的结果。

.5cesses

Jump instructions: The limited 32-bit instruction length is a particular problem for branches in anarchitecture that wants to support very large programs. The smallest opcode field in a MIPS instruction is 6 bits, leaving 26 bits to define the target of a jump. Since all instructions are four-byte aligned in memory,the two least significant address bits need not be stored,allowing an address range of 2^28= 256 MB. Rather than make this branch PC relative, this is interpreted as an absolute address within a 256MB segment. That’s inconvenient for single programs larger than this, although it hasn't been much of a problem yet!

This can be a bit tricky on a conditional branch, where the branch delay instructionmust be (at least)harmless on bothpaths. Where nothing useful can be done, the delay slot isfilled with a nopinstruction.

--------------------------------------------------------------

Late Data from load(load delay slot): Another consequence of the pipeline is that a load instruction’s data arrives from the cache/memory system after the next instruction’s ALU phase starts—so it is not possible to use the data from a load in the following instruction. (See Figure 1.4 for how this works.)

例如《VxWorks BSP for AMD's AU1500(MIPS)》的V100R001CPE\romMipsInit.s中定义ROM异常入口点时,XVECENT宏中利用分支延迟槽传参。

#define XVECENT(f,bev) b f; li k0,bev

############################################

--------------------------------------------------------------

编译器或汇编程序可以考虑充分利用分支延迟,比如在延迟槽中填充有用的指令,把原来放在分支指令之前的指令移动到延迟槽中。

############################################

Theinstruction position immediately after the load is called the load Delay Slot, and an optimizingcompiler will try to do something useful with it. The assembler will hide this from you but may end upputting in a nop.